TAS6421-Q1

ZHCSJM6A - APRIL 2019 - REVISED OCTOBER 2019

# 具有负载突降保护和 I<sup>2</sup>C 诊断功能的 TAS6421-Q1 75W、2MHz 数字输入单通道汽车用 D 类 Burr-Brown™ 音频放大器

## 1 特性

- 高级负载诊断功能

- 直流诊断功能,无需输入时钟即可执行

- 交流诊断功能,可通过阻抗和相位响应实现高频 扬声器检测

- 可轻松满足 CISPR25-L5 EMC 规范

- 符合面向汽车 应用的 AEC-Q100 标准

- 温度等级: -40°C 至 +125°C

- 音频输入

- I<sup>2</sup>S 或 4/8 通道 TDM 输入

- 输入采样率: 44.1kHz、48kHz、96kHz

- 输入格式: 16 位至 32 位 I<sup>2</sup>S 和 TDM

- 音频输出

- 单通道桥接式负载 (BTL)

- 最高可达 2.1MHz 的输出开关频率

- 在 4Ω 负载、14.4V BTL 条件下,输出功率为 27W, THD 为 10%

- 在 2Ω 负载、14.4V BTL 条件下,输出功率为 45W, THD 为 10%

- 在 4Ω 负载、14.4V BTL 条件下的音频性能

- 输出功率为 1W 时, THD+N < 0.02%

- 42μV<sub>RMS</sub> 输出噪声

- -90dB 串扰

- 负载诊断,独立于主机运行

- 开路和短路输出负载

- 输出至电池短路或接地短路

- 线路输出检测高达 6kΩ

- 保护

- 输出电流限制和短路保护

- 40V 负载突降

- 可承受接地开路和电源开路

- 过热警告和关断

- 欠压和过压,直流偏移

- 常规运行

- 4.5V 至 26.4V 电源电压

- I<sup>2</sup>C 控制,具有 4 个地址选项

- 削波检测(自锁或非自锁)

## 2 应用

- 汽车音响主机和外部放大器

- 紧急呼叫 (eCall)

- 虚拟引擎声浪系统 (VESS)

#### 3 说明

TAS6421-Q1 器件是一款单通道数字输入 D 类 Burr-Brown™音频放大器,采用了 2.1MHz PWM 开关频率,能以非常小的 PCB 尺寸实现成本优化的解决方案,可针对启停事件在低至 4.5V 的电压下全面运行,并可在高达 40kHz 的音频带宽下提供出色的音质。TAS6421-Q1 的尺寸和引脚与 TAS642x-Q1 系列器件兼容,实现了灵活性,只需进行极少的重新设计即可轻松支持多种系统配置。

输出开关频率既可以设置为高于调幅 (AM) 频带,以消除 AM 频带干扰并降低输出滤波需求及成本;也可以设置为低于 AM 频带,以优化器件效率。该器件具有内置负载诊断功能,用于检测和诊断误接的输出,以及检测交流耦合的高频扬声器。

#### 器件信息(1)

| 器件型号       | 封装         | 封装尺寸 (标称值)       |

|------------|------------|------------------|

| TAS6421-Q1 | HSSOP (56) | 18.41mm × 7.49mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

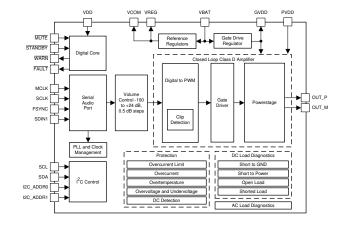

## 功能方框图

|    |                                      | 目录 |      |      |                            |                |

|----|--------------------------------------|----|------|------|----------------------------|----------------|

| 1  | 特性                                   | 1  |      | 10.3 | Feature Description        | 19             |

| 2  | 应用                                   | 1  |      | 10.4 | Device Functional Modes    | 2              |

| 3  | 说明                                   | 1  |      | 10.5 | Programming                | 30             |

| 4  | 修订历史记录                               |    |      | 10.6 | Register Maps              | 3              |

| 5  | 说明(续)                                |    | 11 . | Appl | ication and Implementation | 4              |

| 6  | Device Options                       |    |      | 11.1 | Application Information    | 4              |

| 7  |                                      |    |      | 11.2 | Typical Applications       | 4              |

| ,  | Pin Configuration and Functions      |    | 12   | Powe | er Supply Recommendations  | 5 <sup>,</sup> |

| 8  | Specifications                       |    | 13   | Layo | out                        | 5 <sup>-</sup> |

|    | 8.1 Absolute Maximum Ratings         |    |      | 13.1 | Layout Guidelines          |                |

|    | 8.2 ESD Ratings                      |    |      | 13.2 | Layout Example             |                |

|    | 8.3 Recommended Operating Conditions |    |      | 13.3 | Thermal Considerations     |                |

|    | 8.4 Thermal Information              | -  | 14   | 器件   | 和文档支持                      | 54             |

|    | 8.5 Electrical Characteristics       |    |      | 14.1 | 文档支持                       |                |

| _  | 8.6 Typical Characteristics          |    |      | 14.2 | 接收文档更新通知                   |                |

| 9  | Parameter Measurement Information 1  |    |      | 14.3 | 社区资源                       |                |

| 10 | Detailed description 1               |    |      | 14.4 | 商标                         |                |

|    | 10.1 Overview 1                      |    |      | 14.5 | 静电放电警告                     |                |

|    | 10.2 Functional Block Diagram 1      | 18 |      | 14.6 | Glossary                   |                |

|    |                                      |    |      |      |                            |                |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Ch | hanges from Original (April 2019) to Revision A | Page |

|----|-------------------------------------------------|------|

| •  | 将器件状态从预告信息 更改为生产 数据                             | 1    |

## 5 说明(续)

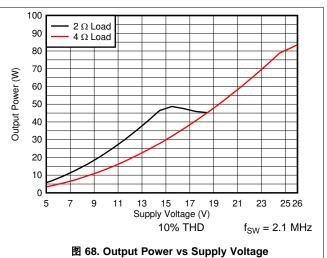

在 14.4V 电源电压条件下,当负载为  $4\Omega$ 、THD+N 为 10% 时,TAS6421-Q1 可提供单通道的 27W 输出功率;当负载为  $2\Omega$ 、THD+N 为 10% 时,可提供 45W 的输出功率。在 25V 电源电压条件下,当负载为  $4\Omega$ 、THD+N 为 10% 时,此器件可提供 75W 的输出功率。

有关兼容引脚的双通道和四通道器件,请参阅 TAS6422-Q1、TAS6424L-Q1、TAS6424M-Q1 和 TAS6424-Q1。

## **6 Device Options**

|             | Channel | Power-Supply    | Channel                |                     | Output Power per o       | channel / 10% THD   |                           |

|-------------|---------|-----------------|------------------------|---------------------|--------------------------|---------------------|---------------------------|

| Part Number | Count   | Voltage Range   | Current<br>Limit (Typ) | 4 Ω / BTL<br>14.4 V | 4 Ω / BTL<br>Max Voltage | 2 Ω / BTL<br>14.4 V | 2 Ω / PBTL<br>Max Voltage |

| TAS6424-Q1  | 4       | 4.5 V to 26.4 V | 6.5 A                  | 27 W                | 75 W at 25 V             | 45 W                | 150 W at 25 V             |

| TAS6424M-Q1 | 4       | 4.5 V to 18 V   | 6.5 A                  | 27 W                | 45 W at 18 V             | 45 W                | 80 W at 18 V              |

| TAS6424L-Q1 | 4       | 4.5 V to 18 V   | 4.8 A                  | 27 W                | 45 W at 18 V             | 27 W                | 80 W at 18 V              |

| TAS6422-Q1  | 2       | 4.5 V to 26.4 V | 6.5 A                  | 27 W                | 75 W at 25 V             | 45 W                | 150 W at 25 V             |

| TAS6421-Q1  | 1       | 4.5 V to 26.4 V | 6.5 A                  | 27 W                | 75 W at 25 V             | 45 W                | N/A                       |

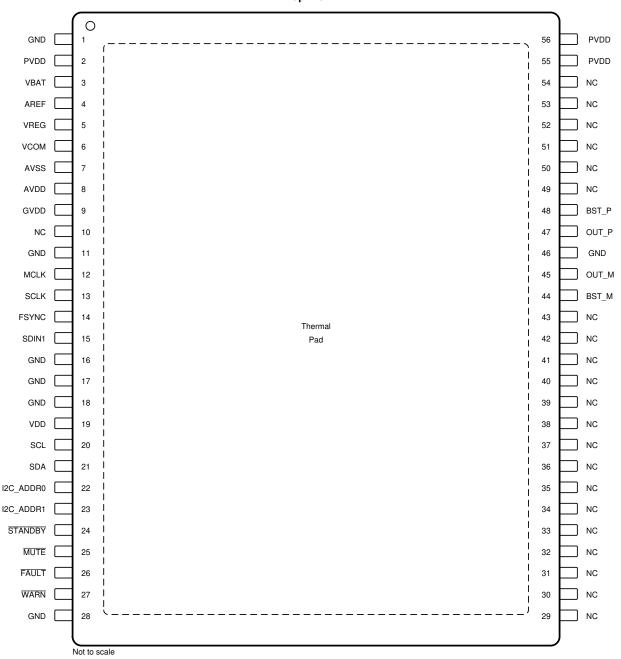

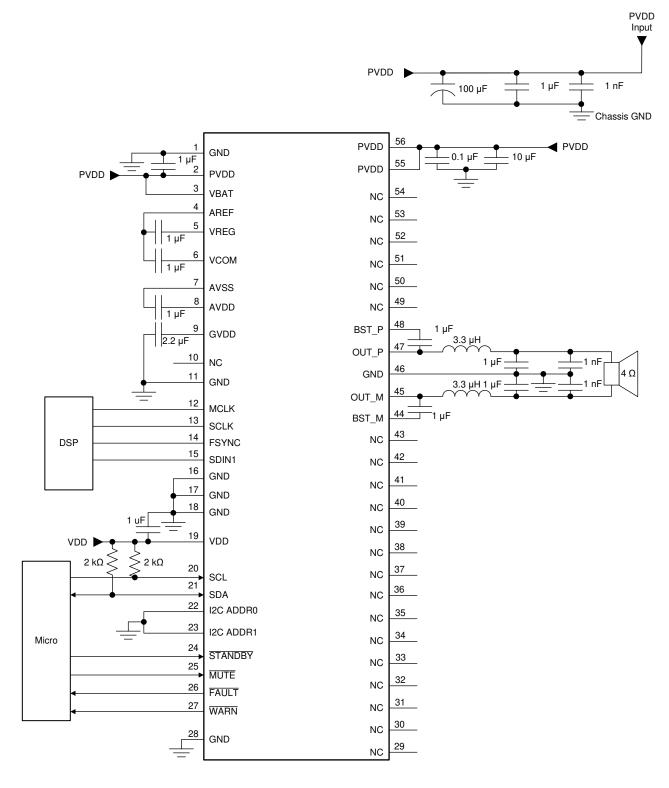

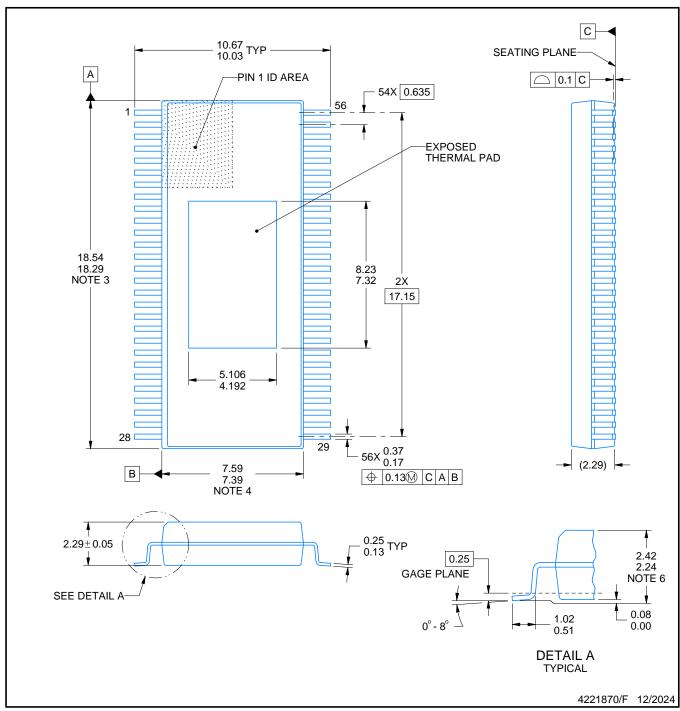

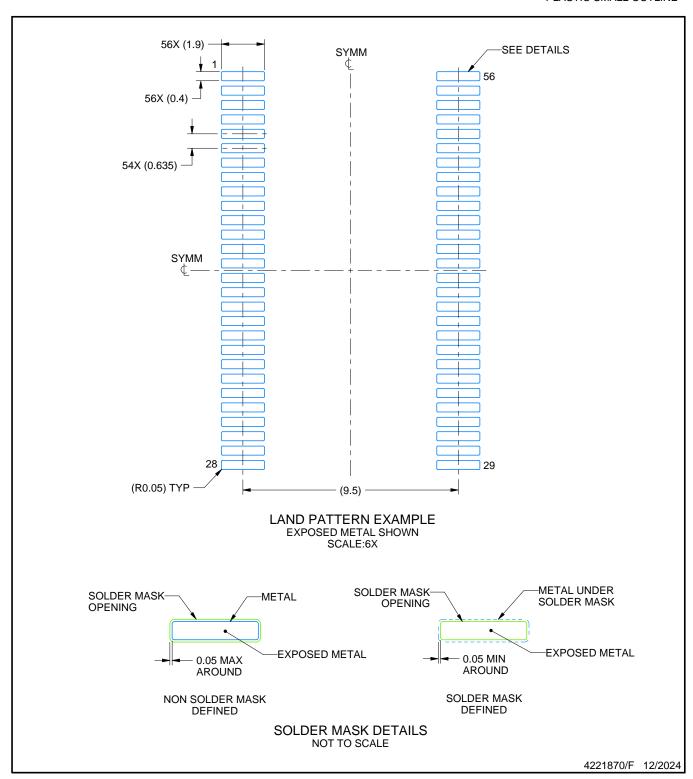

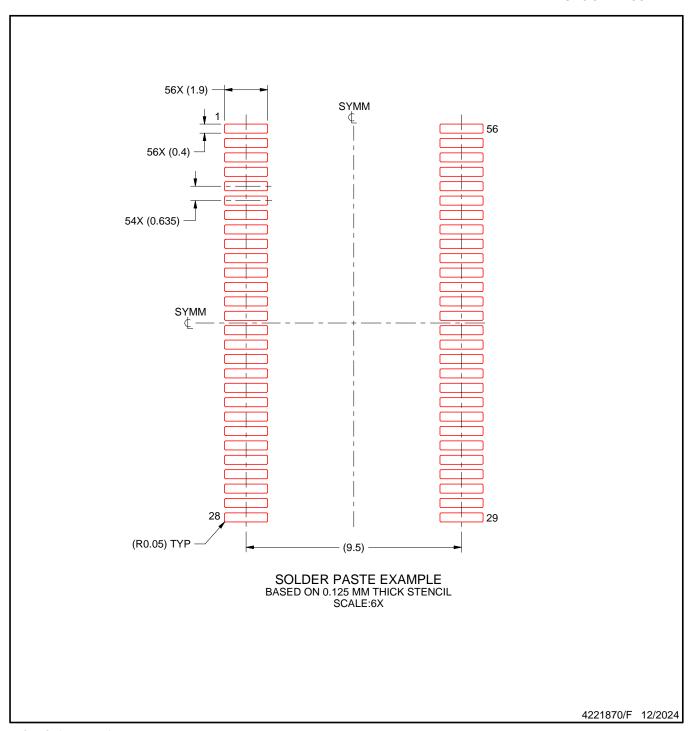

## 7 Pin Configuration and Functions

DKQ Package 56-Pin HSSOP With Exposed Thermal Pad Top View

## **Pin Functions**

| NAME NO.    |                              | TVDE(1) | DESCRIPTION                                                                                                                  |

|-------------|------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

|             |                              | ITPE    | DESCRIPTION                                                                                                                  |

| AREF        | 4                            | PWR     | VREG and VCOM bypass capacitor return                                                                                        |

| AVDD        | 8                            | PWR     | Voltage regulator bypass. Connect 1 µF capacitor from AVDD to AVSS                                                           |

| AVSS        | 7                            | PWR     | AVDD bypass capacitor return                                                                                                 |

| BST_M       | 44                           | PWR     | Bootstrap capacitor connection pin for high-side gate driver                                                                 |

| BST_P       | 48                           | PWR     | Bootstrap capacitor connection pin for high-side gate driver                                                                 |

| FAULT       | 26                           | DO      | Reports a fault (active low, open drain), 100 k $\Omega$ internal pull-up resistor                                           |

| FSYNC       | 14                           | DI      | Audio frame clock input                                                                                                      |

| GND         | 1, 11, 16, 17,<br>18, 28, 46 | GND     | Ground                                                                                                                       |

| GVDD        | 9                            | PWR     | Gate drive voltage regulator derived from VBAT input pin. Connect 2.2 µF capacitor to GND                                    |

| I2C_ADDR0   | 22                           | DI      | I <sup>2</sup> C address pins. Refer to 表 7                                                                                  |

| I2C_ADDR1   | 23                           | וט      | T C address pins. Refer to & 7                                                                                               |

| MCLK        | 12                           | DI      | Audio master clock input                                                                                                     |

| MUTE        | 25                           | DI      | Mutes the device outputs (active low) while keeping output FETs switching at 50%, 100 k $\Omega$ internal pull-down resistor |

| NC          | 10, 29-43,<br>49-54          | NC      | Not connected or pulled to ground                                                                                            |

| OUT_M       | 45                           | NO      | Negative output for the channel                                                                                              |

| OUT_P       | 47                           | РО      | Positive output for the channel                                                                                              |

| PVDD        | 2, 55, 56                    | PWR     | PVDD voltage input (can be connected to battery). Bulk capacitor and bypass capacitor required                               |

| SCL         | 20                           | DI      | I <sup>2</sup> C clock input                                                                                                 |

| SCLK        | 13                           | DI      | Audio bit and serial clock input                                                                                             |

| SDA         | 21                           | DI/DO   | I <sup>2</sup> C data input and output                                                                                       |

| SDIN1       | 15                           | DI      | TDM data input and audio I <sup>2</sup> S data input                                                                         |

| STANDBY     | 24                           | DI      | Enables low power standby state (active Low), 100 kΩ internal pull-down resistor                                             |

| VBAT        | 3                            | PWR     | Battery voltage input                                                                                                        |

| VCOM        | 6                            | PWR     | Bias voltage                                                                                                                 |

| VDD         | 19                           | PWR     | 3.3 V external supply voltage                                                                                                |

| VREG        | 5                            | PWR     | Voltage regulator bypass                                                                                                     |

| WARN        | 27                           | DO      | Clip and overtemperature warning (active low, open drain), 100 k $\Omega$ internal pull-up resistor                          |

| Thermal Pad | _                            | GND     | Provides both electrical and thermal connection for the device. Heatsink must be connected to GND.                           |

<sup>(1)</sup> GND = ground, PWR = power, PO = positive output, NO = negative output, DI = digital input, DO = digital output, DI/DO = digital input and output, NC = no connection

## 8 Specifications

## 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                         |                                                                                |                     | MIN  | MAX       | UNIT |

|-------------------------|--------------------------------------------------------------------------------|---------------------|------|-----------|------|

| PVDD, VBAT              | DC supply voltage relative to GND                                              |                     | -0.3 | 30        | V    |

| V <sub>MAX</sub>        | Transient supply voltage: PVDD, VBAT                                           | t ≤ 400 ms exposure | -1   | 40        | V    |

| V <sub>RAMP</sub>       | Supply-voltage ramp rate: PVDD, VBAT                                           |                     |      | 75        | V/ms |

| VDD                     | DC supply voltage relative to GND                                              |                     | -0.3 | 3.5       | V    |

| I <sub>MAX</sub>        | Maximum current per pin (PVDD, VBAT, OUT_P, OUT_                               | _M, GND)            |      | 8         | Α    |

| I <sub>MAX_PULSED</sub> | Pulsed supply current per PVDD pin (one shot)                                  | t < 100 ms          |      | 12        | Α    |

| V <sub>LOGIC</sub>      | Input voltage for logic pins (SCL, SDA, SDIN1, FSYNC MUTE, STANDBY, I2C_ADDRx) | , MCLK, BCLK, SCLK, | -0.3 | VDD + 0.5 | V    |

| $V_{GND}$               | Maximum voltage between GND pins                                               | -0.3                | 0.3  | V         |      |

| T <sub>J</sub>          | Maximum operating junction temperature                                         | -55                 | 150  | °C        |      |

| T <sub>stg</sub>        | Storage temperature                                                            |                     | -55  | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                    |                                                                                                                                                | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level 2 |                                | ±3000 | V |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|-------|---|

| V <sub>(ESD)</sub> | Electrostatic discharge  Charged-device model (CDM), per AEC Q100–011 All pins  CDM ESD Classification Level C4B Corner pins (1, 28, 29 and 56 | All pins                                                                                  | ±500                           |       |   |

|                    |                                                                                                                                                | CDM ESD Classification Level C4B                                                          | Corner pins (1, 28, 29 and 56) | ±750  | V |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 8.3 Recommended Operating Conditions

|                     |                                                        |                                                      | MIN | TYP  | MAX  | UNIT |

|---------------------|--------------------------------------------------------|------------------------------------------------------|-----|------|------|------|

| PVDD                | Output FET Supply Voltage Range                        | Relative to GND                                      | 4.5 |      | 26.4 |      |

| VBAT                | Battery Supply Voltage Input                           | Relative to GND                                      | 4.5 | 14.4 | 18   | V    |

| VDD                 | DC Logic supply                                        | Relative to GND                                      | 3.0 | 3.3  | 3.5  |      |

| T <sub>A</sub>      | Ambient temperature                                    |                                                      | -40 |      | 125  |      |

| T <sub>J</sub>      | Junction temperature                                   | An adequate thermal design is required               | -40 |      | 150  | °C   |

| R <sub>L</sub>      | Minimum speaker load impedance                         | BTL Mode                                             | 2   | 4    |      | Ω    |

| R <sub>PU_I2C</sub> | I <sup>2</sup> C pullup resistance on SDA and SCL pins |                                                      | 1   | 4.7  | 10   | kΩ   |

| C <sub>Bypass</sub> | External capacitance on bypass pins                    | Pin 2, 3, 5, 6, 8, 19                                |     | 1    |      | μF   |

| C <sub>GVDD</sub>   | External capacitance on GVDD pin                       | Pin 9                                                |     | 2.2  |      | μF   |

| C <sub>OUT</sub>    | External capacitance to GND on OUT pins                | Limit set by DC-diagnostic timing                    |     | 1    | 3.3  | μF   |

| Lo                  | Output filter inductance at 2.1MHz                     | Minimum inductance at I <sub>SD</sub> current levels | 1   |      |      | μH   |

## 8.4 Thermal Information

|                      |                                              | TAS6421-Q1 <sup>(2)</sup> |      |

|----------------------|----------------------------------------------|---------------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DKQ (HSSOP)               |      |

|                      |                                              | 56 PINS                   | UNIT |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 42.8                      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.9                       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 21.2                      | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.5                       | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 20.2                      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | -                         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC Standard 4 Layer PCB.

## 8.5 Electrical Characteristics

|                        | PARAMETER                                     | TEST CONDITIONS                                                                                                | MIN  | TYP   | MAX  | UNIT  |

|------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| OPERATING              | CURRENT                                       |                                                                                                                |      |       |      |       |

| I <sub>PVDD_IDLE</sub> | PVDD idle current                             | Channel playing, no audio input                                                                                |      | 17    | 23   | mA    |

| I <sub>VBAT_IDLE</sub> | VBAT idle current                             | Channel playing, no audio input                                                                                |      | 28    | 32   | mA    |

| I <sub>PVDD_STBY</sub> | PVDD standby current                          | STANDBY Active, VDD = 0 V                                                                                      |      | 0.5   | 1    | μΑ    |

| I <sub>VBAT_STBY</sub> | VBAT standby current                          | STANDBY Active, VDD = 0 V                                                                                      |      | 4     | 6    | μΑ    |

| $I_{VDD}$              | VDD supply current                            | Channel playing, –60-dB signal                                                                                 |      | 15    | 18   | mA    |

| OUTPUT POV             | WER                                           |                                                                                                                |      |       |      |       |

|                        |                                               | 4 Ω, PVDD = 14.4 V, THD+N = 1%, TC = 75°C                                                                      | 20   | 22    |      |       |

|                        |                                               | 4 $\Omega$ , PVDD = 14.4 V, THD+N = 10%, TC = 75°C                                                             | 25   | 27    |      |       |

| D                      | Output november should BTI                    | 2 Ω, PVDD = 14.4 V, THD+N = 1%, TC = 75°C                                                                      | 38   | 40    |      | 147   |

| $P_{O\_BTL}$           | Output power per channel, BTL                 | 2 Ω, PVDD = 14.4 V, THD+N = 10%, TC = 75°C                                                                     | 42   | 45    |      | W     |

|                        |                                               | 4 Ω, PVDD = 25 V, THD+N = 1%, TC = 75°C                                                                        | 50   | 55    |      |       |

|                        |                                               | 4 Ω, PVDD = 25 V, THD+N = 10%, TC = 75°C                                                                       | 70   | 75    |      |       |

| EFF <sub>P</sub>       | Power efficiency                              | 1 channel operating at 25-W output power, 4 $\Omega$ load, PVDD = 14.4 V, TC = 25°C, including inductor losses |      | 86%   |      |       |

| AUDIO PERF             | ORMANCE                                       |                                                                                                                |      |       |      |       |

|                        | Output noise voltage                          | Zero input, A-weighting, gain level 1, PVDD = 14.4 V                                                           |      | 42    |      |       |

| M                      |                                               | Zero input, A-weighting, gain level 2, PVDD = 14.4 V                                                           |      | 55    |      |       |

| V <sub>n</sub>         |                                               | Zero input, A-weighting, gain level 3, PVDD = 18 V                                                             |      | 67    |      | μV    |

|                        |                                               | Zero input, A-weighting, gain level 4, PVDD = 25 V                                                             |      | 85    |      |       |

|                        |                                               | gain level 1, Register 0x01, bit 1-0 = 00                                                                      |      | 7.5   |      |       |

| CAIN                   | Dools Output Valtage /dDEC                    | gain level 2, Register 0x01, bit 1-0 = 01                                                                      |      | 15    |      | \//EC |

| GAIN                   | Peak Output Voltage/dBFS                      | gain level 3, Register 0x01, bit 1-0 = 10                                                                      |      | 21    |      | V/FS  |

|                        |                                               | gain level 4, Register 0x01, bit 1-0 = 11                                                                      |      | 29    |      |       |

| PSRR                   | Power-supply rejection ratio                  | PVDD = 14.4 Vdc + 1 V <sub>RMS</sub> , f = 1 kHz                                                               |      | 75    |      | dB    |

| THD+N                  | Total harmonic distortion + noise             |                                                                                                                |      | 0.02% |      |       |

| LINE OUTPU             | T PERFORMANCE                                 |                                                                                                                |      |       | •    |       |

| V <sub>n_LINEOUT</sub> | LINE output noise voltage                     | Zero input, A-weighting, channel set to LINE MODE                                                              |      | 42    |      | μV    |

| V <sub>O_LINEOUT</sub> | LINE output voltage                           | 0dB input, channel set to LINE MODE                                                                            |      | 5.5   |      | VRMS  |

| THD+N                  | Line output total harmonic distortion + noise | V <sub>O</sub> = 2 V <sub>RMS</sub> , channel set to LINE MODE                                                 |      | 0.01% |      |       |

| DIGITAL INP            | UT PINS                                       |                                                                                                                |      |       |      |       |

| V <sub>IH</sub>        | Input logic level high                        |                                                                                                                | 70   |       |      | %VDD  |

| V <sub>IL</sub>        | Input logic level low                         |                                                                                                                |      |       | 30   | %VDD  |

| I <sub>IH</sub>        | Input logic current, high                     | $V_1 = VDD$                                                                                                    |      |       | 15   | μA    |

| I <sub>IL</sub>        | Input logic current, low                      | $V_1 = 0$                                                                                                      |      |       | -15  | μΑ    |

| PWM OUTPU              | T STAGE                                       |                                                                                                                |      |       |      |       |

| R <sub>DS(on)</sub>    | FET drain-to-source resistance                | Not including bond wire and package resistance                                                                 |      | 90    |      | mΩ    |

| OVERVOLTA              | GE (OV) PROTECTION                            |                                                                                                                |      |       |      |       |

| $V_{PVDD\_OV}$         | PVDD overvoltage shutdown                     |                                                                                                                | 27.0 | 27.8  | 28.8 | V     |

## **Electrical Characteristics (continued)**

|                            | PARAMETER                                  | TEST CONDITIONS                                            | MIN | TYP  | MAX | UNIT     |

|----------------------------|--------------------------------------------|------------------------------------------------------------|-----|------|-----|----------|

| V <sub>PVDD_OV_HYS</sub>   | PVDD overvoltage shutdown hysteresis       |                                                            |     | 0.8  |     | V        |

| $V_{VBAT\_OV}$             | VBAT overvoltage shutdown                  |                                                            | 20  | 21.5 | 23  | V        |

| V <sub>VBAT_OV_HYS</sub>   | VBAT overvoltage shutdown hysteresis       |                                                            |     | 0.6  |     | V        |

| UNDERVOLTA                 | GE (UV) PROTECTION                         |                                                            |     |      |     |          |

| $VBAT_{UV}$                | VBAT undervoltage shutdown                 |                                                            |     | 4    | 4.5 | V        |

| VBAT <sub>UV_HYS</sub>     | VBAT undervoltage shutdown hysteresis      |                                                            |     | 0.2  |     | V        |

| $PVDD_{UV}$                | PVDD undervoltage shutdown                 |                                                            |     | 4    | 4.5 | V        |

| PVDD <sub>UV_HYS</sub>     | PVDD undervoltage shutdown hysteresis      |                                                            |     | 0.2  |     | V        |

| BYPASS VOLT                | AGES                                       |                                                            |     |      |     | •        |

| V <sub>GVDD</sub>          | Gate drive bypass pin voltage              |                                                            |     | 7    |     | V        |

| V <sub>AVDD</sub>          | Analog bypass pin voltage                  |                                                            |     | 6    |     | V        |

| $V_{VCOM}$                 | Common bypass pin voltage                  |                                                            |     | 2.5  |     | V        |

| V <sub>VREG</sub>          | Regulator bypass pin voltage               |                                                            |     | 5.5  |     | V        |

| POWER-ON RE                |                                            |                                                            | I.  |      |     |          |

| V <sub>POR</sub>           | VDD voltage for POR                        |                                                            |     | 2.1  | 2.7 | V        |

| V <sub>POR_HYS</sub>       | VDD POR recovery hysteresis voltage        |                                                            |     | 0.5  |     | V        |

|                            | ATURE (OT) PROTECTION                      |                                                            |     |      |     | -        |

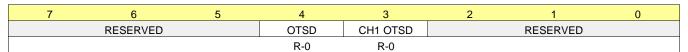

| OTW <sub>(i)</sub>         | Channel overtemperature warning            |                                                            |     | 150  |     | °C       |

| OTSD <sub>(i)</sub>        | Channel overtemperature shutdown           |                                                            |     | 175  |     | °C       |

|                            | Global junction overtemperature            |                                                            |     | 173  |     | _        |

| OTW                        | warning                                    |                                                            |     | 130  |     | °C       |

| OTSD                       | Global junction overtemperature shutdown   |                                                            |     | 160  |     | °C       |

| OT <sub>HYS</sub>          | Overtemperature hysteresis                 |                                                            |     | 15   |     | °C       |

| LOAD OVERC                 | URRENT PROTECTION                          |                                                            | ı   |      |     | I        |

| I <sub>LIM</sub>           | Overcurrent cycle-by-cycle limit           | OC Level 1                                                 | 4.0 | 4.8  |     | Α        |

| LIM                        | Overountent by old by by old innit         | OC Level 2                                                 | 6.0 | 6.5  |     | Α        |

| l                          | Overcurrent shutdown                       | OC Level 1, Any short to supply, ground, or other channels |     | 7    |     | Α        |

| I <sub>SD</sub>            | Overcurrent shutdown                       | OC Level 2, Any short to supply, ground, or other channels |     | 9    |     | Α        |

| MUTE MODE                  |                                            |                                                            |     |      |     |          |

| G <sub>MUTE</sub>          | Output attenuation                         |                                                            |     | 100  |     | dB       |

| CLICK AND PO               | )P                                         |                                                            |     |      |     |          |

| V <sub>CP</sub>            | Output click and pop voltage               | ITU-R 2k filter, High-Z/MUTE to Play, Play to Mute/High-Z  |     | 7    |     | mV       |

| DC OFFSET                  |                                            |                                                            | !   |      |     |          |

| V <sub>OFFSET</sub>        | Output offset voltage                      |                                                            |     | 2    | 5   | mV       |

| DC DETECT                  |                                            |                                                            |     |      |     |          |

| DC <sub>FAULT</sub>        | Output DC fault protection                 |                                                            |     | 2    | 2.5 | V        |

| DIGITAL OUTP               | ' '                                        | 1                                                          | 1   |      |     | <u> </u> |

| V <sub>OH</sub>            | Output voltage for logic level high        | I = ±2 mA                                                  | 90  |      |     | %VDD     |

| V <sub>OL</sub>            | Output voltage for logic level low         | I = ±2 mA                                                  |     |      | 10  | %VDD     |

| t <sub>DELAY_CLIPDET</sub> | Signal delay when output clipping detected |                                                            |     |      | 20  | μs       |

## **Electrical Characteristics (continued)**

|                           | PARAMETER                                              | TEST CONDITIONS                                                 | MIN | TYP | MAX  | UNIT |

|---------------------------|--------------------------------------------------------|-----------------------------------------------------------------|-----|-----|------|------|

| LOAD DIAGN                | OSTICS                                                 |                                                                 |     |     |      |      |

| S2P                       | Resistance to detect a short from OUT pin(s) to PVDD   |                                                                 |     |     | 500  | Ω    |

| S2G                       | Resistance to detect a short from OUT pin(s) to ground |                                                                 |     |     | 200  | Ω    |

| SL                        | Shorted load detection tolerance                       |                                                                 |     |     | ±0.5 | Ω    |

| OL                        | Open load                                              |                                                                 | 40  | 70  |      | Ω    |

| T <sub>DC_DIAG</sub>      | DC diagnostic time                                     |                                                                 |     | 100 |      | ms   |

| LO                        | Line output diagnostic detection                       |                                                                 |     |     | 6    | kΩ   |

| T <sub>LINE_DIAG</sub>    | Line output diagnostic time                            | Not including the preceeding DC_DIAG time                       |     | 40  |      | ms   |

| AC <sub>IMP</sub>         | AC impedance accuracy                                  | Gain linearity, $f$ = 19 kHz, $R_L$ = 2 $\Omega$ to 16 $\Omega$ |     |     | 25%  | ·    |

| AC <sub>IMP</sub>         | AC impedance accuracy                                  | Offset                                                          |     |     | ±0.5 | Ω    |

| T <sub>AC_DIAG</sub>      | AC diagnostic time                                     |                                                                 |     | 170 |      | ms   |

| I <sup>2</sup> C_ADDR PII | NS                                                     |                                                                 | *   |     |      |      |

| t <sub>I2C_ADDR</sub>     | Time delay needed for I <sup>2</sup> C address set-up  |                                                                 |     | 300 |      | μs   |

## **Electrical Characteristics (continued)**

|                                       | PARAMETER                                              | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------|----------------------------|-----|-----|-----|------|

| I <sup>2</sup> C CONTROL              | PORT                                                   |                            | ·   |     |     |      |

| t <sub>BUS</sub>                      | Bus free time between a STOP and START condition       |                            | 1.3 |     |     | μs   |

| t <sub>h1</sub>                       | Hold time, SCL to SDA                                  |                            | 0   |     |     | ns   |

| t <sub>h2</sub>                       | Hold time, start condition to SCL                      |                            | 0.6 |     |     | μs   |

| t <sub>START</sub>                    | I <sup>2</sup> C startup time after VDD power on reset |                            |     |     | 12  | ms   |

| t <sub>RISE</sub>                     | Rise time, SCL and SDA                                 |                            |     |     | 300 | ns   |

| t <sub>FALL</sub>                     | Fall time, SCL and SDA                                 |                            |     |     | 300 | ns   |

| t <sub>SU1</sub>                      | Setup, SDA to SCL                                      |                            | 100 |     |     | ns   |

| t <sub>SU2</sub>                      | Setup, SCL to start condition                          |                            | 0.6 |     |     | μs   |

| t <sub>SU3</sub>                      | Setup, SCL to stop condition                           |                            | 0.6 |     |     | μs   |

| $t_{W(H)}$                            | Required pulse duration SCL High                       |                            | 0.6 |     |     | μs   |

| $t_{W(L)}$                            | Required pulse duration SCL Low                        |                            | 1.3 |     |     | μs   |

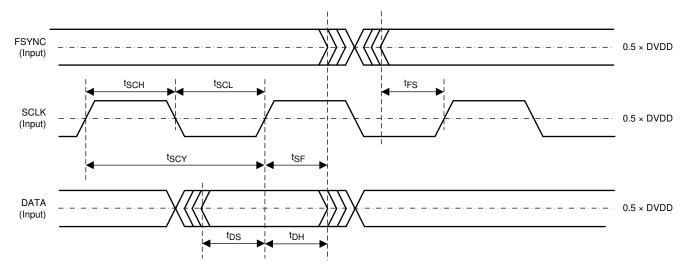

| SERIAL AUDIO                          | PORT                                                   |                            | ·   |     |     |      |

| D <sub>MCLK</sub> , D <sub>SCLK</sub> | Allowable input clock duty cycle                       |                            | 45% | 50% | 55% |      |

| f <sub>MCLK</sub>                     | Supported MCLK frequencies                             | 128, 256, or 512           | 128 |     | 512 | xFS  |

| f <sub>MCLK_Max</sub>                 | Maximum frequency                                      |                            |     |     | 25  | MHz  |

| t <sub>SCY</sub>                      | SCLK pulse cycle time                                  |                            | 40  |     |     | ns   |

| t <sub>SCL</sub>                      | SCLK pulse-with LOW                                    |                            | 16  |     |     | ns   |

| t <sub>SCH</sub>                      | SCLK pulse-with HIGH                                   |                            | 16  |     |     | ns   |

| t <sub>RISE/FALL</sub>                | Rise and fall time                                     |                            |     | <5  |     | ns   |

| t <sub>SF</sub>                       | SCLK rising edge to FSYNC edge                         |                            | 8   |     |     | ns   |

| t <sub>FS</sub>                       | FSYNC rising edge to SCLK edge                         |                            | 8   |     |     | ns   |

| t <sub>DS</sub>                       | DATA set-up time                                       |                            | 8   |     |     | ns   |

| t <sub>DH</sub>                       | DATA hold time                                         |                            | 8   |     |     | ns   |

| Ci                                    | Input capacitance, pins MCLK, SCLK, FSYNC, SDIN1       |                            |     |     | 10  | pf   |

| т                                     | Latency from input to output measured                  | FSYNC = 44.1 kHz or 48 kHz |     |     | 30  |      |

| $T_{LA}$                              | in FSYNC sample count                                  | FSYNC = 96 kHz             |     |     | 12  |      |

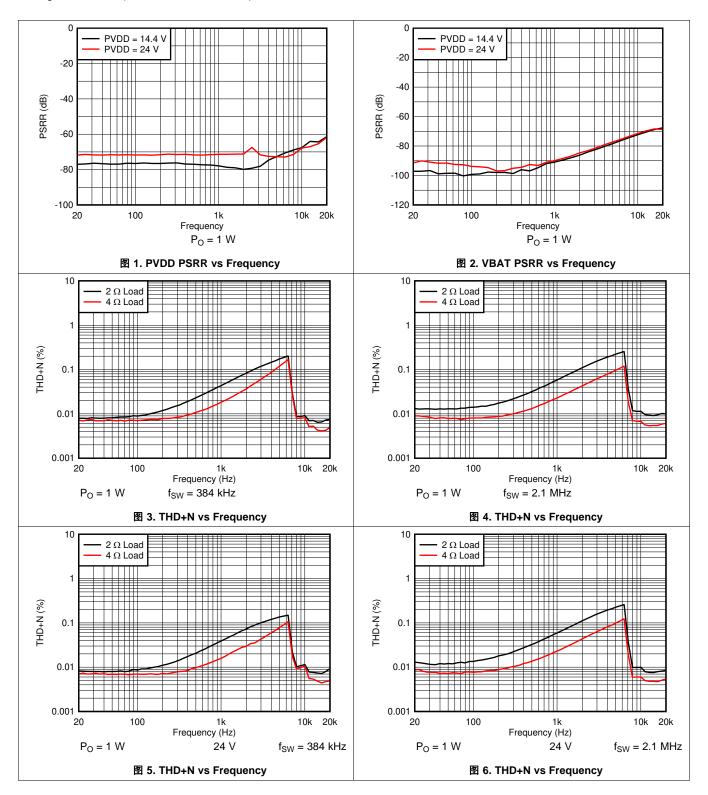

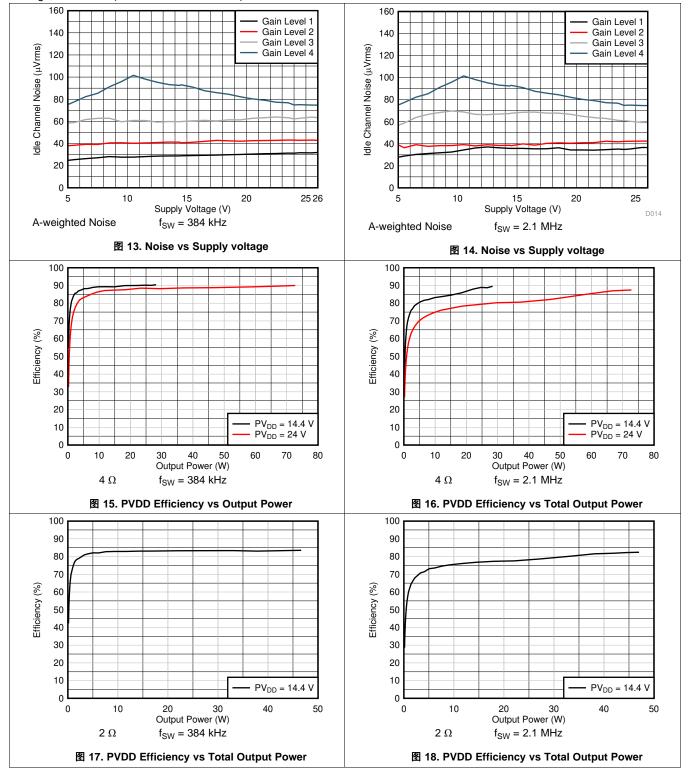

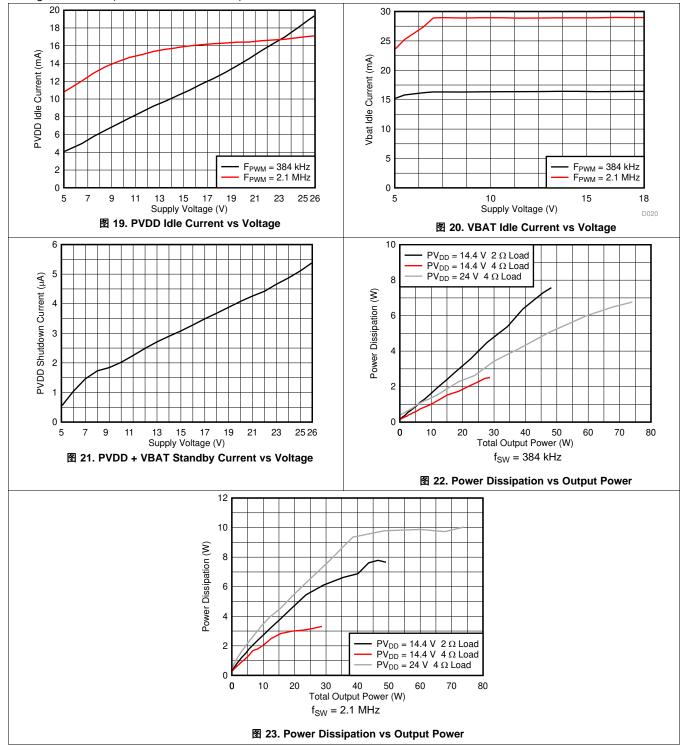

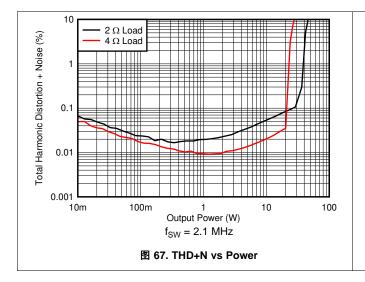

#### 8.6 Typical Characteristics

$T_A = 25$  °C,  $V_{VDD} = 3.3$  V, VBAT = PVDD = 14.4 V,  $R_L = 4$   $\Omega$ ,  $f_{IN} = 1$  kHz,  $f_s = 48$  kHz,  $f_{SW} = 2.1$  MHz, AES17 filter, default I<sup>2</sup>C settings, see 8 66 (unless otherwise noted)

## TEXAS INSTRUMENTS

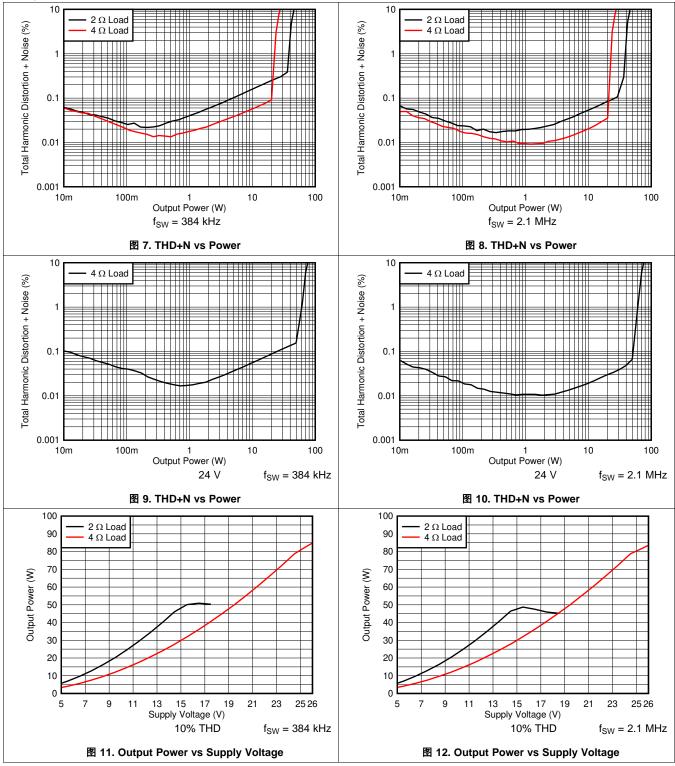

## Typical Characteristics (接下页)

$T_A$  = 25  $^{o}$ C,  $V_{VDD}$  = 3.3 V, VBAT = PVDD = 14.4 V,  $R_L$  = 4  $\Omega$ ,  $f_{IN}$  = 1 kHz,  $f_s$  = 48 kHz,  $f_{SW}$  = 2.1 MHz, AES17 filter, default I $^2$ C settings, see 2 66 (unless otherwise noted)

## Typical Characteristics (接下页)

$T_A = 25$  °C,  $V_{VDD} = 3.3$  V, VBAT = PVDD = 14.4 V,  $R_L = 4$   $\Omega$ ,  $f_{IN} = 1$  kHz,  $f_s = 48$  kHz,  $f_{SW} = 2.1$  MHz, AES17 filter, default  $I^2$ C settings, see 8 66 (unless otherwise noted)

## Typical Characteristics (接下页)

$T_A = 25$  °C,  $V_{VDD} = 3.3$  V, VBAT = PVDD = 14.4 V,  $R_L = 4$   $\Omega$ ,  $f_{IN} = 1$  kHz,  $f_s = 48$  kHz,  $f_{SW} = 2.1$  MHz, AES17 filter, default I<sup>2</sup>C settings, see 8 66 (unless otherwise noted)

## 9 Parameter Measurement Information

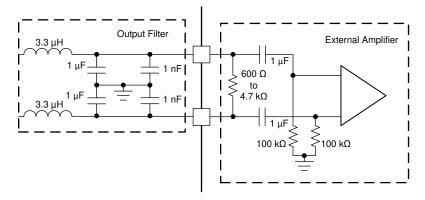

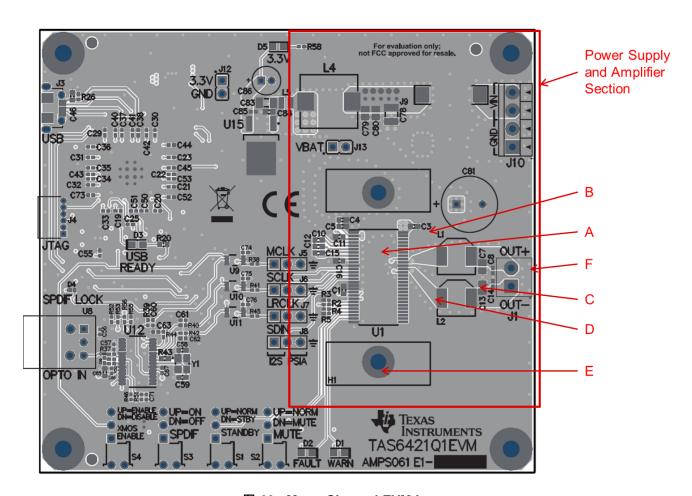

The parameters for the TAS6421-Q1 device were measured using the circuit in ₹ 66.

For measurements with 2.1 MHz switching frequency the 3.3 µH inductor from the TAS6421-Q1 EVM is used.

## 10 Detailed description

#### 10.1 Overview

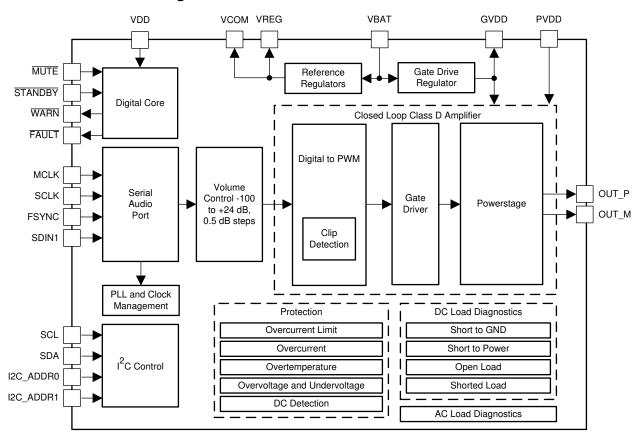

The TAS6421-Q1 device is a single-channel digital-input Class-D audio amplifier specifically tailored for use in the automotive industry. The device is designed for vehicle battery operation or boosted voltage systems. This efficient Class-D technology allows for reduced power consumption, reduced PCB area and reduced heat. The device realizes an audio sound-system design with smaller size and lower weight than traditional Class-AB solutions.

The core design blocks are as follows:

- Serial audio port

- Clock management

- High-pass filter and volume control

- Pulse width modulator (PWM) with output stage feedback

- · Gate drive

- Power FETs

- Diagnostics

- Protection

- Power supply

- I<sup>2</sup>C serial communication bus

## 10.2 Functional Block Diagram

#### 10.3 Feature Description

#### 10.3.1 Serial Audio Port

The serial audio port (SAP) receives audio in either I<sup>2</sup>S, left justified, right justified, or TDM formats.

Settings for the serial audio port are programmed in the SAP Control (Serial Audio-Port Control) Register (address = 0x03) [default = 0x04] and Miscellaneous Control 3 Register (address = 0x21) [default = 0x00].

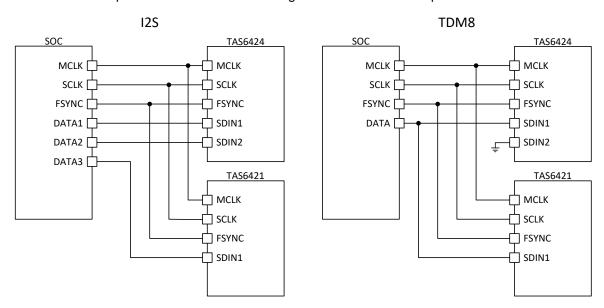

₹ 24 shows the digital audio data connections for I<sup>2</sup>S and TDM8 mode for a five channel system using TAS6424 four-channel Class-D amplifier and a TAS6421-Q1 single-channel Class-D amplifier.

图 24. Digital-Audio Data Connection

#### 10.3.1.1 PS Mode

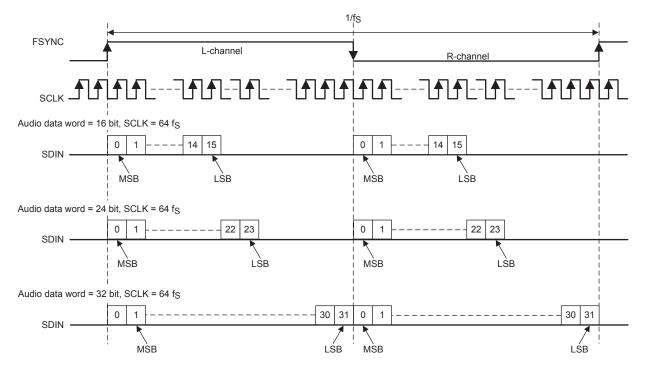

$I^2S$  timing uses the FSYNC pin to define when the data being transmitted is for the left channel and when the data is for the right channel. The FSYNC pin is low for the left channel and high for the right channel. The bit clock, SCLK, runs at 32 ×  $f_S$  or 64 ×  $f_S$  and is used to clock in the data. A delay of one bit clock occurs from the time the FSYNC signal changes state to the first bit of data on the data lines. The data is presented in 2s-complement form (MSB-first). The data is valid on the rising edge of the bit clock and is used to clock in the data.

The SAP Control Register Bits 3-5 allows to select if I<sup>2</sup>S Channel 1 or Channel 2 is amplified.

#### 10.3.1.2 Left-Justified Timing

Left-justified (LJ) timing also uses the FSYNC pin to define when the data being transmitted is for the left channel and when the data is for the right channel. The FSYNC pin is high for the left channel and low for the right channel. A bit clock running at  $32 \times f_S$  or  $64 \times f_S$  is used to clock in the data. The first bit of data appears on the data lines at the same time FSYNC toggles. The data is written MSB-first and is valid on the rising edge of the bit clock. Digital words can be 16-bits or 24-bits wide and pad any unused trailing data-bit positions in the left-right (L/R) frame with zeros.

#### 10.3.1.3 Right-Justified Timing

Right-justified (RJ) timing also uses the FSYNC pin to define when the data being transmitted is for the left channel and when the data is for the right channel. The FSYNC pin is high for the left channel and low for the right channel. A bit clock running at  $32 \times f_S$  or  $64 \times f_S$  is used to clock in the data. The first bit of data appears on the data 8-bit clock periods (for 24-bit data) after the FSYNC pin toggles. In RJ mode the LSB of data is always clocked by the last bit clock before the FSYNC pin transitions. The data is written MSB-first and is valid on the rising edge of bit clock. The device pads the unused leading data-bit positions in the L/R frame with zeros.

## Feature Description (接下页)

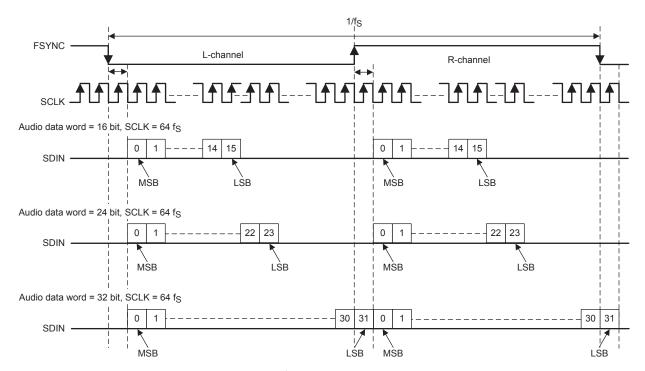

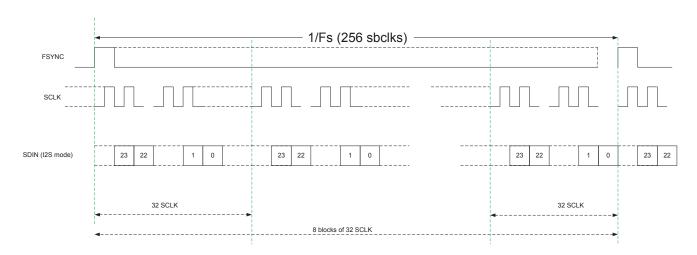

#### 10.3.1.4 TDM Mode

TDM mode supports 4 or 8 channels of audio data. The TDM mode is automatically selected when the TDM clocks are present. The device can be configured through I<sup>2</sup>C to select which TDM channel slot is amplified. The TDM mode supports 16-bit, 24-bit, and 32-bit input data lengths.

In TDM mode, SCLK must be 128 x  $f_s$  or 256 x  $f_s$ , depending on the TDM slot size. In TDM mode SCLK and MCLK can be connected together. If SCLK and MCLK are connected together or the frequency of SCLK and MCLK is equal, FSYNC should be minimum 2 MCLK pulses long.

In TDM mode, the SDIN1 pin (pin 15) is used for digital audio data. 表 1 lists register settings for the TDM channel selection.

**REGISTER SETTING AMPLIFIED CHANNEL** 0x03 0x03 0x03 BIT 5 BIT 4 BIT 3 0 0 0 Slot 1 in TDM8/4 or Left Channel in I<sup>2</sup>S mode Slot 2 in TDM8/4 or Right Channel in I<sup>2</sup>S mode 0 0 1 0 1 0 Slot 3 in TDM8/4 Slot 4 in TDM8/4 0 1 1 0 0 Slot 5 in TDM8 1 0 1 Slot 6 in TDM8 1 1 0 Slot 7 in TDM8 Slot 8 in TDM8

表 1. Channel Selection

#### 10.3.1.5 Supported Clock Rates

The device supports MCLK rates of 128  $\times$  f<sub>S</sub>, 256  $\times$  f<sub>S</sub>, or 512  $\times$  f<sub>S</sub>.

The device supports SCLK rates of 32  $\times$  f<sub>S</sub> or 64  $\times$  f<sub>S</sub> in I<sup>2</sup>S, LJ or RJ modes or 128  $\times$  f<sub>S</sub>, or 256  $\times$  f<sub>S</sub> in TDM mode.

The device supports FSYNC rates of 44.1 kHz, 48 kHz, or 96 kHz.

The maximum clock frequency is 25 MHz. Therefore, for a 96 kHz FSYNC rate, the maximum MCLK rate is  $256 \times f_S$ .

Duty cycle of 50% is required for 128x FSYNC, for 256x and 512x 50% duty cycle is not required.

#### 10.3.1.6 Audio-Clock Error Handling

When any kind of clock error, MCLK-FSYNC or SCLK-FSYNC ratio, or clock halt is detected, the device puts all channels into the Hi-Z state. When all audio clocks are within the expected range, the device automatically returns to the state it was in. See the *Electrical Characteristics* table for timing requirements.

图 25. Serial Audio Timing

图 26. Left-Justified Audio Data Format

图 27. I<sup>2</sup>S Audio Data Format

Audio Data Format: TDM8 mode

图 28. TDM8 Audio Data Format

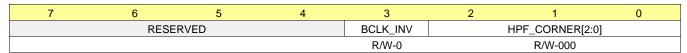

#### 10.3.2 DC Blocking

Direct-current (DC) content in the audio signal can damage speakers. The data path has a high-pass filter to remove any DC from the input signal. The corner frequency is selectable from 4 Hz, 8 Hz,15 Hz, 30 Hz and several more options up to 463 Hz with bits 0 through 2 in register 0x26. The default value of -3 dB is approximately 4 Hz for 44.1 kHz or 48 kHz and approximately 8 Hz for 96 kHz sampling rates.

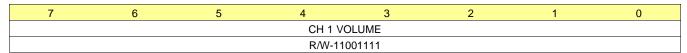

#### 10.3.3 Volume Control and Gain

The output channel has a digital-volume control with a range from -100 dB to +24 dB with 0.5-dB steps. The volume control is set through  $I^2C$ . The gain-ramp rate is programmable through  $I^2C$  to take one step every 1, 2, 4, or 8 FSYNC cycles.

The peak output-voltage swing is also configurable in the gain control register through I<sup>2</sup>C. The four full-scale voltage settings are 7.5 V, 15 V, 21 V, and 29 V. TI recommends selecting the lowest possible for the expected PVDD operation to optimize output noise and dynamic range performance.

#### 10.3.4 High-Frequency Pulse-Width Modulator (PWM)

The PWM converts the PCM input data into a switched signal of varying duty cycle. The PWM modulator is an advanced design with high bandwidth, low noise, low distortion, and excellent stability. The output switching rate is synchronous to the serial audio-clock input and is programmed through I²C to be between 8x and 48x the input-sample rate. The option to switch at high frequency allows the use of smaller and lower cost external filtering components. 表 2 lists the switch frequency options for bits 4 through 6 in the Miscellaneous Control 2 register (address 0x02).

|                   |                  | -       | •          | • •      |          |               |  |

|-------------------|------------------|---------|------------|----------|----------|---------------|--|

| INPUT SAMPLE RATE | BIT 6:4 SETTINGS |         |            |          |          |               |  |

|                   | 000              | 001     | 010 to 100 | 101      | 110      | 111           |  |

| 44.1 kHz          | 352.8 kHz        | 441 kHz | RESERVED   | 1.68 MHz | 1.94 MHz | 2.12 MHz      |  |

| 48 kHz            | 384 kHz          | 480 kHz | RESERVED   | 1.82 MHz | 2.11 MHz | Not supported |  |

| 96 kHz            | 384 kHz          | 480 kHz | RESERVED   | 1.82 MHz | 2.11 MHz | Not supported |  |

表 2. Output Switch Frequency Option

#### 10.3.5 Gate Drive

The gate driver accepts the low-voltage PWM signal and level shifts it to drive a high-current, full-bridge, power-FET stage. The device uses proprietary techniques to optimize EMI and audio performance.

The gate-driver power-supply voltage, GVDD, is internally generated and a decoupling capacitor is connected at pin 9.

The full H-bridge output stages use only NMOS transistors. Therefore, bootstrap capacitors are required for the proper operation of the high side NMOS transistors. A 1- $\mu$ F ceramic capacitor of quality X7R or better, rated for at least 16 V, must be connected from each output to the corresponding bootstrap input. The bootstrap capacitors connected between the BST pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high keeping the high-side MOSFETs turned on.

#### 10.3.6 Power FETs

The BTL output channel comprises four N-channel  $90\text{-m}\Omega$  FETs for high efficiency and maximum power transfer to the load. These FETs are designed to handle the fast switching frequency and large voltage transients during load dump.

#### 10.3.7 Load Diagnostics

The device incorporates both DC-load and AC-load diagnostics, which are used to determine the status of the load. The DC diagnostics are turned on by default, but if a fast startup without diagnostics is required, the DC diagnostics can be bypassed through I<sup>2</sup>C. The DC diagnostics run when the output channel is directed to leave the Hi-Z state and enter the MUTE or PLAY state. The DC diagnostics can also be enabled manually. DC Diagnostics can be started from any operating condition, but if the channel is in PLAY state, then the time to complete the diagnostic is longer because the device must ramp down the audio signal of that channel before transitioning to the Hi-Z state. The DC diagnostics are available as soon as the device supplies are within the recommended operating range. The DC diagnostics do not rely on the audio input clocks to be available to function. DC Diagnostic results are reported through I<sup>2</sup>C registers.

#### 10.3.7.1 DC Load Diagnostics

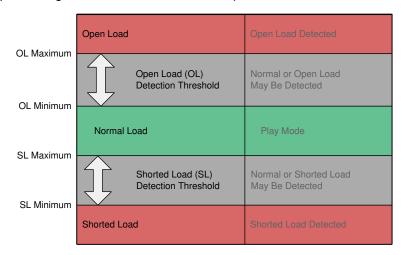

The DC load diagnostics are used to verify the load is connected. The DC diagnostics consists of four tests: short-to-power (S2P), short-to-ground (S2G), open-load (OL), and shorted-load (SL). The S2P and S2G tests trigger if the impedance to GND or a power rail is below that specified in the *Specifications* section. The diagnostic detects a short to vehicle battery, even when the supply is boosted. The SL test has an I<sup>2</sup>C-configurable threshold depending on the expected load to be connected. The OL test reports if the select channel has a load impedance greater than the limits in the *Specifications* section.

图 29. DC Load Diagnostic Reporting Thresholds

## 10.3.7.2 Line Output Diagnostics

The device also includes an optional test to detect a line-output load. A line-output load is a high-impedance load that is above the open-load (OL) threshold such that the DC-load diagnostics report an OL condition. After an OL condition is detected, if the line output detection bit is also set, the channel checks if a line-output load is present as well. This test is not pop free, so if an external amplifier is connected it should be muted.

#### 10.3.7.3 AC Load Diagnostics

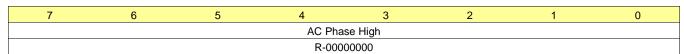

The AC load diagnostic is used to determine the proper connection of a capacitively-coupled speaker or tweeter when used with a passive crossover. The AC load diagnostic is controlled through I<sup>2</sup>C. The AC diagnostics requires an external input signal and reports the approximate load impedance and phase. The selected signal frequency should create current flow through the desired speaker for proper detection. The AC load-diagnostic test procedure is as follows.

#### 10.3.7.3.1 Impedance Magnitude Measurement

For load-impedance detection, use the following test procedure:

- 1. Set the output channel into the Hi-Z state.

- 2. Set the AC\_DIAGS\_LOOPBACK bit (bit 7 in register 0x16) to 0.

- 3. Apply a full-scale input signal from the DSP for the tested channel with the desired frequency (recommended 10 kHz to 20 kHz).

注

The device ramps the signal up and down automatically to prevent pops and clicks.

- 4. Set the device into the AC diagnostic mode (set bit 3 in register 0x15 to 1).

- 5. Read back the AC impedance (register 0x17).

When the test is complete, the channel reporting register indicates the status change from the AC diagnostic mode to the Hi-Z state. The detected impedance is stored in the appropriate I<sup>2</sup>C register.

The hexadecimal register value must be converted to decimal and used to calculate the impedance magnitude using 公式 1:

$$Channelx Impedance = \frac{Impedance \_CHx \times 2.371mV}{(Gain)(I \ mA)} \ (Ohms)$$

(1)

#### 10.3.7.3.2 Impedance Phase Reference Measurement

The first stage to determine the AC phase is to utilize the built-in loopback mode to determine the reference value for the phase measurement. This reference nullifies any phase offset in the device and measure only the phase of the load.

For loopback delay detection, use the following test procedure:

- 1. Set the AC\_DIAGS\_LOOPBACK bit (bit 7 in register 0x16) to 1 to enable AC loopback mode.

- 2. Apply a 0-dBFS 19 kHz signal and enable AC load diagnostics (set bit 3 in register 0x15 to 1).

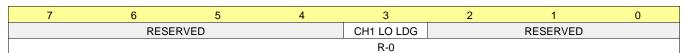

- 3. Read back the 16bit hexadecimal, AC\_LDG\_PHASE1 value. Register 0x1B holds the MSB and register 0x1C holds the LSB.

- 4. Set bit 3 in register 0x15 to 0.

When the test is complete, the channel reporting register indicates the status change from the AC diagnostic mode to the Hi-Z state. The detected impedance is stored in the appropriate I<sup>2</sup>C register.

#### 10.3.7.3.3 Impedance Phase Measurement

After performing the phase reference measurements, measure the phase of the speaker load. This is performed in the same manner as the reference measurements, except the loopback is disabled in register 0x16, bit 7.

For loopback delay detection, use the following test procedure:

- Set the AC\_DIAGS\_LOOPBACK bit (bit 7 in register 0x16) to 0 to disable AC loopback mode.

- 2. Apply a 0-dBFS 19 kHz signal and enable AC load diagnostics by setting bit 3 in register 0x15 to 1.

- 3. Read back the 16-bit hexadecimal, AC\_LDG\_PHASE1 value. Register 0x1B holds the MSB and register 0x1C holds the LSB.

- 4. Read back the hexadecimal stimulus value, STI. Register 0x1D holds the MSB and register 0x1E holds the LSB.

- 5. Set bit 3 in register 0x15 to 0.

When the test is complete, the channel reporting register indicates the status change from the AC diagnostic mode to the Hi-Z state. The detected impedance is stored in the appropriate I<sup>2</sup>C register.

The AC phase in degrees is calculated using 公式 2:

$$Phase\_CHx = 360(\frac{Phase\_CHx(LBK) - Phase\_CHx(LDM)}{STI\_CHx(LDM)})$$

(2)

Where:

- Phase\_CHx(LBK) is the reference phase measurement. LBK stands for loopback mode

- Phase\_CHx(LDM) is the phase measure of the load. LDM stands for load mode

- STI CHx(LDM) is the stimulus value

## 表 3. AC Impedance Code to Magnitude

| SETTING                           | GAIN AT 19 kHz | I(A)  | MEASUREMENT RANGE ( $\Omega$ ) | MAPPING FROM CODE TO MAGNITUDE (Ω/Code) |

|-----------------------------------|----------------|-------|--------------------------------|-----------------------------------------|

| Gain = 4, I = 10 mA (recommended) | 4.28           | 0.01  | 12                             | 0.05832                                 |

| Gain = 4, I = 19 mA               | 4.28           | 0.019 | 6                              | 0.0307                                  |

| Gain = 1, I = 10 mA (recommended) | 1              | 0.01  | 48                             | 0.2496                                  |

| Gain = 1, I = 19 mA               | 1              | 0.019 | 24                             | 0.1314                                  |

#### 10.3.8 Protection and Monitoring

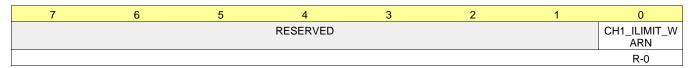

#### 10.3.8.1 Overcurrent Limit (I, IMIT)

The overcurrent limit terminates each PWM pulse to limit the output current flow when the current limit (I<sub>LIMIT</sub>) is exceeded. Power is limited, but operation continues without disruption and prevents undesired shutdown for transient music events. I<sub>LIMIT</sub> is not reported as fault condition to registers or the FAULT pin but as warning condition to the WARN pin and ILIMIT Status Register (address = 0x25) [default = 0x00]. The two programmable levels can be set by bit 4 in the Miscellaneous Control 1 register (address 0x01).

#### 10.3.8.2 Overcurrent Shutdown (I<sub>SD</sub>)

If the output load current reaches  $I_{SD}$ , such as an output short to GND, then a peak current limit occurs, which shuts down the channel. The time to shutdown the channel varies depending on the severity of the short condition. The channel is placed into the Hi-Z state, the fault is reported to the register, and the FAULT pin is asserted. The device remains in this state until the CLEAR FAULT bit is set in Miscellaneous Control 3 Register, 0x21 bit 7. After clearing this bit and if the diagnostics are enabled, the device automatically starts diagnostics on the channel and, if no load failure is found, the device restarts. If a load fault is found the device continues to rerun the diagnostics once per second. Because this hiccup mode uses the diagnostics, no high current is created. If the diagnostics are disabled, the device sets the state for the channel to Hi-Z and requires the MCU to take the appropriate action, setting the CLEAR FAULT bit after the fault was removed, in order to return to Play state. The two programmable levels can be set by bit 4 in the Miscellaneous Control 1 register (address 0x01).

#### 10.3.8.3 DC Detect

This circuit checks the DC offset continuously during normal operation at the output of the amplifier. If the DC offset exceeds the threshold, the channel is placed in the Hi-Z state, the fault is reported to the I<sup>2</sup>C register, and the FAULT pin is asserted. A register bit can be used to mask reporting to the FAULT pin if required.

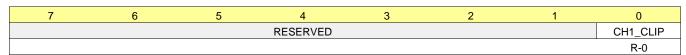

#### 10.3.8.4 Clip Detect

The Clip Detect is reported on the  $\overline{WARN}$  pin if 100% duty-cycle PWM is reached for a minimum number of PWM cycles set by the Clip Window Register (address = 0x23). The default is 20 PWM cycles. The Clip Detect is latched and can be cleared by I<sup>2</sup>C. Masking the clip reporting to the pin is possible through I<sup>2</sup>C. If desired, the Clip Detect can be configured to be non-latching through I<sup>2</sup>C. In non-latching mode, Clip Detect is reported when the PWM duty cycle reaches 100%, and deasserted once the PWM duty cycle falls below 100%.

#### 10.3.8.5 Global Overtemperature Warning (OTW), Overtemperature Shutdown (OTSD)

Four overtemperature warning levels are available in the device (see the *Register Maps* section for thresholds). When the junction temperature exceeds the warning level, the WARN pin is asserted, unless the mask bit has been set to disable reporting. The device functions until the OTSD value is reached, at which point the channels are placed in the Hi-Z state and the FAULT pin is asserted. By default, the device remains shut down after the temperature drops to normal levels. This configuration can be changed in bit 3 of the Miscellaneous Control 3 Register (address = 0x21) [default = 0x00] to auto-recovery: When the junction temperature returns to normal levels, the device automatically recovers and places the channel into the state indicated by the state control register. Note that even in auto-recovery configuration the FAULT pin remains asserted until the CLEAR FAULT bit (bit 7) is set in register 0x21.

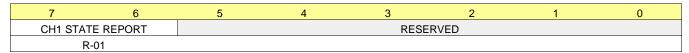

#### 10.3.8.6 Channel Overtemperature Warning [OTW(i)] and Shutdown [OTSD(i)]

In addition to the global OTW, the output channel also has an individual overtemperature warning and shutdown. If the channel exceeds the OTW(i) threshold, the warning register bit is set as the  $\overline{WARN}$  pin is asserted, unless the mask bit has been set to disable reporting. If the channel temperature exceeds the OTSD(i) threshold then the channel goes to the Hi-Z state and either remains there or auto-recovers to the state indicated by the state control register when the temperature drops below the OTW(i) threshold, depending on the setting of bit 3 of the Miscellaneous Control 3 Register (address = 0x21) [default = 0x00].

## 10.3.8.7 Undervoltage (UV) and Power-On-Reset (POR)

The undervoltage (UV) protection detects low voltages on the PVDD and VBAT pins. In the event of an UV condition, the FAULT pin is asserted, and the I<sup>2</sup>C register is updated. A power-on reset (POR) on the VDD pin causes the I<sup>2</sup>C to goes to the high-impedance (Hi-Z) state, and all registers are reset to default values. At power-on or after a POR event, the POR warning bit and WARN pin are asserted.

#### 10.3.8.8 Overvoltage (OV) and Load Dump

The overvoltage (OV) protection detects high voltages on the PVDD pin. If the PVDD pin reaches the OV threshold, the FAULT pin is asserted and the I<sup>2</sup>C register is updated. The device can withstand 40 V load-dump voltage spikes.

#### 10.3.9 Power Supply

The device has three power supply inputs, VDD, PVDD, and VBAT, which are described as follows:

**VDD** This pin is a 3.3V supply pin that provides power to the low voltage circuitry.

VBAT This pin is a higher voltage supply that can be connected to the vehicle battery or the regulated

voltage rail in a boosted system within the recommended limits. For best performance, this rail should be 10 V or higher. See the *Recommended Operating Conditions* table for the maximum supply voltage. This supply rail is used for higher voltage analog circuits but not the output EETs

supply voltage. This supply rail is used for higher voltage analog circuits but not the output FETs.

PVDD This pin is a high-voltage supply that can either be connected to the vehicle battery or to another voltage rail in a boosted system. The PVDD pin supplies the power to the output FETs and can be within the recommended operating limits, even if that is below the VBAT supply, to allow for

dynamic voltage systems.

Several on-chip regulators are included for generating the voltages necessary for the internal circuitry. The external pins are provided only for bypass capacitors to filter the supply and should not be used to power other circuits.

The device can withstand fortuitous open ground and power conditions within the absolute maximum ratings for the device. Fortuitous open ground usually occurs when a speaker wire is shorted to ground, allowing for a second ground path through the body diode in the output FETs.

### 10.3.9.1 Vehicle-Battery Power-Supply Sequence

The device can accept any sequence of the VBAT, PVDD and VDD supply.

#### 10.3.9.1.1 Power-Up Sequence

In a typical system, the VBAT and PVDD supplies are both connected to the vehicle battery and power up at the same time. The VDD supply should be applied after the VBAT and PVDD supplies are within the recommended operating range.

#### 10.3.9.1.2 Power-Down Sequence

To power-down the device, first set the STANDBY pin low for at least 15ms before removing PVDD, VBAT or VDD. After 15ms, the power supplies can be removed.

#### 10.3.9.2 Boosted Power-Supply Sequence

In this case, the VBAT and PVDD inputs are not connected to the same supply.

When powering up, apply the VBAT supply first, the VDD supply second, and the PVDD supply last.

When powering down, first set the STANDBY pin low for at least 15ms before removing PVDD, VBAT or VDD. After 15 ms, the power supplies can be removed.

#### 10.3.10 Hardware Control Pins

The device has four pins for control and device status: FAULT, MUTE, WARN, and STANDBY.

#### 10.3.10.1 FAULT

The FAULT pin reports faults and is active low under any of the following conditions:

- Channel faults (overcurrent or DC detection)

- · Overtemperature shutdown

- Overvoltage or undervoltage conditions on the VBAT or PVDD pins

- Clock errors

For all listed faults, the FAULT pin remains asserted after the fault condition is rectified. Deassert the FAULT pin by writing the CLEAR FAULT bit (bit 7) in register 0x21. The only exception is the fault report caused by Overtemperature shutdown, for which the FAULT pin deasserts automatically when the junction temperature returns to normal levels and the device automatically recovers.

The register reports for all fault reports remain asserted until they are cleared by writing the CLEAR FAULT bit (bit 7) in register 0x21.

Register bits are available to mask fault categories from reporting to the FAULT pin. These bits only mask the setting of the pin and do not affect the register reporting or protection of the device. By default all faults are reported to the pin. See the *Register Maps* section for a description of the mask settings.

This pin is an open-drain output with an internal 100 k $\Omega$  pull-up resistor to VDD.

#### 10.3.10.2 WARN

This active-low output pin reports audio clipping, overtemperature warnings, overcurrent limit warnings and POR events.

Clipping is reported if any channel is at the maximum modulation for 20 consecutive PWM clocks (default value) which results in a 10-µs delay to report the onset of clipping. Changing the number of required consecutive PWM clocks in the Clip Window Register (address = 0x23) impacts the report delay time. The Clip Detect warning bit is sticky in latching mode and can be cleared by the CLEAR FAULT bit (bit 7) in register 0x21.

An overtemperature warning (OTW) is reported if the general temperature or the channel temperature warnings are set. The warning temperature can be set through bits 5 and 6 in register 0x01.

Register bits are available to mask either clipping, OTW or I<sub>LIMIT</sub> reporting to the pin. These bits only mask the setting of the pin and do not affect the register reporting. By default clipping, I<sub>LIMIT</sub> and OTW are reported.

The WARN pin is latched and can be cleared by writing the CLEAR FAULT bit (bit 7) in register 0x21.

This pin is an open-drain output with an internal 100 k $\Omega$  pull-up resistor to VDD.

#### 10.3.10.3 MUTE

This active-low input pin is used for hardware control of the mute and unmute function.

This pin has a 100  $k\Omega$  internal pull-down resistor.

#### 10.3.10.4 STANDBY

When this active-low input pin is asserted, the device goes into shutdown and current draw is limited. This pin can be used to shut down the device rapidly. The outputs are ramped down in less than 5 ms if the device is not already in the Hi-Z state.

This pin has a 100 k $\Omega$  internal pull-down resistor.

#### 10.4 Device Functional Modes

## 10.4.1 Operating Modes and Faults

The operating modes and faults are listed in the following tables.

Global Faults affect the entire device while the effect and management of Channel Faults is limited to the Output Stage. Although the system effects of a Global Fault and a Channel Fault can be identical in a 1-channel device such as TAS6421-Q1, this split and naming convention was selected to remain compatible with the multi-channel TAS642x-Q1 family devices.

### 表 4. Operating Modes

| STATE NAME | OUTPUT FETS          | OSCILLATOR | I <sup>2</sup> C |

|------------|----------------------|------------|------------------|

| STANDBY    | Hi-Z                 | Stopped    | Active           |

| Hi-Z       | Hi-Z                 | Active     | Active           |

| MUTE       | Switching at 50%     | Active     | Active           |

| PLAY       | Switching with audio | Active     | Active           |

#### 表 5. Global Faults and Actions

| FAULT/<br>EVENT | FAULT/EVENT<br>CATEGORY | MONITORING<br>MODES | REPORTING<br>METHOD           | ACTION<br>RESULT |

|-----------------|-------------------------|---------------------|-------------------------------|------------------|

| POR             |                         | All                 | $I^2C + \overline{WARN}$ pin  | Standby          |

| VBAT UV         | Valtage foult           |                     |                               |                  |

| PVDD UV         | Voltage fault           | Hi-Z, mute, normal  | $I^2C + \overline{FAULT}$ pin | Hi-Z             |

| VBAT or PVDD OV |                         |                     |                               |                  |

| OTW             | Thermal warning         | Hi-Z, mute, normal  | I <sup>2</sup> C + WARN pin   | None             |

| OTSD            | Thermal shutdown        | Hi-Z, mute, normal  | I <sup>2</sup> C + FAULT pin  | Hi-Z             |

## 表 6. Channel Faults and Actions

| FAULT/<br>EVENT      | FAULT/EVENT<br>CATEGORY | MONITORING<br>MODES | REPORTING<br>METHOD                     | ACTION<br>TYPE |  |

|----------------------|-------------------------|---------------------|-----------------------------------------|----------------|--|

| Clipping             | Warning                 |                     | I <sup>2</sup> C + WARN or FAULT pin    | None           |  |

| Overcurrent limiting | Protection              | Mute and play       | I <sup>2</sup> C + WARN pin             | Current limit  |  |

| Overcurrent fault    | Output channel fault    | . ,                 | I <sup>2</sup> C + <del>FAULT</del> pin | Hi-Z           |  |

| DC detect            | Output channel lauit    |                     | I C + FAULT PIN                         | ΠΙ-Ζ           |  |

#### 10.5 Programming

#### 10.5.1 I<sup>2</sup>C Serial Communication Bus

The device communicates with the system processor through the I<sup>2</sup>C serial communication bus as an I<sup>2</sup>C slaveonly device. The processor can poll the device through I<sup>2</sup>C to determine the operating status, configure settings, or run diagnostics. For a complete list and description of all I<sup>2</sup>C controls, see the *Register Maps* section.

The device includes two  $I^2C$  address pins, so up to four devices can be used together in a system with no additional bus switching hardware. The  $I^2C$  ADDRx pins set the slave address of the device as listed in  $\frac{1}{8}$  7.

| J. 111 6 7 (44) 50000 |                        |                        |                        |                       |  |  |  |

|-----------------------|------------------------|------------------------|------------------------|-----------------------|--|--|--|

| DESCRIPTION           | I <sup>2</sup> C ADDR1 | I <sup>2</sup> C ADDR0 | I <sup>2</sup> C Write | I <sup>2</sup> C Read |  |  |  |

| Device 0              | 0                      | 0                      | 0xD4                   | 0xD5                  |  |  |  |

| Device 1              | 0                      | 1                      | 0xD6                   | 0xD7                  |  |  |  |

| Device 2              | 1                      | 0                      | 0xD8                   | 0xD9                  |  |  |  |

| Device 3              | 1                      | 1                      | 0xDA                   | 0xDB                  |  |  |  |

表 7. I<sup>2</sup>C Addresses

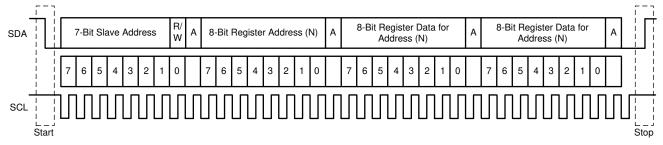

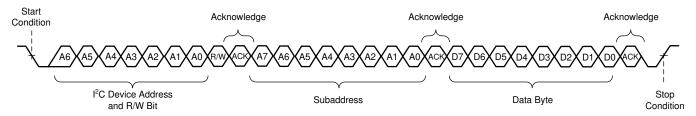

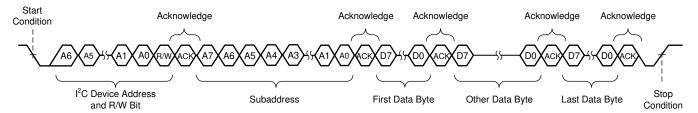

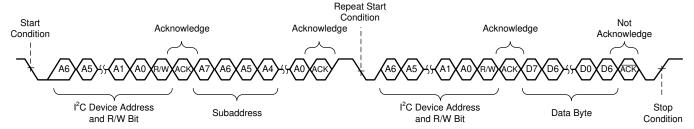

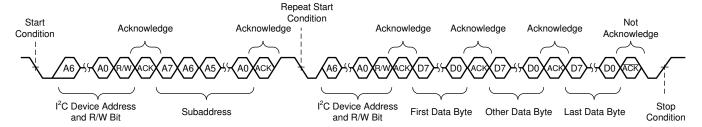

#### 10.5.2 I<sup>2</sup>C Bus Protocol

The device has a bidirectional serial-control interface that is compatible with the Inter IC (I<sup>2</sup>C) bus protocol and supports 100 kbps and 400 kbps data transfer rates for random and sequential write and read operations. The TAS6421-Q1 device is a slave-only device that does not support a multimaster bus environment or wait-state insertion. The control interface is used to program the registers of the device and to read device status.

The I<sup>2</sup>C bus uses two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially, one bit at a time. The address and data are transferred in byte (8bit) format with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is HIGH to indicate a start and stop conditions. A HIGH-to-LOW transition on SDA indicates a start, and a LOW-to-HIGH transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then wait for an acknowledge condition. The device holds SDA LOW during the acknowledge-clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus a R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pull-up resistor must be used for the SDA and SCL signals to set the HIGH level for the bus. The number of bytes that can be transmitted between start and stop conditions is unlimited. When the last word transfers, the master generates a stop condition to release the bus.