**SN74HCS08-Q1**

ZHCSJT4E - MAY 2019 - REVISED DECEMBER 2021

# SN74HCS08-Q1 具有施密特触发输入的汽车类四路 2 输入与门

## 1 特性

- 符合面向汽车应用的 AEC-Q100 标准:

- 器件温度等级 1:

- 40°C 至 +125°C, T<sub>A</sub>

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C6

- 宽工作电压范围: 2V 至 6V

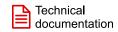

- 施密特触发输入可实现慢速或高噪声输入信号

- 低功耗

- I<sub>CC</sub> 典型值为 100nA

- 输入泄漏电流典型值为 ±100nA

- 电压为 6V 时,输出驱动为 ±7.8mA

## 2 应用

- 将电源正常信号相结合

- 将使能信号相结合

# 3 说明

此器件包含四个具有施密特触发输入的独立双输入与 门。每个逻辑门以正逻辑执行布尔函数  $Y = A \oplus B$ 。

#### 器件信息

| 器件型号            | 封装 <sup>(1)</sup> | 封装尺寸(标称值)        |  |  |

|-----------------|-------------------|------------------|--|--|

| SN74HCS08PW-Q1  | TSSOP (14)        | 5.00mm × 4.40mm  |  |  |

| SN74HCS08D-Q1   | SOIC (14)         | 9.90mm × 3.90mm  |  |  |

| SN74HCS08BQA-Q1 | WQFN (14)         | 3.00mm × 2.50mm  |  |  |

| SN74HCS08DYY-Q1 | SOT-23-THIN (14)  | 2.00mm × 4.20 mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

施密特触发输入的优势

## **Table of Contents**

| 1 特性                                 | 1              | 8.3 Feature Description                 | 8  |

|--------------------------------------|----------------|-----------------------------------------|----|

| 2 应用                                 |                | 8.4 Device Functional Modes             |    |

| 3 说明                                 |                | 9 Application and Implementation        | 10 |

| 4 Revision History                   |                | 9.1 Application Information             |    |

| 5 Pin Configuration and Functions    |                | 9.2 Typical Application                 |    |

| Pin Functions                        |                | 10 Power Supply Recommendations         | 13 |

| 6 Specifications                     |                | 11 Layout                               | 13 |

| 6.1 Absolute Maximum Ratings         |                | 11.1 Layout Guidelines                  | 13 |

| 6.2 ESD Ratings                      |                | 11.2 Layout Example                     | 13 |

| 6.3 Recommended Operating Conditions |                | 12 Device and Documentation Support     | 14 |

| 6.4 Thermal Information              |                | 12.1 Documentation Support              | 14 |

| 6.5 Electrical Characteristics       |                | 12.2 接收文档更新通知                           | 14 |

| 6.6 Switching Characteristics        |                | 12.3 支持资源                               | 14 |

| 6.7 Typical Characteristics          |                | 12.4 Trademarks                         | 14 |

| 7 Parameter Measurement Information  |                | 12.5 Electrostatic Discharge Caution    | 14 |

| 8 Detailed Description               |                | 12.6 术语表                                | 14 |

| 8.1 Overview                         |                | 13 Mechanical, Packaging, and Orderable |    |

| 8.2 Functional Block Diagram         | <mark>8</mark> | Information                             | 15 |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| Changes fr               | om Revision D (March 2021) to Revision E (December 2021)                                    | Page |

|--------------------------|---------------------------------------------------------------------------------------------|------|

| <ul><li>向器件信</li></ul>   | · 息表 中添加了 DYY 封装信息                                                                          |      |

|                          | YY package information to Pin Configuration and Functions                                   |      |

|                          | YY package to Thermal Information table                                                     |      |

| Changes fr               | om Revision C (September 2019) to Revision D (March 2021)                                   | Page |

| <ul> <li>更新了整</li> </ul> | 个文档中的表格、图和交叉参考的编号格式                                                                         | 1    |

| • 向器件信                   | F息添加了 BQA 封装信息                                                                              | 1    |

|                          | QA package information to Pin Configuration and Functions                                   |      |

|                          | QA package to <i>Thermal Information</i> table                                              |      |

| Changes fr               | om Revision B (August 2019) to Revision C (September 2019)                                  | Page |

| <ul><li>向器件信</li></ul>   | ·息表中添加了 D 封装                                                                                | 1    |

|                          | package column to Thermal Information table                                                 |      |

| Changes fr               | om Revision A (July 2019) to Revision B (August 2019)                                       | Page |

| • Deleted                | " $I_{CC}$ " and "output" from "Continuous current through $V_{CC}$ or GND" row for clarity | 4    |

| Changes fr               | om Revision * (May 2019) to Revision A (July 2019)                                          | Page |

| <ul><li>将"预告</li></ul>   | 信息"更改为"量产数据"                                                                                |      |

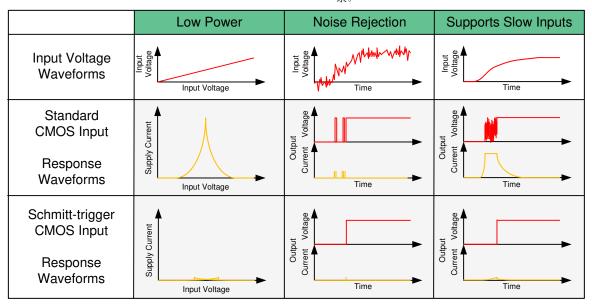

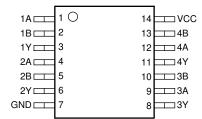

# **5 Pin Configuration and Functions**

D, PW, or DYY Package 14-Pin SOIC, TSSOP or SOT Top View

#### **Pin Functions**

| PIN                      |     | I/O    | DESCRIPTION                                                                                            |

|--------------------------|-----|--------|--------------------------------------------------------------------------------------------------------|

| NAME                     | NO. | _ I/O  | DESCRIPTION                                                                                            |

| 1A                       | 1   | Input  | Channel 1, Input A                                                                                     |

| 1B                       | 2   | Input  | Channel 1, Input B                                                                                     |

| 1Y                       | 3   | Output | Channel 1, Output Y                                                                                    |

| 2A                       | 4   | Input  | Channel 2, Input A                                                                                     |

| 2B                       | 5   | Input  | Channel 2, Input B                                                                                     |

| 2Y                       | 6   | Output | Channel 2, Output Y                                                                                    |

| GND                      | 7   | _      | Ground                                                                                                 |

| 3Y                       | 8   | Output | Channel 3, Output Y                                                                                    |

| 3A                       | 9   | Input  | Channel 3, Input A                                                                                     |

| 3B                       | 10  | Input  | Channel 3, Input B                                                                                     |

| 4Y                       | 11  | Output | Channel 4, Output Y                                                                                    |

| 4A                       | 12  | Input  | Channel 4, Input A                                                                                     |

| 4B                       | 13  | Input  | Channel 4, Input B                                                                                     |

| V <sub>CC</sub>          | 14  | _      | Positive Supply                                                                                        |

| Thermal Pad <sup>(</sup> | 1)  | _      | The thermal pad can be connected to GND or left floating. Do not connect to any other signal or supply |

### 1. BQA Package only.

## **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                   |                                                 | MIN  | MAX | UNIT |

|------------------|---------------------------------------------------|-------------------------------------------------|------|-----|------|

| V <sub>CC</sub>  | Supply voltage                                    | Supply voltage                                  |      |     |      |

| I <sub>IK</sub>  | Input clamp current <sup>(2)</sup>                | $V_1 < -0.5 \text{ or } V_1 > V_{CC} + 0.5$     |      | ±20 | mA   |

| I <sub>OK</sub>  | Output clamp current <sup>(2)</sup>               | $V_{O} < -0.5 \text{ or } V_{O} > V_{CC} + 0.5$ |      | ±20 | mA   |

| Io               | Continuous output current                         | $V_O = 0$ to $V_{CC}$                           |      | ±35 | mA   |

|                  | Continuous current through V <sub>CC</sub> or GND |                                                 |      | ±70 | mA   |

| TJ               | Junction temperature <sup>(3)</sup>               |                                                 | 150  | °C  |      |

| T <sub>stg</sub> | Storage temperature                               |                                                 | - 65 | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 6.2 ESD Ratings

|                                            |                                                                                           |                                                                              | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level 2 | ±4000                                                                        | V     |      |

|                                            |                                                                                           | Charged device model (CDM), per AEC Q100-011 CDM ESD Classification Level C6 | ±1500 | V    |

<sup>(1)</sup> AEC Q100-002 indicate that HBM stressing shall be in accordrance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                     | MIN  | NOM MAX         | UNIT |

|-----------------|-------------------------------------|------|-----------------|------|

| V <sub>CC</sub> | Supply voltage                      | 2    | 6               | V    |

| VI              | Input voltage                       | 0    | V <sub>CC</sub> | V    |

| Vo              | Output voltage                      | 0    | V <sub>CC</sub> | V    |

| ∆ t/ ∆ v        | Input transition rise and fall rate |      | Unlimited       | ns/V |

| T <sub>A</sub>  | Ambient temperature                 | - 40 | 125             | °C   |

Product Folder Links: SN74HCS08-Q1

<sup>(2)</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed. Do not exceed the absolute maximum voltage supply rating.

<sup>(3)</sup> Guaranteed by design.

### **6.4 Thermal Information**

|                           | THERMAL METRIC(1)                            | PW (TSSOP) | D (SOIC) | BQA (WQFN) | DYY (SOT) | UNIT |

|---------------------------|----------------------------------------------|------------|----------|------------|-----------|------|

|                           |                                              | 14 PINS    | 14 PINS  | 14 PINS    | 14 PINS   |      |

| R <sub>θ JA</sub>         | Junction-to-ambient thermal resistance       | 151.7      | 133.6    | 109.7      | 236.5     | °C/W |

| R <sub>θ</sub><br>JC(top) | Junction-to-case (top) thermal resistance    | 79.4       | 89.0     | 111.0      | 143.2     | °C/W |

| R <sub>θ JB</sub>         | Junction-to-board thermal resistance         | 94.7       | 89.5     | 77.9       | 146.0     | °C/W |

| ΨЈТ                       | Junction-to-top characterization parameter   | 25.2       | 45.5     | 20.2       | 29.5      | °C/W |

| ΨЈВ                       | Junction-to-board characterization parameter | 94.1       | 89.1     | 77.8       | 145.6     | °C/W |

| R <sub>θ</sub><br>JC(bot) | Junction-to-case (bottom) thermal resistance | N/A        | N/A      | 56.6       | N/A       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### **6.5 Electrical Characteristics**

over operating free-air temperature range; typical ratings measured at TA = 25°C (unless otherwise noted).

|                 | PARAMETER                                       | TEST CO                    | NDITIONS                  | V <sub>cc</sub> | MIN                   | TYP                     | MAX   | UNIT      |

|-----------------|-------------------------------------------------|----------------------------|---------------------------|-----------------|-----------------------|-------------------------|-------|-----------|

|                 |                                                 |                            |                           | 2 V             | 0.7                   |                         | 1.5   |           |

| V <sub>T+</sub> | Positive switching threshold                    |                            |                           | 4.5 V           | 1.7                   |                         | 3.15  | V         |

|                 |                                                 |                            |                           | 6 V             | 2.1                   |                         | 4.2   |           |

|                 |                                                 |                            |                           | 2 V             | 0.3                   |                         | 1.0   |           |

| V <sub>T-</sub> | Negative switching threshold                    |                            |                           | 4.5 V           | 0.9                   |                         | 2.2   | V         |

|                 |                                                 |                            |                           | 6 V             | 1.2                   |                         | 3.0   |           |

|                 |                                                 |                            |                           | 2 V             | 0.2                   |                         | 1.0   |           |

| ΔV <sub>T</sub> | Hysteresis (V <sub>T+</sub> - V <sub>T-</sub> ) |                            |                           | 4.5 V           | 0.4                   |                         | 1.4   | \ \ \ \ \ |

|                 |                                                 |                            |                           | 6 V             | 0.6                   |                         | 1.6   |           |

|                 |                                                 |                            | I <sub>OH</sub> = -20 μA  | 2 V to 6 V      | V <sub>CC</sub> - 0.1 | V <sub>CC</sub> - 0.002 |       |           |

| V <sub>OH</sub> | High-level output voltage                       | $V_I = V_{IH}$ or $V_{IL}$ | I <sub>OH</sub> = -6 mA   | 4.5 V           | 4                     | 4.3                     |       | V         |

|                 |                                                 |                            | I <sub>OH</sub> = -7.8 mA | 6 V             | 5.4                   | 5.75                    |       |           |

|                 |                                                 |                            | I <sub>OL</sub> = 20 μA   | 2 V to 6 V      |                       | 0.002                   | 0.1   |           |

| V <sub>OL</sub> | Low-level output voltage                        | $V_I = V_{IH}$ or $V_{IL}$ | I <sub>OL</sub> = 6 mA    | 4.5 V           |                       | 0.18                    | 0.30  | \ \ \     |

|                 |                                                 |                            | I <sub>OL</sub> = 7.8 mA  | 6 V             |                       | 0.22                    | 0.33  |           |

| II              | Input leakage current                           | $V_I = V_{CC}$ or 0        |                           | 6 V             |                       | ±100                    | ±1000 | nA        |

| I <sub>CC</sub> | Supply current                                  | $V_I = V_{CC}$ or 0, $I_C$ | ) = 0                     | 6 V             |                       | 0.1                     | 2     | μA        |

| Ci              | Input capacitance                               |                            |                           | 2 V to 6 V      |                       |                         | 5     | pF        |

| C <sub>pd</sub> | Power dissipation capacitance per gate          | No load                    |                           | 2 V to 6 V      |                       | 10                      |       | pF        |

### 6.6 Switching Characteristics

over operating free-air temperature range; typical ratings measured at TA = 25°C (unless otherwise noted). See the *Parameter Measurement Information*

|                               | PARAMETER                         | FROM (INPUT) | TO (OUTPUT) | V <sub>CC</sub> | MIN | TYP | MAX | UNIT |

|-------------------------------|-----------------------------------|--------------|-------------|-----------------|-----|-----|-----|------|

|                               | t <sub>pd</sub> Propagation delay |              |             | 2 V             |     | 14  | 36  |      |

| t <sub>pd</sub>               |                                   | A or B       |             | 4.5 V           |     | 7   | 13  | ns   |

|                               |                                   |              |             | 6 V             |     | 6   | 12  |      |

|                               |                                   |              | Y           | 2 V             |     | 9   | 17  |      |

| t <sub>t</sub> Transition-tir | Transition-time                   |              |             | 4.5 V           |     | 5   | 8   | ns   |

|                               |                                   |              |             | 6 V             |     | 4   | 7   |      |

### **6.7 Typical Characteristics**

$T_A = 25^{\circ}C$

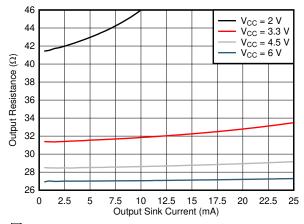

图 6-1. Output driver resistance in LOW state.

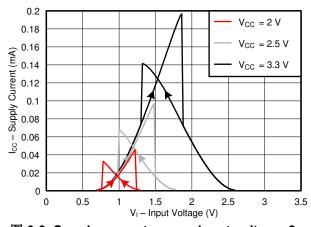

图 6-3. Supply current across input voltage, 2-, 2.5-, and 3.3-V supply

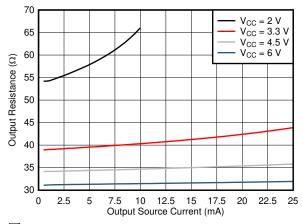

图 6-2. Output driver resistance in HIGH state.

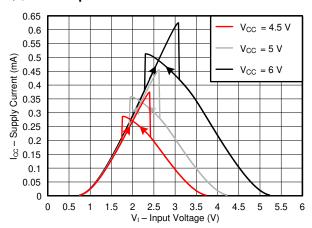

图 6-4. Supply current across input voltage, 4.5-, 5-, and 6-V supply

## 7 Parameter Measurement Information

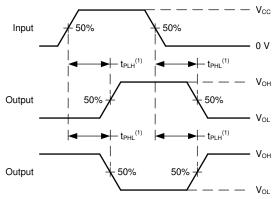

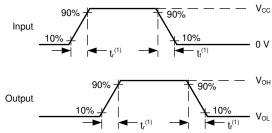

Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_O$  = 50  $\Omega$ ,  $t_t$  < 2.5 ns.

For clock inputs,  $f_{\text{max}}$  is measured when the input duty cycle is 50%.

The outputs are measured one at a time with one input transition per measurement.

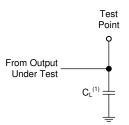

(1) C<sub>L</sub> includes probe and test-fixture capacitance.

#### 图 7-1. Load Circuit for Push-Pull Outputs

(1) The greater between  $t_{PLH}$  and  $t_{PHL}$  is the same as  $t_{pd}$ .

图 7-2. Voltage Waveforms Propagation Delays

(1) The greater between  $t_{\text{r}}$  and  $t_{\text{f}}$  is the same as  $t_{\text{t}}$ .

图 7-3. Voltage Waveforms, Input and Output Transition Times

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

## 8 Detailed Description

#### 8.1 Overview

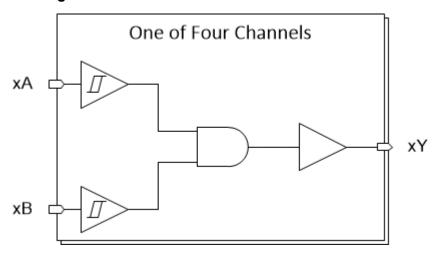

This device contains four independent 2-input AND Gates with Schmitt-trigger inputs. Each gate performs the Boolean function Y = A ● B in positive logic.

#### 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Balanced CMOS Push-Pull Outputs

This device includes balanced CMOS push-pull outputs. The term "balanced" indicates that the device can sink and source similar currents. The drive capability of this device may create fast edges into light loads so routing and load conditions should be considered to prevent ringing. Additionally, the outputs of this device are capable of driving larger currents than the device can sustain without being damaged. It is important for the output power of the device to be limited to avoid damage due to overcurrent. The electrical and thermal limits defined in the *Absolute Maximum Ratings* must be followed at all times.

Unused push-pull CMOS outputs should be left disconnected.

#### 8.3.2 CMOS Schmitt-Trigger Inputs

This device includes inputs with the Schmitt-trigger architecture. These inputs are high impedance and are typically modeled as a resistor in parallel with the input capacitance given in the *Electrical Characteristics* table from the input to ground. The worst case resistance is calculated with the maximum input voltage, given in the *Absolute Maximum Ratings* table, and the maximum input leakage current, given in the *Electrical Characteristics* table, using Ohm's law ( $R = V \div I$ ).

The Schmitt-trigger input architecture provides hysteresis as defined by  $\Delta V_T$  in the *Electrical Characteristics* table, which makes this device extremely tolerant to slow or noisy inputs. While the inputs can be driven much slower than standard CMOS inputs, it is still recommended to properly terminate unused inputs. Driving the inputs with slow transitioning signals will increase dynamic current consumption of the device. For additional information regarding Schmitt-trigger inputs, please see Understanding Schmitt Triggers.

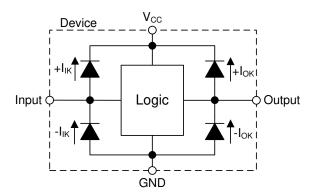

#### 8.3.3 Clamp Diode Structure

The inputs and outputs to this device have both positive and negative clamping diodes as depicted in Electrical Placement of Clamping Diodes for Each Input and Output.

### **CAUTION**

Voltages beyond the values specified in the *Absolute Maximum Ratings* table can cause damage to the device. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

图 8-1. Electrical Placement of Clamping Diodes for Each Input and Output

#### 8.4 Device Functional Modes

Function Table lists the functional modes of the SN74HCS08-Q1.

表 8-1. Function Table

| INPU | TS <sup>(1)</sup> | OUTPUT |  |  |  |

|------|-------------------|--------|--|--|--|

| Α    | В                 | Y      |  |  |  |

| Н    | Н                 | Н      |  |  |  |

| L    | Х                 | L      |  |  |  |

| X    | L                 | L      |  |  |  |

(1) H = High Voltage Level, L = Low Voltage Level, X = Don't Care

## 9 Application and Implementation

#### 备注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 9.1 Application Information

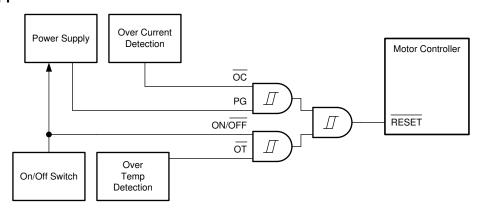

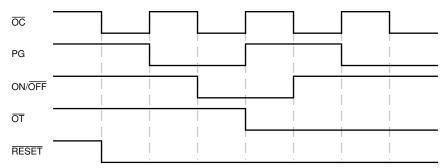

In this application, three 2-input AND gates are combined to produce a 4-input AND gate function as shown in § 9-1. The fourth gate can be used for another application in the system, or the inputs can be grounded and the channel left unused.

The SN74HCS08-Q1 is used to directly control the RESET pin of a motor controller. The controller requires four input signals to all be HIGH before being enabled, and should be disabled in the event that any one signal goes LOW. The 4-input AND gate function combines the four individual reset signals into a single active-low reset signal.

Many power good signals utilize open-drain outputs which can produce slow input transition rates when they transition from LOW to Hi-Z mode. This makes the SN74HCS08-Q1 ideal for the application because it has Schmitt-trigger inputs that do not have input transition rate requirements.

## 9.2 Typical Application

图 9-1. Typical application block diagram

#### 9.2.1 Design Requirements

#### 9.2.1.1 Power Considerations

Ensure the desired supply voltage is within the range specified in the *Recommended Operating Conditions*. The supply voltage sets the device's electrical characteristics as described in the *Electrical Characteristics*.

The positive voltage supply must be capable of sourcing current equal to the total current to be sourced by all outputs of the SN74HCS08-Q1 plus the maximum static supply current,  $I_{CC}$ , listed in *Electrical Characteristics* and any transient current required for switching. The logic device can only source as much current as is provided by the positive supply source. Be sure not to exceed the maximum total current through  $V_{CC}$  listed in the *Absolute Maximum Ratings*.

The ground must be capable of sinking current equal to the total current to be sunk by all outputs of the SN74HCS08-Q1 plus the maximum supply current, I<sub>CC</sub>, listed in *Electrical Characteristics*, and any transient current required for switching. The logic device can only sink as much current as can be sunk into its ground connection. Be sure not to exceed the maximum total current through GND listed in the *Absolute Maximum Ratings*.

The SN74HCS08-Q1 can drive a load with a total capacitance less than or equal to 50 pF while still meeting all of the datasheet specifications. Larger capacitive loads can be applied, however it is not recommended to exceed 50 pF.

The SN74HCS08-Q1 can drive a load with total resistance described by  $R_L \geqslant V_O$  /  $I_O$ , with the output voltage and current defined in the *Electrical Characteristics* table with  $V_{OH}$  and  $V_{OL}$ . When outputting in the high state, the output voltage in the equation is defined as the difference between the measured output voltage and the supply voltage at the  $V_{CC}$  pin.

Total power consumption can be calculated using the information provided in CMOS Power Consumption and Cpd Calculation.

Thermal increase can be calculated using the information provided in Thermal Characteristics of Standard Linear and Logic (SLL) Packages and Devices.

#### CAUTION

The maximum junction temperature,  $T_{J(max)}$  listed in the *Absolute Maximum Ratings*, is an additional limitation to prevent damage to the device. Do not violate any values listed in the *Absolute Maximum Ratings*. These limits are provided to prevent damage to the device.

#### 9.2.1.2 Input Considerations

Input signals must cross  $V_{t-(min)}$  to be considered a logic LOW, and  $V_{t+(max)}$  to be considered a logic HIGH. Do not exceed the maximum input voltage range found in the *Absolute Maximum Ratings*.

Unused inputs must be terminated to either  $V_{CC}$  or ground. These can be directly terminated if the input is completely unused, or they can be connected with a pull-up or pull-down resistor if the input is to be used sometimes, but not always. A pull-up resistor is used for a default state of HIGH, and a pull-down resistor is used for a default state of LOW. The resistor size is limited by drive current of the controller, leakage current into the SN74HCS08-Q1, as specified in the *Electrical Characteristics*, and the desired input transition rate. A 10-k  $\Omega$  resistor value is often used due to these factors.

The SN74HCS08-Q1 has no input signal transition rate requirements because it has Schmitt-trigger inputs.

Another benefit to having Schmitt-trigger inputs is the ability to reject noise. Noise with a large enough amplitude can still cause issues. To know how much noise is too much, please refer to the  $\Delta V_{T(min)}$  in the *Electrical Characteristics*. This hysteresis value will provide the peak-to-peak limit.

Unlike what happens with standard CMOS inputs, Schmitt-trigger inputs can be held at any valid value without causing huge increases in power consumption. The typical additional current caused by holding an input at a value other than V<sub>CC</sub> or ground is plotted in the *Typical Characteristics*.

Refer to the Feature Description section for additional information regarding the inputs for this device.

#### 9.2.1.3 Output Considerations

The positive supply voltage is used to produce the output HIGH voltage. Drawing current from the output will decrease the output voltage as specified by the  $V_{OH}$  specification in the *Electrical Characteristics*. The ground voltage is used to produce the output LOW voltage. Sinking current into the output will increase the output voltage as specified by the  $V_{OL}$  specification in the *Electrical Characteristics*.

Push-pull outputs that could be in opposite states, even for a very short time period, should never be connected directly together. This can cause excessive current and damage to the device.

Two channels within the same device with the same input signals can be connected in parallel for additional output drive strength.

Unused outputs can be left floating. Do not connect outputs directly to V<sub>CC</sub> or ground.

Refer to Feature Description section for additional information regarding the outputs for this device.

Copyright © 2022 Texas Instruments Incorporated

### 9.2.2 Detailed Design Procedure

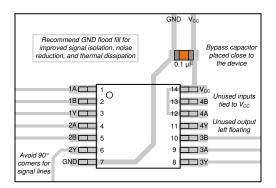

- Add a decoupling capacitor from V<sub>CC</sub> to GND. The capacitor needs to be placed physically close to the device and electrically close to both the V<sub>CC</sub> and GND pins. An example layout is shown in the *Layout* section.

- 2. Ensure the capacitive load at the output is ≤ 50 pF. This is not a hard limit, however it will ensure optimal performance. This can be accomplished by providing short, appropriately sized traces from the SN74HCS08-Q1 to the receiving device(s).

- 3. Ensure the resistive load at the output is larger than  $(V_{CC} / I_{O(max)})$   $\Omega$ . This will ensure that the maximum output current from the *Absolute Maximum Ratings* is not violated. Most CMOS inputs have a resistive load measured in megaohms; much larger than the minimum calculated above.

- 4. Thermal issues are rarely a concern for logic gates, however the power consumption and thermal increase can be calculated using the steps provided in the application report, CMOS Power Consumption and Cpd Calculation.

#### 9.2.3 Application Curves

图 9-2. Application timing diagram

## 10 Power Supply Recommendations

The power supply can be any voltage between the minimum and maximum supply voltage rating located in the *Recommended Operating Conditions*. Each  $V_{CC}$  terminal should have a good bypass capacitor to prevent power disturbance. A 0.1-  $\mu$  F capacitor is recommended for this device. It is acceptable to parallel multiple bypass caps to reject different frequencies of noise. The 0.1-  $\mu$  F and 1-  $\mu$  F capacitors are commonly used in parallel. The bypass capacitor should be installed as close to the power terminal as possible for best results, as shown in given example layout image.

## 11 Layout

#### 11.1 Layout Guidelines

When using multiple-input and multiple-channel logic devices inputs must not ever be left floating. In many cases, functions or parts of functions of digital logic devices are unused; for example, when only two inputs of a triple-input AND gate are used or only 3 of the 4 buffer gates are used. Such unused input pins must not be left unconnected because the undefined voltages at the outside connections result in undefined operational states. All unused inputs of digital logic devices must be connected to a logic high or logic low voltage, as defined by the input voltage specifications, to prevent them from floating. The logic level that must be applied to any particular unused input depends on the function of the device. Generally, the inputs are tied to GND or V<sub>CC</sub>, whichever makes more sense for the logic function or is more convenient.

## 11.2 Layout Example

图 11-1. Example layout for the SN74HCS08-Q1

## 12 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

### **12.1 Documentation Support**

#### 12.1.1 Related Documentation

For related documentation see the following:

- Texas Instruments, HCMOS Design Considerations application report (SCLA007)

- Texas Instruments, CMOS Power Consumption and C<sub>pd</sub> Calculation application report (SDYA009)

- Texas Instruments, Designing With Logic application report

### 12.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 12.3 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 12.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 12.6 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins            | Package qty   Carrier | RoHS | Lead finish/ MSL rating/ |                    | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|---------------------------|-----------------------|------|--------------------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                           |                       | (3)  | Ball material            | Peak reflow        |              | (6)          |

|                       |        |               |                           |                       |      | (4)                      | (5)                |              |              |

| SN74HCS08QBQARQ1      | Active | Production    | WQFN (BQA)   14           | 3000   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q       |

| SN74HCS08QBQARQ1.A    | Active | Production    | WQFN (BQA)   14           | 3000   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q       |

| SN74HCS08QDRQ1        | Active | Production    | SOIC (D)   14             | 2500   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q1      |

| SN74HCS08QDRQ1.A      | Active | Production    | SOIC (D)   14             | 2500   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q1      |

| SN74HCS08QDYYRQ1      | Active | Production    | SOT-23-THIN<br>(DYY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q       |

| SN74HCS08QDYYRQ1.A    | Active | Production    | SOT-23-THIN<br>(DYY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q       |

| SN74HCS08QPWRQ1       | Active | Production    | TSSOP (PW)   14           | 2000   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q       |

| SN74HCS08QPWRQ1.A     | Active | Production    | TSSOP (PW)   14           | 2000   LARGE T&R      | Yes  | NIPDAU                   | Level-1-260C-UNLIM | -40 to 125   | HCS08Q       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## PACKAGE OPTION ADDENDUM

www.ti.com 23-May-2025

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF SN74HCS08-Q1:

Catalog: SN74HCS08

NOTE: Qualified Version Definitions:

Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

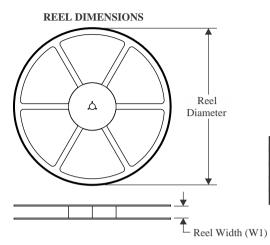

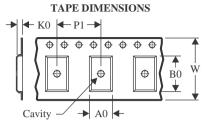

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

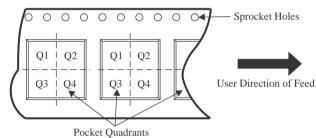

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN74HCS08QBQARQ1 | WQFN            | BQA                | 14 | 3000 | 180.0                    | 12.4                     | 2.8        | 3.3        | 1.1        | 4.0        | 12.0      | Q1               |

| SN74HCS08QDRQ1   | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| SN74HCS08QDYYRQ1 | SOT-23-<br>THIN | DYY                | 14 | 3000 | 330.0                    | 12.4                     | 4.8        | 3.6        | 1.6        | 8.0        | 12.0      | Q3               |

www.ti.com 24-Jul-2025

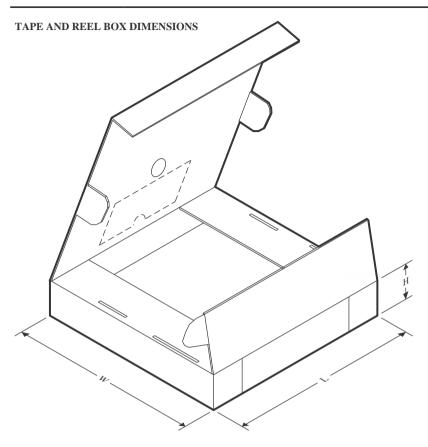

### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN74HCS08QBQARQ1 | WQFN         | BQA             | 14   | 3000 | 210.0       | 185.0      | 35.0        |

| SN74HCS08QDRQ1   | SOIC         | D               | 14   | 2500 | 353.0       | 353.0      | 32.0        |

| SN74HCS08QDYYRQ1 | SOT-23-THIN  | DYY             | 14   | 3000 | 336.6       | 336.6      | 31.8        |

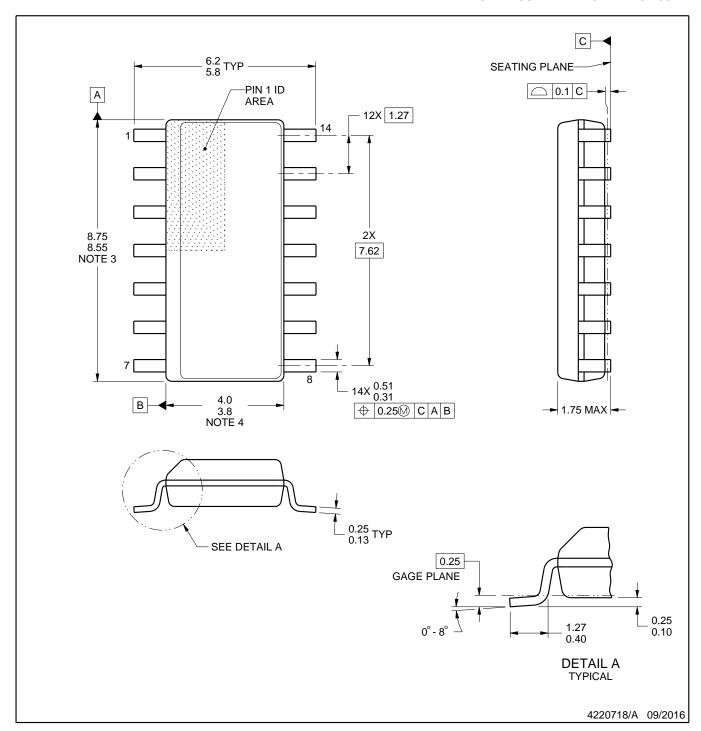

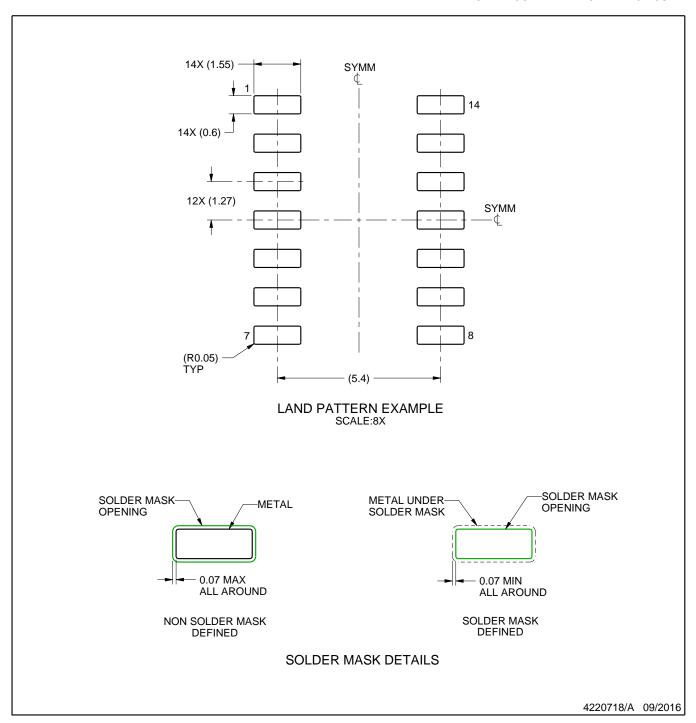

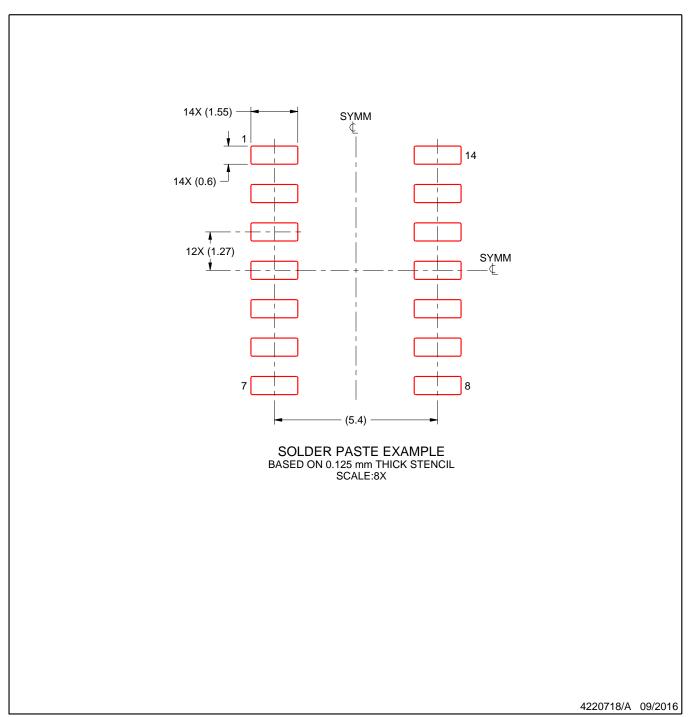

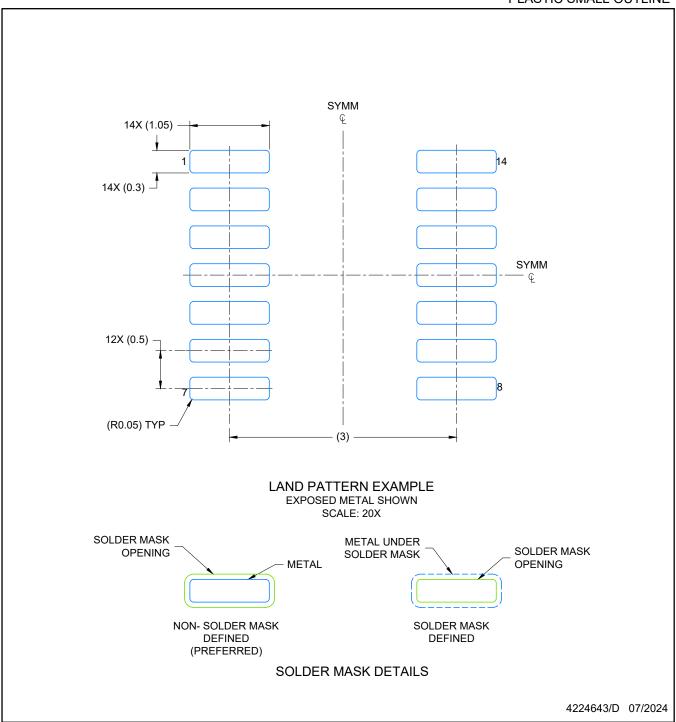

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

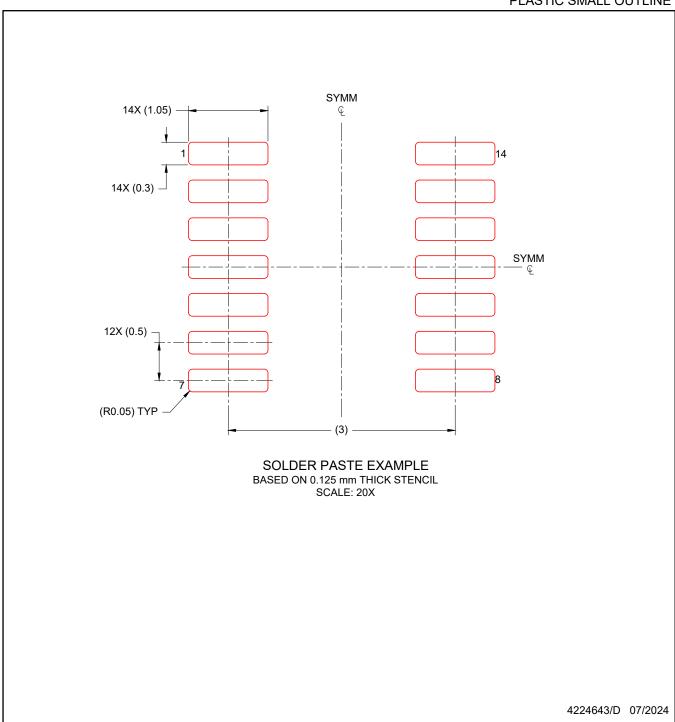

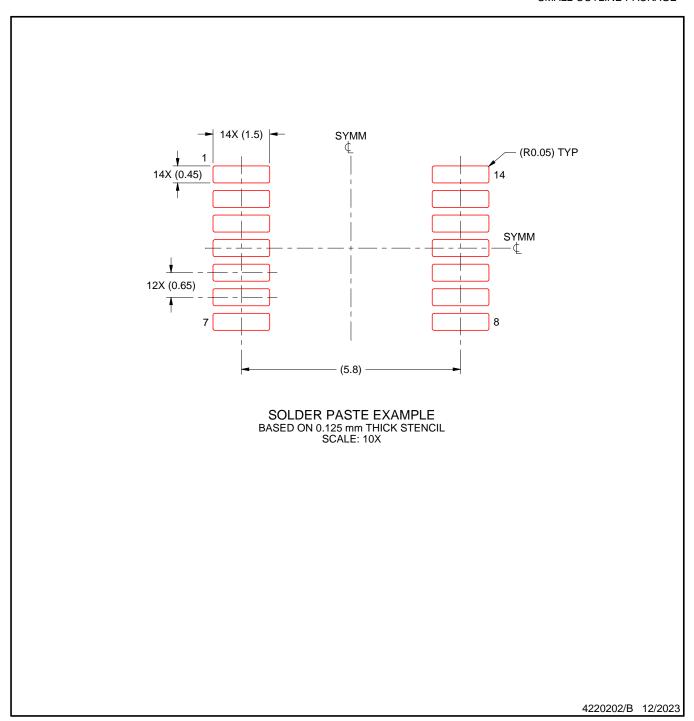

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

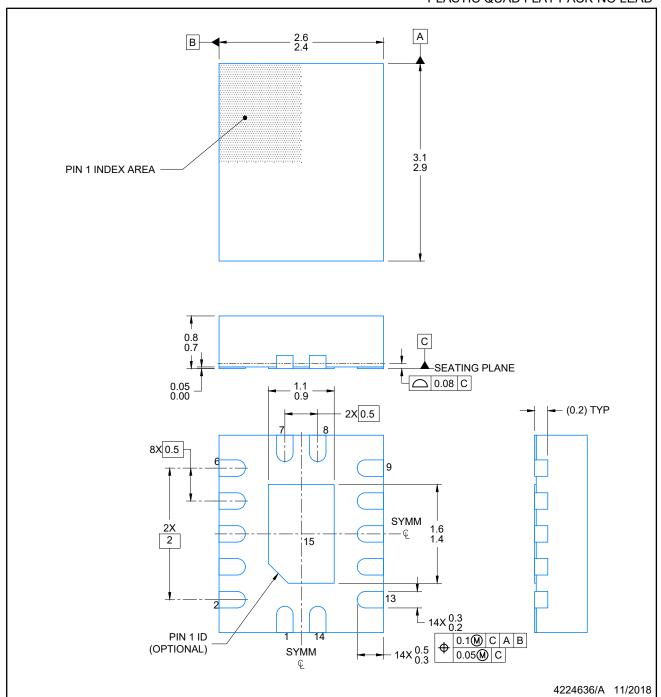

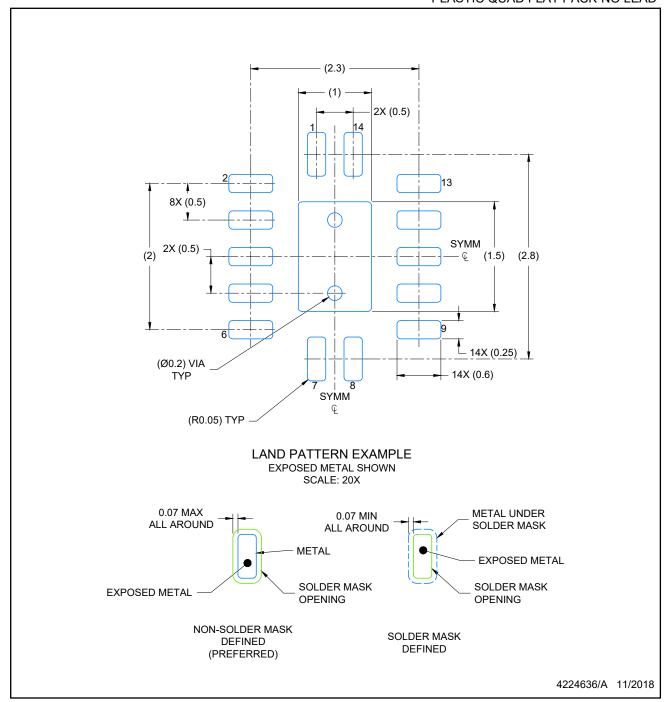

2.5 x 3, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

INSTRUMENTS www.ti.com

PLASTIC QUAD FLAT PACK-NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC QUAD FLAT PACK-NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLAT PACK-NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

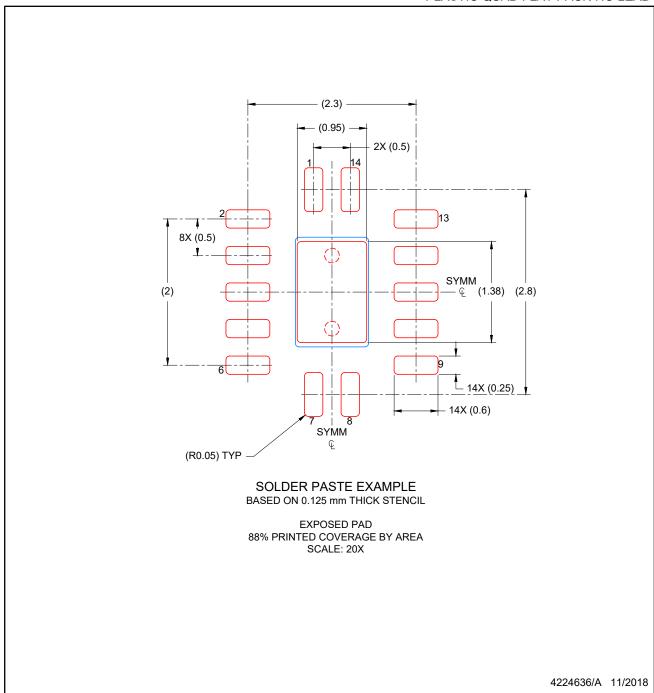

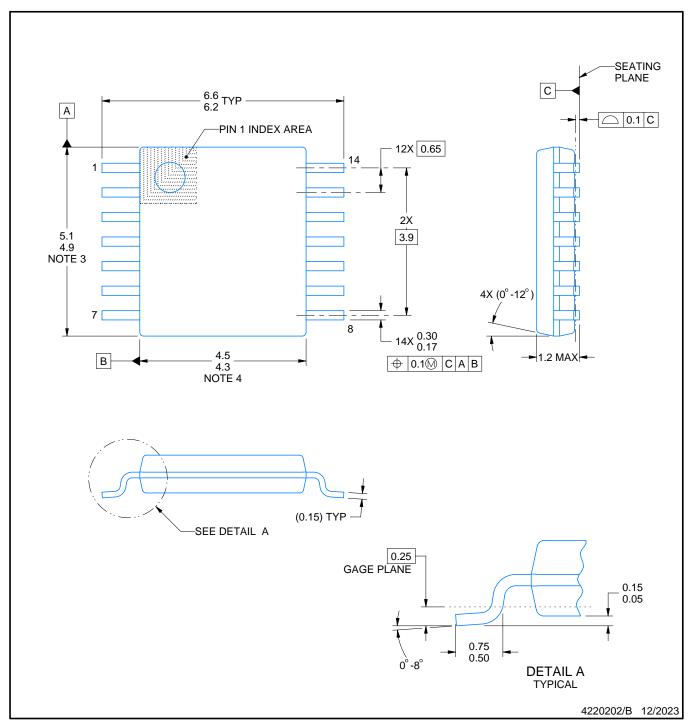

PLASTIC SMALL OUTLINE

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per side

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- 5. Reference JEDEC Registration MO-345, Variation AB

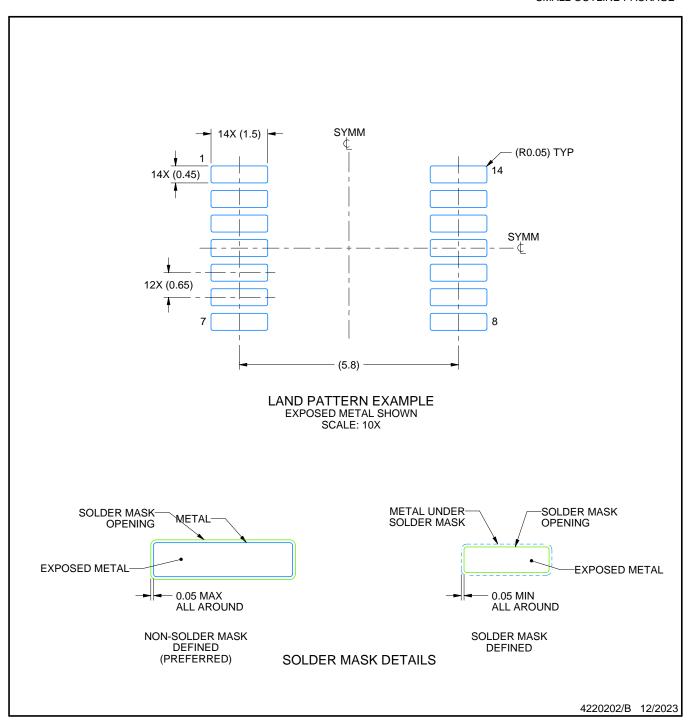

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

PLASTIC SMALL OUTLINE

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

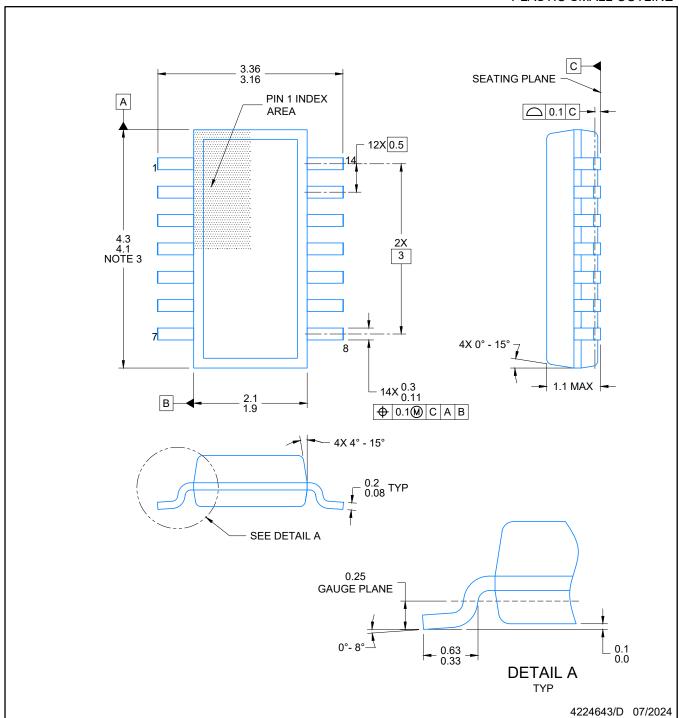

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司