🕳 Order

Now

#### SN65DSI85-Q1

ZHCSFS6B-JULY 2016-REVISED JUNE 2018

# SN65DSI85-Q1 汽车类双通道 MIPI<sup>®</sup>DSI 转双链路 LVDS 桥接器

## 1 特性

- 符合汽车类应用的 要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 2: -40℃ 至 105℃ 的环境运行 温度范围

- 器件 HBM ESD 分类等级 3A

- 器件 CDM ESD 分类等级 C6

- 实现了 MIPI D-PHY 版本 1.00.00 物理层前端和显示屏串行接口 (DSI) 版本 1.02.00

- 双通道 DSI 接收器在每个通道上可针对 1 条, 2 条, 3 条或 4 条 D-PHY 数据信道进行配置, 每信 道的运行速率高达 1Gbps

- 支持 RGB666 和 RGB888 格式的 18bpp 与 24bpp DSI 视频流

- 适合 60fps WQXGA 2560 × 1600 分辨率(18bpp 和 24bpp 颜色),以及 60fps(120fps 等效)

WUXGA 1920 × 1200 分辨率和 3D 图形显示 (24bpp 颜色)

- MIPI 前端可配置为单通道或双通道 DSI 配置

- 针对单链路或双链路 LVDS 的输出配置

- 支持双通道 DSI ODD/EVEN 和 LEFT/RIGHT 操作 模式

- 支持两个单通道 DSI 转两条单链路 LVDS 的操作模式

- 双链路或单链路模式下 LVDS 输出时钟范围为 25MHz 到 154MHz

- LVDS 像素时钟可采用自由运行持续 D-PHY 时钟 或外部基准时钟 (REFCLK)

- 1.8V 主 V<sub>CC</sub> 电源

- 低功耗 特性 包括关断模式、低 LVDS 输出电压摆 幅、共模以及 MIPI 超低功耗状态 (ULPS) 支持

- 针对简化印刷电路板 (PCB) 走线的 LVDS 通道交换 (SWAP), LVDS 引脚顺序反向特性

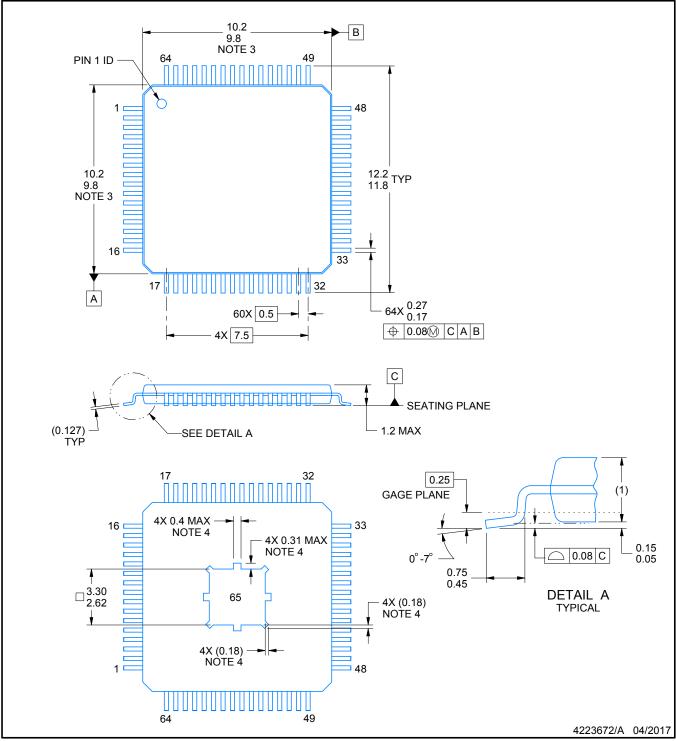

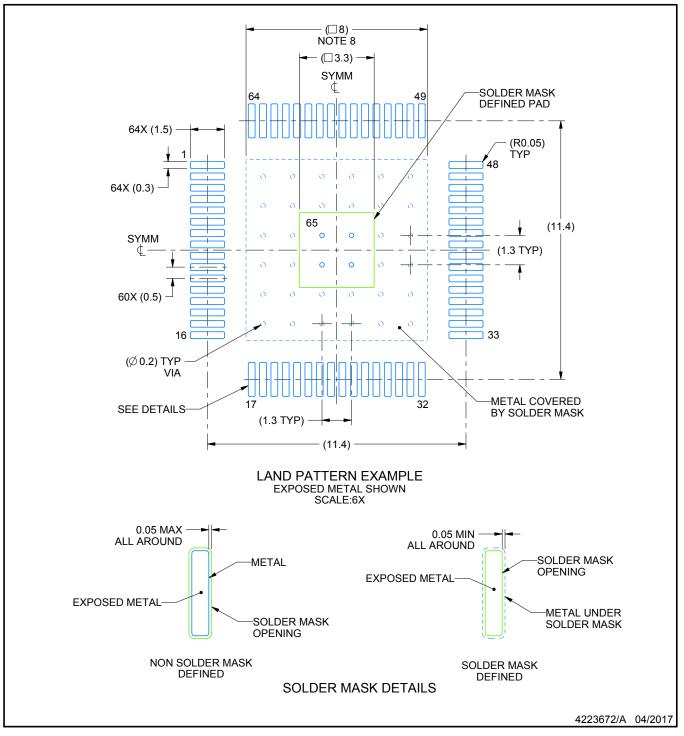

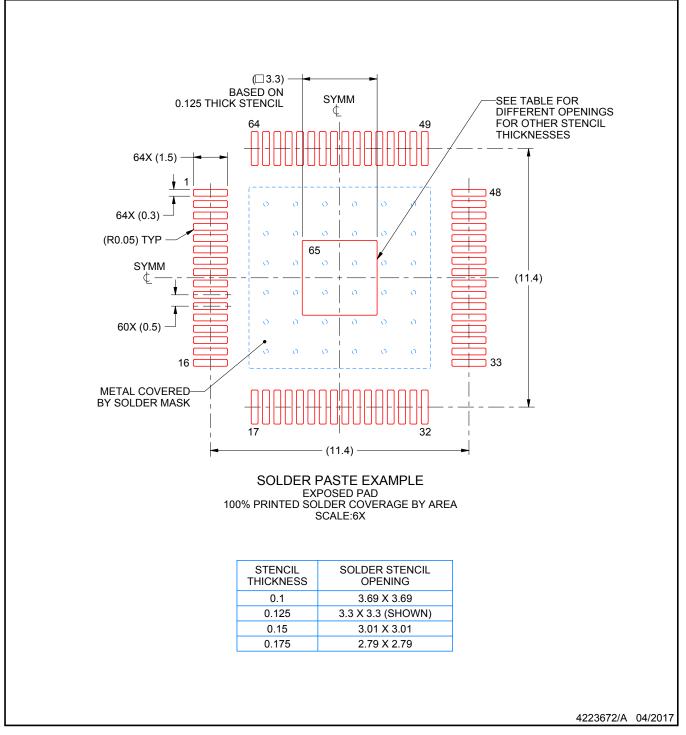

- 采用 64 引脚 10mm × 10mm HTQFP (PAP) 封装 PowerPAD™IC 封装

## 2 应用

- 集成显示屏的信息娱乐系统主机

- 具有远程显示屏的信息娱乐系统主机

- 后座信息娱乐系统

- 混合动力汽车仪表板

- 便携式导航设备

- 导航

- 工业人机界面 (HMI) 和显示屏

## 3 说明

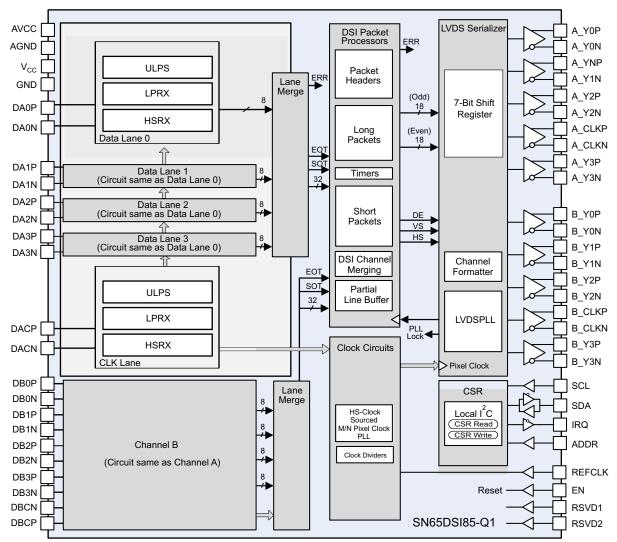

SN65DSI85-Q1 DSI 转 LVDS 桥接器 具有 一个双通 道 MIPI D-PHY 接收器前端

配置,此配置中在每个通道上具有 4 条信道,每条信 道的运行速率为 1Gbps,最大输入带宽为 8Gbps。该 桥接器可解码 MIPI DSI 18bpp RGB666 和 24bpp RGB888 视频流,并将格式化视频数据流转换为 LVDS 输出(像素时钟范围为 25MHz 至 154MHz), 从而提供一个双链路 LVDS、单链路 LVDS 或两个单 链路 LVDS 接口(每个链路具有 4 个数据信道)。

SN65DSI85-Q1 器件非常适用于 60fps 的 WQXGA (2560 × 1600),以及等效 120fps(高达 24 bpp)的 WUXGA 3D 图形和全高清 (1920x1080)分辨率。该器 件实现了部分线路缓冲以适应 DSI 与 LVDS 接口间的 数据流不匹配的情况。

SN65DSI85-Q1 器件采用小外形 10mm × 10mm HTQFP

(0.5mm 间距)封装,工作温度范围为 –40℃ 至 +105℃。

## 器件信息<sup>(1)</sup>

| 器件编号         | 封装         | 封装尺寸(标称值)         |

|--------------|------------|-------------------|

| SN65DSI85-Q1 | HTQFP (64) | 10.00mm x 10.00mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

## 典型应用

| Application<br>Processor<br>With DSI<br>Output | DA[3:0]P      |                                                        | A_Y0:3N     | TFT LCD Display |  |  |  |  |

|------------------------------------------------|---------------|--------------------------------------------------------|-------------|-----------------|--|--|--|--|

|                                                | DA[3:0]N      | Dual-Channel<br>DSI to LVDS<br>Bridge<br>SN65SDSI85-Q1 | DSI to LVDS | A Y0:3P         |  |  |  |  |

|                                                | DACP/N        |                                                        |             | A_CLKN/P        |  |  |  |  |

|                                                | /<br>DB[3:0]P |                                                        | B_Y0:3N     |                 |  |  |  |  |

|                                                | /<br>DB[3:0]N |                                                        | B_Y0:3P     |                 |  |  |  |  |

|                                                | SCL/SDA       |                                                        | B_CLKN/P    | THE -           |  |  |  |  |

|                                                | '             |                                                        | ,           |                 |  |  |  |  |

Copyright © 2016, Texas Instruments Incorporated

# <del>欢</del>至四)

#### Copyright © 2016–2018, Texas Instruments Incorporated

www.ti.com.cn

Page

## 目录

| 特性   |                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------|

| 应用   | 1                                                                                                                 |

| 说明   | 1                                                                                                                 |

| 修订   | 历史记录 2                                                                                                            |

| Pin  | Configuration and Functions 3                                                                                     |

| Spe  | cifications5                                                                                                      |

| 6.1  | Absolute Maximum Ratings 5                                                                                        |

| 6.2  | ESD Ratings 5                                                                                                     |

| 6.3  | Recommended Operating Conditions 6                                                                                |

| 6.4  | Thermal Information 6                                                                                             |

| 6.5  | Electrical Characteristics 6                                                                                      |

| 6.6  | Switching Characteristics 9                                                                                       |

| Para | ameter Measurement Information 10                                                                                 |

| Deta | ailed Description 13                                                                                              |

| 8.1  | Overview 13                                                                                                       |

| 8.2  | Functional Block Diagram 13                                                                                       |

| 8.3  | Feature Description 14                                                                                            |

| 8.4  | Device Functional Modes24                                                                                         |

| 8.5  | Programming                                                                                                       |

|      | 1<br>应 说 修 <b>Pin</b><br><b>Spe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Para</b><br>8.1<br>8.3<br>8.4 |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Cł | hanges from Revision A (December 2016) to Revision B P                                  |      |  |

|----|-----------------------------------------------------------------------------------------|------|--|

| •  | Deleted figure RESET and Initialization Timing Definition While V <sub>CC</sub> is High | . 12 |  |

| •  | Changed the paragraph following Figure 8                                                | . 14 |  |

| •  | Changed Table 1                                                                         | . 15 |  |

## Changes from Original (July 2016) to Revision A

| • | 己将器件状态更改为量产数据 | 1 |

|---|---------------|---|

|   |               | - |

|    | 8.6  | Register Maps 25               |

|----|------|--------------------------------|

| 9  | App  | lication and Implementation53  |

|    | 9.1  | Application Information 53     |

|    | 9.2  | Typical Applications 54        |

| 10 | Pow  | ver Supply Recommendations     |

|    | 10.1 | V <sub>CC</sub> Power Supply60 |

|    | 10.2 | VCORE Power Supply 60          |

| 11 | Lay  | out                            |

|    | 11.1 | Layout Guidelines 60           |

|    | 11.2 | Layout Example 61              |

| 12 | 器件   | 和文档支持 62                       |

|    | 12.1 | 文档支持62                         |

|    | 12.2 | 接收文档更新通知 62                    |

|    | 12.3 | 社区资源62                         |

|    | 12.4 | 商标62                           |

|    | 12.5 |                                |

|    | 12.6 | 术语表 62                         |

| 13 | 机械   | 、封装和可订购信息62                    |

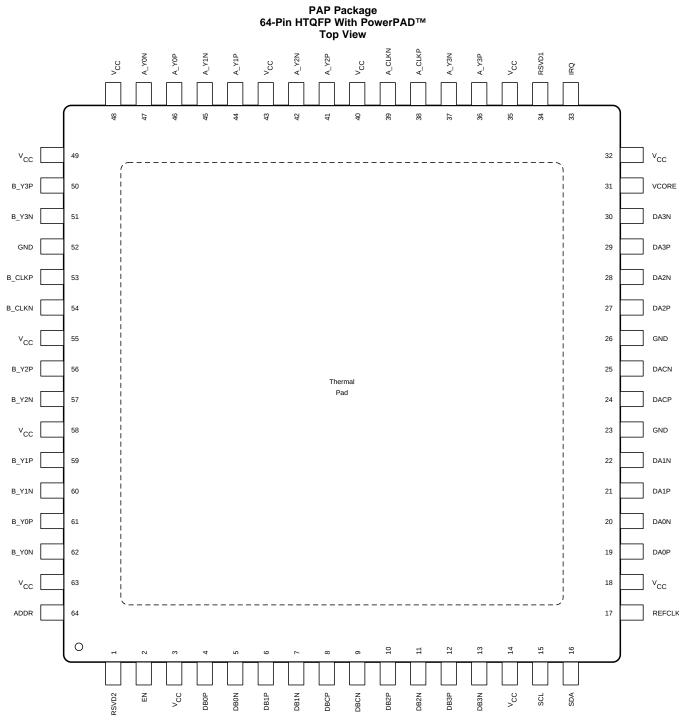

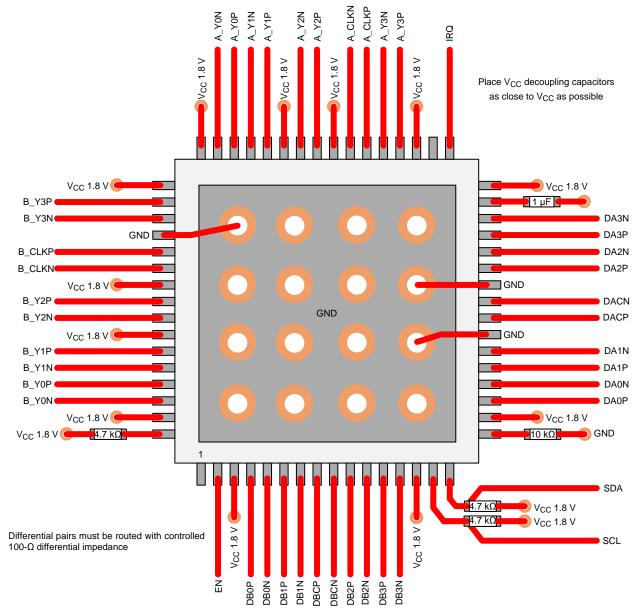

## 5 Pin Configuration and Functions

See the *Layout* section for layout information.

SN65DSI85-Q1 ZHCSFS6B-JULY 2016-REVISED JUNE 2018

www.ti.com.cn

INSTRUMENTS

Texas

## **Pin Functions**

|        | PIN |      | Pin Functions                                                                                                                                                                                                                                                |  |

|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                  |  |

| ADDR   | 64  | I/O  | Local I <sup>2</sup> C interface target address select. See Table 6. In normal operation this pin is an input. When the ADDR pin is programmed high, it must be tied to the same 1.8-V power rails where the SN65DSI85-Q1 VCC 1.8-V power rail is connected. |  |

| A_Y0P  | 46  | 0    | LV/DS channel A LV/DS data output 0                                                                                                                                                                                                                          |  |

| A_Y0N  | 47  | 0    | LVDS channel A, LVDS data output 0                                                                                                                                                                                                                           |  |

| A_Y1P  | 44  | 0    | LVDS channel A, LVDS data output 1                                                                                                                                                                                                                           |  |

| A_Y1N  | 45  | 0    |                                                                                                                                                                                                                                                              |  |

| A_Y2P  | 41  | 0    | LVDS channel A, LVDS data output 2                                                                                                                                                                                                                           |  |

| A_Y2N  | 42  | 0    |                                                                                                                                                                                                                                                              |  |

| A_Y3P  | 36  | 0    | LVDS channel A, LVDS data output 3. A_Y3P and A_Y3N must be left not connected                                                                                                                                                                               |  |

| A_Y3N  | 37  | 0    | (NC) for 18-bpp panels.                                                                                                                                                                                                                                      |  |

| A_CLKP | 38  | 0    | LVDS channel A, LVDS clock output                                                                                                                                                                                                                            |  |

| A_CLKN | 39  | 0    |                                                                                                                                                                                                                                                              |  |

| B_Y0P  | 61  | 0    | LVDS channel B, LVDS data output 0                                                                                                                                                                                                                           |  |

| B_Y0N  | 62  | 0    |                                                                                                                                                                                                                                                              |  |

| B_Y1P  | 59  | 0    | LVDS channel B, LVDS data output 1                                                                                                                                                                                                                           |  |

| B_Y1N  | 60  | 0    |                                                                                                                                                                                                                                                              |  |

| B_Y2P  | 56  | 0    | LVDS channel B, LVDS data output 2                                                                                                                                                                                                                           |  |

| B_Y2N  | 57  | 0    |                                                                                                                                                                                                                                                              |  |

| B_Y3P  | 50  | 0    | LVDS channel B, LVDS data output 3. B_Y3P and B_Y3N must be left NC for 18-bpp                                                                                                                                                                               |  |

| B_Y3N  | 51  | 0    | panels.                                                                                                                                                                                                                                                      |  |

| B_CLKP | 53  | 0    | LVDS channel B, LVDS clock output                                                                                                                                                                                                                            |  |

| B_CLKN | 54  | 0    |                                                                                                                                                                                                                                                              |  |

| DA0P   | 19  | I    | MIPI D-PHY channel A, data lane 0; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DA0N   | 20  | I    |                                                                                                                                                                                                                                                              |  |

| DA1P   | 21  | Ι    | MIPI D-PHY channel A, data lane 1; data rate up to 1 Gbps                                                                                                                                                                                                    |  |

| DA1N   | 22  | I    |                                                                                                                                                                                                                                                              |  |

| DA2P   | 27  | I    | MIPI D-PHY channel A, data lane 2; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DA2N   | 28  | I    |                                                                                                                                                                                                                                                              |  |

| DA3P   | 29  | Ι    | MIPI D-PHY channel A, data lane 3; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DA3N   | 30  | I    |                                                                                                                                                                                                                                                              |  |

| DACP   | 24  | Ι    | MIRI D RHV channel A clock lane; data rate up to 1 Chan                                                                                                                                                                                                      |  |

| DACN   | 25  | Ι    | MIPI D-PHY channel A, clock lane; data rate up to 1 Gbps.                                                                                                                                                                                                    |  |

| DB0P   | 4   | Ι    | MIPI D-PHY channel B, data lane 0; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DB0N   | 5   | Ι    |                                                                                                                                                                                                                                                              |  |

| DB1P   | 6   | Ι    | MIPI D-PHY channel B, data lane 1; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DB1N   | 7   | Ι    |                                                                                                                                                                                                                                                              |  |

| DB2P   | 10  | I    | MIPL D. PHV channel B. data lane 2: data rate up to 1 Chan                                                                                                                                                                                                   |  |

| DB2N   | 11  | I    | MIPI D-PHY channel B, data lane 2; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DB3P   | 12  | Ι    | MIPI D.PHY channel B. data lane 3: data rate up to 1 Chan                                                                                                                                                                                                    |  |

| DB3N   | 13  | Ι    | MIPI D-PHY channel B, data lane 3; data rate up to 1 Gbps.                                                                                                                                                                                                   |  |

| DBCP   | 8   | Ι    |                                                                                                                                                                                                                                                              |  |

| DBCN   | 9   | I    | MIPI D-PHY channel B, clock lane; operates up to 1 Gbps.                                                                                                                                                                                                     |  |

| EN     | 2   | I    | Chip enable and reset. The device is reset (shutdown) when the EN pin is low.                                                                                                                                                                                |  |

|        | 23  | G    |                                                                                                                                                                                                                                                              |  |

| GND    | 26  | G    | Reference ground                                                                                                                                                                                                                                             |  |

|        | 52  | G    |                                                                                                                                                                                                                                                              |  |

## **Pin Functions (continued)**

| PIN             |     | TYPE | DECODIDION                                                                                                                                                                                                                                                                                                             |  |  |

|-----------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                            |  |  |

| IRQ             | 33  | 0    | Interrupt signal                                                                                                                                                                                                                                                                                                       |  |  |

| REFCLK          | 17  | I    | This pin is an optional external reference clock for the LVDS pixel clock. If an external<br>eference clock is not used, this pin must be pulled to ground with an external resistor.<br>The source of the reference clock must be placed as close as possible with a series<br>esistor near the source to reduce EMI. |  |  |

| RSVD1           | 34  | I/O  | Reserved. This pin must be left unconnected for normal operation.                                                                                                                                                                                                                                                      |  |  |

| RSVD2           | 1   | I    | Reserved. This pin must be left unconnected for normal operation.                                                                                                                                                                                                                                                      |  |  |

| SCL             | 15  | I    | Local I <sup>2</sup> C interface clock.                                                                                                                                                                                                                                                                                |  |  |

| SDA             | 16  | I/O  | Local I <sup>2</sup> C interface data                                                                                                                                                                                                                                                                                  |  |  |

|                 | 3   | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 14  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 18  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 32  | —    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 35  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

| M               | 40  | _    | 1.8-V power supply                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>CC</sub> | 43  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 48  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 49  | —    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 55  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 58  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

|                 | 63  | _    |                                                                                                                                                                                                                                                                                                                        |  |  |

| VCORE           | 31  | Р    | 1.1-V output from the voltage regulator. This pin must have a $1-\mu F$ external capacitor to ground.                                                                                                                                                                                                                  |  |  |

| PowerPAD        |     | _    | Reference ground                                                                                                                                                                                                                                                                                                       |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                |                                             | MIN  | MAX   | UNIT |

|------------------|--------------------------------|---------------------------------------------|------|-------|------|

| V <sub>CC</sub>  | Supply voltage                 |                                             | -0.3 | 2.175 | V    |

|                  |                                | CMOS input pins                             | -0.5 | 2.175 | V    |

|                  | Input voltage                  | DSI input pins (DAxP, DAxN, DBxP, and DBxN) | -0.4 | 1.4   | V    |

| T <sub>A</sub>   | Operating free-air temperature |                                             | -40  | 105   | °C   |

| TJ               | Junction temperature           |                                             | -40  | 115   | °C   |

| T <sub>stg</sub> | Storage temperature            |                                             | -65  | 150   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |               |                                                         | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±4000 | V    |

| V <sub>(ESD)</sub> |               | Charged-device model (CDM), per AEC Q100-011            | ±1000 | v    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

ZHCSFS6B-JULY 2016-REVISED JUNE 2018

www.ti.com.cn

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                               | MIN                           | NOM | MAX  | UNIT              |

|-----------------------|-----------------------------------------------|-------------------------------|-----|------|-------------------|

| V <sub>CC</sub>       | V <sub>CC</sub> power supply                  | 1.65                          | 1.8 | 1.95 | V                 |

| V <sub>PSN</sub>      | Supply noise on any $V_{CC}$ pin              | $f_{(noise)} > 1 \text{ MHz}$ |     | 0.05 | V                 |

| V <sub>(DSI)</sub>    | DSI input pin voltage                         | -50                           |     | 1350 | mV                |

| $f_{(I2C)}$           | Local I <sup>2</sup> C input frequency        |                               |     | 400  | kHz               |

| $f_{HS(CLK)}$         | DSI high-speed (HS) clock input frequency     | 40                            |     | 500  | MHz               |

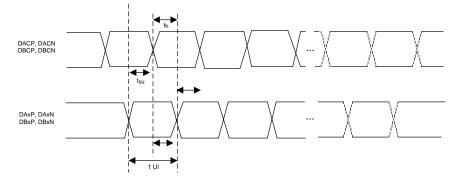

| t <sub>su</sub>       | DSI HS data to clock setup time; see Figure 1 | 0.15                          |     |      | UI <sup>(1)</sup> |

| t <sub>h</sub>        | DSI HS data to clock hold time; see Figure 1  | 0.15                          |     |      | UI <sup>(1)</sup> |

| Z <sub>OD(LVDS)</sub> | LVDS output differential impedance            | 90                            |     | 132  | Ω                 |

| Т <sub>С</sub>        | Case temperature                              |                               |     | 92.2 | °C                |

(1) The unit interval (UI) is one half of the period of the HS clock; at 500 MHz the minimum setup and hold time is 150 ps.

## 6.4 Thermal Information

|                       |                                              | SN65DSI85-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PAP (HTQFP)  | UNIT |

|                       |                                              | 64 PINS      |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 36.1         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18.2         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20.6         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.8          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 20.5         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.2          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                               | TEST CONDITIONS                                              | MIN                 | TYP <sup>(1)</sup> | MAX                   | UNIT |

|-------------------|-----------------------------------------|--------------------------------------------------------------|---------------------|--------------------|-----------------------|------|

| VIL               | Low-level control signal input voltage  |                                                              |                     |                    | 0.3 × V <sub>CC</sub> | V    |

| VIH               | High-level control signal input voltage |                                                              | $0.7 \times V_{CC}$ |                    |                       | V    |

| V <sub>OH</sub>   | High-level output voltage               | $I_{OH} = -4 \text{ mA}$                                     | 1.25                |                    |                       | V    |

| V <sub>OL</sub>   | Low-level output voltage                | I <sub>OL</sub> = 4 mA                                       |                     |                    | 0.4                   | V    |

| I <sub>LKG</sub>  | Input failsafe leakage current          | V <sub>CC</sub> = 0; V <sub>CC(PIN)</sub> = 1.8 V            |                     |                    | ±30                   | μΑ   |

| I <sub>IH</sub>   | High level input current                | Any input terminal                                           |                     |                    | ±30                   | μΑ   |

| IIL               | Low level input current                 | Any input terminal                                           |                     |                    | ±30                   | μΑ   |

| I <sub>OZ</sub>   | High-impedance output current           | CMOS output terminals                                        |                     |                    | ±10                   | μΑ   |

| I <sub>OS</sub>   | Short-circuit output current            | Any output driving GND short                                 |                     |                    | ±50                   | mA   |

| I <sub>CC</sub>   | Device active current                   | See <sup>(2)</sup>                                           |                     | 127                | 232                   | mA   |

| I <sub>ULPS</sub> | Device standby current                  | All data and clock lanes are in ultra-low power state (ULPS) |                     | 7.7                | 14                    | mA   |

| I <sub>RST</sub>  | Shutdown current                        | EN = 0                                                       |                     | 0.04               | 130                   | μA   |

| R <sub>EN</sub>   | EN control input resistor               |                                                              |                     | 200                |                       | kΩ   |

(1)

All typical values are at V<sub>CC</sub> = 1.8V and T<sub>A</sub> = 25°C SN65DSI85-Q1: DUAL Channel DSI to DUAL Channel LVDS, 1920 x 1200 (a) number of LVDS lanes =  $2 \times (3 \text{ data lanes} + 1 \text{ CLK lane})$ (2)

(b) number of DSI lanes = 2 x (4 data lanes + 1 CLK lane

(c) LVDS CLK OUT = 81.6 M

(d) DSI CLK = 490 M

(e) RGB888, LVDS18bpp

Maximum values are at V<sub>CC</sub> = 1.95 V and T<sub>A</sub> = 105°C

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                          | TEST CONDITIONS                                                                                                                            | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| MIPI DSI IN          | ITERFACE                                                                           |                                                                                                                                            |     |                    |     |      |

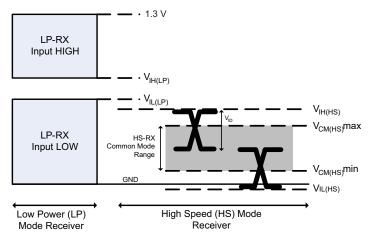

| V <sub>IH-LP</sub>   | LP receiver input high threshold                                                   | See Figure 2                                                                                                                               | 880 |                    |     | mV   |

| V <sub>IL-LP</sub>   | LP receiver input low threshold                                                    | See Figure 2                                                                                                                               |     |                    | 550 | mV   |

| V <sub>ID</sub>      | HS differential input voltage                                                      |                                                                                                                                            | 100 |                    | 270 | mV   |

| V <sub>IDT</sub>     | HS differential input voltage threshold                                            |                                                                                                                                            |     |                    | 50  | mV   |

| VIL-ULPS             | LP receiver input low threshold; ultra-low power state (ULPS)                      |                                                                                                                                            |     |                    | 300 | mV   |

| V <sub>CM-HS</sub>   | HS common mode voltage; steady-state                                               |                                                                                                                                            | 70  |                    | 330 | mV   |

| $\Delta V_{CM-HS}$   | HS common mode peak-to-peak variation<br>including symbol delta and interference   |                                                                                                                                            |     |                    | 100 | mV   |

| V <sub>IH-HS</sub>   | HS single-ended input high voltage                                                 | See Figure 2                                                                                                                               |     |                    | 460 | mV   |

| V <sub>IL-HS</sub>   | HS single-ended input low voltage                                                  | See Figure 2                                                                                                                               | -40 |                    |     | mV   |

| V <sub>TERM-EN</sub> | HS termination enable; single-ended input voltage (both Dp AND Dn apply to enable) | Termination is switched simultaneous for<br>Dn and Dp                                                                                      |     |                    | 450 | mV   |

| R <sub>DIFF-HS</sub> | HS mode differential input impedance                                               |                                                                                                                                            | 80  |                    | 125 | Ω    |

| LVDS OUT             | PUT                                                                                | L I                                                                                                                                        |     |                    |     |      |

|                      | -                                                                                  | CSR 0x19.3:2=00 and, or CSR $0x19.1:0=00$<br>100 $\Omega$ near end termination                                                             | 180 | 245                | 330 |      |

|                      |                                                                                    | CSR 0x19.3:2=01 and, or CSR $0x19.3:2=01$ and, or CSR $0x19.1:0=01$ $100 \ \Omega$ near end termination                                    | 215 | 293                | 392 |      |

|                      |                                                                                    | CSR 0x19.3:2=10 and, or CSR $0x19.3:2=10$ and, or CSR $0x19.1:0=10$ $100 \ \Omega$ near end termination                                    | 250 | 341                | 455 |      |

| N7 1                 | Steady-state differential output voltage for                                       | CSR 0x19.3:2=11 and, or CSR $0x19.1:0=11$<br>100 $\Omega$ near end termination                                                             | 290 | 389                | 515 | V    |

| V <sub>od</sub>      | A_Yx P/N and B_Yx P/N                                                              | CSR 0x19.3:2=00 and, or CSR $0x19.3:2=00$ and, or CSR $0x19.1:0=00$ 200 $\Omega$ near end termination                                      | 150 | 204                | 275 | mV   |

|                      | -                                                                                  | CSR 0x19.3:2=01 and, or CSR<br>0x19.1:0=01<br>200 $\Omega$ near end termination                                                            | 200 | 271                | 365 |      |

|                      |                                                                                    | $\begin{array}{c} \text{CSR } 0x19.3:2=10 \text{ and, or CSR} \\ 0x19.1:0=10 \\ 200 \ \Omega \text{ near end termination} \end{array}$     | 250 | 337                | 450 |      |

|                      |                                                                                    | $\begin{array}{c} \text{CSR 0x19.3:2=11 and, or CSR} \\ \text{0x19.1:0=11} \\ \text{200 } \Omega \text{ near end termination} \end{array}$ | 300 | 402                | 535 |      |

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                            | TEST CONDITIONS                                                                                                                                                | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|-----------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

|                       |                                                                                      | CSR 0x19.3:2=00 and, or CSR<br>0x19.1:0=00<br>100 Ω near end termination                                                                                       | 140  | 191                | 262  |      |

|                       |                                                                                      | CSR 0x19.3:2=01 and, or CSR $0x19.3:2=01$ and, or CSR $0x19.1:0=01$ $100 \Omega$ near end termination                                                          | 168  | 229                | 315  |      |

|                       |                                                                                      | CSR 0x19.3:2=10 and, or CSR<br>0x19.1:0=10<br>100 Ω near end termination                                                                                       | 195  | 266                | 365  |      |

| NZ I                  | Steady-state differential output voltage for                                         | CSR 0x19.3:2=11 and, or CSR<br>0x19.1:0=11<br>100 Ω near end termination                                                                                       | 226  | 303                | 415  |      |

| V <sub>od</sub>       | A_CLKP/N and B_CLKP/N                                                                | CSR 0x19.3:2=00 and, or CSR<br>0x19.1:0=00<br>200 Ω near end termination                                                                                       | 117  | 159                | 220  | mV   |

|                       |                                                                                      | CSR 0x19.3:2=01 and, or CSR<br>0x19.1:0=01<br>200 Ω near end termination                                                                                       | 156  | 211                | 295  |      |

|                       |                                                                                      | CSR 0x19.3:2=10 and, or CSR         195         263           0x19.1:0=10         195         263           200 Ω near end termination         195         263 | 362  |                    |      |      |

|                       |                                                                                      | CSR 0x19.3:2=11 and, or CSR $0x19.3:2=11$ and, or CSR $0x19.1:0=11$ 200 $\Omega$ near end termination                                                          | 234  | 314                | 435  |      |

| $\Delta  V_{OD} $     | Change in steady-state differential output<br>voltage between opposite binary states | RL = 100 Ω                                                                                                                                                     |      |                    | 35   | mV   |

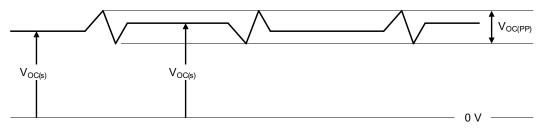

| V <sub>OC(SS)</sub>   | Steady state common-mode output                                                      | CSR 0x19.6 = 1 and CSR 0x1B.6 = 1;<br>and, or CSR 0x19.4 = 1 and<br>CSR 0x1B.4 = 1; see Figure 3                                                               | 0.75 | 0.9                | 1.13 | V    |

| 00(00)                | voltage <sup>(3)</sup>                                                               | CSR 0x19.6 = 0 and, or CSR 0x19.4 = 0;<br>see Figure 3                                                                                                         | 1    | 1.25               | 1.5  |      |

| V <sub>OC(PP)</sub>   | Peak-to-peak common-mode output voltage                                              | see Figure 3                                                                                                                                                   |      |                    | 35   | mV   |

| R <sub>LVDS_DIS</sub> | Pulldown resistance for disabled LVDS<br>outputs                                     |                                                                                                                                                                |      | 1                  |      | kΩ   |

(3) Tested at  $V_{CC}$  = 1.8V ,  $T_A$  = –40°C for MIN,  $T_A$  = 25°C for TYP,  $T_A$  = 105°C for MAX.

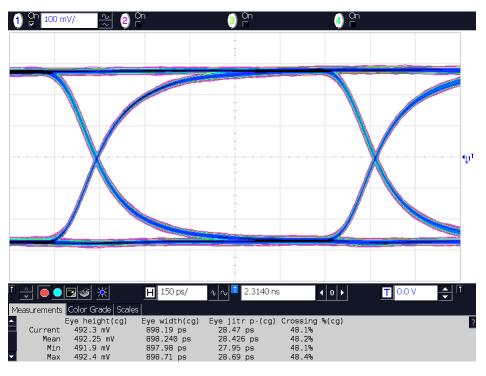

## 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                                    | TEST CONDITIONS                        | MIN                       | TYP <sup>(1)</sup> MAX    | UNIT |

|---------------------------------|--------------------------------------------------------------|----------------------------------------|---------------------------|---------------------------|------|

| DSI                             |                                                              |                                        |                           |                           |      |

| t <sub>GS</sub>                 | DSI LP glitch suppression pulse width                        |                                        |                           | 300                       | ps   |

| LVDS                            |                                                              |                                        | Ш                         |                           | -1   |

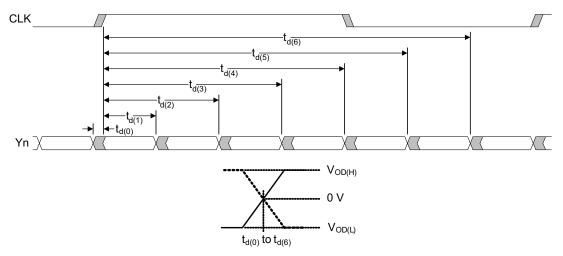

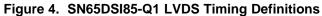

| t <sub>c</sub>                  | Output clock period                                          |                                        | 6.49                      | 40                        | ns   |

| t <sub>w</sub>                  | High-level output clock (CLK) pulse duration                 |                                        |                           | 4/7 t <sub>c</sub>        | ns   |

| t <sub>0</sub>                  | Delay time, CLK↑ to 1st serial bit position                  |                                        | -0.15                     | 0.15                      | ns   |

| t <sub>1</sub>                  | Delay time, CLK↑ to 2nd serial bit position                  |                                        | 1/7 t <sub>c</sub> – 0.15 | 1/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>2</sub>                  | Delay time, CLK↑ to 3rd serial bit position                  | t <sub>c</sub> = 6.49 ns;              | 2/7 t <sub>c</sub> – 0.15 | 2/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>3</sub>                  | Delay time, CLK↑ to 4th serial bit position                  | Input clock jitter < 25 ps<br>(REFCLK) | 3/7 t <sub>c</sub> - 0.15 | 3/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>4</sub>                  | Delay time, CLK↑ to 5th serial bit position                  | See Figure 4                           | 4/7 t <sub>c</sub> – 0.15 | 4/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>5</sub>                  | Delay time, CLK↑ to 6th serial bit position                  |                                        | 5/7 t <sub>c</sub> - 0.15 | 5/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>6</sub>                  | Delay time, CLK↑ to 7th serial bit position                  |                                        | 6/7 t <sub>c</sub> – 0.15 | 6/7 t <sub>c</sub> + 0.15 | ns   |

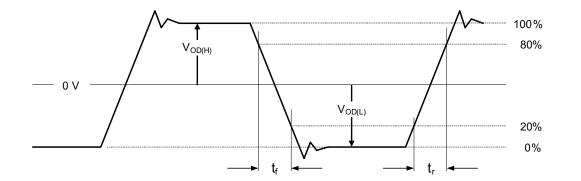

| t <sub>r</sub>                  | Differential output rise-time                                | San Figure 4                           | 180                       | FOO                       |      |

| t <sub>f</sub>                  | Differential output fall-time                                | See Figure 4                           | 160                       | 500                       | ps   |

|                                 | LVDS CLK A to CLK B skew                                     |                                        | -10                       | 10                        | ps   |

| EN, ULPS, R                     | ESET                                                         |                                        |                           |                           |      |

| t <sub>en</sub>                 | Enable time from EN or ULPS; see                             | t <sub>c(o)</sub> = 12.9 ns            |                           | 1                         | ms   |

| t <sub>dis</sub>                | Disable time to standby                                      | t <sub>c(o)</sub> = 12.9 ns            |                           | 0.1                       | ms   |

| t <sub>reset</sub>              | Reset Time                                                   |                                        | 10                        |                           | ms   |

| REFCLK                          |                                                              |                                        |                           |                           |      |

| F <sub>REFCLK</sub>             | REFCLK Freqeuncy. Supported frequencies:<br>25 MHz - 15 4MHz |                                        | 25                        | 154                       | MHz  |

| t <sub>r</sub> , t <sub>f</sub> | REFCLK rise and fall time                                    |                                        | 100ps                     | 1ns                       | s    |

| t <sub>pj</sub>                 | REFCLK Peak-to-Peak Phase Jitter                             |                                        |                           | 50                        | ps   |

| Duty                            | REFCLK Duty Cycle                                            |                                        | 40%                       | 50% 60%                   |      |

| REFCLK or I                     | DSI CLK (DACP/N, DBCP/N)                                     |                                        |                           |                           |      |

|                                 | SSC enabled Input CLK center spread depth <sup>(2)</sup>     |                                        | 0.5%                      | 1% 2%                     |      |

| SSC_CLKIN                       | Modulation Frequency Range                                   |                                        | 30                        | 60                        | kHz  |

All typical values are at V<sub>CC</sub> = 1.8 V and T<sub>A</sub> = 25°C

For EMI reduction purpose, SN65DSI85-Q1 supports the center spreading of the LVDS CLK output through the REFCLK or DSI CLK input. The center spread CLK input to the REFCLK or DSI CLK is passed through to the LVDS CLK output A\_CLKP/N and/or B\_CLKP/N.

## 7 Parameter Measurement Information

Figure 1. DSI HS Mode Receiver Timing Definitions

Figure 2. DSI Receiver Voltage Definitions

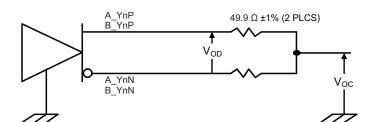

Figure 3. Test Load and Voltage Definitions for LVDS Outputs

STRUMENTS

AS

## **Parameter Measurement Information (continued)**

- (1) See the ULPS section of the data sheet for the ULPS entry and exit sequence.

- (2) ULPS entry and exit protocol and timing requirements must be met according to the MIPI DPHY specification.

Figure 5. ULPS Timing Definition

## 8 Detailed Description

## 8.1 Overview

The SN65DSI85-Q1 device is an AEC-Q100 qualified, 2-channel MIPI DSI to dual-link LVDS transmitter. The device features a dual-channel MIPI D-PHY receiver front-end configurable for 1 to 4 data lanes per channel operating at 1 Gbps/lane for a maximum input bandwidth of 8 Gbps. This device decodes MIPI DSI 18-bpp RGB666 and 24-bpp RGB888 data stream and converts it to an LVDS output operating at pixel-clock frequencies of 25 MHz to 154 MHz. The LVDS output can be configured as a dual-link LVDS, two single-link LVDS, or a single-link LVDS output interface with four data lanes per link.

## 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

SN65DSI85-Q1 ZHCSFS6B-JULY 2016-REVISED JUNE 2018

## 8.3 Feature Description

#### 8.3.1 Reset Implementation

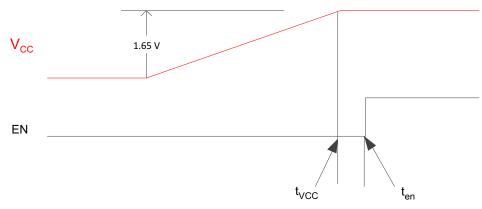

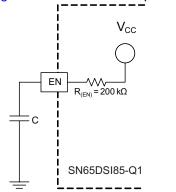

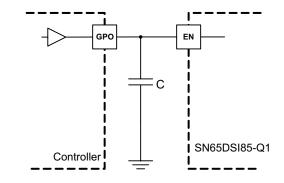

When the EN pin is deasserted (low), the SN65DSI85-Q1 device is in SHUTDOWN or RESET state. In this state, CMOS inputs are ignored, the MIPI D-PHY inputs are disabled and outputs are high impedance. Transitioning the EN input from a low to a high level after the  $V_{CC}$  supply has reached the minimum operating voltage as shown in Figure 6 is critical. This transition is achieved by a control signal to the EN input, or by an external capacitor connected between EN and GND.

When implementing the external capacitor, the size of the external capacitor depends on the power up ramp of the  $V_{CC}$  supply, where a slower ramp-up results in a larger value external capacitor. See the latest reference schematic for the SN65DSI85-Q1 device and, or consider an approximately 200-nF capacitor as a reasonable first estimate for the size of the external capacitor.

Figure 7 and Figure 8 show both EN implementations.

Figure 7. External Capacitor Controlled EN

When the SN65DSI85-Q1 is reset while  $V_{CC}$  is high, the EN pin must be held low for at least 10 ms before being asserted high as described in Table 1 to be sure that the device is properly reset. The DSI CLK lane MUST be in HS and the DSI data lanes MUST be driven to LP11 while the device is in reset before the EN pin is asserted per the timing described in Table 1.

### 8.3.2 Initialization Setup

Use the following initialization sequence to setup the SN65DSI85-Q1. This sequence is required for proper operation of the device. Steps 9 through 11 in the sequence are optional.

For additional information see Figure 6.

## Feature Description (continued)

| INITIALIZATION<br>SEQUENCE<br>NUMBER | INITIALIZATION SEQUENCE DESCRIPTION                                                                                                                            |  |  |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Init seq 1                           | Power on                                                                                                                                                       |  |  |  |  |  |  |  |

| Init seq 2                           | After power is applied and stable, the DSI CLK lanes MUST be in HS state and the DSI data lanes MUST be driven to LP11 state                                   |  |  |  |  |  |  |  |

| Init seq 3                           | Set EN pin to Low                                                                                                                                              |  |  |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |  |  |

| Init seq 4                           | Tie EN pin to High                                                                                                                                             |  |  |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |  |  |

| Init seq 5                           | Initialize all CSR registers to their appropriate values based on the implementation (The SN65DSI8x is not functional until the CSR registers are initialized) |  |  |  |  |  |  |  |

| Init seq 6                           | Set the PLL_EN bit (CSR 0x0D.0)                                                                                                                                |  |  |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |  |  |

| Init seq 7                           | Set the SOFT_RESET bit (CSR 0x09.0)                                                                                                                            |  |  |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |  |  |

| Init seq 8                           | Change DSI data lanes to HS state and start DSI video stream                                                                                                   |  |  |  |  |  |  |  |

| Wait 5 ms <sup>(1)</sup>             |                                                                                                                                                                |  |  |  |  |  |  |  |

| Init seq 9                           | Read back all resisters and confirm they were correctly written                                                                                                |  |  |  |  |  |  |  |

| Init seq 10                          | Write 0xFF to CSR 0xE5 to clear the error registers                                                                                                            |  |  |  |  |  |  |  |

| Wait 1 ms <sup>(1)</sup>             |                                                                                                                                                                |  |  |  |  |  |  |  |

| Init seq 11                          | Read CSR 0xE5. If CSR 0xE5!= 0x00, then go back to step #2 and re-initialize                                                                                   |  |  |  |  |  |  |  |

#### **Table 1. Initialization Sequence**

(1) Minimum recommended delay. This value can be exceeded.

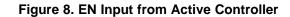

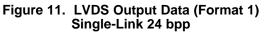

### 8.3.3 LVDS Output Formats

The SN65DSI85-Q1 device processes DSI packets and produces video data driven to the LVDS interface in an industry standard format. Single-Link LVDS and Dual-Link LVDS are supported by the SN65DSI85-Q1 device. When the LVDS output is implemented in a Dual-Link configuration, channel A carries the odd pixel data, and channel B carries the even pixel data. During conditions such as the default condition, and some video synchronization periods, where no video stream data is passing from the DSI input to the LVDS output, the SN65DSI85-Q1 device transmits zero value pixel data on the LVDS outputs while maintaining transmission of the vertical sync and horizontal sync status.

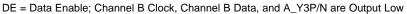

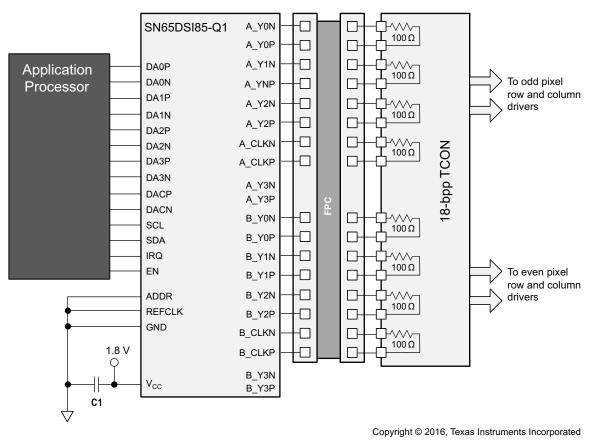

Figure 9 shows a Single-Link LVDS 18-bpp application.

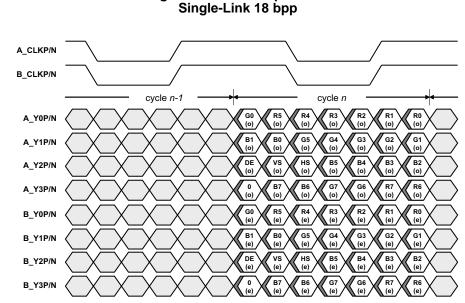

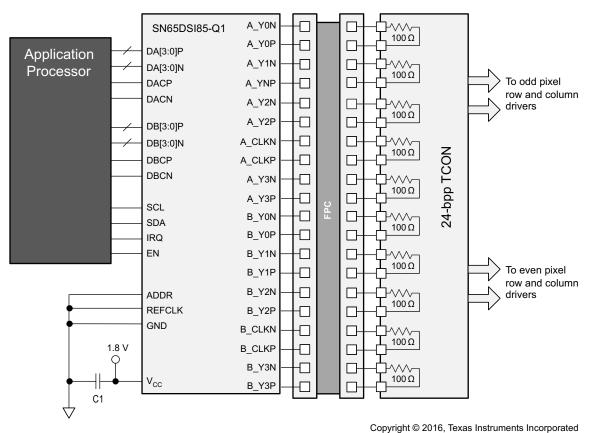

Figure 10 shows a Dual-Link 24-bpp application using Format 2, controlled by CHA\_24BPP\_FORMAT1 (CSR 0x18.1) and CHB\_24BPP\_FORMAT1 (CSR 0x18.0). In data Format 2, the two MSB per color are transferred on the Y3P/N LVDS lane.

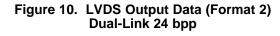

Figure 11 shows a 24 bpp Single-Link application using Format 1. In data Format 1, the two LSB per color are transferred on the Y3P/N LVDS lane.

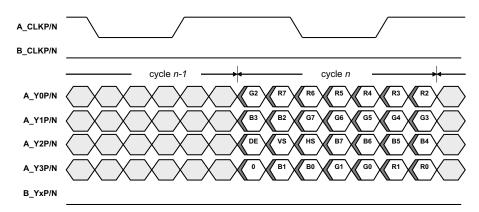

Figure 12 shows a Single-Link LVDS application where 24 bpp data is received from DSI and converted to 18 bpp data for transmission to an 18 bpp panel. This application is configured by setting CHA\_24BPP\_FORMAT1 (CSR 0x18.1) to 1 and CHA\_24BPP\_MODE (CSR 0x18.3) to 0. In this configuration, the SN65DSI85-Q1 will not transmit the 2 LSB per color since the Y3P/N LVDS lane is disabled.

### NOTE

Note: Figure 9, Figure 10, Figure 11, and Figure 12 only illustrate a few example applications for the SN65DSI85-Q1. Other applications are also supported.

Figure 9. LVDS Output Data

DE = Data Enable; (o) = Odd Pixels; (e) = Even Pixels

DE = Data Enable; Channel B Clock and Data are Output Low

A\_CLKP/N B\_CLKP/N cycle n-1 cycle n A\_Y0P/N G2 R7 R6 R5 R4 R R2 A\_Y1P/N G3 в3 B2 DE A\_Y2P/N A\_Y3P/N B\_YxP/N

DE = Data Enable; Channel B Clock, Channel B Data, and A\_Y3P/N are Output Low; Channel B Clock, Channel B Data, and A\_Y3P/N are Output Low

Figure 12. LVDS Output Data (Format 1) 24 bpp to Single-Link 18 bpp Conversion

SN65DSI85-Q1 ZHCSFS6B – JULY 2016 – REVISED JUNE 2018

www.ti.com.cn

## 8.3.4 DSI Lane Merging

The SN65DSI85-Q1 supports four DSI data lanes per input channel, and may be configured to support one, two, or three DSI data lanes per channel. Unused DSI input pins on the SN65DSI85-Q1 should be left unconnected or driven to LP11 state. The bytes received from the data lanes are merged in HS mode to form packets that carry the video stream. DSI data lanes are bit and byte aligned.

Figure 13 shows the lane merging function for each channel; 4-Lane, 3-Lane, and 2-Lane modes are illustrated

| HS BYTES TRANSMITTED (n) IS INTEGER MULTIPLE OF 4                                                                                                                                                                                                                                                                                                                                   | HS BYTES TRANSMITTED (n) IS INTEGER MULTIPLE OF 3                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LANE 0     SOT     BYTE 0     BYTE 4     BYTE 8     BYTE n-4     EOT       LANE 1     SOT     BYTE 1     BYTE 5     BYTE 9     BYTE n-3     EOT       LANE 2     SOT     BYTE 2     BYTE 6     BYTE 10     BYTE n-2     EOT       LANE 3     SOT     BYTE 3     BYTE 7     BYTE 11     BYTE n-1     EOT                                                                             | LANE 0     SOT     BYTE 0     BYTE 3     BYTE 6     BYTE n-3     EOT       LANE 1     SOT     BYTE 1     BYTE 4     BYTE 7     BYTE n-2     EOT       LANE 2     SOT     BYTE 2     BYTE 5     BYTE 8     BYTE n-1     EOT |

|                                                                                                                                                                                                                                                                                                                                                                                     | HS BYTES TRANSMITTED (n) IS 1 LESS THAN INTEGER MULTIPLE OF 3                                                                                                                                                              |

| HS BYTES TRANSMITTED (n) IS 1 LESS THAN INTEGER MULTIPLE OF 4           LANE 0         SOT         BYTE 0         BYTE 4         BYTE 8         BYTE n-3         EOT           LANE 1         SOT         BYTE 1         BYTE 5         BYTE 9         BYTE n-2         EOT           LANE 2         SOT         BYTE 2         BYTE 6         BYTE 10         BYTE n-1         EOT | LANE 0     SOT     BYTE 0     BYTE 3     BYTE 6     BYTE n-2     EOT       LANE 1     SOT     BYTE 1     BYTE 4     BYTE 7     BYTE n-1     EOT       LANE 2     SOT     BYTE 2     BYTE 5     BYTE 8     EOT              |

| LANE 3 SOT BYTE 3 BYTE 7 BYTE 11 EOT                                                                                                                                                                                                                                                                                                                                                | HS BYTES TRANSMITTED (n) IS 2 LESS THAN INTEGER MULTIPLE OF 3                                                                                                                                                              |

| HS BYTES TRANSMITTED (n) IS 2 LESS THAN INTEGER MULTIPLE OF 4 LANE 0 SOT BYTE 0 BYTE 4 BYTE 8 BYTE n-2 EOT LANE 1 SOT BYTE 1 BYTE 5 BYTE 9 BYTE n-1 EOT LANE 2 SOT BYTE 2 BYTE 6 BYTE 10 EOT                                                                                                                                                                                        | LANE 0     SOT     BYTE0     BYTE3     BYTE6     BYTE n-1     EOT       LANE 1     SOT     BYTE 1     BYTE 4     BYTE 7     EOT       LANE 2     SOT     BYTE2     BYTE5     BYTE8     EOT                                 |

| LANE 3 SOT BYTE 3 BYTE 7 BYTE 11 EOT                                                                                                                                                                                                                                                                                                                                                | 3 DSI Data Lane Configuration                                                                                                                                                                                              |

| HS BYTES TRANSMITTED (n) IS 3 LESS THAN INTEGER MULTIPLE OF 4                                                                                                                                                                                                                                                                                                                       | HS BYTES TRANSMITTED (n) IS INTEGER MULTIPLE OF 2                                                                                                                                                                          |

| LANE 0 SOT BYTE 0 BYTE 4 BYTE 8 BYTE n-1 EOT LANE 1 SOT BYTE 1 BYTE 5 BYTE 9 EOT LANE 2 SOT BYTE 2 BYTE 6 BYTE 10 EOT                                                                                                                                                                                                                                                               | LANE 0         SOT         BYTE 0         BYTE 2         BYTE 4         BYTE n2         EOT           LANE 1         SOT         BYTE 1         BYTE 3         BYTE 5         BYTE n-1         EOT                         |

|                                                                                                                                                                                                                                                                                                                                                                                     | HS BYTES TRANSMITTED (n) IS 1 LESS THAN INTEGER MULTIPLE OF 2                                                                                                                                                              |

| 4 DSI Data Lane Configuration (default)                                                                                                                                                                                                                                                                                                                                             | LANE 0 SOT BYTE 0 BYTE 2 BYTE 4 BYTE n-1 EOT                                                                                                                                                                               |

2 DSI Data Lane Configuration

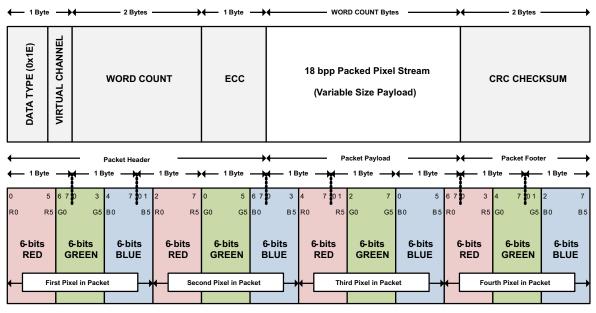

### 8.3.5 DSI Pixel Stream Packets

The SN65DSI85-Q1 processes 18-bpp (RGB666) and 24-bpp (RGB888) DSI packets on each channel as shown in Figure 14, Figure 15, and Figure 16.

| ←        | - 1 Byte                 | • →             | ←      |            | — 2 By  | /tes |         |             |                                                                   | - 1 Byte  | $\rightarrow$ | •      |            |           | WOF | D COU              | NT Byte     | es - |         |              | ▶      |         | <u> </u>     | ytes |         | <u> </u>     |

|----------|--------------------------|-----------------|--------|------------|---------|------|---------|-------------|-------------------------------------------------------------------|-----------|---------------|--------|------------|-----------|-----|--------------------|-------------|------|---------|--------------|--------|---------|--------------|------|---------|--------------|

|          | <b>DATA TYPE (0</b> х2E) | VIRTUAL CHANNEL |        | v          | /ORD    | со   | UNT     |             | ECC 18 bpp Loosely Packed Pixel Stream<br>(Variable Size Payload) |           |               |        |            |           |     |                    |             |      |         |              |        |         | IEC          | KSU  | м       |              |

| <b>↓</b> | – 1 Byte                 | • →             | _<br>← |            | cket He |      | - 1 By  |             | •                                                                 | - 1 Byte  | <b>→</b>      | ←<br>← | - 1 Byte   |           |     | acket P<br>- 1 Byt |             | →•   | – 1 By  | /te —        | →<br>← |         | Packet       |      |         | →<br>/te →   |

| 0 1      | 2<br>R0                  | 7<br>R5         |        | 2<br>G0    | 7<br>G5 |      | 2<br>B0 | 7<br>B5     |                                                                   | 2<br>R0   | 7<br>R5       |        | 2<br>G0    | 7<br>G5   |     | 2<br>B0            | 7<br>B5     |      | 2<br>R0 | 7<br>Re      |        | 2<br>G0 | 7<br>G5      |      | 2<br>B0 | 7<br>B5      |

|          |                          | oits<br>ED      |        | 6-b<br>GRE |         |      |         | oits<br>.UE |                                                                   | 6-b<br>RE |               |        | 6-b<br>GRI |           |     | -                  | bits<br>.UE |      |         | -bits<br>RED |        |         | bits<br>REEN |      | -       | -bits<br>LUE |

| ←        |                          | -               | Fir    | st Pixel i | n Packe | et   | -       |             | •                                                                 |           |               | Seco   | nd Pixe    | l in Pacl | ket |                    |             | -    |         | -            | Thi    | rd Pixe | el in Pack   | iet  |         | •            |

Variable Size Payload (Three Pixels Per Nine Bytes of Payload) -

Figure 14. 18-bpp (Loosely Packed) DSI Packet Structure

Variable Size Payload (Four Pixels Per Nine Bytes of Payload)

Figure 15. 18-bpp (Tightly Packed) DSI Packet Structure

INSTRUMENTS

**FEXAS**

www.ti.com.cn

Figure 16. 24-bpp DSI Packet Structure

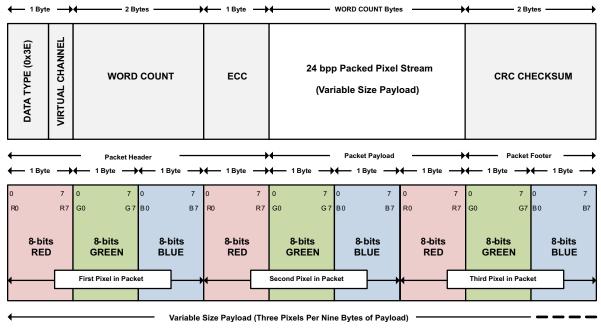

## 8.3.6 DSI Video Transmission Specifications

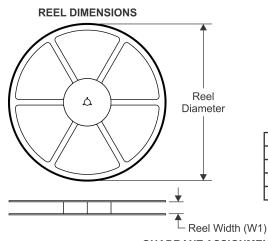

The SN65DSI85-Q1 supports burst video mode and non-burst video mode with sync events or with sync pulses packet transmission as described in the DSI specification. The burst mode supports time-compressed pixel stream packets that leave added time per scan line for power savings LP mode. The SN65DSI85-Q1 requires a transition to LP mode once per frame to enable PHY synchronization with the DSI host processor; however, for a robust and low-power implementation, the transition to LP mode is recommended on every video line.