**OPA836, OPA2836**

ZHCS019J - JANUARY 2011 - REVISED MARCH 2021

| OPAv836 极任功耗        | 劫到劫给山  | <b>缶劫</b> 输λ | 电压反馈运算放大器 |

|---------------------|--------|--------------|-----------|

| UFAX0JU IXI IKI 切化、 | 北判北間山、 | 贝扎肋八、        | 电压区坝运异拟八硷 |

# 1 特性

• 低功耗:

Texas

INSTRUMENTS

- 电源电压: 2.5V 至 5.5V

- 静态电流:1mA(典型值)

- 断电模式: 0.5µA ( 典型值 )

- 带宽:205MHz

- 压摆率:560V/us

- 上升时间: 3ns (2VSTEP) ٠

- 稳定时间 (0.1%): 22ns (2VSTEP)

- 过驱恢复时间:60ns

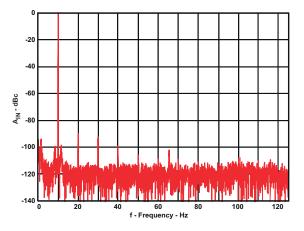

- SNR:在1kHz (1VRMS)时为0.00013% (-117.6dBc)

- THD:在1kHz (1VRMS)时为0.00003% (-130dBc)

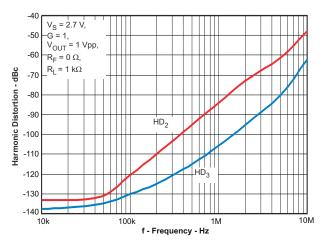

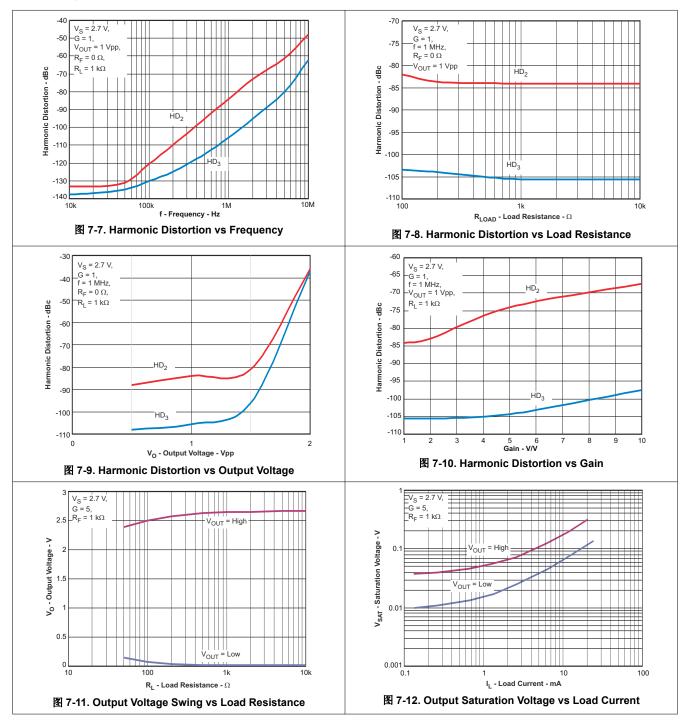

- HD2/HD3:在1MHz (2VPP)时为-85dBc/-105dBc

- 输入电压噪声: 4.6nV/ √ Hz (f = 100kHz)

- 输入失调电压:65µV(最大 ±400µV)

- CMRR : 116dB

- 输出电流驱动:50mA

- **RRO**: 轨到轨输出

- 输入电压范围: - 0.2V 到 +3.9V (5V 电源)

- 工作温度范围: - 40°C 至 +125°C

# 2 应用

- 低功耗信号调节

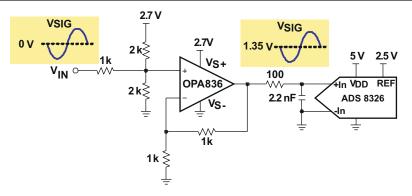

- 音频模数转换器 (ADC) 输入缓冲器

- 低功耗逐次逼近寄存器 (SAR) 和三角积分 (ΔΣ) ADC 驱动器

- • 便携式系统

- 低功耗系统

- 高密度系统

# 3 说明

OPA836 和 OPA2836 器件 (OPAx836) 为单通道和双 通道超低功耗、轨至轨输出、负电源轨输入、电压反馈 (VFB)运算放大器,依设计可由 2.5V 至 5.5V 范围内 的单电源或者 ±1.25V 至 ±2.75V 范围内的双电源供电 运行。这些轨至轨放大器每通道仅消耗 1mA 的电流, 单位增益带宽为 205MHz, 功耗/性能比处于先进水 平。

OPA836 和 OPA2836 器件同时拥有低功耗特性和出色 的高频性能,并且可提供其他同类器件所无法达到的性 能/功耗比,因此非常适合注重功耗的电池供电类便携 式应用。这些器件还具有节能模式,可将电流降至 1.5 µA以下,这对于电池供电类应用中的高频放大器 而言是极具吸引力的解决方案。

OPA836 RUN 封装选件包含集成的增益设置电阻器, 因此可在印刷电路板上实现超小的尺寸 (约 2.00mm × 2.00mm)。通过在 PCB 上添加电路迹线,可实现 +1, -1, -1.33, +2, +2.33, -3, +4, -4, +5、-5.33、+6.33、-7、+8的增益和-0.1429、-0.1875、-0.25、-0.33、-0.75的反相衰减。有关 详细信息,请参见表 9-1 和表 9-2。

OPA836 和 OPA2836 器件在 - 40°C 至 +125°C 的扩 展工业温度范围内运行。

**竖**件信息(1)

| 器件型号    | 封装         | 封装尺寸(标称值)       |

|---------|------------|-----------------|

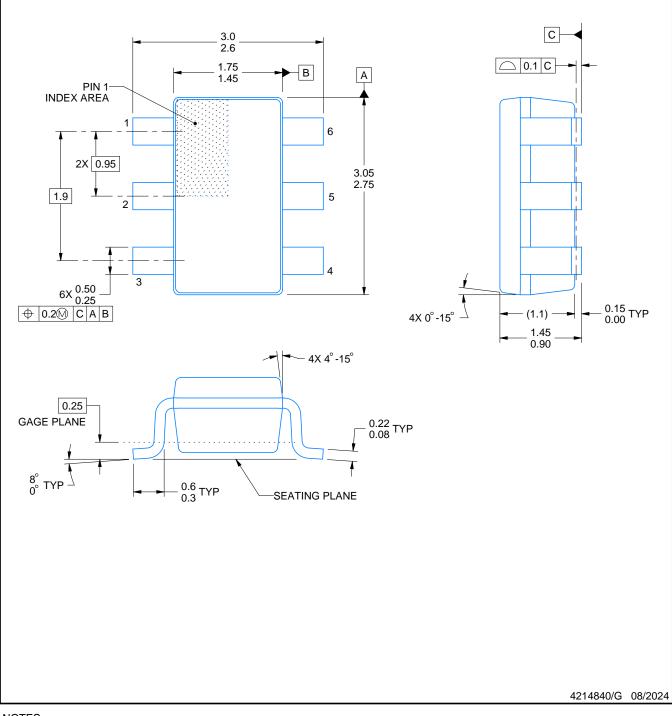

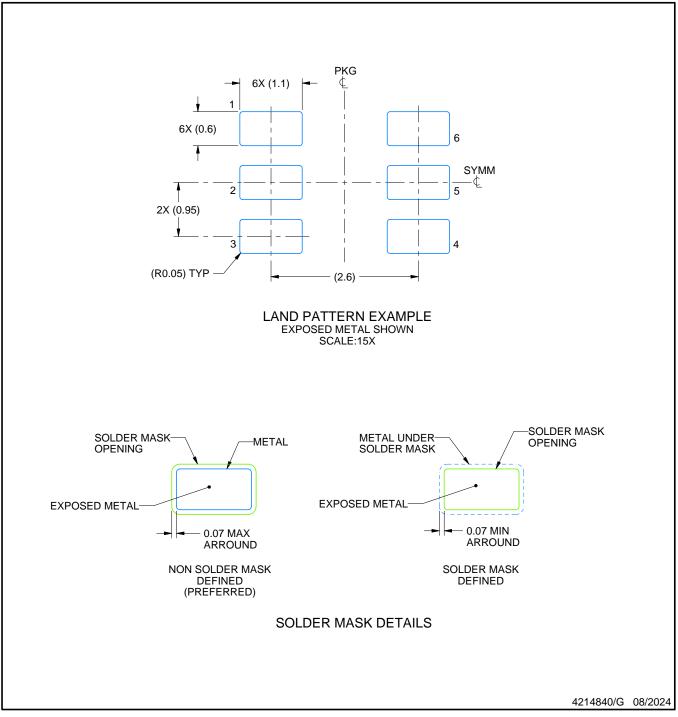

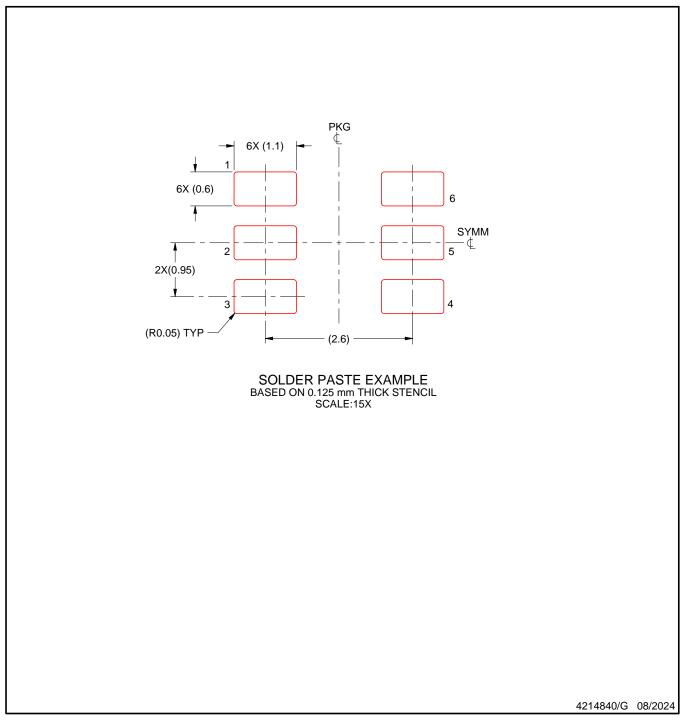

| OPA836  | SOT-23 (6) | 2.90mm × 1.60mm |

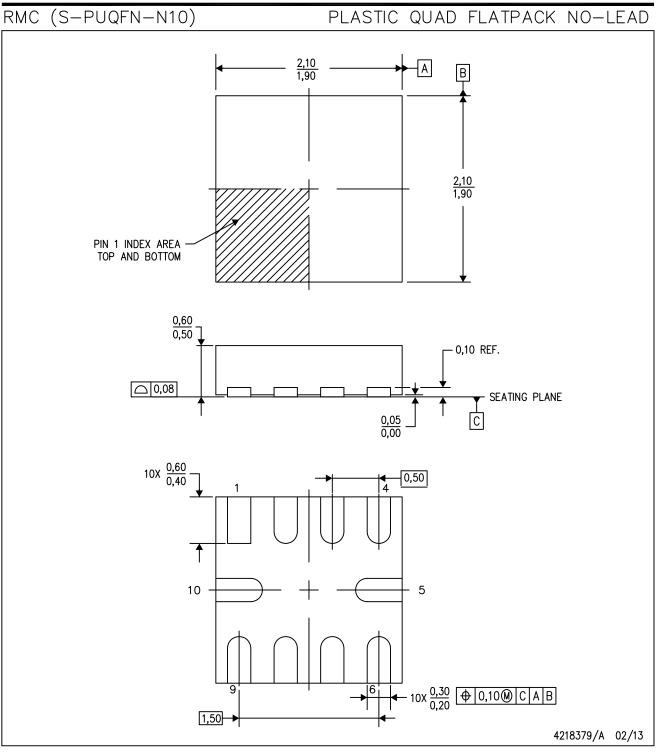

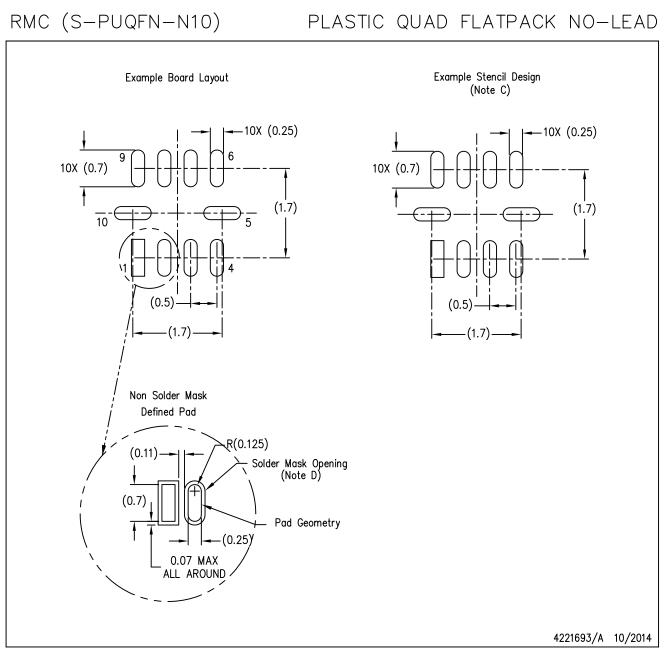

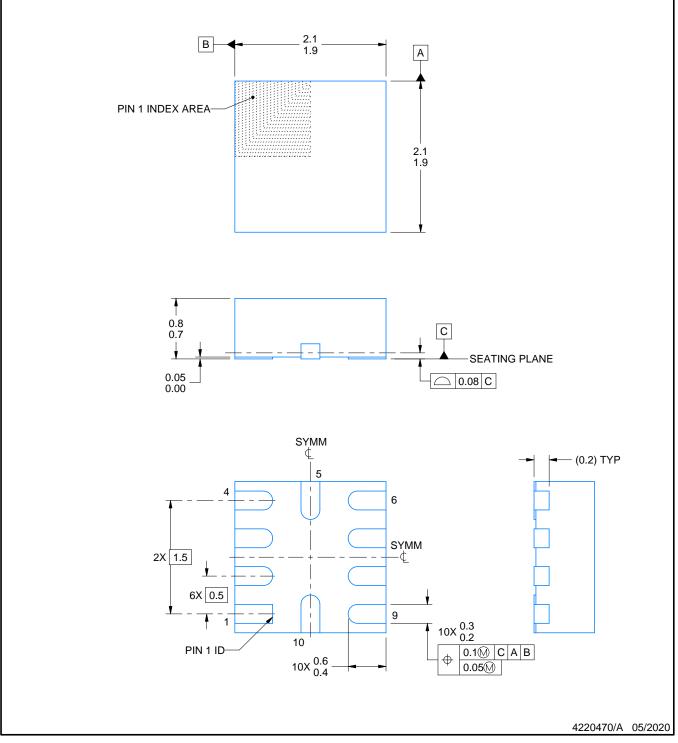

| UFA030  | WQFN (10)  | 2.00mm x 2.00mm |

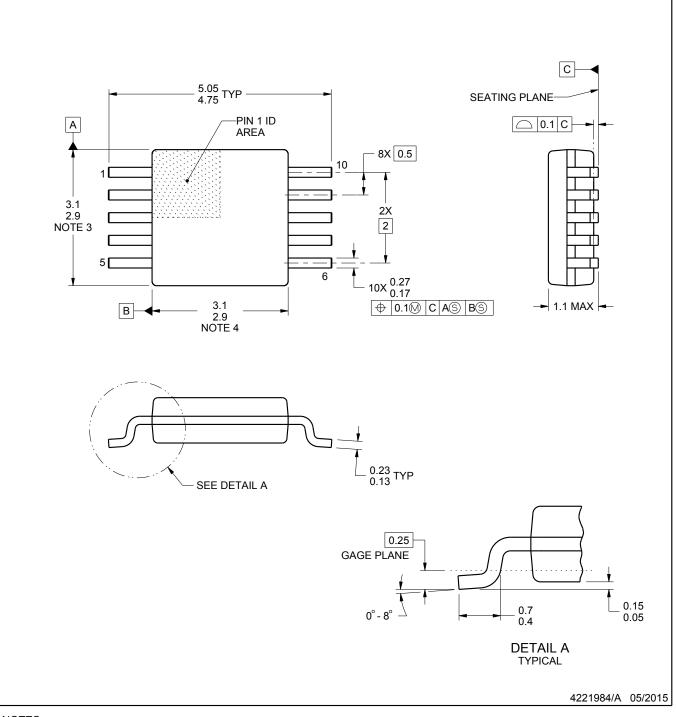

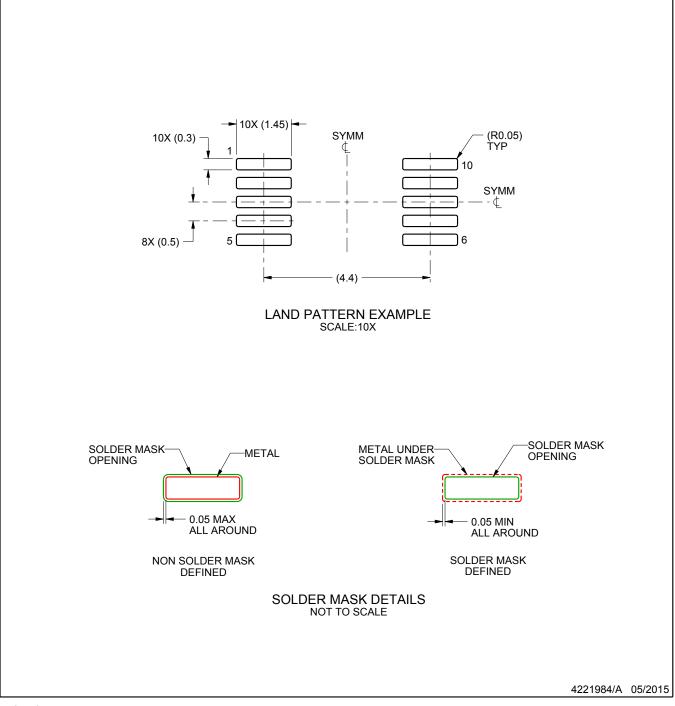

|         | SOIC (8)   | 4.90mm × 3.91mm |

| OPA2836 | VSSOP (10) | 3.00mm × 3.00mm |

| 0FA2030 | UQFN (10)  | 2.00mm x 2.00mm |

|         | WQFN (10)  | 2.00mm x 2.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

谐波失真与频率间的关系

# **Table of Contents**

| 1 | 特性                                                     | 1 |

|---|--------------------------------------------------------|---|

|   | 应用                                                     | 1 |

| 3 | 说明                                                     | 1 |

| 4 | Revision History                                       | 2 |

| 5 | Device Comparison Table                                | 5 |

| 6 | Pin Configuration and Functions                        | 6 |

| 7 | Specifications                                         | 8 |

|   | 7.1 Absolute Maximum Ratings                           | 8 |

|   | 7.2 ESD Ratings                                        | 8 |

|   | 7.3 Recommended Operating Conditions                   | 8 |

|   | 7.4 Thermal Information: OPA836                        | 8 |

|   | 7.5 Thermal Information: OPA2836                       |   |

|   | 7.6 Electrical Characteristics: V <sub>S</sub> = 2.7 V | 9 |

|   | 7.7 Electrical Characteristics: V <sub>S</sub> = 5 V1  | 2 |

|   | 7.8 Typical Characteristics: V <sub>S</sub> = 2.7 V1   | 5 |

|   | 7.9 Typical Characteristics: V <sub>S</sub> = 5 V 2    | 0 |

| 8 | Detailed Description                                   | 5 |

|   | 8.1 Overview                                           | 5 |

|   | 8.2 Functional Block Diagrams2                         | 5 |

| 8.3 Feature Description                 | 25 |

|-----------------------------------------|----|

| 8.4 Device Functional Modes             |    |

| 9 Application and Implementation        |    |

| 9.1 Application Information             |    |

| 9.2 Typical Applications                |    |

| 10 Power Supply Recommendations         |    |

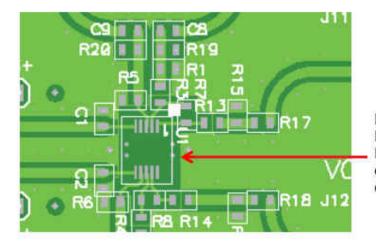

| 11 Layout                               | 42 |

| 11.1 Layout Guidelines                  |    |

| 11.2 Layout Example                     |    |

| 12 Device and Documentation Support     | 44 |

| 12.1 Device Support                     |    |

| 12.2 接收文档更新通知                           |    |

| 12.3 支持资源                               | 44 |

| 12.4 静电放电警告                             |    |

| 12.5 术语表                                |    |

| 12.6 Trademarks                         |    |

| 13 Mechanical, Packaging, and Orderable |    |

| Information                             |    |

|                                         |    |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| C     | hanges from Revision I (October 2016) to Revision J (March 2021)                                                                                                                                                                                                                                  | Page           |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •     | 更新了整个文档的表、图和交叉参考的编号格式                                                                                                                                                                                                                                                                             | 1              |

| •     | Changed the input impedance common mode conditions From: = 200    1.2 k Ω    pF (Typical) To                                                                                                                                                                                                      | ): 100    1.2  |

|       | M Ω    pF (Typical)                                                                                                                                                                                                                                                                               | 9              |

| •     | Changed the input impedance differential mode conditions From: = 200    1 k Ω    pF (Typical) To    pF (Typical)                                                                                                                                                                                  |                |

| •     | Changed the input impedance common mode conditions From: = 200    1.2 k Q    pF (Typical) To                                                                                                                                                                                                      |                |

|       | M Ω    pF (Typical)                                                                                                                                                                                                                                                                               | 12             |

| •     | Changed the input impedance differential mode conditions From: = 200    1 k $\Omega$    pF (Typical) To                                                                                                                                                                                           | : 100    1 k Ω |

|       | pF (Typical)                                                                                                                                                                                                                                                                                      | 12             |

|       |                                                                                                                                                                                                                                                                                                   |                |

| C     | hanges from Revision H (September 2016) to Revision I (October 2016)                                                                                                                                                                                                                              | Page           |

|       | hanges from Revision H (September 2016) to Revision I (October 2016)<br>更改了整个数据表中各节的文本,使之更加清晰准确                                                                                                                                                                                                   |                |

| •     | - · · · · ·                                                                                                                                                                                                                                                                                       | 1              |

| •     | 更改了整个数据表中各节的文本,使之更加清晰准确                                                                                                                                                                                                                                                                           |                |

| •     | 更改了整个数据表中各节的文本,使之更加清晰准确<br>Changed "R <sub>G</sub> = ∞ Ω (open)" to "R <sub>G</sub> = open"                                                                                                                                                                                                       |                |

| •     | 更改了整个数据表中各节的文本,使之更加清晰准确<br>Changed "R <sub>G</sub> = ∞ Ω (open)" to "R <sub>G</sub> = open"<br>Changed "gain tracking is superior to using" to "gain drift is superior to the drift with"                                                                                                         |                |

| • • • | 更改了整个数据表中各节的文本,使之更加清晰准确<br>Changed "R <sub>G</sub> = ∞ Ω (open)" to "R <sub>G</sub> = open"<br>Changed "gain tracking is superior to using" to "gain drift is superior to the drift with"<br>Changed "results in degraded harmonic distortion" to "increases the harmonic distortion"             |                |

| •     | 更改了整个数据表中各节的文本,使之更加清晰准确<br>Changed "R <sub>G</sub> = $\infty \Omega$ (open)" to "R <sub>G</sub> = open"<br>Changed "gain tracking is superior to using" to "gain drift is superior to the drift with"<br>Changed "results in degraded harmonic distortion" to "increases the harmonic distortion" |                |

| • | Changed "Type" column header to "I/O" on <i>Pin Functions</i> table                                                        | . 6            |

|---|----------------------------------------------------------------------------------------------------------------------------|----------------|

| • | Reformatted header rows in Thermal Information: OPA836 and Thermal Information: OPA2836 tables                             | <mark>8</mark> |

| • | Reformatted Thermal Information table note                                                                                 | 8              |

| • | Reformatted Thermal Information table note                                                                                 | 9              |

| • | Deleted the word "linear" from Output section parameters in <i>Electrical Characteristics</i> V <sub>S</sub> = 2.7 V table | 9              |

| • | Deleted the word "linear" from Output section parameters in <i>Electrical Characteristics</i> V <sub>S</sub> = 5 V table   | .12            |

| • | Reformatted Development Support subsection                                                                                 | 44             |

|   |                                                                                                                            |                |

Page

Page

## Changes from Revision E (September 2013) to Revision F (June 2015)

| C | hanges from Revision D (October 2011) to Revision E (September 2013)   | Page |

|---|------------------------------------------------------------------------|------|

| • | 在文档中增加了 OPA2836 RMC 封装                                                 | 1    |

|   | Added RMC pin definitions to Pin Functions table                       |      |

| • | Deleted Packaging/Ordering Information table, leaving only note to POA | 8    |

| • | Added OPA2836 RMC package to Thermal Information table                 | 9    |

|   |                                                                        |      |

| С | hanges from Revision C (September 2011) to Revision D (September 2011)                         | Page           |

|---|------------------------------------------------------------------------------------------------|----------------|

| • | Removed Product Preview from OPA835IRUNT and OPA835IRUNR                                       | 5              |

| • | Removed Product Preview from OPA836IRUNT and OPA836IRUNR                                       | <mark>8</mark> |

| • | Changed typical value for resistor temperature coefficien parameter from TBD to < 10           | 9              |

| • | Changed "quiescent operating current" parameter to "quiescent operating current per amplifier" | 9              |

| • | Changed resistor temperature coefficient typical value from TBD to < 10                        | 12             |

| • | Changed "quiescent operating current" to "quiescent operating current per amplifier"           | 12             |

## Changes from Revision B (May 2011) to Revision C (August 2011)

在"说明"中添加了"OPA836 RUN 封装..."文本.....1 • Changed typical value for channel to channel crosstalk (OPA2836) parameter from TBD to - 120 dB............9 Changed the quiescent operating current ( $T_A = 25^{\circ}C$ ) minimum value from 0.8 mA to 0.7 mA......9 • Changed the minimum value for power supply rejection (±PSRR) parameter from 95 dB to 91 dB......9 Changed the power-down quiescent current test condition from  $\overline{PD} = 0.7$  V to  $\overline{PD} = 0.5$  V......9 Changed typical value for channel to channel crosstalk (OPA2836) parameter from TBD to - 120 dB...... 12 ٠ Changed the Common-mode rejection ratio Min value From: 97 dB To: 94 dB..... 12 • Added GAIN SETTING RESISTORS (OPA836I RUN ONLY) parameter to *Electrical Characteristics* table....12 ٠ Changed the power supply rejection (±PSRR) minimum value from: 97 dB to 94 dB.....12 Changed the Power-down quiescent current CONDITIONS From: PD = 0.7 V To: PD = 0.5 V......12 ٠ Changed the Power-down quiescent current Conditions From: PD = 0.7 V To: PD = 0.5 V...... 12 Added Figure Crosstalk vs Frequency......15

Page

# Changes from Revision A (March 2011) to Revision B (May 2011)

• 已将 OPA836 从"产品预发布"更改为"量产数据".....1

# **5** Device Comparison Table

| DEVICE  | BW (A <sub>V</sub> = 1)<br>(MHz) | SLEW RATE<br>(V/µs) | lq (+5 V)<br>(mA) | INPUT NOISE<br>(nV/ √ Hz) | RAIL-TO-RAIL<br>IN/OUT | DUALS   |

|---------|----------------------------------|---------------------|-------------------|---------------------------|------------------------|---------|

| OPA836  | 205                              | 560                 | 1                 | 4.6                       | - VS/Out               | OPA2836 |

| OPA835  | 30                               | 110                 | 0.25              | 9.3                       | - VS/Out               | OPA2835 |

| OPA365  | 50                               | 25                  | 5                 | 4.5                       | In/Out                 | OPA2365 |

| THS4281 | 95                               | 35                  | 0.75              | 12.5                      | In/Out                 |         |

| LMH6618 | 140                              | 45                  | 1.25              | 10                        | In/Out                 | LMH6619 |

| OPA830  | 310                              | 600                 | 3.9               | 9.5                       | - VS/Out               | OPA2830 |

# **6** Pin Configuration and Functions

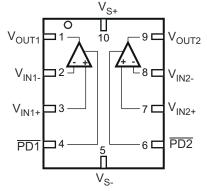

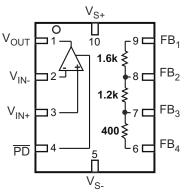

图 6-1. OPA2836 RUN, RMC Packages 10-Pin WQFN, UQFN Top View

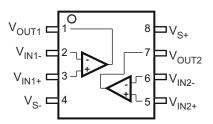

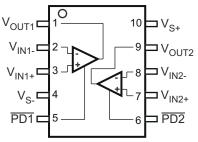

图 6-3. OPA2836 D Package 8-Pin SOIC Top View

图 6-2. OPA836 RUN Package 10-Pin WQFN Top View

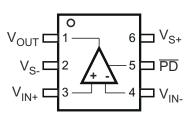

图 6-4. OPA836 DBV Package 6-Pin SOT-23 Top View

图 6-5. OPA2836 DGS Package 10-Pin VSSOP Top View

## 表 6-1. Pin Functions

| PIN                |        |      |                                                                                                     |       |               |                                                                                                      |                                                                                                        |  |

|--------------------|--------|------|-----------------------------------------------------------------------------------------------------|-------|---------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

|                    | OPA836 |      | OPA2836                                                                                             |       | I/O           | DESCRIPTION                                                                                          |                                                                                                        |  |

| NAME               | SOT-23 | WQFN | SOIC                                                                                                | VSSOP | WQFN,<br>UQFN |                                                                                                      |                                                                                                        |  |

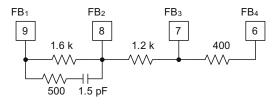

| FB <sub>1</sub>    |        | 9    |                                                                                                     |       |               | I/O                                                                                                  | Connection to top of 2.4-k $\Omega$ internal gain setting resistors                                    |  |

| FB <sub>2</sub>    |        | 8    |                                                                                                     |       |               | I/O                                                                                                  | Connection to junction of 1.8-k $\Omega$ and 2.4-k $\Omega$ internal gain setting resistors            |  |

| FB <sub>3</sub>    |        | 7    |                                                                                                     | _     | _             | I/O                                                                                                  | Connection to junction of 600- $\Omega$ and 1.8-k $\Omega$ internal gain setting resistors             |  |

| FB <sub>4</sub>    |        | 6    |                                                                                                     |       |               | I/O                                                                                                  | Connection to bottom of 600- $\Omega$ internal gain setting resistors                                  |  |

| PD                 | 5      | 4    |                                                                                                     |       | I             | Amplifier Power Down, low = low-power mode,<br>high = normal operation ( <b>PIN MUST BE DRIVEN</b> ) |                                                                                                        |  |

| PD1                |        |      | 5 4 I Amplifier 1 Power Down, low = low-power mode,<br>high = normal operation (PIN MUST BE DRIVEN) |       |               |                                                                                                      |                                                                                                        |  |

| PD2                |        | _    |                                                                                                     | 6 6   |               | I                                                                                                    | Amplifier 2 Power Down, low = low-power mode,<br>high = normal operation ( <b>PIN MUST BE DRIVEN</b> ) |  |

| V <sub>IN+</sub>   | 3      | 3    |                                                                                                     |       |               | I                                                                                                    | Amplifier noninverting input                                                                           |  |

| V <sub>IN</sub> –  | 4      | 2    |                                                                                                     |       |               | I                                                                                                    | Amplifier inverting input                                                                              |  |

| V <sub>IN1+</sub>  |        |      | 3                                                                                                   | 3     | 3             | I                                                                                                    | Amplifier 1 noninverting input                                                                         |  |

| V <sub>IN1</sub> - |        |      | 2                                                                                                   | 2     | 2             | I                                                                                                    | Amplifier 1 inverting input                                                                            |  |

| V <sub>IN2+</sub>  |        |      | 5                                                                                                   | 7     | 7             | I                                                                                                    | Amplifier 2 noninverting input                                                                         |  |

| V <sub>IN2</sub> – | ]      |      | 6                                                                                                   | 8     | 8             | I                                                                                                    | Amplifier 2 inverting input                                                                            |  |

| V <sub>OUT</sub>   | 1      | 1    | _                                                                                                   | —     | —             | 0                                                                                                    | Amplifier output                                                                                       |  |

| V <sub>OUT1</sub>  |        |      | 1                                                                                                   | 1     | 1             | 0                                                                                                    | Amplifier 1 output                                                                                     |  |

| V <sub>OUT2</sub>  | ] _    |      | 7                                                                                                   | 9     | 9             | 0                                                                                                    | Amplifier 2 output                                                                                     |  |

| V <sub>S+</sub>    | 6      | 10   | 8                                                                                                   | 10    | 10            | POW                                                                                                  | Positive power supply input                                                                            |  |

| V <sub>S -</sub>   | 2      | 5    | 4                                                                                                   | 4     | 5             | POW                                                                                                  | Negative power supply input                                                                            |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                                | MIN                    | MAX                   | UNIT |

|----------------------|--------------------------------|------------------------|-----------------------|------|

| $V_{S-}$ to $V_{S+}$ | Supply voltage                 |                        | 5.5                   | V    |

| VI                   | Input voltage                  | V <sub>S -</sub> - 0.7 | V <sub>S+</sub> + 0.7 | V    |

| V <sub>ID</sub>      | Differential input voltage     |                        | 1                     | V    |

| l <sub>l</sub>       | Continuous input current       |                        | 0.85                  | mA   |

| lo                   | Continuous output current      |                        | 60                    | mA   |

|                      | Continuous power dissipation   | See ∄<br>an<br>#77     | d                     |      |

| TJ                   | Maximum junction temperature   |                        | 150                   | °C   |

| T <sub>A</sub>       | Operating free-air temperature | - 40                   | 125                   | °C   |

| T <sub>stg</sub>     | Storage temperature            | - 65                   | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±6000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

|                    |                         | Machine model                                                                  | ±200  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                       | MIN  | NOM | MAX | UNIT |

|-----------------|-----------------------|------|-----|-----|------|

| V <sub>S+</sub> | Single supply voltage | 2.5  | 5   | 5.5 | V    |

| T <sub>A</sub>  | Ambient temperature   | - 40 | 25  | 125 | °C   |

# 7.4 Thermal Information: OPA836

|                               |                                              | OP            |               |      |

|-------------------------------|----------------------------------------------|---------------|---------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | DBV (SOT23-6) | RUN (WQFN-10) | UNIT |

|                               |                                              | 6 PINS        | 10 PINS       |      |

| R <sub>θ JA</sub>             | Junction-to-ambient thermal resistance       | 194           | 145.8         | °C/W |

| R <sub>θ JC(top)</sub>        | Junction-to-case (top) thermal resistance    | 129.2         | 75.1          | °C/W |

| R <sub>0 JB</sub>             | Junction-to-board thermal resistance         | 39.4          | 38.9          | °C/W |

| ΨJT                           | Junction-to-top characterization parameter   | 25.6          | 13.5          | °C/W |

| ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 38.9          | 104.5         | °C/W |

(1) For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics (SPRA953).

# 7.5 Thermal Information: OPA2836

| THERMAL METRIC <sup>(1)</sup> |                                              | D (SOIC-8) | (DGS) VSSOP,<br>MSOP-10 | (RUN)<br>WQFN-10 | RMC<br>(UQFN-10) | UNIT |

|-------------------------------|----------------------------------------------|------------|-------------------------|------------------|------------------|------|

|                               |                                              | 8 PINS     | 10 PINS                 | 10 PINS          | 10 PINS          |      |

| R <sub>0 JA</sub>             | Junction-to-ambient thermal resistance       | 150.1      | 206                     | 145.8            | 143.2            | °C/W |

| R <sub>0</sub> JCtop          | Junction-to-case (top) thermal resistance    | 83.8       | 75.3                    | 75.1             | 49.0             | °C/W |

| R <sub>0 JB</sub>             | Junction-to-board thermal resistance         | 68.4       | 96.2                    | 38.9             | 61.9             | °C/W |

| ΨJT                           | Junction-to-top characterization parameter   | 33.0       | 12.9                    | 13.5             | 3.3              | °C/W |

| ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 67.9       | 94.6                    | 104.5            | 61.9             | °C/W |

(1) For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics (SPRA953).

# 7.6 Electrical Characteristics: V<sub>S</sub> = 2.7 V

at  $V_{S+}$  = +2.7 V,  $V_{S-}$  = 0 V,  $V_{OUT}$  = 1  $V_{PP}$ ,  $R_F$  = 0  $\Omega$ ,  $R_L$  = 2 k  $\Omega$ , G = 1 V/V, input and output referenced to mid-supply,  $V_{IN\_CM}$  = mid-supply - 0.5 V.  $T_A$  = 25°C, unless otherwise noted.

| PARAMETER                               | TEST CONDITIONS                                                                                                              | MIN TYP M |          | TEST<br>LEVEL <sup>(1)</sup> |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------------------------------|

| AC PERFORMANCE                          |                                                                                                                              | I         |          |                              |

|                                         | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1                                                                              | 200       |          | 0                            |

| Small signal handwidth                  | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 2                                                                              | 100       | MHz      |                              |

| Small-signal bandwidth                  | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 5                                                                              | 26        | MHZ      | С                            |

|                                         | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10                                                                             | 11        |          |                              |

| Gain-bandwidth product                  | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10                                                                             | 110       | MHz      | С                            |

| Large-signal bandwidth                  | V <sub>OUT</sub> = 1 V <sub>PP</sub> , G = 2                                                                                 | 60        | MHz      | С                            |

| Bandwidth for 0.1-dB flatness           | V <sub>OUT</sub> = 1 V <sub>PP</sub> , G = 2                                                                                 | 25        | MHz      | С                            |

| Slew rate, rise                         | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 260       | V/µs     | С                            |

| Slew rate, fall                         | $V_{OUT}$ = 1 $V_{STEP}$ , G = 2                                                                                             | 240       | V/µs     | С                            |

| Rise time                               | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 4         | ns       | С                            |

| Fall time                               | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 4.5       | ns       | С                            |

| Settling time to 1%, rise               | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 15        | ns       | С                            |

| Settling time to 1%, fall               | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 15        | ns       | С                            |

| Settling time to 0.1%, rise             | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 30        | ns       | С                            |

| Settling time to 0.1%, fall             | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 25        | ns       | С                            |

| Settling time to 0.01%, rise            | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 50        | ns       | С                            |

| Settling time to 0.01%, fall            | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 45        | ns       | С                            |

| Overshoot/Undershoot                    | V <sub>OUT</sub> = 1 V <sub>STEP</sub> , G = 2                                                                               | 5%/3%     |          | С                            |

|                                         | f = 10 kHz, $V_{IN_{CM}}$ = mid-supply - 0.5 V                                                                               | - 133     |          | С                            |

| Second-order harmonic distortion        | f = 100 kHz, $V_{IN\_CM}$ = mid-supply - 0.5 V                                                                               | - 120     | dBc      | С                            |

|                                         | $f = 1 \text{ MHz}, V_{IN\_CM} = \text{mid-supply} - 0.5 \text{ V}$                                                          | - 84      |          | С                            |

|                                         | f = 10 kHz, $V_{IN CM}$ = mid-supply - 0.5 V                                                                                 | - 137     |          | С                            |

| Third-order harmonic distortion         | f = 100 kHz, $V_{IN CM}$ = mid-supply - 0.5 V                                                                                | - 130     | dBc      | С                            |

|                                         | f = 1 MHz, V <sub>IN CM</sub> = mid-supply - 0.5 V                                                                           | - 105     |          | С                            |

| Second-order intermodulation distortion | f = 1 MHz, 200-kHz Tone Spacing,<br>V <sub>OUT</sub> Envelope = 1 V <sub>PP</sub><br>V <sub>IN_CM</sub> = mid-supply - 0.5 V | - 90      | dBc      | С                            |

| Third-order intermodulation distortion  | on distortion                                                                                                                |           | dBc      | С                            |

| Input voltage noise                     | f = 100 KHz                                                                                                                  | 4.6       | nV/√ Hz  | С                            |

| Voltage noise 1/f corner frequency      |                                                                                                                              | 215       | Hz       | С                            |

| Input current noise                     | f = 1 MHz                                                                                                                    | 0.75      | pA/ √ Hz | С                            |

Copyright © 2021 Texas Instruments Incorporated

# 7.6 Electrical Characteristics: V<sub>S</sub> = 2.7 V (continued)

| PARAMETER                                 | TEST CONDITIONS                                                     | MIN    | ТҮР              | MAX  | UNIT      | TEST<br>LEVEL <sup>(1</sup> |

|-------------------------------------------|---------------------------------------------------------------------|--------|------------------|------|-----------|-----------------------------|

| AC PERFORMANCE (continued)                |                                                                     |        |                  |      |           |                             |

| Current noise 1/f corner frequency        |                                                                     |        | 31.7             |      | kHz       | С                           |

| Overdrive recovery time, over/under       | Overdrive = 0.5 V                                                   |        | 55/60            |      | ns        | С                           |

| Closed-loop output impedance              | f = 100 kHz                                                         |        | 0.02             |      | Ω         | С                           |

| Channel-to-channel crosstalk (OPA2836)    | f = 10 kHz                                                          |        | - 120            |      | dB        | С                           |

| DC PERFORMANCE                            |                                                                     |        |                  |      |           |                             |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                                     | 100    | 125              |      | dB        | А                           |

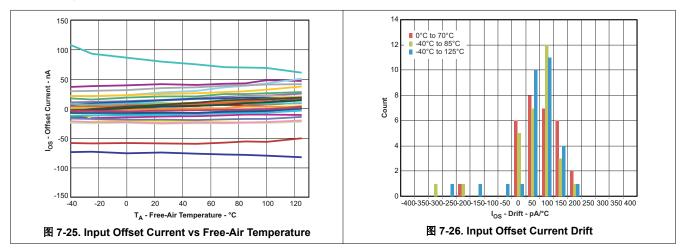

|                                           | T <sub>A</sub> = 25°C                                               | - 400  | ±65              | 400  |           | А                           |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 | - 680  |                  | 680  |           |                             |

| Input referred offset voltage             | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        | - 760  |                  | 760  | μV        | в                           |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                              | - 1060 |                  | 1060 |           |                             |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 | - 6.2  | ±1               | 6.2  |           |                             |

| Input offset voltage drift <sup>(2)</sup> | $T_A = -40^{\circ}C$ to $85^{\circ}C$                               | - 6    | ±1               | 6    | µV/°C     | В                           |

|                                           | $T_{A} = -40^{\circ}$ C to 125°C                                    | - 6.6  | ±1.1             | 6.6  |           |                             |

|                                           | $T_A = 25^{\circ}C$                                                 | 300    | 650              | 1000 |           | A                           |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 | 190    |                  | 1400 |           |                             |

| Input bias current <sup>(3)</sup>         | $T_A = -40^{\circ}C$ to $85^{\circ}C$                               | 120    |                  | 1500 | nA        | в                           |

|                                           | T <sub>A</sub> = -40°C to 125°C                                     | 120    |                  | 1800 |           |                             |

|                                           | T <sub>A</sub> = 0°C to 70°C                                        | - 2    | ±0.33            | 2    | - 1       |                             |

| Input bias current drift <sup>(2)</sup>   | $T_A = -40^{\circ}C$ to $85^{\circ}C$                               | - 1.9  | ±0.32            | 1.9  |           | в                           |

|                                           | $T_{A} = -40^{\circ}C \text{ to } 125^{\circ}C$                     | - 2.1  | ±0.37            | 2.1  |           |                             |

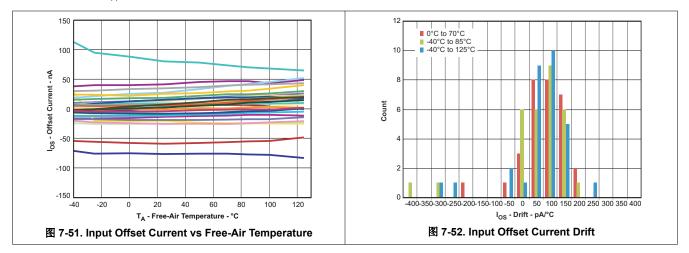

|                                           | T <sub>A</sub> = 25°C                                               | - 180  | ±30              | 180  |           | А                           |

|                                           | T <sub>A</sub> = 0°C to 70°C                                        | - 200  | ±30              | 200  |           |                             |

| Input offset current                      | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        | - 215  | ±30              | 215  | nA        | в                           |

|                                           | $T_{A} = -40^{\circ}C \text{ to } 125^{\circ}C$                     | - 240  | ±30              | 240  |           |                             |

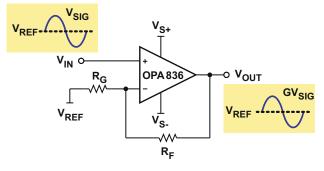

|                                           | $T_A = 0^{\circ}C \text{ to } 70^{\circ}C$                          | - 460  | ±77              | 460  |           |                             |

| Input offset current drift <sup>(2)</sup> | $T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C$                      | - 575  | ±95              | 575  | pA/°C     | в                           |

|                                           | $T_{A} = -40^{\circ}C \text{ to } 125^{\circ}C$                     | - 600  | ±100             | 600  |           |                             |

| INPUT                                     |                                                                     |        |                  |      |           |                             |

|                                           | T <sub>A</sub> = 25°C,<br>< 3-dB degradation in CMRR limit          |        | - 0.2            | 0    | V         | А                           |

| Common-mode input range low               | $T_A = -40^{\circ}C$ to 125°C,<br>< 3-dB degradation in CMRR limit  |        | - 0.2            | 0    | V         | В                           |

| Common mode input renze hist              | T <sub>A</sub> = 25°C,<br>< 3-dB degradation in CMRR limit          | 1.5    | 1.6              |      | V         | A                           |

| Common-mode input range high              | $T_A = -40^{\circ}$ C to 125°C,<br>< 3-dB degradation in CMRR limit | 1.5    | 1.6              |      | V         | В                           |

| nput operating voltage range              | T <sub>A</sub> = 25°C,<br>< 6-dB degradation in THD                 |        | - 0.3 to<br>1.75 |      | V         | С                           |

| Common-mode rejection ratio               |                                                                     | 91     | 114              |      | dB        | А                           |

| Input impedance common-mode               |                                                                     |        | 100    1.2       |      | M Ω    pF | С                           |

| Input impedance differential mode         |                                                                     |        | 100    1         |      | k Ω ∥ pF  | С                           |

# 7.6 Electrical Characteristics: V<sub>S</sub> = 2.7 V (continued)

at  $V_{S+}$  = +2.7 V,  $V_{S-}$  = 0 V,  $V_{OUT}$  = 1  $V_{PP}$ ,  $R_F$  = 0  $\Omega$ ,  $R_L$  = 2 k  $\Omega$ , G = 1 V/V, input and output referenced to mid-supply,  $V_{IN\_CM}$  = mid-supply - 0.5 V.  $T_A$  = 25°C, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                                                | MIN  | ТҮР   | MAX  | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|----------------------------------------------------------------|------|-------|------|------|------------------------------|

| ОИТРИТ                                    | ·                                                              |      |       |      |      |                              |

| Output voltage low                        | T <sub>A</sub> = 25°C, G = 5                                   |      | 0.15  | 0.2  | V    | A                            |

| Output voltage low                        | $T_A = -40^{\circ}C$ to 125°C, G = 5                           |      | 0.15  | 0.2  | V    | В                            |

|                                           | T <sub>A</sub> = 25°C, G = 5                                   | 2.45 | 2.5   |      | V    | А                            |

| Output voltage high                       | $T_A = -40^{\circ}C$ to 125°C, G = 5                           | 2.45 | 2.5   |      | V    | В                            |

| Output saturation voltage, high/low       | T <sub>A</sub> = 25°C, G = 5                                   |      | 80/40 |      | mV   | С                            |

|                                           | T <sub>A</sub> = 25°C                                          | ±40  | ±45   |      | mA   | А                            |

| Output current drive                      | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                  | ±40  | ±45   |      | mA   | В                            |

| GAIN SETTING RESISTORS (OPA836IRUN O      | NLY)                                                           |      |       |      |      |                              |

| Resistor FB1 to FB2                       | DC resistance                                                  | 1584 | 1600  | 1616 | Ω    | А                            |

| Resistor FB2 to FB3                       | DC resistance                                                  | 1188 | 1200  | 1212 | Ω    | А                            |

| Resistor FB3 to FB4                       | DC resistance                                                  | 396  | 400   | 404  | Ω    | А                            |

| Resistor tolerance                        | DC resistance                                                  | - 1% |       | 1%   |      | А                            |

| Resistor temperature coefficient          | DC resistance                                                  |      | <10   |      | PPM  | С                            |

| POWER SUPPLY                              | · · · ·                                                        |      |       |      |      |                              |

| Specified operating voltage               |                                                                | 2.5  |       | 5.5  | V    | В                            |

|                                           | T <sub>A</sub> = 25°C                                          | 0.7  | 0.95  | 1.15 | mA   | А                            |

| Quiescent operating current per amplifier | $T_A = -40^{\circ}C$ to 125°C                                  | 0.6  |       | 1.4  | mA   | В                            |

| Power supply rejection (±PSRR)            |                                                                | 91   | 108   |      | dB   | А                            |

| POWER DOWN                                | · · · · ·                                                      |      |       |      |      |                              |

| Enable voltage threshold                  | Specified "on" above V <sub>S -</sub> + 2.1 V                  |      |       | 2.1  | V    | А                            |

| Disable voltage threshold                 | Specified "off" below V <sub>S -</sub> + 0.7 V                 | 0.7  |       |      | V    | А                            |

| Power-down pin bias current               | PD = 0.5 V                                                     |      | 20    | 500  | nA   | А                            |

| Power-down quiescent current              | PD = 0.5 V                                                     |      | 0.5   | 1.5  | μA   | А                            |

| Turnon time delay                         | Time from PD = high to V <sub>OUT</sub> = 90% of final value   |      | 200   |      | ns   | С                            |

| Turnoff time delay                        | Time from PD = low to V <sub>OUT</sub> = 10% of original value |      | 25    |      | ns   | С                            |

(1) Test levels (all values set by characterization and simulation): (A) 100% tested at 25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

(2) Input Offset Voltage Drift, Input Bias Current Drift, and Input Offset Current Drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

(3) Current is considered positive out of the pin.

# 7.7 Electrical Characteristics: $V_S = 5 V$

| PARAMETER                                 | TEST CONDITIONS                                                                   | MIN TYP N |          | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|-----------------------------------------------------------------------------------|-----------|----------|------------------------------|

| AC PERFORMANCE                            |                                                                                   |           |          |                              |

|                                           | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1                                   | 205       |          |                              |

|                                           | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 2                                   | 100       |          | 0                            |

| Small-signal bandwidth                    | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 5                                   | 28        | MHz      | С                            |

|                                           | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10                                  | 11.8      |          |                              |

| Gain-bandwidth product                    | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10                                  | 118       | MHz      | С                            |

| Large-signal bandwidth                    | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 2                                      | 87        | MHz      | С                            |

| Bandwidth for 0.1-dB flatness             | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 2                                      | 29        | MHz      | С                            |

| Slew rate, rise                           | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 560       | V/µs     | С                            |

| Slew rate, fall                           | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 580       | V/µs     | С                            |

| Rise time                                 | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 3         | ns       | С                            |

| Fall time                                 | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 3         | ns       | С                            |

| AC PERFORMANCE (continued)                |                                                                                   |           |          |                              |

| Settling time to 1%, rise                 | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 22        | ns       | С                            |

| Settling time to 1%, fall                 | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 22        | ns       | С                            |

| Settling time to 0.1%, rise               | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 30        | ns       | С                            |

| Settling time to 0.1%, fall               | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 30        | ns       | С                            |

| Settling time to 0.01%, rise              | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 40        | ns       | С                            |

| Settling time to 0.01%, fall              | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 45        | ns       | С                            |

| Overshoot/Undershoot                      | V <sub>OUT</sub> = 2-V Step, G = 2                                                | 7.5%/5%   |          | С                            |

|                                           | f = 10 kHz                                                                        | - 133     |          |                              |

| Second-order harmonic distortion          | f = 100 kHz                                                                       | - 120     | dBc      | с                            |

|                                           | f = 1 MHz                                                                         | - 85      |          |                              |

|                                           | f = 10 kHz                                                                        | - 140     |          |                              |

| Third-order harmonic distortion           | f = 100 kHz                                                                       | - 130     | dBc      | с                            |

|                                           | f = 1 MHz                                                                         | - 105     |          |                              |

| Second-order intermodulation distortion   | f = 1 MHz, 200 kHz Tone Spacing,<br>V <sub>OUT</sub> Envelope = 2 V <sub>PP</sub> | - 79      | dBc      | с                            |

| Third-order intermodulation distortion    | f = 1 MHz, 200 kHz Tone Spacing,<br>V <sub>OUT</sub> Envelope = 2 V <sub>PP</sub> | - 91      | dBc      | С                            |

|                                           | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> ,                                | 0.00013%  |          | 0                            |

| Signal-to-noise ratio, SNR                | 22 kHz bandwidth                                                                  | - 117.6   | dBc      | С                            |

|                                           |                                                                                   | 0.00003%  |          |                              |

| Total harmonic distortion, THD            | $f = 1 \text{ kHz}, V_{OUT} = 1 V_{RMS}$                                          | - 130     | dBc      | С                            |

| Input voltage noise                       | f = 100 KHz                                                                       | 4.6       | nV/ √ Hz | С                            |

| Voltage noise 1/f corner frequency        |                                                                                   | 215       | Hz       | С                            |

| Input current noise                       | f > 1 MHz                                                                         | 0.75      | pA/ √ Hz | С                            |

| Current noise 1/f corner frequency        |                                                                                   | 31.7      | kHz      | С                            |

| Overdrive recovery time, over/under       | Overdrive = 0.5 V                                                                 | 55/60     | ns       | С                            |

| Closed-loop output impedance              | f = 100 kHz                                                                       | 0.02      | Ω        | С                            |

| Channel to channel crosstalk (OPA2836)    | f = 10 kHz                                                                        | - 120     | dB       | С                            |

| DC PERFORMANCE                            | I                                                                                 | -         |          | L                            |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                                                   | 100 122   | dB       | A                            |

|                                           |                                                                                   |           |          |                              |

# 7.7 Electrical Characteristics: V<sub>S</sub> = 5 V (continued)

| PARAMETER                                 | TEST CONDITIONS                                                     | MIN    | ТҮР              | MAX  | UNIT       | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|---------------------------------------------------------------------|--------|------------------|------|------------|------------------------------|

|                                           | T <sub>A</sub> = 25°C                                               | - 400  | ±65              | 400  |            | A                            |

| Input referred offect velters             | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 | - 685  |                  | 685  |            |                              |

| Input referred offset voltage             | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        | - 765  |                  | 765  | μV         | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                              | - 1080 |                  | 1080 |            |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 | - 6.3  | ±1.05            | 6.3  |            |                              |

| Input offset voltage drift <sup>(2)</sup> | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        | - 6.1  | ±1               | 6.1  | µV/°C      | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                              | - 6.8  | ±1.1             | 6.8  |            |                              |

|                                           | T <sub>A</sub> = 25°C                                               | 300    | 650              | 1000 |            | А                            |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 | 190    |                  | 1400 |            |                              |

| Input bias current <sup>(3)</sup>         | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        | 120    |                  | 1550 | nA         | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                              | 120    |                  | 1850 |            |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 |        | ±0.34            | ±2   |            |                              |

| Input bias current drift <sup>(2)</sup>   | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        |        | ±0.34            | ±2   | nA/°C      | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                              |        | ±0.38            | ±2.3 |            |                              |

| DC PERFORMANCE (continued)                | I                                                                   |        |                  |      | II         |                              |

|                                           | T <sub>A</sub> = 25°C                                               |        | ±30              | ±180 |            | А                            |

| Input offect ourrent                      | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 |        | ±30              | ±200 | <b>n</b> A |                              |

| Input offset current                      | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        |        | ±30              | ±215 | nA         | В                            |

|                                           | $T_A = -40^{\circ}C$ to 125°C                                       |        | ±30              | ±250 |            |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                 |        | ±80              | ±480 |            |                              |

| Input offset current drift <sup>(2)</sup> | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                        |        | ±100             | ±600 | pA/°C      | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                              |        | ±110             | ±660 |            |                              |

| INPUT                                     |                                                                     |        |                  |      |            |                              |

| <b>6</b>                                  | T <sub>A</sub> = 25°C,<br>< 3-dB degradation in CMRR limit          |        | - 0.2            | 0    | V          | А                            |

| Common-mode input range low               | $T_A = -40^{\circ}$ C to 125°C,<br>< 3-dB degradation in CMRR limit |        | - 0.2            | 0    | V          | В                            |

| Common-mode input range high              | T <sub>A</sub> = 25°C,<br>< 3-dB degradation in CMRR limit          | 3.8    | 3.9              |      | V          | А                            |

|                                           | $T_A = -40^{\circ}$ C to 125°C,<br>< 3-dB degradation in CMRR limit | 3.8    | 3.9              |      | V          | В                            |

| Input linear operating voltage range      | T <sub>A</sub> = 25°C,<br>< 6-dB degradation in THD                 |        | - 0.3 to<br>4.05 |      | v          | С                            |

| Common-mode rejection ratio               |                                                                     | 94     | 116              |      | dB         | Α                            |

| Input impedance common mode               |                                                                     |        | 100    1.2       |      | M Ω    pF  | С                            |

| Input impedance differential mode         |                                                                     |        | 100    1         |      | k Ω    pF  | С                            |

| ОИТРИТ                                    |                                                                     |        |                  |      |            |                              |

| Output voltage low                        | T <sub>A</sub> = 25°C, G = 5                                        |        | 0.15             | 0.2  | V          | А                            |

|                                           | $T_A = -40^{\circ}C$ to 125°C, G = 5                                |        | 0.15             | 0.2  | V          | В                            |

| Output voltage high                       | T <sub>A</sub> = 25°C, G = 5                                        | 4.75   | 4.8              |      | V          | А                            |

|                                           | $T_A = -40^{\circ}C$ to 125°C, G = 5                                | 4.75   | 4.8              |      | V          | В                            |

| Output saturation voltage, high/low       | T <sub>A</sub> = 25°C, G = 5                                        |        | 100/50           |      | mV         | С                            |

| Output current drive                      | T <sub>A</sub> = 25°C                                               | ±40    | ±50              |      | mA         | Α                            |

|                                           | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                       | ±40    | ±50              |      | mA         | В                            |

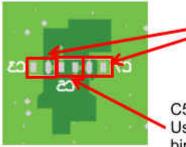

| GAIN SETTING RESISTORS (OPA836IRUN        | ONLY)                                                               |        |                  |      |            |                              |

| Resistor FB1 to FB2                       | DC resistance                                                       | 1584   | 1600             | 1616 | Ω          | А                            |

| Resistor FB2 to FB3                       | DC resistance                                                       | 1188   | 1200             | 1212 | Ω          | A                            |

# 7.7 Electrical Characteristics: V<sub>S</sub> = 5 V (continued)

at V<sub>S+</sub> = +5 V, V<sub>S-</sub> = 0 V, V<sub>OUT</sub> = 2 V<sub>PP</sub>, R<sub>F</sub> = 0  $\Omega$ , R<sub>L</sub> = 1 k $\Omega$ , G = 1 V/V, input and output referenced to mid-supply. T<sub>A</sub> = 25°C, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                                                             | MIN  | ТҮР | MAX | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|-----------------------------------------------------------------------------|------|-----|-----|------|------------------------------|

| Resistor FB3 to FB4                       | DC resistance                                                               | 396  | 400 | 404 | Ω    | A                            |

| Resistor tolerance                        | DC resistance                                                               | - 1  |     | 1%  |      | А                            |

| Resistor temperature coefficient          | DC resistance                                                               |      | <10 |     | PPM  | С                            |

| POWER SUPPLY                              | · · · ·                                                                     |      |     |     |      |                              |

| Specified operating voltage               |                                                                             | 2.5  |     | 5.5 | V    | В                            |

|                                           | T <sub>A</sub> = 25°C                                                       | 0.8  | 1.0 | 1.2 | mA   | А                            |

| Quiescent operating current per amplifier | $T_{A} = -40^{\circ}C \text{ to } 125^{\circ}C$                             | 0.65 |     | 1.5 | mA   | В                            |

| Power supply rejection (±PSRR)            |                                                                             | 94   | 108 |     | dB   | A                            |

| POWER DOWN                                | I                                                                           |      |     |     |      | 1                            |

| Enable voltage threshold                  | Specified "on" above V <sub>S -</sub> + 2.1 V                               |      |     | 2.1 | V    | А                            |

| Disable voltage threshold                 | Specified "off" below V <sub>S -</sub> + 0.7 V                              | 0.7  |     |     | V    | А                            |

| Power-down pin bias current               | PD = 0.5 V                                                                  |      | 20  | 500 | nA   | А                            |

| Power-down quiescent current              | PD = 0.5 V                                                                  |      | 0.5 | 1.5 | μA   | А                            |

| Turnon time delay                         | Time from $\overline{PD}$ = high to V <sub>OUT</sub> = 90% of final value   |      | 170 |     | ns   | С                            |

| Turnoff time delay                        | Time from $\overline{PD}$ = low to V <sub>OUT</sub> = 10% of original value |      | 35  |     | ns   | С                            |

(1) Test levels (all values set by characterization and simulation): (A) 100% tested at 25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

(2) Input Offset Voltage Drift, Input Bias Current Drift, and Input Offset Current Drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

(3) Current is considered positive out of the pin.

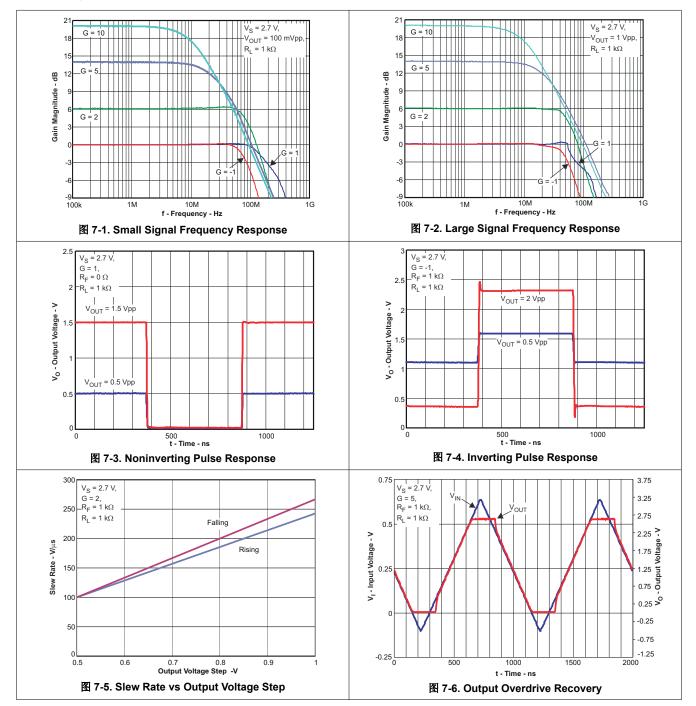

# 7.8 Typical Characteristics: V<sub>S</sub> = 2.7 V (continued)

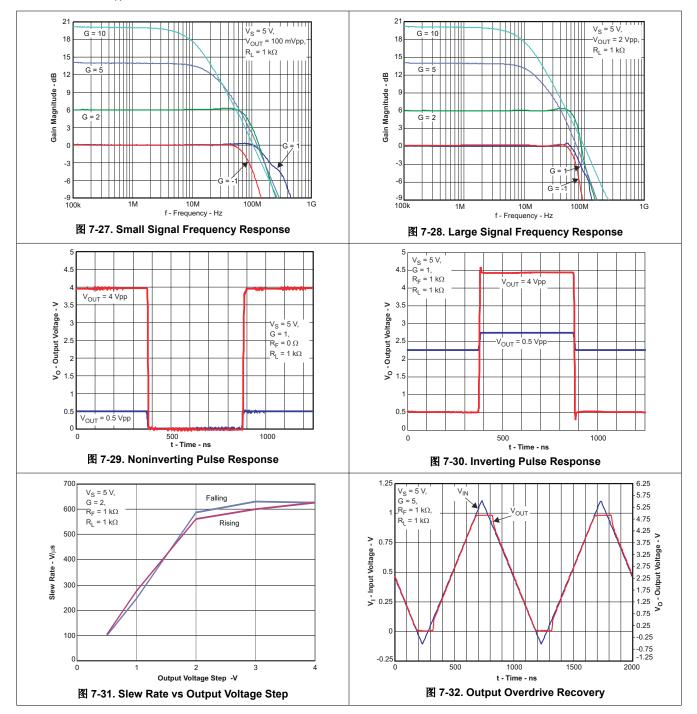

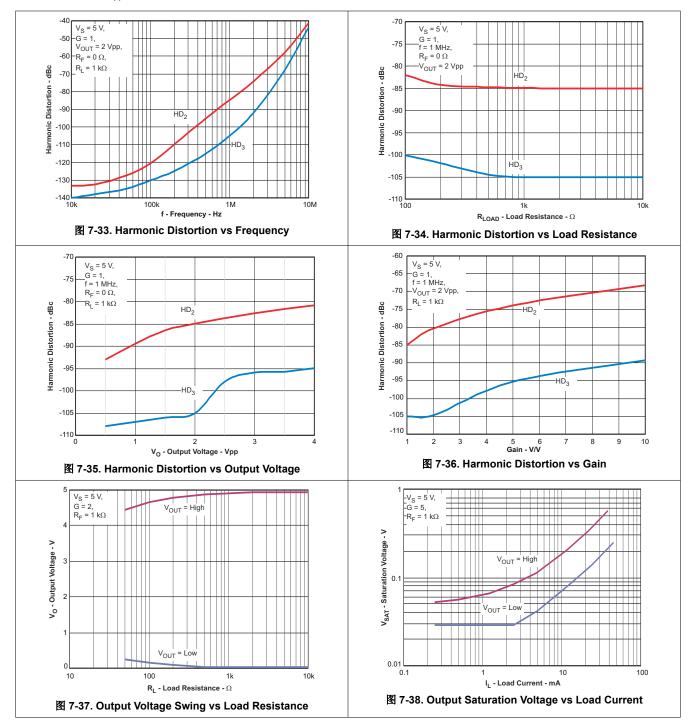

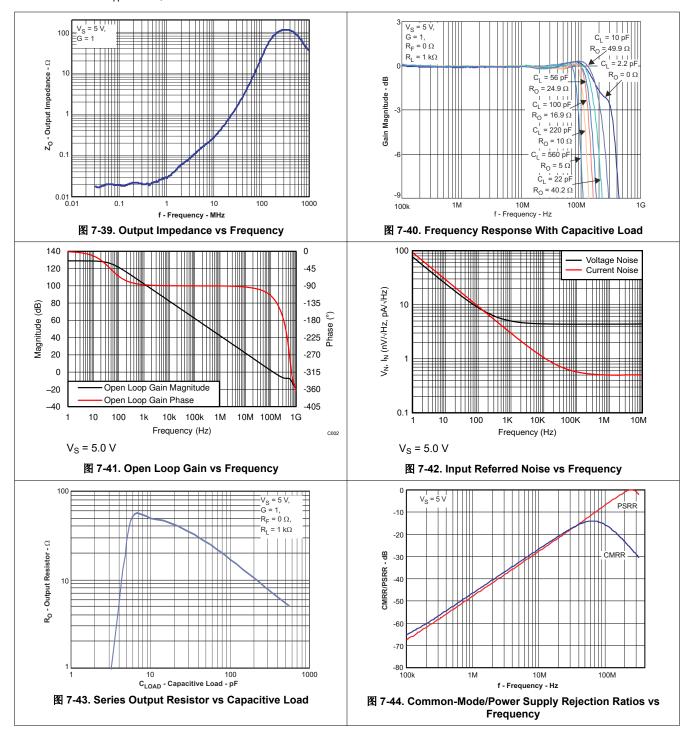

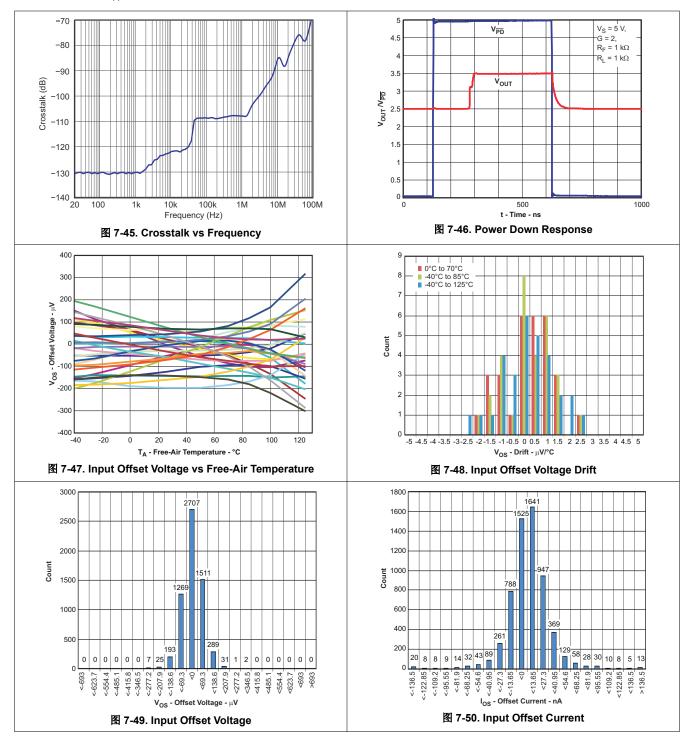

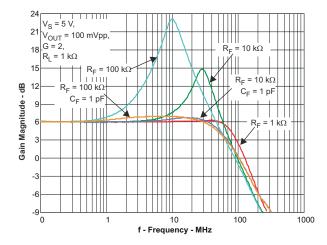

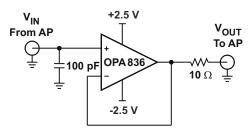

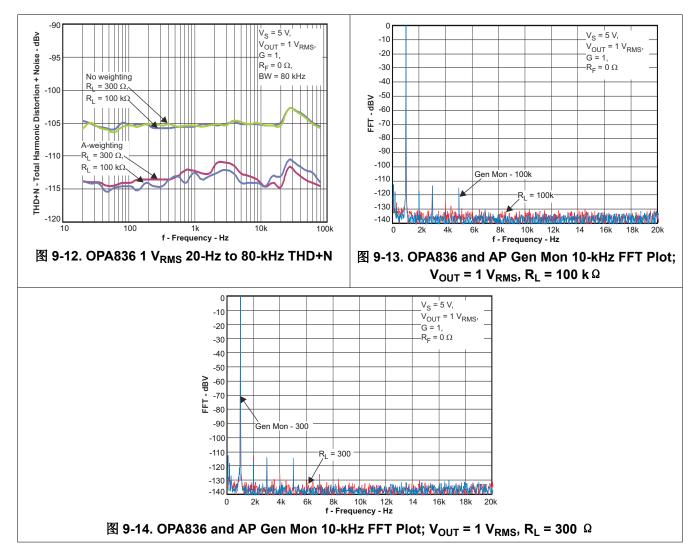

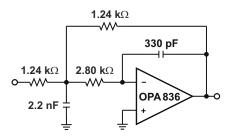

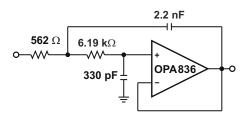

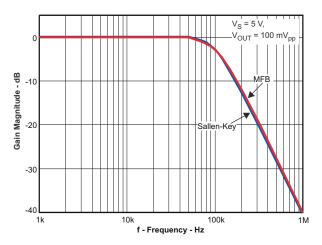

# 7.9 Typical Characteristics: $V_S = 5 V$

# 7.9 Typical Characteristics: $V_S = 5 V$

# 7.9 Typical Characteristics: V<sub>S</sub> = 5 V (continued)

# 8 Detailed Description

## 8.1 Overview

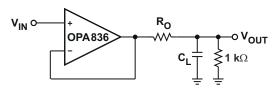

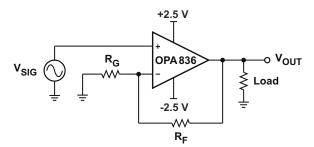

The OPAx836 family of bipolar-input operational amplifiers offers excellent bandwidth of 205 MHz with ultra-low THD of 0.00003% at 1 kHz. The OPAx836 device can swing to within 200 mV of the supply rails while driving a 1-k $\Omega$  load. The input common-mode of the amplifier can swing to 200 mV below the negative supply rail. This level of performance is achieved at 1 mA of quiescent current per amplifier channel.

## 8.2 Functional Block Diagrams

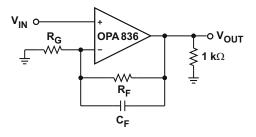

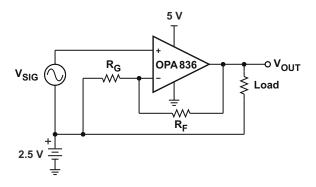

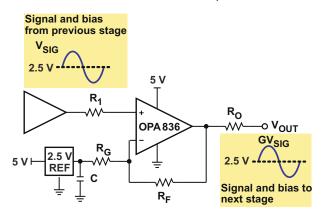

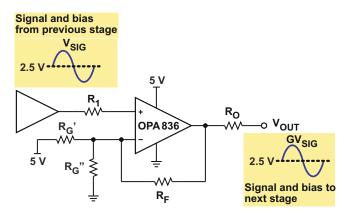

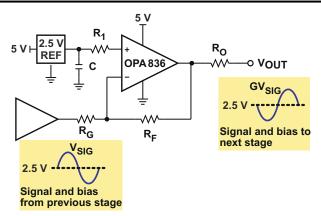

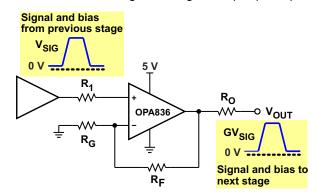

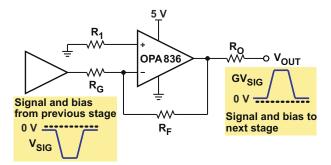

图 8-2. Inverting Amplifier

# 8.3 Feature Description

## 8.3.1 Input Common-Mode Voltage Range

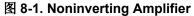

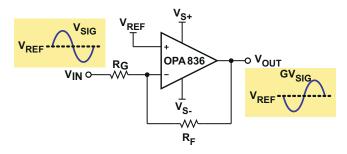

When the primary design goal is a linear amplifier with high CMRR, it is important to not violate the input common-mode voltage range ( $V_{ICR}$ ) of an operational amplifier.

The common-mode input range specifications in the table data use CMRR to set the limit. The limits are selected to ensure CMRR will not degrade more than 3 dB below the CMRR limit if the input voltage is kept within the specified range. The limits cover all process variations and most parts will be better than specified. The typical specifications are from 0.2 V below the negative rail to 1.1 V below the positive rail.

Assuming the operational amplifier is in linear operation, the voltage difference between the input pins is small (ideally 0 V) and input common-mode voltage is analyzed at either input pin with the other input pin assumed to be at the same potential. The voltage at  $V_{IN+}$  is simple to evaluate. In noninverting configuration,  $\boxtimes$  8-1, the input signal,  $V_{IN}$ , must not violate the  $V_{ICR}$ . In inverting configuration,  $\boxtimes$  8-2, the reference voltage,  $V_{REF}$ , must be within the  $V_{ICR}$ .

The input voltage limits have fixed headroom to the power rails and track the power supply voltages. For one 5-V supply, the linear input voltage ranges from -0.2 V to 3.9 V and from -0.2 V to 1.6 V for a 2.7-V supply. The delta headroom from each power supply rail is the same in either case: -0.2 V and 1.1 V.

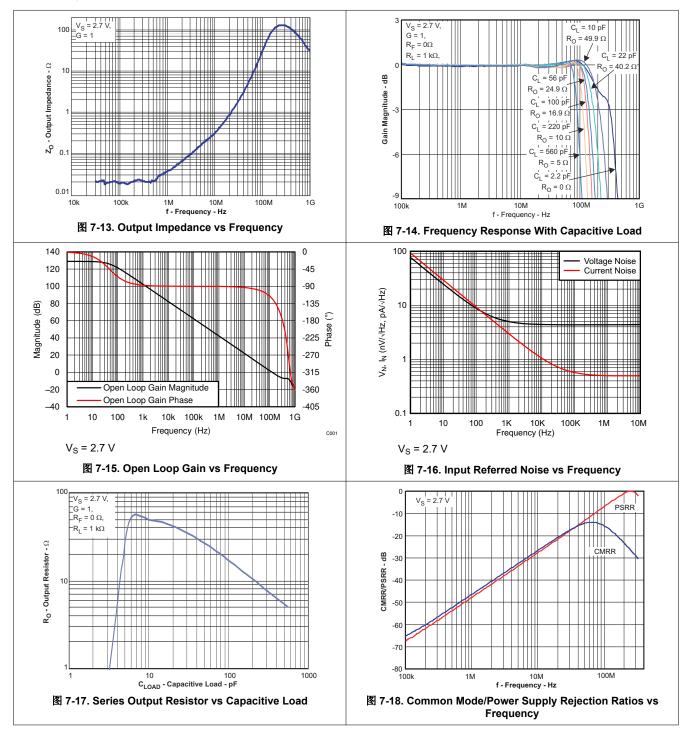

#### 8.3.2 Output Voltage Range

The OPA836 and OPA2836 devices are rail-to-rail output (RRO) operational amplifiers. Rail-to-rail output typically means the output voltage swings within a couple hundred millivolts of the supply rails. There are different ways to specify this: one is with the output still in linear operation and another is with the output saturated. Saturated output voltages are closer to the power supply rails than linear outputs, but the signal is not a linear representation of the input. Linear output is a better representation of how well a device performs when used as a linear amplifier. Saturation and linear operation limits are affected by the output current, where higher currents lead to more loss in the output transistors.

Output Voltage Swing vs Load Resistance and Output Voltage Swing vs Load Resistance show saturated voltage-swing limits versus output load resistance and Output Saturation Voltage vs Load Current and Output Saturation Voltage vs Load Current and Output Saturation Voltage vs Load Current show the output saturation voltage versus load current. Given a light load, the output voltage limits have nearly constant headroom to the power rails and track the power supply voltages. For example, with a 2-k $\Omega$  load and single 5-V supply, the linear output voltage ranges from 0.15 V to 4.8 V, and ranges from 0.15 V to 2.5 V for a 2.7-V supply. The delta from each power supply rail is the same in either case: 0.15 V and 0.2 V.

With devices like the OPA836 and OPA2836, where the input range is lower than the output range, typically the input will limit the available signal swing only in noninverting gain of 1. Signal swing in noninverting configurations in gains > +1 and inverting configurations in any gain is typically limited by the output voltage limits of the operational amplifier.

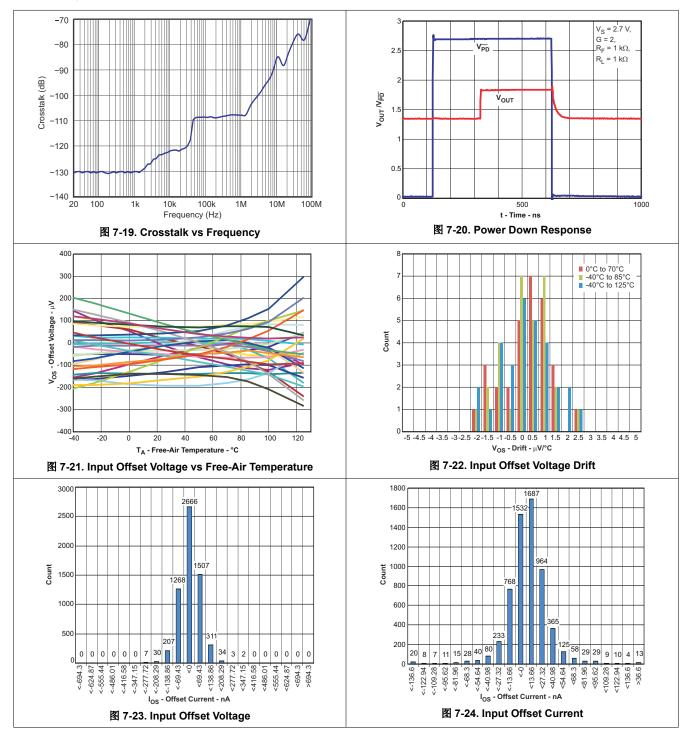

#### 8.3.3 Power-Down Operation

The OPA836 and OPA2836 devices include a power-down mode. Under logic control, the amplifiers can switch from normal operation to a standby current of < 1.5  $\mu$ A. When the  $\overline{PD}$  pin is connected high, the amplifier is active. Connecting  $\overline{PD}$  pin low disables the amplifier and places the output in a high-impedance state. When the amplifier is configured as a unity-gain buffer, the output stage is in a high dc-impedance state. To protect the input stage of the amplifier, the devices use internal, back-to-back ESD diodes between the inverting and noninverting input pins. This configuration creates a parallel low-impedance path from the amplifier output to the noninverting pin when the differential voltage between the pins exceeds a diode voltage drop. When the op amp is configured in other gains, the feedback (RF) and gain (RG) resistor network forms a parallel load.

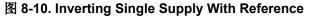

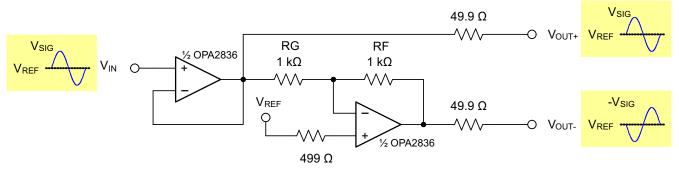

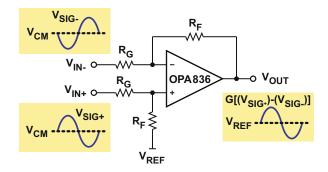

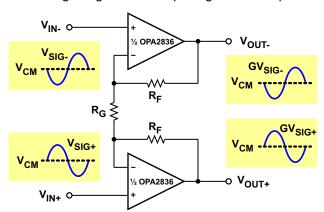

The PD pin must be actively driven high or low and must not be left floating. If the power-down mode is not used, PD must be tied to the positive supply rail.