# 高电压、大电流运算放大器

查询样品: OPA549-HiRel

# 特性

- 高输出电流:

- 8A 持续电流

- 10A 峰值电流

- 宽电源电压范围:

- 单电源: 8 V至 60V

- 双电源: ±4V 至 ±30V

- 宽输出电压摆幅

- 受到完全保护:

- 过热保护

- 可调电流

- 输出禁用控制

- 热关断指示器

- 高转换率: 9V/µs

- 控制基准引脚

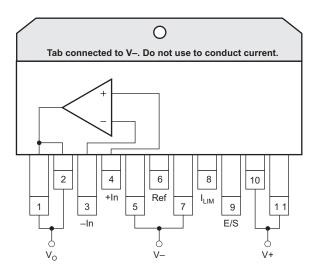

- 11 引线功率封装

# 应用范围

- 阀门、致动器驱动器

- 同步器、伺服器驱动器

- 电源

- 测试设备

- 转换器激励

- 音频功率放大器

# 支持国防、航空航天、和医疗应用

- 受控基线

- 一个组装/测试场所

- 一个制造场所

- 军用温度范围 (-55°C/125°C) 内可用(1)

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

(1) 可提供额外温度范围-请与厂家联系

# 说明

OPA549 是一款低成本、高压大电流运算放大器,此放大器非常适合于驱动多种负载。 这个激光微调的单片集成电路提供出色的低电平信号精度和高输出电压和电流。

为了实现设计灵活性, OPA549 可由单电源或者双电源供电。 输入共模的扩展范围低于负电源。

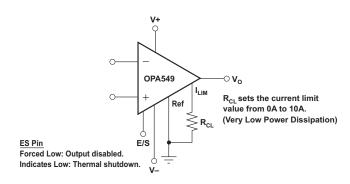

OPA549 在过热情况下和电流过载时受到内部保护。此外,OPA549 提供一个精准的、用户可选择的限流。与其它使用一个与输出电流路径串联的功率电阻器的设计不同,OPA549 间接的感应负载。 这样允许使用一个电阻器或者电势计在 0A 至 10A 间对限流进行调节,或者使用一个电压输出或电流输出模数转换器 (DAC) 来进行数控。

使能/状态 (E/S) 引脚提供了两个功能。 对于它的监控可被用来确定器件是否处于热关断状态,它还可以被强制为低电平以禁用输出级并且有效地断开负载。

OPA549 采用 11 引线功率封装。 它的铜质拉环可以很容易地安装到散热片上,这样可实现出色的散热性能。 额定运行温度范围为 -55°C 至 + 125°C。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# ORDERING INFORMATION<sup>(1)</sup>

| T <sub>CASE</sub> | PACKAGE | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|-------------------|---------|-----------------------|------------------|--|

| -55°C to 125°C    | KVC     | OPA549MKVC            | OPA549M          |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

Connect both pins 1 and 2 to output. Connect both pins 5 and 7 to V-. Connect both pins 10 and 11 to V+.

Figure 1. Connection Diagram

# ABSOLUTE MAXIMUM RATINGS(1)

|                  | Output current                  |                  | See Figure 8                 |

|------------------|---------------------------------|------------------|------------------------------|

| V+ to V-         | Supply voltage                  |                  | 60 V                         |

| VI               | Input voltage range             |                  | (V−) − 0.5 V to (V+) + 0.5 V |

|                  | Input voltage reference maximum |                  | (V+) - 8                     |

|                  | Input shutdown voltage          |                  | Ref - 0.5 V to V+            |

| T <sub>OP</sub>  | Operating temperature           |                  | −55°C to 125°C               |

| T <sub>stg</sub> | Storage temperature             |                  | −55°C to 125°C               |

| TJ               | Junction temperature            |                  | 150°C                        |

|                  | Lead temperature                | Soldering, 10 s  | 300°C                        |

| ESD              | Electrostatic discharge rating  | Human Body Model | 2000 V                       |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                  |                                                             | OPA549  |       |

|------------------|-------------------------------------------------------------|---------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | KVC     | UNITS |

|                  |                                                             | 11 PINS |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 21.5    |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 17.4    |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 9.2     | 90044 |

| Ψлт              | Junction-to-top characterization parameter <sup>(5)</sup>   | 1.5     | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter (6)            | 9.2     |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 0.1     |       |

- (1) 有关传统和全新热度量的更多信息,请参阅 IC 封装热度量 应用报告 (文献号:SPRA953)。

- (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的规定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然对流条件下的结至环境热阻抗。

- (3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明,通过在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结至电路板的热阻。

- (5) 结至顶部的特征参数,( ψ<sub>JT</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中描述的程序从仿真数据中提取出该 参数以便获得 θ<sub>JA</sub>。

- (6) 结至电路板的特征参数,(ψ<sub>JB</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第7 章)中描述的程序从仿真数据中提取出该 参数以便获得 θ<sub>IA</sub> 。

- (7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到了内容接近的说明。

### **ELECTRICAL CHARACTERISTICS**

At  $T_{CASE} = 25$ °C,  $V_S = \pm 30$ V, Ref = 0V, and and E/S pin open (unless otherwise noted)

|                                  | PARAMETER                            | TEST CONDITIONS                                                                                                     | MIN        | TYP                  | MAX  | UNIT               |

|----------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------|----------------------|------|--------------------|

| OFFSET '                         | VOLTAGE                              |                                                                                                                     |            |                      |      |                    |

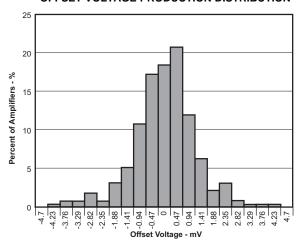

|                                  |                                      | V <sub>CM</sub> = 0 V, I <sub>O</sub> = 0 A, T <sub>CASE</sub> = 25°C                                               |            | ±1                   | ±5   | mV                 |

| V <sub>OS</sub>                  | Input offset voltage                 | V <sub>CM</sub> = 0 V, I <sub>O</sub> = 0 A,<br>T <sub>CASE</sub> = -55°C to 125°C                                  |            |                      | ±7   | mV                 |

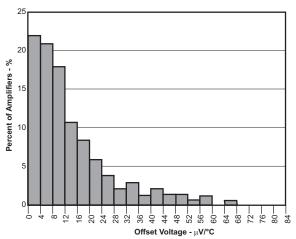

| dV <sub>OS</sub> / dT            | Input offset voltage drift           | $V_{CM} = 0 \text{ V, } I_{O} = 0 \text{ A,}$<br>$T_{CASE} = -55^{\circ}\text{C to } 125^{\circ}\text{C}$           |            | ±20                  |      | μV/°C              |

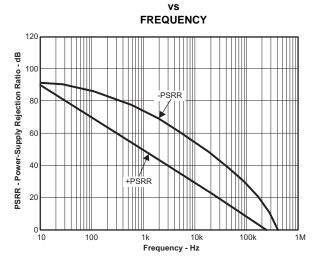

| PSRR                             | Input offset voltage vs power supply | $V_S = \pm 4 \text{ V to } \pm 30 \text{ V, Ref} = V-,$<br>$T_{CASE} = -55^{\circ}\text{C to } 125^{\circ}\text{C}$ | 25         |                      | 100  | μV/V               |

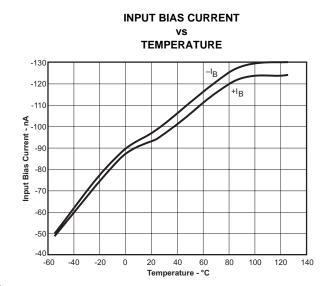

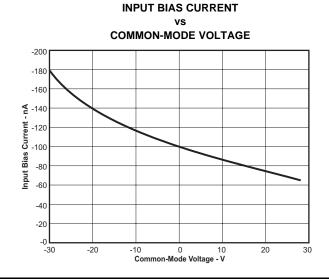

| INPUT BI                         | AS CURRENT                           |                                                                                                                     | ·          |                      |      |                    |

| I <sub>B</sub>                   | Input bias current <sup>(1)</sup>    | V <sub>CM</sub> = 0 V, T <sub>CASE</sub> = -55°C to 125°C                                                           |            | -100                 | -500 | nA                 |

| Ios                              | Input offset current                 | V <sub>CM</sub> = 0 V, T <sub>CASE</sub> = -55°C to 125°C                                                           |            | ±5                   | ±100 | nA                 |

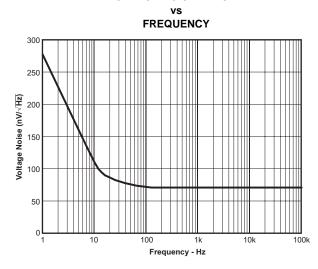

| NOISE                            |                                      |                                                                                                                     |            |                      |      |                    |

| e <sub>n</sub>                   | Input voltage noise density          | f = 1 kHz                                                                                                           |            | 705                  |      | nV/√ <del>Hz</del> |

| i <sub>n</sub>                   | Input current noise density          | f = 1 kHz                                                                                                           |            | 1                    |      | pA/√ <del>Hz</del> |

| INPUT VO                         | DLTAGE RANGE                         |                                                                                                                     | ·          |                      |      |                    |

| V                                | Common mode valtage range            | Linear operation; Positive,<br>T <sub>CASE</sub> = -55°C to 125°C                                                   | (V+) - 3   | (V+) - 2.3           |      | V                  |

| $V_{CM}$                         | Common-mode voltage range            | Linear operation; Negative,<br>T <sub>CASE</sub> = -55°C to 125°C                                                   | (V-) - 0.1 | (V-) - 0.2           |      | V                  |

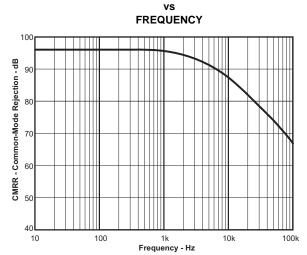

| CMRR Common-mode rejection ratio |                                      | V <sub>CM</sub> = (V-) - 0.1 V to (V+) - 3 V,<br>T <sub>CASE</sub> = -55°C to 125°C                                 | 78         | 95                   |      | dB                 |

| INPUT IM                         | PEDANCE                              |                                                                                                                     |            |                      |      |                    |

|                                  | Differential                         |                                                                                                                     |            | 10 <sup>7</sup>    6 |      | Ω    pF            |

|                                  | Common-mode                          |                                                                                                                     |            | 10 <sup>9</sup>    4 |      | Ω    pF            |

<sup>(1)</sup> Positive conventional current is defined as flowing into the terminal.

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_{CASE} = 25$ °C,  $V_S = \pm 30$ V, Ref = 0V, and and E/S pin open (unless otherwise noted)

|                   | PARAMETER                                                  | TEST CONDITIONS                                                                                                            | MIN                         | TYP           | MAX                     | UNIT     |

|-------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|-------------------------|----------|

| OPEN-LC           | OOP GAIN                                                   |                                                                                                                            |                             |               | ,                       |          |

| A <sub>OL</sub>   | Open-loop voltage gain                                     | $V_{O} = \pm 25 \text{ V}, R_{L} = 1 \text{ k}\Omega,$<br>$T_{CASE} = -55^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | 100                         | 110           |                         | dB       |

|                   |                                                            | $V_O = \pm 25 \text{ V}, R_L = 4 \Omega$                                                                                   | 100                         |               |                         | <u> </u> |

| FREQUE            | NCY RESPONSE                                               |                                                                                                                            |                             |               |                         |          |

| GBW               | Gain-bandwidth product                                     |                                                                                                                            |                             | 0.9           |                         | MHz      |

| SR                | Slew rate                                                  | G = 1, 50-Vp-p step, $R_L = 4 \Omega$                                                                                      |                             | V/µs          |                         |          |

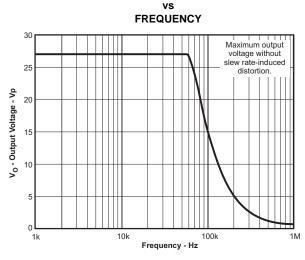

|                   | Full-power bandwidth                                       |                                                                                                                            | See Typ                     | ical Characte | ristics                 |          |

| t <sub>S</sub>    | Settling time                                              | ±0.1%, G = -10, 50-V step                                                                                                  |                             | 20            |                         | μs       |

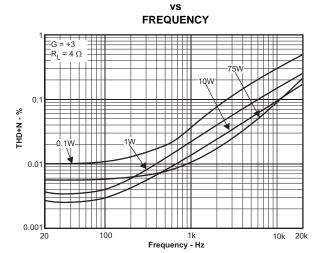

| THD+N             | Total harmonic distortion + noise (2)                      | $f = 1 \text{ kHz}, R_L = 4 \Omega, G = 3, Power = 25 W$                                                                   |                             | 0.015         |                         | %        |

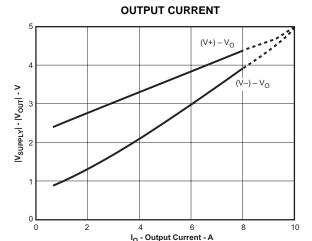

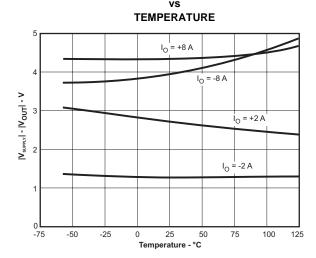

| OUTPUT            |                                                            |                                                                                                                            |                             |               |                         |          |

|                   |                                                            | $I_O = 2 \text{ A}, T_{CASE} = -55^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$                                        | (V+) - 3.7                  | (V+) - 2.7    |                         | -        |

|                   |                                                            | I <sub>O</sub> = -2 A, T <sub>CASE</sub> = -55°C to 125°C                                                                  | (V-) + 1.8                  | (V-) + 1.4    |                         |          |

|                   | Voltage output                                             | I <sub>O</sub> = 8 A, T <sub>CASE</sub> = -55°C to 125°C                                                                   | (V+) - 5.0                  | (V+) - 4.3    |                         | V        |

|                   |                                                            | I <sub>O</sub> = -8 A, T <sub>CASE</sub> = -55°C to 125°C                                                                  | (V-) + 4.9                  | (V-) + 3.9    |                         |          |

|                   |                                                            | $R_L = 8 \Omega$ to V-, $T_{CASE} = -55$ °C to 125°C                                                                       | (V-) + 0.4                  | (V-) + 0.1    |                         |          |

|                   | Maximum continuous current                                 | dc                                                                                                                         | ±8                          |               |                         | Α        |

|                   | output <sup>(3)</sup>                                      | ac; Waveform cannot exceed 10-A peak                                                                                       |                             | 8             |                         | A rms    |

|                   | Output current limit range                                 |                                                                                                                            |                             | 0 to ±10      |                         | Α        |

|                   | Output current limit equation                              |                                                                                                                            | I <sub>LIM</sub> = 15800    | x 4.75 V/(750 | 0 Ω + R <sub>CL</sub> ) | Α        |

|                   | Output current limit tolerance <sup>(4)</sup>              | $R_{CL} = 7.5 \text{ k}\Omega \text{ (I}_{LIM} = \pm 5 \text{ A)}, R_L = 4 \Omega$                                         |                             | ±200          | ±600                    | mA       |

| C <sub>LOAD</sub> | Capacitive load drive (stable operation)                   |                                                                                                                            | See Typical Characteristics |               | ristics                 |          |

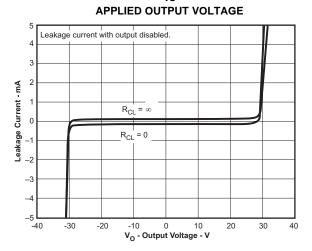

|                   | Output disabled leakage current                            | $V_{O} = 0 \text{ V}, T_{CASE} = -55^{\circ}\text{C to } 125^{\circ}\text{C}$                                              | -2000                       | ±200          | 2000                    | μΑ       |

|                   | Output disabled capacitance                                |                                                                                                                            |                             | 750           |                         | pF       |

| OUTPUT            | ENABLE/STATUS (E/S) PIN                                    |                                                                                                                            |                             |               |                         |          |

|                   | Shutdown input mode V <sub>E/S</sub> high (output enabled) | E/S pin open or forced high                                                                                                | (Ref) + 2.4                 |               |                         | V        |

|                   | Shutdown input mode V <sub>E/S</sub> low (output disabled) | E/S pin forced low                                                                                                         |                             |               | (Ref) + 0.8             | ٧        |

|                   | Shutdown input mode $I_{\text{E/S}}$ high (output enabled) | E/S pin indicates high                                                                                                     |                             | -50           |                         | μΑ       |

|                   | Shutdown input mode I <sub>E/S</sub> low (output disabled) | E/S pin indicates low                                                                                                      |                             | -55           |                         | μΑ       |

|                   | Ouput disable time                                         |                                                                                                                            |                             | 1             |                         | μs       |

|                   | Output enable time                                         |                                                                                                                            |                             | 3             |                         | μs       |

|                   | Thermal shutdown status output (normal operation)          | Sourcing 20 µA                                                                                                             | (Ref) + 2.4                 | (Ref) + 3.5   |                         | V        |

|                   | Thermal shutdown status output (thermally shutdown)        | Sinking 5 μA, T <sub>J</sub> > 160°C                                                                                       |                             | (Ref) + 0.2   | (Ref) + 0.8             | V        |

|                   | lunction tomporature                                       | Shutdown                                                                                                                   |                             | 160           |                         | °C       |

|                   | Junction temperature                                       | Reset from shutdown                                                                                                        |                             | 140           |                         | °C       |

See Total Harmonic Distortion + Noise vs Frequency in the Typical Characteristics section for additional power levels. See Safe Operating Area (SOA) in the Typical Characteristics section. High-speed test at  $T_J = 25^{\circ}\text{C}$

## **ELECTRICAL CHARACTERISTICS (continued)**

At T<sub>CASE</sub> = 25°C, V<sub>S</sub> = ±30V, Ref = 0V, and and E/S pin open (unless otherwise noted)

|                | PARAMETER                 | TEST CONDITIONS                                                              | MIN | TYP  | MAX | UNIT |

|----------------|---------------------------|------------------------------------------------------------------------------|-----|------|-----|------|

| Ref (F         | REFERENCE PIN FOR CONTROL | SIGNALS)                                                                     |     |      |     |      |

|                | Voltage range             |                                                                              | V-  |      |     | V    |

|                | Current <sup>(5)</sup>    |                                                                              |     | -3.5 |     | mA   |

| POWE           | ER SUPPLY                 |                                                                              |     |      |     |      |

| Vs             | Specified voltage range   | $T_{CASE} = -55^{\circ}C$ to 125°C                                           |     | ±30  |     | V    |

|                | Operating voltage range   | (V+) - (V-)                                                                  | 8   |      | 60  | V    |

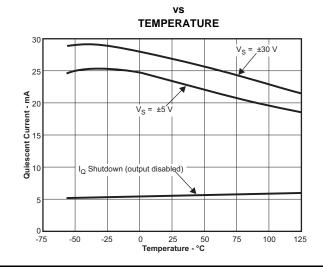

| I <sub>O</sub> | Quiescent current         | $I_{LIM}$ connected to Ref $I_O = 0$ ,<br>$T_{CASE} = -55^{\circ}C$ to 125°C |     | ±26  | ±35 | mA   |

| _              |                           | Shutdown mode; I <sub>LIM</sub> connected to Ref                             |     | ±6   |     |      |

(5) Positive conventional current is defined as flowing into the terminal.

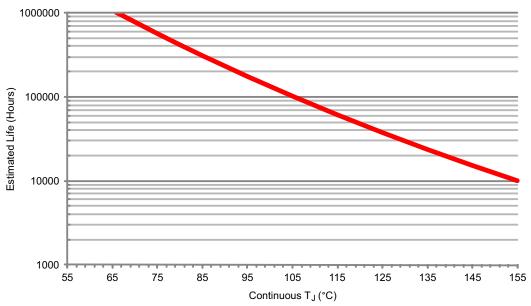

- A. See datasheet for absolute maximum and minimum recommended operating conditions.

- B. Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- C. The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

- D. This curve represents operation with 8-A continuous output current.

Figure 2. OPA549MKVC Operating Life Derating Chart

# **TYPICAL CHARACTERISTICS**

$T_A = 25$ °C,  $V_S = 5$  V,  $C_L = 0$  pF (unless otherwise noted)

-160

# **OPEN-LOOP AND PHASE** vs **FREQUENCY** 100 -40 80 -60 Gain - dB -100 -120 -140 -20

**NSTRUMENTS**

10k f - Frequency - Hz

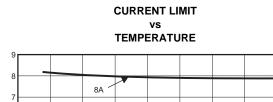

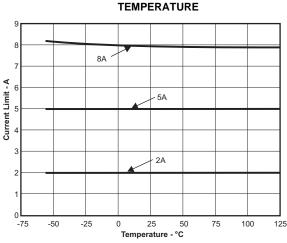

**CURRENT LIMIT**

# **TYPICAL CHARACTERISTICS (continued)**

$T_A = 25$ °C,  $V_S = 5$  V,  $C_L = 0$  pF (unless otherwise noted)

# **COMMON-MODE REJECTION RATIO**

# POWER-SUPPLY REJECTION RATIO

### **VOLTAGE NOISE DENSITY**

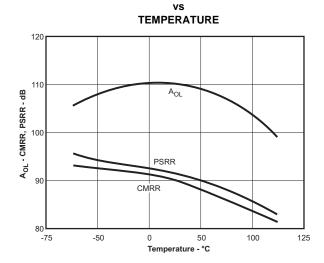

# OPEN-LOOP GAIN, COMMON-MODE REJECTION RATIO AND POWER-SUPPLY REJECTION RATIO

# **TYPICAL CHARACTERISTICS (continued)**

$T_A = 25$ °C,  $V_S = 5$  V,  $C_L = 0$  pF (unless otherwise noted)

### **GAIN-BANDWIDTH PRODUCT AND SLEW RATE**

#### vs **TEMPERATURE** 16 0.9 15 GBW 0.8 Gain-Bandwidth Product - MHz 0.7 13 12 11 11 Slew Rate - V/μs 0.6 0.5 0.4 0.3 0.2 SR-0.1 0 **└** -75 -25 50 75 100 125 Temperature - °C

# TOTAL HARMONIC DISTORTION + NOISE

**NSTRUMENTS**

### **OUTPUT VOLTAGE SWING**

### **OUTPUT VOLTAGE SWING**

# MAXIMUM OUTPUT VOLTAGE SWING

# OUTPUT LEAKAGE CURRENT

# **TYPICAL CHARACTERISTICS (continued)**

$T_A = 25$ °C,  $V_S = 5$  V,  $C_L = 0$  pF (unless otherwise noted)

### OFFSET VOLTAGE PRODUCTION DISTRIBUTION

### OFFSET VOLTAGE DRIFT PRODUCTION DISTRIBUTION

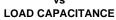

# SMALL-SIGNAL OVERSHOOT

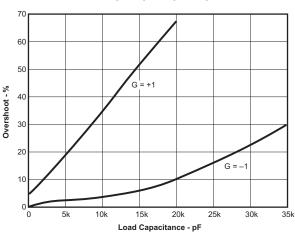

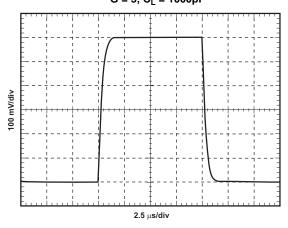

LARGE-SIGNAL STEP RESPONSE G = 3, C<sub>L</sub> = 1000pF

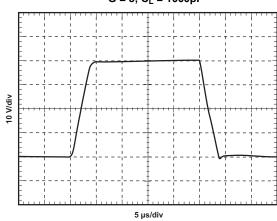

# SMALL-SIGNAL STEP RESPONSE $G = 1, C_L = 1000pF$

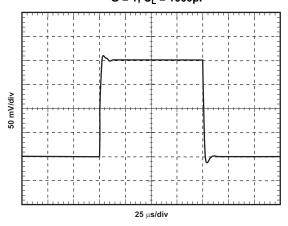

$\begin{aligned} \text{SMALL-SIGNAL STEP RESPONSE} \\ \text{G = 3, C}_{\text{L}} &= 1000 \text{pF} \end{aligned}$

#### APPLICATION INFORMATION

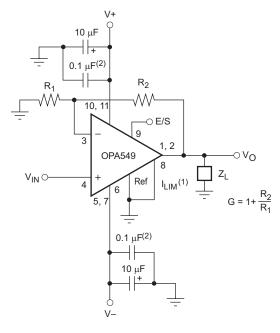

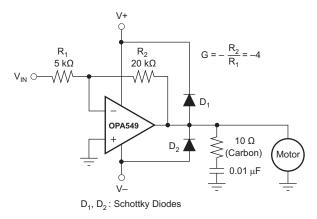

Figure 3 shows the OPA549 connected as a basic noninverting amplifier. The OPA549 can be used in virtually any operational amplifier configuration.

Power-supply terminals should be bypassed with low series impedance capacitors. The technique shown in Figure 3, using a ceramic and tantalum type in parallel, is recommended. Power-supply wiring should have low series impedance.

Be sure to connect both output pins (pins 1 and 2).

NOTES: (1) I<sub>LIM</sub>connected to Ref gives the maximum current limit, 10A (peak). (2) Connect capacitors directly to package power-supply pins.

Figure 3. Basic Circuit Connections

### **Power Supplies**

The OPA549 operates from single (8-V to 60-V) or dual (±4-V to ±30-V) supplies with excellent performance. Most behavior remains unchanged throughout the full operating voltage range. Parameters that vary significantly with operating voltage are shown in the Typical Characteristics. Some applications do not require equal positive and negative output voltage swing. Power-supply voltages do not need to be equal. The OPA549 can operate with as little as 8 V between the supplies and with up to 60 V between the supplies. For example, the positive supply could be set to 55 V with the negative supply at –5 V. Be sure to connect both V– pins (pins 5 and 7) to the negative power supply, and both V+ pins (pins 10 and 11) to the positive power supply. Package tab is internally connected to V–; however, do not use the tab to conduct current.

# Control Reference (Ref) Pin

The OPA549 features a reference (Ref) pin to which the  $I_{LIM}$  and the E/S pin are referred. Ref simply provides a reference point accessible to the user that can be set to V-, ground, or any reference of the user's choice. Ref cannot be set below the negative supply or above (V+) – 8 V. If the minimum  $V_S$  is used, Ref must be set at V-.

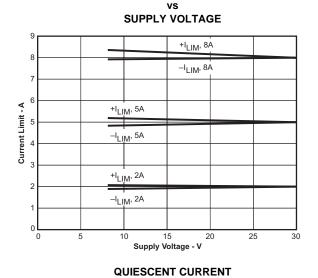

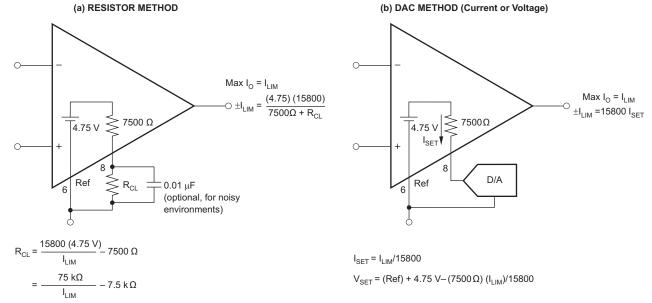

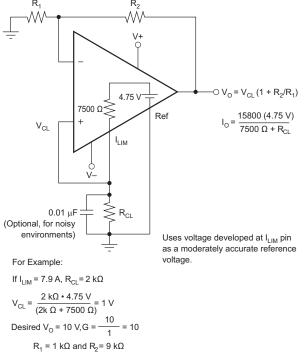

#### Adjustable Current Limit

The OPA549's accurate, user-defined current limit can be set from 0 A to 10 A by controlling the input to the I<sub>LIM</sub> pin. Unlike other designs, which use a power resistor in series with the output current path, the OPA549 senses the load indirectly. This allows the current limit to be set with a 0-µA to 633-µA control signal. In contrast, other designs require a limiting resistor to handle the full output current (up to 10 A in this case).

Although the design of the OPA549 allows output currents up to 10 A, it is not recommended that the device be operated continuously at that level. The highest rated continuous current capability is 8 A. Continuously running the OPA549 at output currents greater than 8 A will degrade long-term reliability.

Operation of the OPA549 with current limit less than 1 A results in reduced current limit accuracy. Applications requiring lower output current may be better suited to the OPA547 or OPA548.

#### **Resistor-Controlled Current Limit**

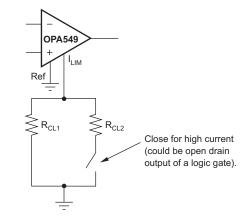

See Figure 4(a) for a simplified schematic of the internal circuitry used to set the current limit. Leaving the I<sub>LIM</sub> pin open programs the output current to zero, while connecting I<sub>LIM</sub> directly to Ref programs the maximum output current limit, typically 10 A.

With the OPA549, the simplest method for adjusting the current limit uses a resistor or potentiometer connected between the I<sub>LIM</sub> pin and Ref according to Equation 1:

$$R_{CL} = \frac{75kV}{I_{LIM}} - 7.5k\Omega \tag{1}$$

Refer to Figure 4 for commonly used values.

# **Digitally-Controlled Current Limit**

The low-level control signal (0  $\mu$ A to 633  $\mu$ A) also allows the current limit to be digitally controlled by setting either a current ( $I_{SET}$ ) or voltage ( $V_{SET}$ ). The output current  $I_{LIM}$  can be adjusted by varying  $I_{SET}$  according to Equation 2:

$$I_{SET} = \frac{I_{LIM}}{15800} \tag{2}$$

Figure 4(b) demonstrates a circuit configuration implementing this feature.

The output current I<sub>LIM</sub> can be adjusted by varying V<sub>SET</sub> according to Equation 3:

$$V_{SET} = (\text{Re f}) + 4.75 \text{V} - \frac{(7500W)(I_{LIM})}{15800}$$

(3)

demonstrates a circuit configuration implementing this feature.

OPA549 CURRENT LIMIT: 0 A to 10 A

| DESIRED<br>CURRENT LIMIT | RESISTOR <sup>(1)</sup> (R <sub>CL</sub> ) | CURRENT<br>(I <sub>SET</sub> ) | VOLTAGE<br>(V <sub>SET</sub> ) |

|--------------------------|--------------------------------------------|--------------------------------|--------------------------------|

| 0A(2)                    | I <sub>LIM</sub> Open                      | 0 μΑ                           | (Ref) + 4.75 V                 |

| 2.5 A                    | 22.6 kΩ                                    | 158 μΑ                         | (Ref) + 3.56 V                 |

| 3 A                      | 17.4 kΩ                                    | 190 μΑ                         | (Ref) + 3.33 V                 |

| 4 A                      | 11.3 k Ω                                   | 253 μΑ                         | (Ref) + 2.85 V                 |

| 5 A                      | 7.5 kΩ                                     | 316 μΑ                         | (Ref) + 2.38 V                 |

| 6 A                      | 4.99 kΩ                                    | 380 μΑ                         | (Ref) + 1.90 V                 |

| 7 A                      | 3.24 kΩ                                    | 443 μΑ                         | (Ref) + 1.43 V                 |

| 8 A                      | 1.87 kΩ                                    | 506 μΑ                         | (Ref) + 0.95 V                 |

| 9 A                      | 845 Ω                                      | 570 μΑ                         | (Ref) + 0.48 V                 |

| 10 A                     | I <sub>LIM</sub> Connected to Ref          | 633 μΑ                         | (Ref)                          |

NOTES: (1) Resistors are nearest standard 1% values. (2) Offset in the current limit circuitry may introduce approximately  $\pm 0.25$  A variation at low current limit values.

Figure 4. Adjustable Current Limit

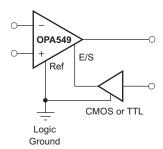

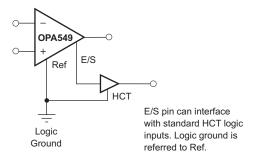

### Enable/Status (E/S) Pin

The enable/status pin provides two unique functions: 1) output disable by forcing the pin low, and 2) thermal shutdown indication by monitoring the voltage level at the pin. Either or both of these functions can be utilized in an application. For normal operation (output enabled), the E/S pin can be left open or driven high (at least 2.4 V above Ref). A small value capacitor connected between the E/S pin and  $C_{REF}$  may be required for noisy applications.

## **Output Disable**

To disable the output, the E/S pin is pulled to a logic low (no greater than 0.8 V above Ref). Typically the output is shut down in 1  $\mu$ s. To return the output to an enabled state, the E/S pin should be disconnected (open) or pulled to at least 2.4 V above Ref. It should be noted that driving the E/S pin high (output enabled) does not defeat internal shutdown; however, it does prevent the user from monitoring the thermal shutdown status. Figure 5 shows an example implementing this function.

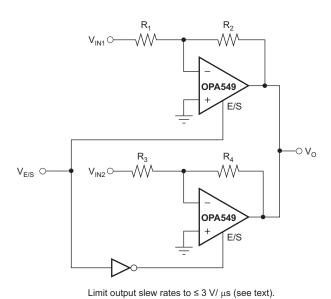

This function not only conserves power during idle periods (quiescent current drops to approximately 6 mA) but also allows multiplexing in multi-channel applications. See Figure 14 for two OPA549s in a switched amplifier configuration. The on/off state of the two amplifiers is controlled by the voltage on the E/S pin. Under these conditions, the disabled device will behave like a 750-pF load. Slewing faster than 3 V/µs will cause leakage current to rapidly increase in devices that are disabled, and will contribute additional load. At high temperature (125°C), the slewing threshold drops to approximately 2 V/µs. Input signals must be limited to avoid excessive slewing in multiplexed applications.

Figure 5. Output Disable

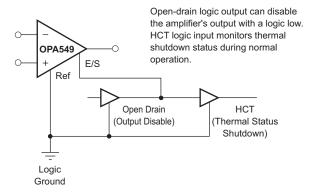

#### **Thermal Shutdown Status**

The OPA549 has thermal shutdown circuitry that protects the amplifier from damage. The thermal protection circuitry disables the output when the junction temperature reaches approximately 160°C and allows the device to cool. When the junction temperature cools to approximately 140°C, the output circuitry is automatically reenabled. Depending on load and signal conditions, the thermal protection circuit may cycle on and off. The E/S pin can be monitored to determine if the device is in shutdown. During normal operation, the voltage on the E/S pin is typically 3.5V above Ref. Once shutdown has occurred, this voltage drops to approximately 200 mV above Ref. Figure 6 shows an example implementing this function.

Figure 6. Thermal Shutdown Status

External logic circuitry or an LED can be used to indicate if the output has been thermally shutdown, see Figure 12.

### **Output Disable and Thermal Shutdown Status**

As mentioned earlier, the OPA549's output can be disabled and the disable status can be monitored simultaneously. Figure 7 provides an example of interfacing to the E/S pin.

Figure 7. Output Disable and Thermal Shutdown Status

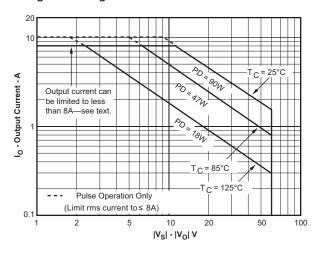

## Safe Operating Area

Stress on the output transistors is determined both by the output current and by the output voltage across the conducting output transistor,  $V_S - V_O$ . The power dissipated by the output transistor is equal to the product of the output current and the voltage across the conducting transistor,  $V_S - V_O$ . The safe operating area (SOA curve, Figure 8) shows the permissible range of voltage and current.

Figure 8. Safe Operating Area

The safe output current decreases as  $V_S - V_O$  increases. Output short circuits are a very demanding case for SOA. A short circuit to ground forces the full power-supply voltage (V+ or V–) across the conducting transistor. Increasing the case temperature reduces the safe output current that can be tolerated without activating the thermal shutdown circuit of the OPA549. For further insight on SOA, consult Application Bulletin (SBOA022).

### **Power Dissipation**

Power dissipation depends on power supply, signal, and load conditions. For dc signals, power dissipation is equal to the product of output current times the voltage across the conducting output transistor. Power dissipation can be minimized by using the lowest possible power-supply voltage necessary to assure the required output voltage swing.

For resistive loads, the maximum power dissipation occurs at a dc output voltage of one-half the power-supply voltage. Dissipation with ac signals is lower. Application Bulletin (SBOA022) explains how to calculate or measure power dissipation with unusual signals and loads.

### **Thermal Protection**

Power dissipated in the OPA549 will cause the junction temperature to rise. Internal thermal shutdown circuitry shuts down the output when the die temperature reaches approximately 160°C and resets when the die has cooled to 140°C. Depending on load and signal conditions, the thermal protection circuit may cycle on and off. This limits the dissipation of the amplifier but may have an undesirable effect on the load.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heat sink. For reliable operation, junction temperature should be limited to 125°C maximum. To estimate the margin of safety in a complete design (including heat sink) increase the ambient temperature until the thermal protection is triggered.

Use worst-case load and signal conditions. For good reliability, thermal protection should trigger more than 35°C above the maximum expected ambient condition of your application. This produces a junction temperature of 125°C at the maximum expected ambient condition.

The internal protection circuitry of the OPA549 was designed to protect against overload conditions. It was not intended to replace proper heat sinking. Continuously running the OPA549 into thermal shutdown will degrade reliability.

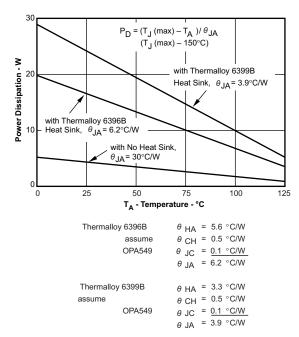

## **Amplifier Mounting and Heat Sinking**

Most applications require a heat sink to assure that the maximum operating junction temperature (125°C) is not exceeded. In addition, the junction temperature should be kept as low as possible for increased reliability. Junction temperature can be determined according to the Equations:

$$T_{J} = T_{A} + P_{D}\theta_{JA} \tag{4}$$

$$\theta_{JA} = \theta_{JC} + \theta_{CH} + \theta_{HA} \tag{5}$$

#### Where:

$T_{J}$  = Junction Temperature (°C)

$T_A$  = Ambient Temperature (°C)

P<sub>D</sub> = Power Dissipated (W)

$\theta_{JC}$  = Junction-to-Case Thermal Resistance (°C/W)

$\theta_{CH}$  = Case-to-Heat Sink Thermal Resistance (°C/W)

$\theta_{HA}$  = Heat Sink-to-Ambient Thermal Resistance (°C/W)

$\theta_{JA}$  = Junction-to-Air Thermal Resistance (°C/W)

Figure 9 shows maximum power dissipation versus ambient temperature with and without the use of a heat sink. Using a heat sink significantly increases the maximum power dissipation at a given ambient temperature, as shown in Figure 9.

The challenge in selecting the heat sink required lies in determining the power dissipated by the OPA549. For dc output, power dissipation is simply the load current times the voltage developed across the conducting output transistor,  $P_D = I_L \ (V_S - V_O)$ . Other loads are not as simple. Consult the SBOA022 Application Report for further insight on calculating power dissipation. Once power dissipation for an application is known, the proper heat sink can be selected.

### **Heat Sink Selection Example**

An 11-lead power ZIP package is dissipating 10 Watts. The maximum expected ambient temperature is 40°C. Find the proper heat sink to keep the junction temperature below 125°C (150°C minus 25°C safety margin).

Combining Equation 4 and Equation 5 gives:

$$T_{J} = T_{A} + P_{D} \left( \theta_{JC} + \theta_{CH} + \theta_{HA} \right) \tag{6}$$

$T_J$ ,  $T_A$ , and  $P_D$  are given.  $\theta_{JC}$  is provided in the Specifications Table, 0.1°C/W (dc).  $\theta_{CH}$  can be obtained from the heat sink manufacturer. Its value depends on heat sink size, area, and material used. Semiconductor package type, mounting screw torque, insulating material used (if any), and thermal joint compound used (if any) also affect  $\theta_{CH}$ . A typical  $\theta_{CH}$  for a mounted 11-lead power ZIP package is 0.5°C/W. Now we can solve for  $\theta_{HA}$ :

$$\begin{split} \theta_{HA} &= [(T_J - T_A)/P_D] - \theta_{JC} - \theta_{CH} \\ \theta_{HA} &= [(125^{\circ}C - 55^{\circ}C)/10 \text{ W}] - 0.1^{\circ}C/W - 0.5^{\circ}C/W \\ \theta_{HA} &= 6.4^{\circ}C/W \end{split}$$

To maintain junction temperature below 125°C, the heat sink selected must have a  $\theta_{HA}$  less than 6.4°C/W. In other words, the heat sink temperature rise above ambient must be less than 64°C (6.4°C/W • 10 W). For example, at 10 W, Thermalloy model number 6396B has a heat sink temperature rise of 56°C ( $\theta_{HA}$  = 56°C/10 W = 5.6°C/W), which is below the required 66°C required in this example. Thermalloy model number 6399B has a sink temperature rise of 33°C ( $\theta_{HA}$  = 33°C/10 W = 3.3°C/W), which is also below the required 66°C required in this example. Figure 9 shows power dissipation versus ambient temperature for a 11-lead power ZIP package with the Thermalloy 6396B and 6399B heat sinks.

Figure 9. Maximum Power Dissipation vs Ambient Temperature

Another variable to consider is natural convection versus forced convection air flow. Forced-air cooling by a small fan can lower  $\theta_{CA}$  ( $\theta_{CH}$  +  $\theta_{HA}$ ) dramatically. Some heat sink manufacturers provide thermal data for both of these cases. Heat sink performance is generally specified under idealized conditions that may be difficult to achieve in an actual application. For additional information on determining heat sink requirements, consult Application Report (SBOA021).

As mentioned earlier, once a heat sink has been selected, the complete design should be tested under worst-case load and signal conditions to ensure proper thermal protection. Any tendency to activate the thermal protection circuitry may indicate inadequate heat sinking.

The tab of the 11-lead power ZIP package is electrically connected to the negative supply, V—. It may be desirable to isolate the tab of the 11-lead power ZIP package from its mounting surface with a mica (or other film) insulator. For lowest overall thermal resistance, it is best to isolate the entire heat sink/OPA549 structure from the mounting surface rather than to use an insulator between the semiconductor and heat sink.

### **Output Stage Compensation**

The complex load impedances common in power op amp applications can cause output stage instability. For normal operation, output compensation circuitry is typically not required. However, for difficult loads or if the OPA549 is intended to be driven into current limit, an R/C network may be required. Figure 10 shows an output R/C compensation (snubber) network which generally provides excellent stability.

Figure 10. Motor Drive Circuit

A snubber circuit may also enhance stability when driving large capacitive loads (> 1000 pF) or inductive loads (motors, loads separated from the amplifier by long cables). Typically,  $3-\Omega$  to  $10-\Omega$  resistors in series with  $0.01-\mu$ F to  $0.1-\mu$ F capacitors is adequate. Some variations in circuit values may be required with certain loads.

### **Output Protection**

Reactive and EMF-generating loads can return load current to the amplifier, causing the output voltage to exceed the power-supply voltage. This damaging condition can be avoided with clamp diodes from the output terminal to the power supplies, as shown in Figure 10. Schottky rectifier diodes with an 8-A or greater continuous rating are recommended.

### **Voltage Source Application**

Figure 11 illustrates how to use the OPA549 to provide an accurate voltage source with only three external resistors. First, the current limit resistor,  $R_{CL}$ , is chosen according to the desired output current. The resulting voltage at the  $I_{LIM}$  pin is constant and stable over temperature. This voltage,  $V_{CL}$ , is connected to the noninverting input of the op amp and used as a voltage reference, thus eliminating the need for an external reference. The feedback resistors are selected to gain  $V_{CL}$  to the desired output voltage level.

Figure 11. Voltage Source

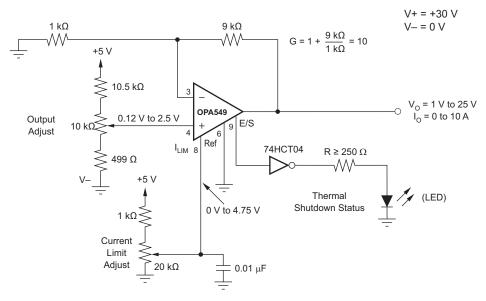

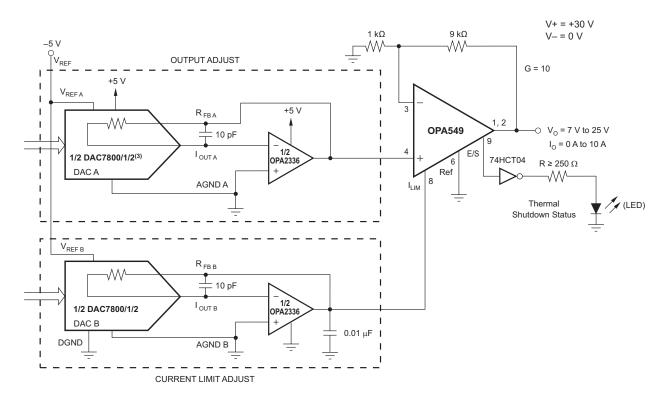

# **Programmable Power Supply**

A programmable source and sink power supply can easily be built using the OPA549. Both the output voltage and output current are user-controlled. See Figure 12 for a circuit using potentiometers to adjust the output voltage and current while Figure 13 uses DACs. An LED connected to the E/S pin through a logic gate indicates if the OPA549 is in thermal shutdown.

Figure 12. Resistor-Controlled Programmable Power Supply

Choose DAC780X based on digital interface: DAC7800—12-bit interface, DAC7801—8-bit interface + 4 bits, DAC7802—serial interface.

Figure 13. Digitally-Controlled Programmable Power Supply

Figure 14. Switched Amplifier

Figure 15. Multiple Current Limit Values

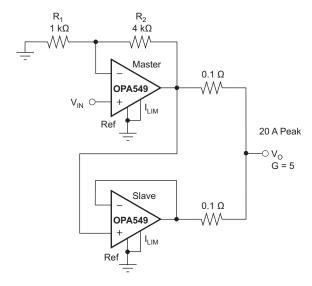

Figure 16. Parallel Output for Increased Output Current

www.ti.com 11-Nov-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins              | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                             |                       |      | (4)                           | (5)                        |              |                  |

| OPA549MKVC            | Active | Production    | Power Package<br>(KVC)   11 | 25   TUBE             | Yes  | SN                            | N/A for Pkg Type           | -55 to 125   | OPA549M          |

| OPA549MKVC.A          | Active | Production    | Power Package<br>(KVC)   11 | 25   TUBE             | Yes  | SN                            | N/A for Pkg Type           | -55 to 125   | OPA549M          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

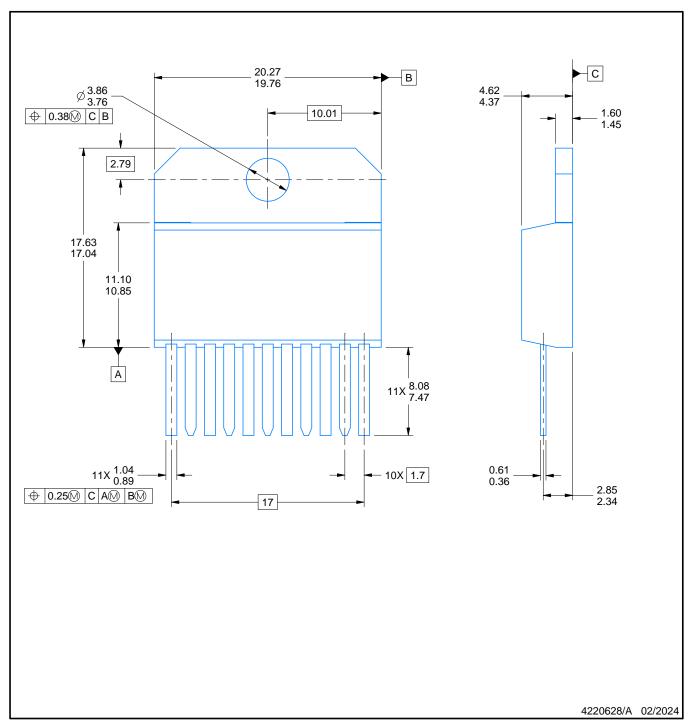

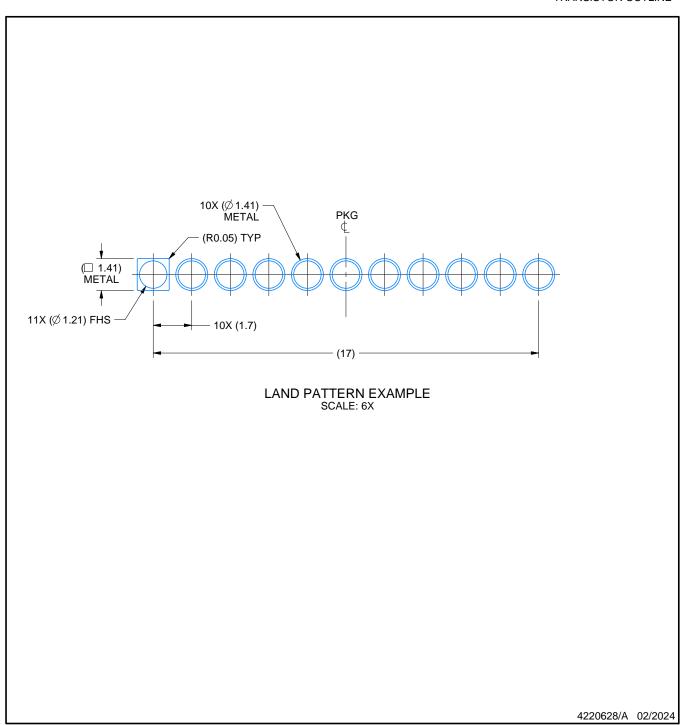

TRANSISTOR OUTLINE

## NOTES:

- Dimensions are in millimeters. Any dimension in brackets or parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Falls within JEDEC MO-48-AA. Reference for body dimensions only (excluding lead forming dimensions).

TRANSISTOR OUTLINE

NOTES: (continued)

4. Refer to IPC-7251 which may have alternate design recommendations.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月