**OPA141**

OPA4141

# 单电源、10MHz、轨至轨输出、低噪声、JFET 放大器

查询样品: OPA141, OPA2141, OPA4141

#### 特性

低电源电流: 2.3mA(最大值)

低失调漂移: 10μV/℃(最大值)

低输入偏置电流: 20pA(最大值)

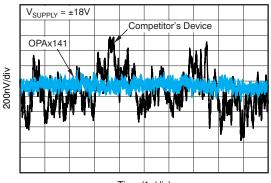

超低1/f噪声: 250nV<sub>PP</sub>

低噪声: 6.5nV/√Hz

• 宽带宽: 10MHz

• 转换速率: 20 V/µs

• 输入电压范围包括V—

• 轨至轨输出

• 单电源操作: 4.5V至36

双电源操作: ±2.25V至±18V

• 无相位反转

MSOP-8、TSSOP 封装

#### 应用

- 电池供电型仪器

- 工业控制

- 医疗仪表

- 光电二极管放大器

- 有源滤波器

- 数据采集系统

- 便携式音频

- 自动测试系统

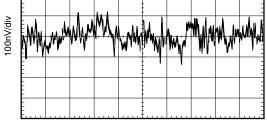

#### 图 1. 0.1Hz至10Hz噪声

Time (1s/div)

#### 说明

OPA141、OPA2141 和 OPA4141放大器系列为低功耗 JFET输入放大器,具有优良的漂移特性和低输入偏置电流。 轨至轨输出摆幅与包括了V—的输入范围使得设计人员不仅能够充分利用 JFET 放大器的低噪声特性,同时还能实现与新式的单电源、高精度模数转换器 (ADC) 和数模转换器 (DAC) 的连接。

OPA141 实现了10MHz 的单位增益带宽和 20 V/µs 的转换速率,而仅消耗 1.8mA(典型值)的静态电流。该器件采用 4.5V 至 36V 的单工作电源或±2.25V 至±18V 的双工作电源。

所有版本的技术规格均针对一**40**℃ 至**+125**℃ 的温度 范围而拟订,以便在最严苛的环境中使用。

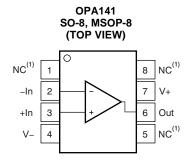

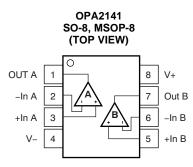

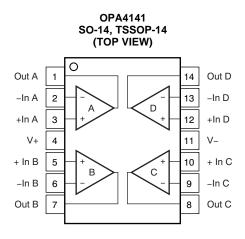

OPA141(单通道器件)和 OPA2141(双通道器件)版本采用MSOP-8和 SO-8 封装; OPA4141(四通道器件)则采用 SO-14和 TSSOP-14 封装。

相关产品

| 特性                                | 产品                    |

|-----------------------------------|-----------------------|

| 高精度、低功耗、10MHz FET输入工业运算放大器        | OPA140 <sup>(1)</sup> |

| 采用SOT-23封装的2.2nV/√Hz、低功耗、36V运算放大器 | OPA209 <sup>(1)</sup> |

| 低噪声、高精度、JFET 输入运算放大器              | OPA827                |

| 低噪声、低IQ、高精度运算放大器                  | OPA376                |

| 高速、FET 输入运算放大器                    | OPA132                |

1. 前瞻性产品,预计于2010年第三季度供货。

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range (unless otherwise noted).

|                           |                            | VALUE                  | UNIT |  |  |

|---------------------------|----------------------------|------------------------|------|--|--|

| Supply Voltage            |                            | ±20                    | V    |  |  |

| Signal Input<br>Terminals | Voltage <sup>(2)</sup>     | (V-) -0.5 to (V+) +0.5 | V    |  |  |

|                           | Current <sup>(2)</sup>     | ±10                    | mA   |  |  |

| Output Short-Cir          | rcuit <sup>(3)</sup>       | Continuous             |      |  |  |

| Operating Temp            | erature, T <sub>A</sub>    | -55 to +150            | °C   |  |  |

| Storage Temper            | rature, T <sub>A</sub>     | -65 to +150            | °C   |  |  |

| Junction Tempe            | rature, T <sub>J</sub>     | +150                   | °C   |  |  |

| ESD Botings               | Human Body Model (HBM)     | 2000                   | V    |  |  |

| ESD Ratings               | Charged Device Model (CDM) | 500                    | V    |  |  |

- (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

- (2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current limited to 10 mA or less.

- (3) Short-circuit to V<sub>S</sub>/2 (ground in symmetrical dual-supply setups), one amplifier per package.

#### PACKAGE INFORMATION(1)

| PRODUCT   | PACKAGE-LEAD | PACKAGE DESIGNATOR | PACKAGE MARKING |

|-----------|--------------|--------------------|-----------------|

| ODA444    | SO-8         | D                  | O141A           |

| OPA141    | MSOP-8       | DGK                | 141             |

| OD40444   | SO-8         | D                  | O2141A          |

| OPA2141   | MSOP-8       | DGK                | 2141            |

| ODA 44.44 | TSSOP-14     | PW                 | O4141A          |

| OPA4141   | SO-14        | D                  | O4141AG4        |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder at <a href="https://www.ti.com">www.ti.com</a>.

#### THERMAL INFORMATION

|                         |                                                             | OPA141,<br>OPA2141 | OPA141,<br>OPA2141 |       |

|-------------------------|-------------------------------------------------------------|--------------------|--------------------|-------|

|                         | THERMAL METRIC                                              | D (SO)             | DGK (MSOP)(1)      | UNITS |

|                         |                                                             | 8                  | 8                  |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance (2)                  | 160                | 180                |       |

| $\theta_{JC(top)}$      | Junction-to-case(top) thermal resistance (3)                | 75                 | 55                 |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance (4)                    | 60                 | 130                | °C/W  |

| ΨЈТ                     | Junction-to-top characterization parameter (5)              | 9                  | n/a                | C/VV  |

| ΨЈВ                     | Junction-to-board characterization parameter <sup>(6)</sup> | 50                 | 120                |       |

| θ <sub>JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance <sup>(7)</sup>  | n/a                | n/a                |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted

- from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

- JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### THERMAL INFORMATION

|                         |                                                     | OPA4141 | OPA4141                   |       |

|-------------------------|-----------------------------------------------------|---------|---------------------------|-------|

|                         | THERMAL METRIC                                      | D (SO)  | PW (TSSOP) <sup>(1)</sup> | UNITS |

|                         |                                                     | 14      | 14                        |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance (2)          | 97      | 135                       |       |

| θ <sub>JC(top)</sub>    | Junction-to-case(top) thermal resistance (3)        | 56      | 45                        |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(4)</sup> | 53      | 66                        | 90.04 |

| ΨЈТ                     | Junction-to-top characterization parameter (5)      | 19      | n/a                       | °C/W  |

| ΨЈВ                     | Junction-to-board characterization parameter (6)    | 46      | 60                        |       |

| θ <sub>JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance (7)     | n/a     | n/a                       |       |

- For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDÉC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## ELECTRICAL CHARACTERISTICS: $V_S = +4.5V$ to +36V; $\pm 2.25V$ to $\pm 18V$

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $R_L = 2k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

|                               |                      |                                                             | OPA141    | OPA141, OPA2141, OPA4141 |          |                        |  |  |

|-------------------------------|----------------------|-------------------------------------------------------------|-----------|--------------------------|----------|------------------------|--|--|

| PARAMETER                     |                      | CONDITIONS                                                  | MIN       | TYP                      | MAX      | UNIT                   |  |  |

| OFFSET VOLTAGE                |                      |                                                             |           |                          |          |                        |  |  |

| Offset Voltage, RTI           | Vos                  | $V_S = \pm 18V$                                             |           | ±1                       | ±3.5     | mV                     |  |  |

| Over Temperature              |                      | V <sub>S</sub> = ±18V                                       |           |                          | ±4.3     | mV                     |  |  |

| Drift                         | dV <sub>OS</sub> /dT | V <sub>S</sub> = ±18V                                       |           | ±2                       | ±10      | μ <b>۷/</b> ° <b>C</b> |  |  |

| vs Power Supply               | PSRR                 | V <sub>S</sub> = ±2.25V to ±18V                             |           | ±0.14                    | ±2       | μV/V                   |  |  |

| Over Temperature              |                      | V <sub>S</sub> = ±2.25V to ±18V                             |           |                          | ±4       | μ <b>V/V</b>           |  |  |

| INPUT BIAS CURRENT            |                      |                                                             |           |                          |          |                        |  |  |

| Input Bias Current            | Ι <sub>Β</sub>       |                                                             |           | ±2                       | ±20      | рА                     |  |  |

| Over Temperature              |                      |                                                             |           |                          | ±5       | nA                     |  |  |

| Input Offset Current          | Ios                  |                                                             |           | ±2                       | ±20      | pА                     |  |  |

| Over Temperature              |                      |                                                             |           |                          | ±1       | nA                     |  |  |

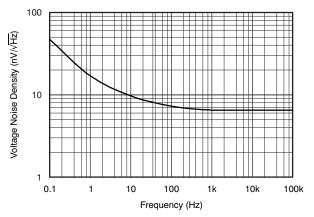

| NOISE                         |                      |                                                             |           |                          |          |                        |  |  |

| Input Voltage Noise           |                      |                                                             |           |                          |          |                        |  |  |

| f = 0.1Hz to 10Hz             |                      |                                                             |           | 250                      |          | $nV_{PP}$              |  |  |

| f = 0.1Hz to 10Hz             |                      |                                                             |           | 42                       |          | $nV_{RMS}$             |  |  |

| Input Voltage Noise Density   | e <sub>n</sub>       |                                                             |           |                          |          |                        |  |  |

| f = 10Hz                      |                      |                                                             |           | 12                       |          | nV/√ <del>Hz</del>     |  |  |

| f = 100Hz                     |                      |                                                             |           | 6.5                      |          | nV/√ <del>Hz</del>     |  |  |

| f = 1kHz                      |                      |                                                             |           | 6.5                      |          | nV/√ <del>Hz</del>     |  |  |

| Input Current Noise Density   | i <sub>n</sub>       |                                                             |           |                          |          |                        |  |  |

| f = 1kHz                      |                      |                                                             |           | 0.8                      |          | fA/√Hz                 |  |  |

| INPUT VOLTAGE RANGE           |                      |                                                             |           |                          |          |                        |  |  |

| Common-Mode Voltage Range     | V <sub>CM</sub>      |                                                             | (V-) -0.1 |                          | (V+)-3.5 | ٧                      |  |  |

| Common-Mode Rejection Ratio   | CMRR                 | $V_S = \pm 18V$ , $V_{CM} = (V-) -0.1V$<br>to $(V+) - 3.5V$ | 120       | 126                      |          | dB                     |  |  |

| Over Temperature              |                      | $V_S = \pm 18V$ , $V_{CM} = (V-) -0.1V$<br>to $(V+) - 3.5V$ | 120       |                          |          | dB                     |  |  |

| INPUT IMPEDANCE               |                      |                                                             |           |                          |          |                        |  |  |

| Differential                  |                      |                                                             |           | 10 <sup>13</sup>    8    |          | Ω    pF                |  |  |

| Common-Mode                   |                      | $V_{CM} = (V-) -0.1V$ to $(V+) -3.5V$                       |           | 10 <sup>13</sup>    6    |          | Ω    pF                |  |  |

| OPEN-LOOP GAIN                |                      |                                                             |           |                          |          |                        |  |  |

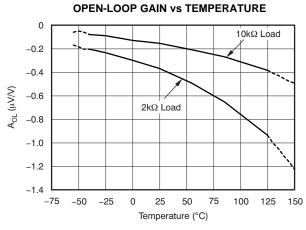

| Open-Loop Voltage Gain        | $A_{OL}$             | $V_O = (V-)+0.35V$ to $(V+)-0.35V$ , $R_L = 2k\Omega$       | 114       | 126                      |          | dB                     |  |  |

| Over Temperature              |                      | $V_O = (V-)+0.35V$ to $(V+)-0.35V$ , $R_L = 2k\Omega$       | 108       |                          |          | dB                     |  |  |

| FREQUENCY RESPONSE            |                      |                                                             |           |                          |          |                        |  |  |

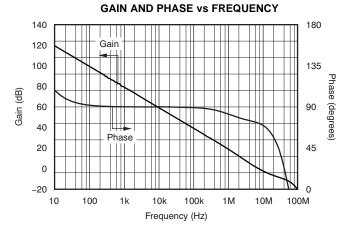

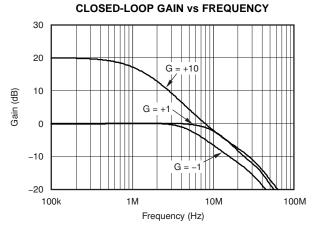

| Gain Bandwidth Product        | BW                   |                                                             |           | 10                       |          | MHz                    |  |  |

| Slew Rate                     | -                    |                                                             |           | 20                       |          | V/µs                   |  |  |

| Settling Time, 12-bit (0.024) |                      |                                                             |           | 880                      |          | ns                     |  |  |

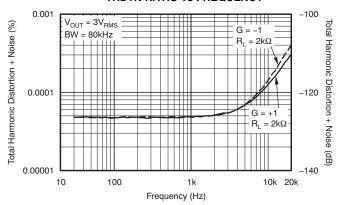

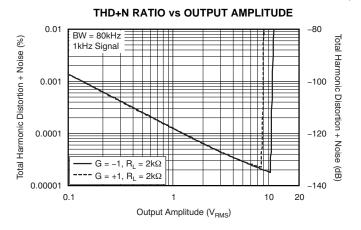

| THD+N                         |                      | 1kHz, G = 1, V <sub>O</sub> = 3.5V <sub>RMS</sub>           |           | 0.00005                  |          | %                      |  |  |

| Overload Recovery Time        |                      |                                                             |           | 600                      |          | ns                     |  |  |

## ELECTRICAL CHARACTERISTICS: $V_S = +4.5V$ to +36V; $\pm 2.25V$ to $\pm 18V$ (continued)

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $R_L = 2k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

|                                   |                   |                                              | OPA141,   | OPA2141,  | OPA4141   |      |  |

|-----------------------------------|-------------------|----------------------------------------------|-----------|-----------|-----------|------|--|

| PARAMETER                         |                   | CONDITIONS                                   | MIN       | TYP       | MAX       | UNIT |  |

| ОИТРИТ                            |                   |                                              |           |           |           |      |  |

| Voltage Output                    | Vo                | $R_L = 10k\Omega$                            | (V-)+0.2  |           | (V+)-0.2  | V    |  |

|                                   |                   | $R_L = 2k\Omega$                             | (V-)+0.35 |           | (V+)-0.35 | V    |  |

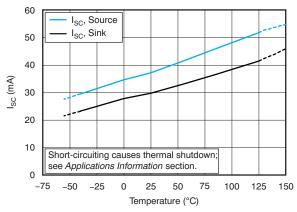

| Short-Circuit Current             | I <sub>SC</sub>   | Source                                       |           | +36       |           | mA   |  |

|                                   |                   | Sink                                         |           | -30       |           | mA   |  |

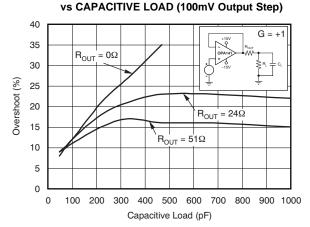

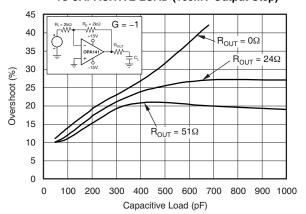

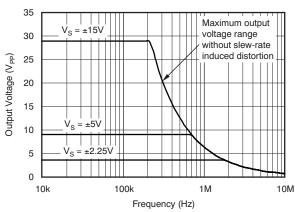

| Capacitive Load Drive             | C <sub>LOAD</sub> |                                              | See Figu  | re 20 and | Figure 21 |      |  |

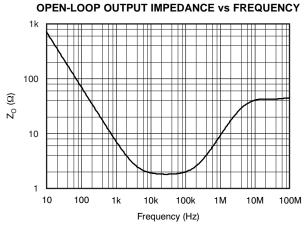

| Open-Loop Output Impedance        | R <sub>O</sub>    | f = 1MHz, I <sub>O</sub> = 0 (See Figure 19) |           | 10        |           | Ω    |  |

| POWER SUPPLY                      |                   |                                              |           |           |           |      |  |

| Specified Voltage Range           | Vs                |                                              | ±2.25     |           | ±18       | V    |  |

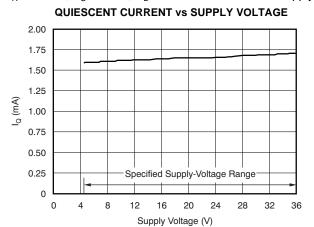

| Quiescent Current (per amplifier) | IQ                | I <sub>O</sub> = 0mA                         |           | 1.8       | 2.3       | mA   |  |

| Over Temperature                  |                   |                                              |           |           | 3.1       | mA   |  |

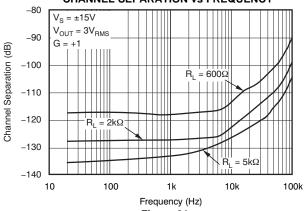

| CHANNEL SEPARATION                |                   |                                              |           |           |           |      |  |

| Channel Separation                |                   | At dc                                        |           | 0.02      |           | μV/V |  |

|                                   |                   | At 100kHz                                    |           | 10        |           | μV/V |  |

| TEMPERATURE RANGE                 |                   |                                              |           |           |           |      |  |

| Specified Range                   |                   |                                              | -40       |           | +125      | °C   |  |

| Operating Range                   |                   |                                              | -55       |           | +150      | °C   |  |

#### **PIN ASSIGNMENTS**

(1) NC denotes no internal connection.

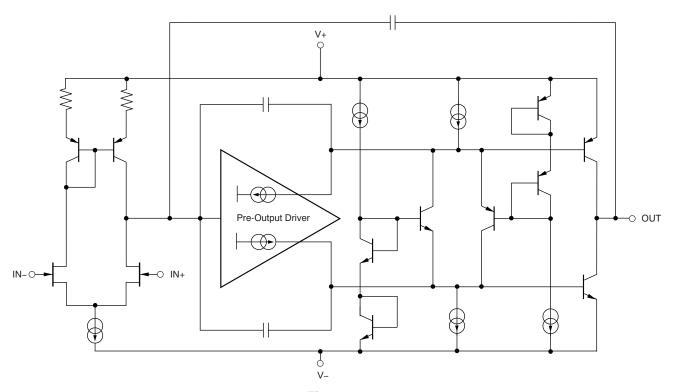

#### SIMPLIFIED BLOCK DIAGRAM

Figure 2.

#### **TYPICAL CHARACTERISTICS SUMMARY**

#### **TABLE OF GRAPHS**

**Table 1. Characteristic Performance Measurements**

| DESCRIPTION                                               | FIGURE    |

|-----------------------------------------------------------|-----------|

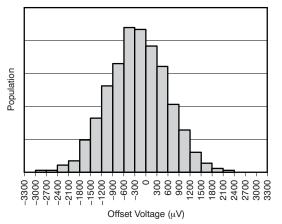

| Offset Voltage Production Distribution                    | Figure 3  |

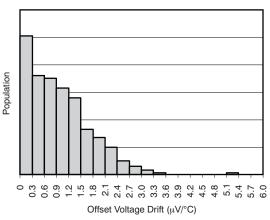

| Offset Voltage Drift Distribution                         | Figure 4  |

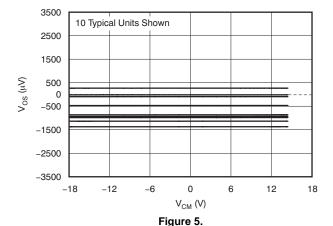

| Offset Voltage vs Common-Mode Voltage (Max Supply)        | Figure 5  |

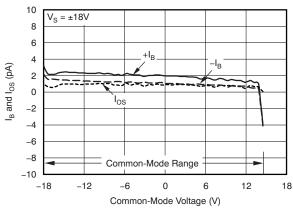

| I <sub>B</sub> and I <sub>OS</sub> vs Common-Mode Voltage | Figure 6  |

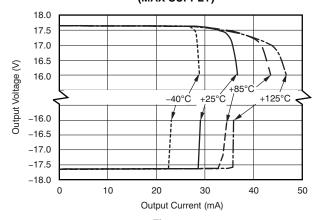

| Output Voltage Swing vs Output Current                    | Figure 7  |

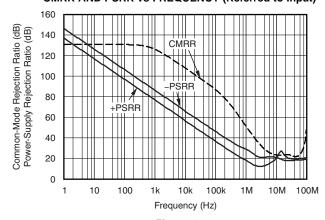

| CMRR and PSRR vs Frequency (RTI)                          | Figure 8  |

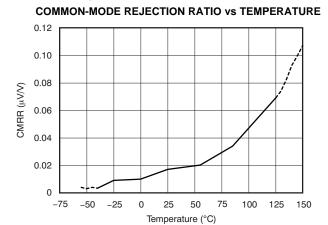

| Common-Mode Rejection Ratio vs Temperature                | Figure 9  |

| 0.1Hz to 10Hz Noise                                       | Figure 10 |

| Input Voltage Noise Density vs Frequency                  | Figure 11 |

| THD+N Ratio vs Frequency (80kHz AP Bandwidth)             | Figure 12 |

| THD+N Ratio vs Output Amplitude                           | Figure 13 |

| Quiescent Current vs Temperature                          | Figure 14 |

| Quiescent Current vs Supply Voltage                       | Figure 15 |

| Gain and Phase vs Frequency                               | Figure 16 |

| Closed-Loop Gain vs Frequency                             | Figure 17 |

| Open-Loop Gain vs Temperature                             | Figure 18 |

| Open-Loop Output Impedance vs Frequency                   | Figure 19 |

| Small-Signal Overshoot vs Capacitive Load (G = +1)        | Figure 20 |

| Small-Signal Overshoot vs Capacitive Load (G = −1)        | Figure 21 |

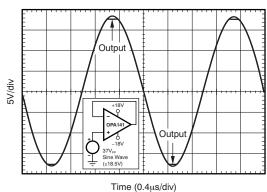

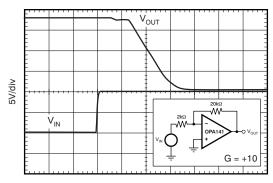

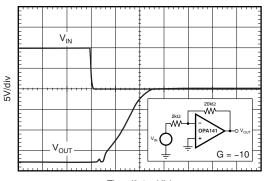

| No Phase Reversal                                         | Figure 22 |

| Positive Overload Recovery                                | Figure 23 |

| Negative Overload Recovery                                | Figure 24 |

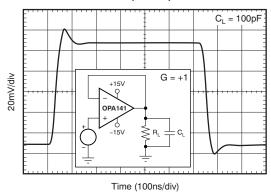

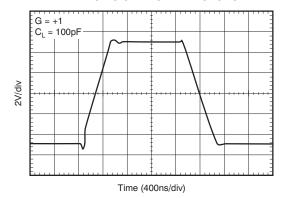

| Small-Signal Step Response (G = +1)                       | Figure 25 |

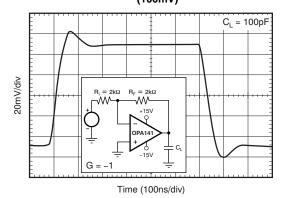

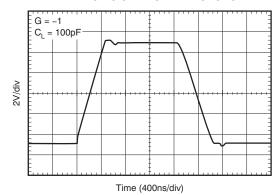

| Small-Signal Step Response (G = -1)                       | Figure 26 |

| Large-Signal Step Response (G = +1)                       | Figure 27 |

| Large-Signal Step Response (G = -1)                       | Figure 28 |

| Short-Circuit Current vs Temperature                      | Figure 29 |

| Maximum Output Voltage vs Frequency                       | Figure 30 |

| Channel Separation vs Frequency                           | Figure 31 |

#### **TYPICAL CHARACTERISTICS**

At  $T_A$  = +25°C,  $V_S$  = ±18V,  $R_L$  = 2k $\Omega$  connected to midsupply,  $V_{CM}$  =  $V_{OUT}$  = midsupply, unless otherwise noted.

#### OFFSET VOLTAGE PRODUCTION DISTRIBUTION

Figure 3.

# OFFSET VOLTAGE vs COMMON-MODE VOLTAGE

OUTPUT VOLTAGE SWING vs OUTPUT CURRENT (MAX SUPPLY)

Figure 7.

#### OFFSET VOLTAGE DRIFT DISTRIBUTION

Figure 4.

#### IB AND IOS VS COMMON-MODE VOLTAGE

Figure 6.

#### CMRR AND PSRR vs FREQUENCY (Referred to Input)

Figure 8.

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 18V$ ,  $R_L = 2k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

0.1Hz to 10Hz NOISE

Figure 9.

Figure 10.

Time (1s/div)

THD+N RATIO vs FREQUENCY

Figure 11.

Figure 12.

**QUIESCENT CURRENT vs TEMPERATURE**

2.0 <del>(YE)</del> 1.5 0.5

0

2.5

-75 -50 -25

Figure 13.

Temperature (°C) Figure 14.

50 75

100

125 150

25

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 18V$ ,  $R_L = 2k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

Figure 15.

Figure 16.

Figure 17.

Figure 18.

SMALL-SIGNAL OVERSHOOT

Figure 20.

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 18V$ ,  $R_L = 2k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

# SMALL-SIGNAL OVERSHOOT vs CAPACITIVE LOAD (100mV Output Step)

Figure 21.

#### **NO PHASE REVERSAL**

Figure 22.

#### **POSITIVE OVERLOAD RECOVERY**

Time  $(0.4\mu\text{s/div})$

#### **NEGATIVE OVERLOAD RECOVERY**

Time (0.4 $\mu$ s/div) Figure 24.

Figure 23.

# SMALL-SIGNAL STEP RESPONSE (100mV)

Figure 25.

# SMALL-SIGNAL STEP RESPONSE (100mV)

Figure 26.

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 18V$ ,  $R_L = 2k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

#### **LARGE-SIGNAL STEP RESPONSE**

Figure 27.

LARGE-SIGNAL STEP RESPONSE

Figure 28.

#### SHORT-CIRCUIT CURRENT vs TEMPERATURE

Figure 29.

#### MAXIMUM OUTPUT VOLTAGE vs FREQUENCY

Figure 30.

#### CHANNEL SEPARATION vs FREQUENCY

Figure 31.

#### APPLICATION INFORMATION

The OPA141, OPA2141, and OPA4141 are unity-gain stable, operational amplifiers with very low noise, input bias current, and input offset voltage. Applications with noisy or high-impedance power supplies require decoupling capacitors placed close to the device pins. In most cases, 0.1µF capacitors are adequate. Figure 2 shows a simplified schematic of the OPA141.

#### **OPERATING VOLTAGE**

The OPA141, OPA2141, and OPA4141 series of op amps can be used with single or dual supplies from an operating range of  $V_S = +4.5 \text{V}$  ( $\pm 2.25 \text{V}$ ) and up to  $V_S = +36 \text{V}$  ( $\pm 18 \text{V}$ ). These devices do not require symmetrical supplies; they only require a minimum supply voltage of +4.5V ( $\pm 2.25 \text{V}$ ). For  $V_S$  less than  $\pm 3.5 \text{V}$ , the common-mode input range does not include midsupply. Supply voltages higher than +40V can permanently damage the device; see the Absolute Maximum Ratings table. Key parameters are specified over the operating temperature range,  $T_A = -40 \, ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ . Key parameters that vary over the supply voltage or temperature range are shown in the Typical Characteristics section of this data sheet.

#### **CAPACITIVE LOAD AND STABILITY**

The dynamic characteristics of the OPAx141 have been optimized for commonly encountered gains, loads, and operating conditions. The combination of low closed-loop gain and high capacitive loads decreases the phase margin of the amplifier and can lead to gain peaking or oscillations. As a result, heavier capacitive loads must be isolated from the output. The simplest way to achieve this isolation is to add a small resistor ( $R_{OUT}$  equal to  $50\Omega$ , for example) in series with the output.

Figure 20 and Figure 21 illustrate graphs of *Small-Signal Overshoot vs Capacitive Load* for several values of R<sub>OUT</sub>. Also, refer to Applications Bulletin AB-028 (literature number SBOA015, available for download from the TI web site) for details of analysis techniques and application circuits.

#### **NOISE PERFORMANCE**

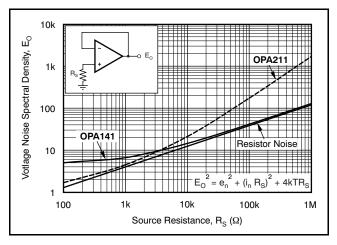

Figure 32 shows the total circuit noise for varying source impedances with the operational amplifier in a unity-gain configuration (with no feedback resistor network and therefore no additional noise contributions). The OPA141 and OPA211 are shown with total circuit noise calculated. The op amp itself

contributes both a voltage noise component and a current noise component. The voltage noise is commonly modeled as a time-varying component of the offset voltage. The current noise is modeled as the time-varying component of the input bias current and reacts with the source resistance to create a voltage component of noise. Therefore, the lowest noise op amp for a given application depends on the source impedance. For low source impedance, current noise is negligible, and voltage noise generally dominates. The OPA141, OPA2141, and OPA4141 family has both low voltage noise and extremely low current noise because of the FET input of the op amp. As a result, the current noise contribution of the OPAx141 series is negligible for any practical source impedance, which makes it the better choice for applications with high source impedance.

The equation in Figure 32 shows the calculation of the total circuit noise, with these parameters:

- e<sub>n</sub> = voltage noise

- I<sub>n</sub> = current noise

- R<sub>S</sub> = source impedance

- $k = Boltzmann's constant = 1.38 \times 10^{-23} J/K$

- T = temperature in degrees Kelvin (K)

For more details on calculating noise, see the section on Basic Noise Calculations.

Figure 32. Noise Performance of the OPA141 and OPA211 in Unity-Gain Buffer Configuration

# TEXAS INSTRUMENTS

#### **BASIC NOISE CALCULATIONS**

Low-noise circuit design requires careful analysis of all noise sources. External noise sources can dominate in many cases; consider the effect of source resistance on overall op amp noise performance. Total noise of the circuit is the root-sum-square combination of all noise components.

The resistive portion of the source impedance produces thermal noise proportional to the square root of the resistance. This function is plotted in Figure 32. The source impedance is usually fixed; consequently, select the op amp and the feedback resistors to minimize the respective contributions to the total noise.

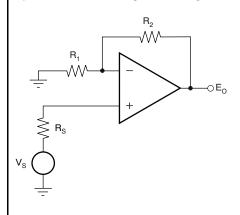

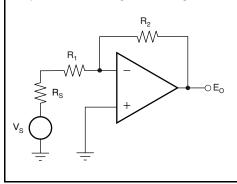

Figure 33 illustrates both noninverting (A) and inverting (B) op amp circuit configurations with gain. In circuit configurations with gain, the feedback network resistors also contribute noise. In general, the current noise of the op amp reacts with the feedback resistors to create additional noise components. However, the extremely low current noise of the OPAx141 means that its current noise contribution can be neglected.

The feedback resistor values can generally be chosen to make these noise sources negligible. Note that low impedance feedback resistors load the output of the amplifier. The equations for total noise are shown for both configurations.

#### A) Noise in Noninverting Gain Configuration

Noise at the output:

$$E_0^2 = \left(1 + \frac{R_2}{R_1}\right)^2 e_n^2 + \left(\frac{R_2}{R_1}\right)^2 e_1^2 + e_2^2 + \left(1 + \frac{R_2}{R_1}\right)^2 e_s^2$$

Where

$$e_S = \sqrt{4kTR_S}$$

= thermal noise of  $R_S$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

B) Noise in Inverting Gain Configuration

Noise at the output:

$${E_0}^2 = \left(1 + \frac{{R_2}}{{R_1} + {R_S}}\right)^2 {e_n}^2 + \left(\frac{{R_2}}{{R_1} + {R_S}}\right)^2 {e_1}^2 + {e_2}^2 + \left(\frac{{R_2}}{{R_1} + {R_S}}\right)^2 {e_s}^2$$

Where

$$e_S = \sqrt{4kTR_S}$$

= thermal noise of  $R_S$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

For the OPAx141 series of operational amplifiers at 1kHz,  $e_n = 6.5 \text{nV}/\sqrt{\text{Hz}}$ .

Figure 33. Noise Calculation in Gain Configurations

#### PHASE-REVERSAL PROTECTION

The OPA141, OPA2141, and OPA4141 family has internal phase-reversal protection. Many FET- and bipolar-input op amps exhibit a phase reversal when the input is driven beyond its linear common-mode range. This condition is most often encountered in noninverting circuits when the input is driven beyond the specified common-mode voltage range, causing the output to reverse into the opposite rail. The input circuitry of the OPA141, OPA2141, and OPA4141 phase reversal prevents with excessive common-mode voltage; instead, the output limits into the appropriate rail (see Figure 22).

#### **OUTPUT CURRENT LIMIT**

The output current of the OPAx141 series is limited by internal circuitry to +36mA/-30mA (sourcing/sinking), to protect the device if the output is accidentally shorted. This short-circuit current depends on temperature, as shown in Figure 29.

# POWER DISSIPATION AND THERMAL PROTECTION

The OPAx141 series of op amps are capable of driving  $2k\Omega$  loads with power-supply voltages of up to  $\pm 18V$  over the specified temperature range. In a single-supply configuration, where the load is connected to the negative supply voltage, the minimum load resistance is  $2.8k\Omega$  at a supply voltage of +36V. For lower supply voltages (either single-supply or symmetrical supplies), a lower load resistance may be used, as long as the output current does not exceed 13mA; otherwise, the device short-circuit current protection circuit may activate.

Internal power dissipation increases when operating at high supply voltages. Copper leadframe construction used in the OPA141, OPA2141, and OPA4141 series devices improves heat dissipation compared to conventional materials. Printed circuit board (PCB) layout can also help reduce a possible increase in junction temperature. Wide copper traces help dissipate the heat by acting as an additional heatsink. Temperature rise can be further minimized by soldering the devices directly to the PCB rather than using a socket.

Although the output current is limited by internal protection circuitry, accidental shorting of one or more output channels of a device can result in excessive heating. For instance, when an output is shorted to mid-supply, the typical short-circuit current of 36mA leads to an internal power dissipation of over 600mW at a supply of ±18V.

In the case of a dual OPA2141 in an MSOP-8 package (thermal resistance  $\theta_{JA}=180^{\circ}\text{C/W}$ ), such power dissipation would lead the die temperature to be 220°C above ambient temperature, when both channels are shorted. This temperature increase significantly decreases the operating life of the device.

In order to prevent excessive heating, the OPAx141 series has an internal thermal shutdown circuit, which shuts down the device if the die temperature exceeds approximately +180°C. Once this thermal shutdown circuit activates, a built-in hysteresis of 15°C ensures that the die temperature must drop to approximately +165°C before the device switches on again.

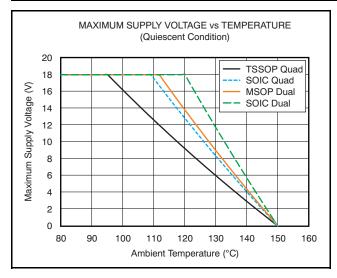

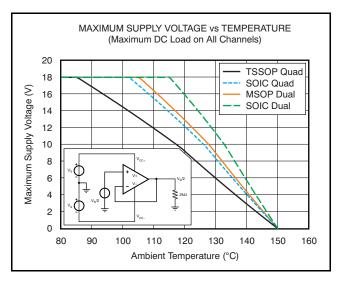

Additional consideration should be given to the combination of maximum operating voltage, maximum operating temperature, load, and package type. Figure 34 and Figure 35 show several practical considerations when evaluating the OPA2141 (dual version) and the OPA4141 (quad version).

As an example, the OPA4141 has a maximum total quiescent current of 12.4mA (3.1mA/channel) over temperature. The TSSOP-14 package has a typical thermal resistance of 135°C/W. This parameter means that because the junction temperature should not exceed 150°C in order to ensure reliable operation, either the supply voltage must be reduced, or the ambient temperature should remain low enough so that the junction temperature does not exceed 150°C. This condition is illustrated in Figure 34 for various package types. Moreover, resistive loading of the output causes additional power dissipation and thus self-heating, which also must be considered when establishing the maximum supply voltage or operating temperature. To this end, Figure 35 shows the maximum supply voltage versus temperature for a worst-case dc load resistance of 2kΩ.

Figure 34. Maximum Supply Voltage vs Temperature (OPA2141 and OPA4141), Quiescent Condition

Figure 35. Maximum Supply Voltage vs Temperature (OPA2141 and OPA4141), Maximum DC Load

#### **ELECTRICAL OVERSTRESS**

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but may involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

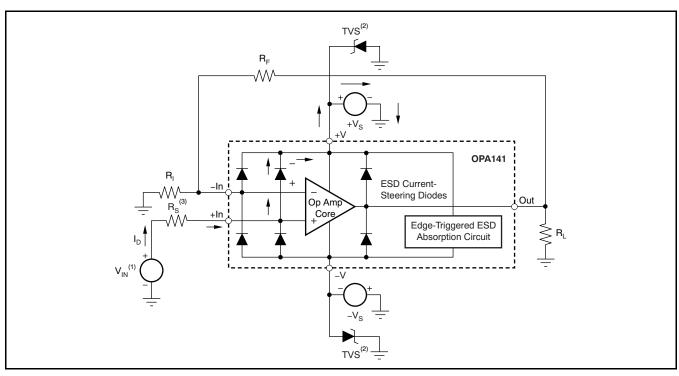

It is helpful to have a good understanding of this basic ESD circuitry and its relevance to an electrical overstress event. See Figure 36 for an illustration of the ESD circuits contained in the OPAx141 series (indicated by the dashed line area). The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where they meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

An ESD event produces a short duration, high-voltage pulse that is transformed into a short duration, high-current pulse as it discharges through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent it from being damaged. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more of the amplifier device pins, current flows through one or more of the steering diodes. Depending on the path that the current takes, the absorption device may activate. The absorption device has a trigger, or threshold voltage, that is above the normal operating voltage of the OPAx141 but below the device breakdown voltage level. Once this threshold is exceeded, the absorption device quickly activates and clamps the voltage across the supply rails to a safe level.

When the operational amplifier connects into a circuit such as the one Figure 36 shows, the ESD protection components are intended to remain inactive and not become involved in the application circuit operation. However, circumstances may arise where an applied voltage exceeds the operating voltage range of a given pin. Should this condition occur, there is a risk that some of the internal ESD protection circuits may be biased on, and conduct current. Any such current flow occurs through steering diode paths and rarely involves the absorption device.

Figure 36 depicts a specific example where the input voltage,  $V_{IN}$ , exceeds the positive supply voltage (+V<sub>S</sub>) by 500mV or more. Much of what happens in the circuit depends on the supply characteristics. If +V<sub>S</sub> can sink the current, one of the upper input steering diodes conducts and directs current to +V<sub>S</sub>. Excessively high current levels can flow with increasingly higher  $V_{IN}$ . As a result, the datasheet specifications recommend that applications limit the input current to 10mA.

If the supply is not capable of sinking the current,  $V_{\text{IN}}$  may begin sourcing current to the operational amplifier, and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings.

Another common question involves what happens to the amplifier if an input signal is applied to the input while the power supplies  $+V_S$  and/or  $-V_S$  are at 0V.

Again, it depends on the supply characteristic while at 0V, or at a level below the input signal amplitude. If the supplies appear as high impedance, then the operational amplifier supply current may be supplied by the input source via the current steering diodes. This state is not a normal bias condition; the amplifier most likely will not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current, and any resistance in the input path.

If there is an uncertainty about the ability of the supply to absorb this current, external zener diodes may be added to the supply pins as shown in Figure 36. The zener voltage must be selected such that the diode does not turn on during normal operation.

However, its zener voltage should be low enough so that the zener diode conducts if the supply pin begins to rise above the safe operating supply voltage level.

- (1)  $V_{IN} = +V_S + 500 \text{mV}.$

- (2) TVS:  $+V_{S(max)} > V_{TVSBR (Min)} > +V_{S}$

- (3) Suggested value approximately  $1k\Omega$ .

Figure 36. Equivalent Internal ESD Circuitry and Its Relation to a Typical Circuit Application

www.ti.com

17-Jun-2025

#### **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material  | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|-----------------|-----------------------|-----------------|--------------------------------|----------------------------|--------------|------------------|

| OPA141AID             | Active     | Production    | SOIC (D)   8    | 75   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O141A            |

| OPA141AID.B           | Active     | Production    | SOIC (D)   8    | 75   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O141A            |

| OPA141AIDGKR          | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | Call TI   Nipdauag<br>  Nipdau | Level-2-260C-1 YEAR        | -40 to 125   | 141              |

| OPA141AIDGKR.B        | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 141              |

| OPA141AIDGKRG4        | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 141              |

| OPA141AIDGKRG4.B      | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 141              |

| OPA141AIDGKT          | Active     | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes             | Call TI   Nipdauag<br>  Nipdau | Level-2-260C-1 YEAR        | -40 to 125   | 141              |

| OPA141AIDGKT.B        | Active     | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 141              |

| OPA141AIDR            | Active     | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O141A            |

| OPA141AIDR.B          | Active     | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O141A            |

| OPA141AIDRG4          | Active     | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O141A            |

| OPA141AIDRG4.B        | Active     | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O141A            |

| OPA2141AID            | Active     | Production    | SOIC (D)   8    | 75   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O2141A           |

| OPA2141AID.B          | Active     | Production    | SOIC (D)   8    | 75   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O2141A           |

| OPA2141AIDGKR         | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | Call TI   Nipdauag<br>  Nipdau | Level-2-260C-1 YEAR        | -40 to 125   | 2141             |

| OPA2141AIDGKR.B       | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 2141             |

| OPA2141AIDGKRG4       | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 2141             |

| OPA2141AIDGKRG4.B     | Active     | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 2141             |

| OPA2141AIDGKT         | Active     | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes             | Call TI   Nipdauag<br>  Nipdau | Level-2-260C-1 YEAR        | -40 to 125   | 2141             |

| OPA2141AIDGKT.B       | Active     | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | 2141             |

| OPA2141AIDR           | Active     | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O2141A           |

| OPA2141AIDR.B         | Active     | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O2141A           |

| OPA4141AID            | Active     | Production    | SOIC (D)   14   | 50   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O4141A           |

| OPA4141AID.B          | Active     | Production    | SOIC (D)   14   | 50   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O4141A           |

| OPA4141AIDG4          | Active     | Production    | SOIC (D)   14   | 50   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O4141A           |

| OPA4141AIDG4.B        | Active     | Production    | SOIC (D)   14   | 50   TUBE             | Yes             | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | O4141A           |

17-Jun-2025

www.ti.com

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| OPA4141AIDR           | Active | Production    | SOIC (D)   14   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIDR.B         | Active | Production    | SOIC (D)   14   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIPW           | Active | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIPW.B         | Active | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIPWG4         | Active | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIPWG4.B       | Active | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIPWR          | Active | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

| OPA4141AIPWR.B        | Active | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | O4141A       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 17-Jun-2025

www.ti.com 24-Jul-2025

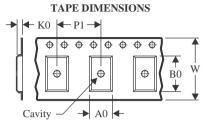

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

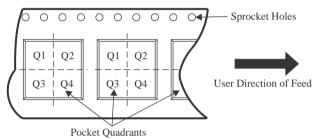

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA141AIDGKR    | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA141AIDGKRG4  | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA141AIDGKT    | VSSOP           | DGK                | 8  | 250  | 180.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA141AIDR      | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| OPA141AIDRG4    | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| OPA2141AIDGKR   | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA2141AIDGKRG4 | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA2141AIDGKT   | VSSOP           | DGK                | 8  | 250  | 180.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA2141AIDR     | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| OPA4141AIDR     | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| OPA4141AIPWR    | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 24-Jul-2025

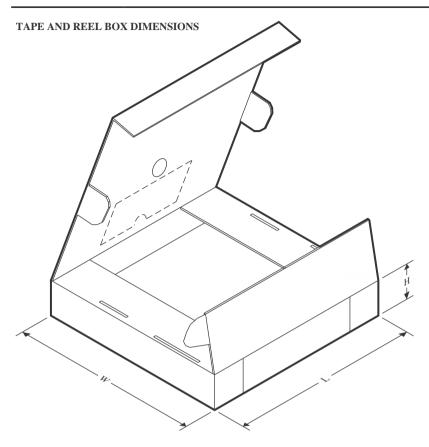

\*All dimensions are nominal

| 7 til dilliciolorio die Hominal |              |                 |      |      |             |             |             |

|---------------------------------|--------------|-----------------|------|------|-------------|-------------|-------------|

| Device                          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm)  | Height (mm) |

| OPA141AIDGKR                    | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0       | 32.0        |

| OPA141AIDGKRG4                  | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0 353.0 |             |

| OPA141AIDGKT                    | VSSOP        | DGK             | 8    | 250  | 213.0 191.0 |             | 35.0        |

| OPA141AIDR                      | SOIC         | D               | 8    | 2500 | 353.0 353.0 |             | 32.0        |

| OPA141AIDRG4                    | SOIC         | D               | 8    | 2500 | 353.0 353.0 |             | 32.0        |

| OPA2141AIDGKR                   | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0       | 32.0        |

| OPA2141AIDGKRG4                 | VSSOP        | DGK             | 8    | 2500 | 353.0 353.0 |             | 32.0        |

| OPA2141AIDGKT                   | VSSOP        | DGK             | 8    | 250  | 213.0       | 191.0       | 35.0        |

| OPA2141AIDR                     | SOIC         | D               | 8    | 2500 | 353.0 353.0 |             | 32.0        |

| OPA4141AIDR                     | SOIC         | D               | 14   | 2500 | 353.0       | 353.0       | 32.0        |

| OPA4141AIPWR                    | TSSOP        | PW              | 14   | 2000 | 353.0       | 353.0       | 32.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

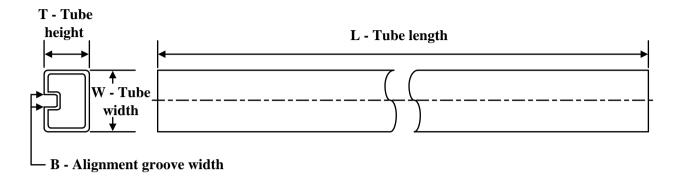

#### **TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| OPA141AID       | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA141AID.B     | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA2141AID      | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA2141AID.B    | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA4141AID      | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| OPA4141AID.B    | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| OPA4141AIDG4    | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| OPA4141AIDG4.B  | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| OPA4141AIPW     | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250   | 2.8    |

| OPA4141AIPW.B   | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250   | 2.8    |

| OPA4141AIPWG4   | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250   | 2.8    |

| OPA4141AIPWG4.B | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250   | 2.8    |

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

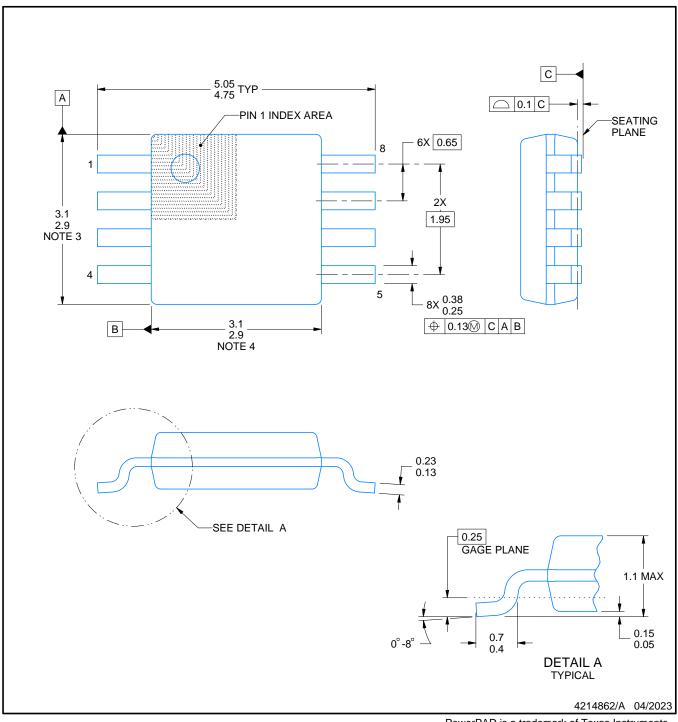

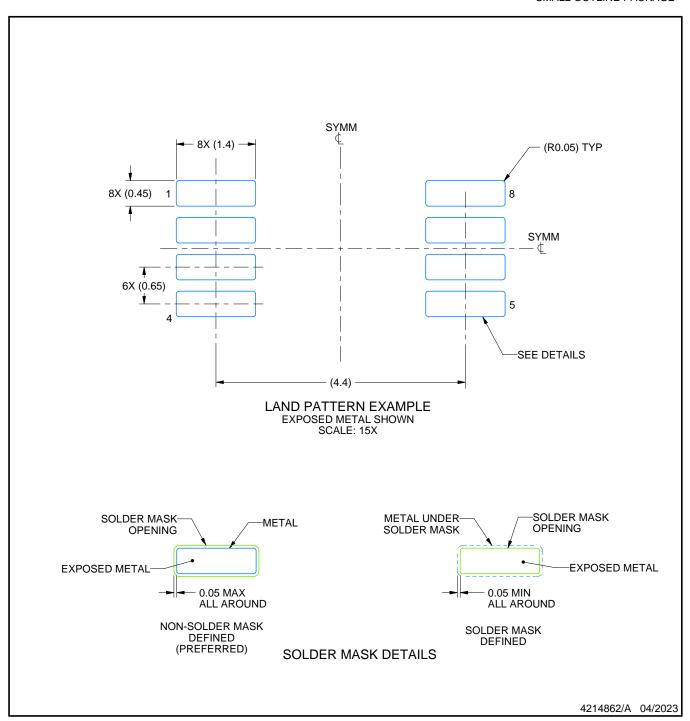

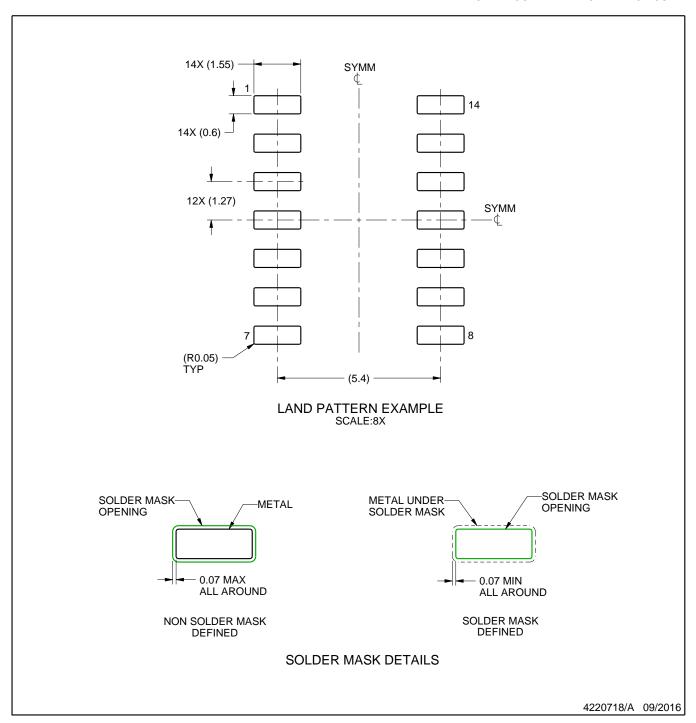

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

NOTES: (continued)

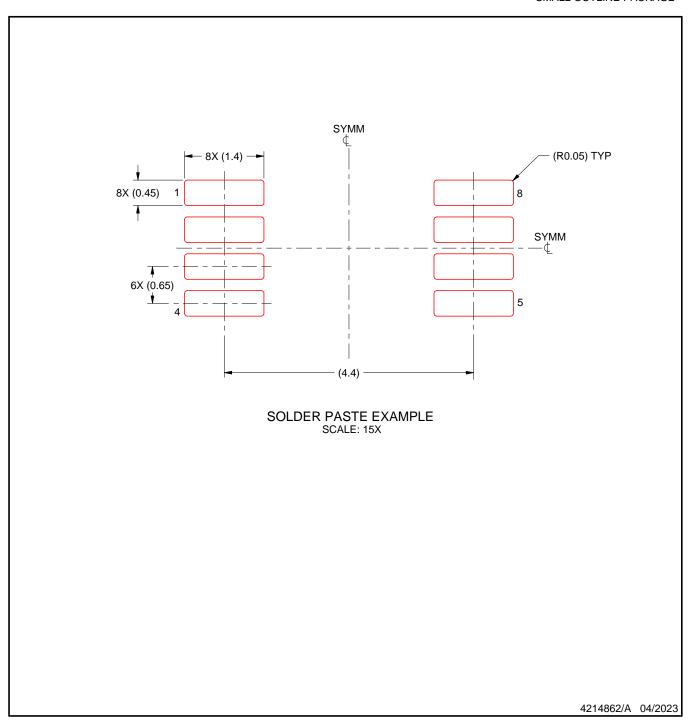

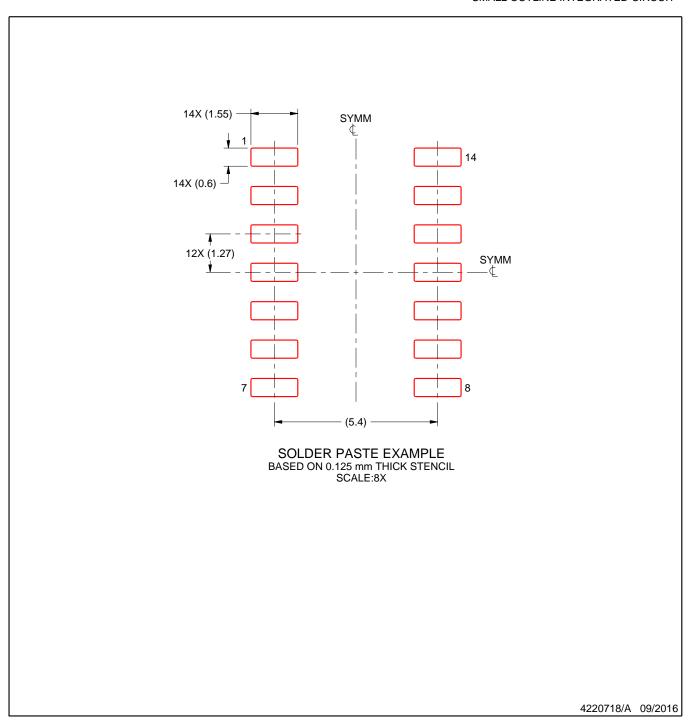

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

#### NOTES:

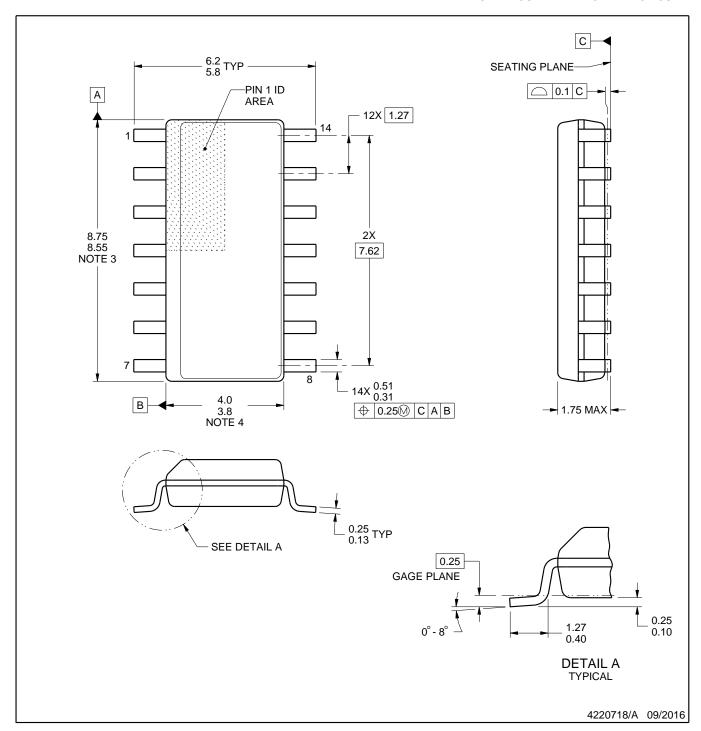

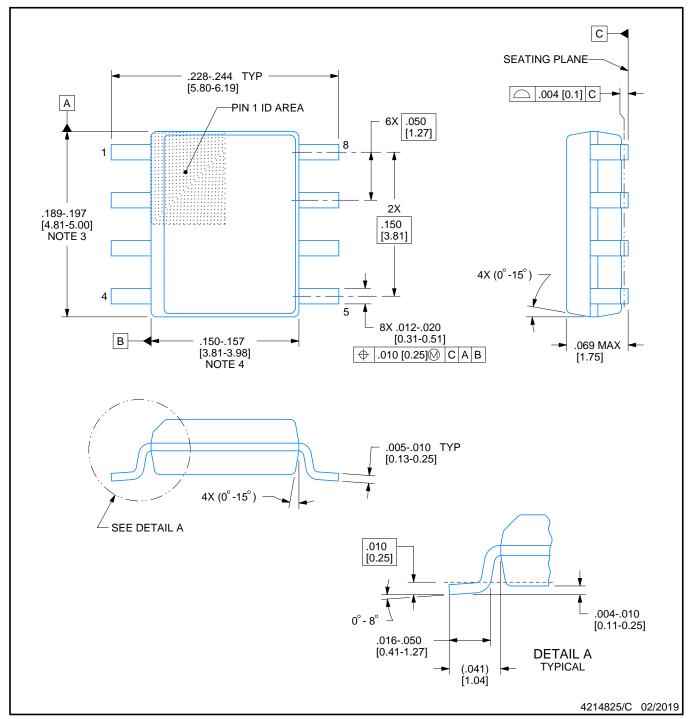

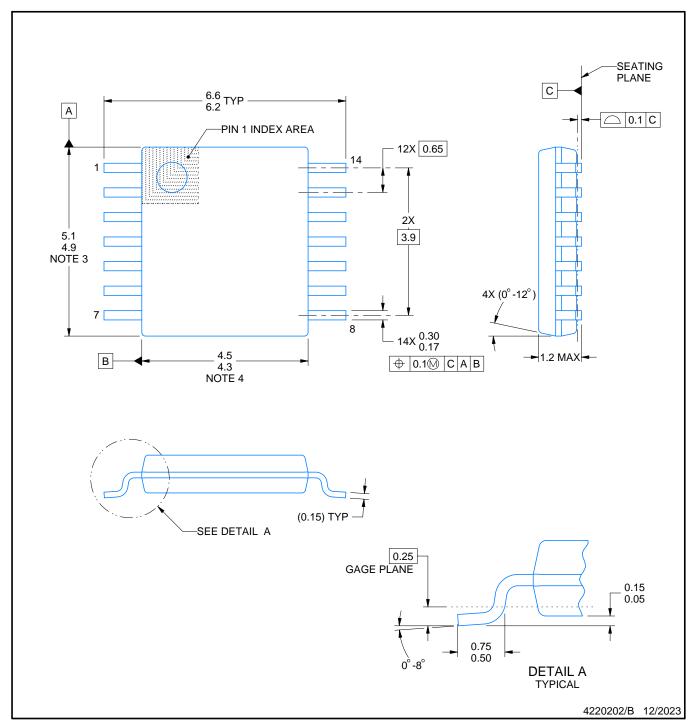

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

NOTES: (continued)

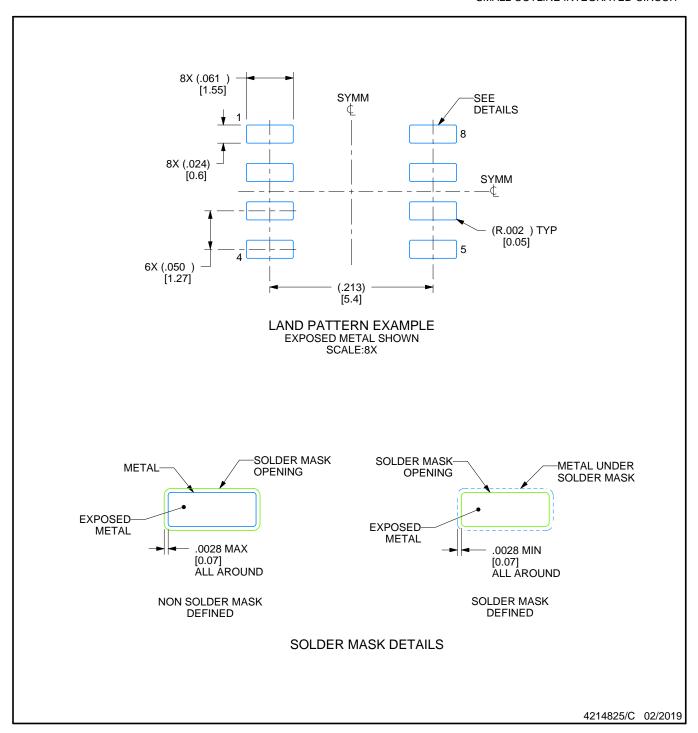

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### NOTES:

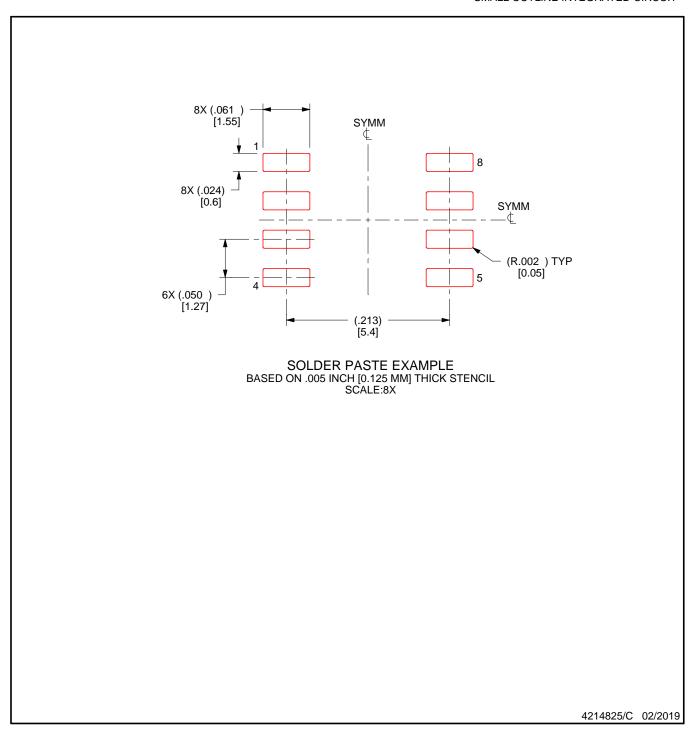

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

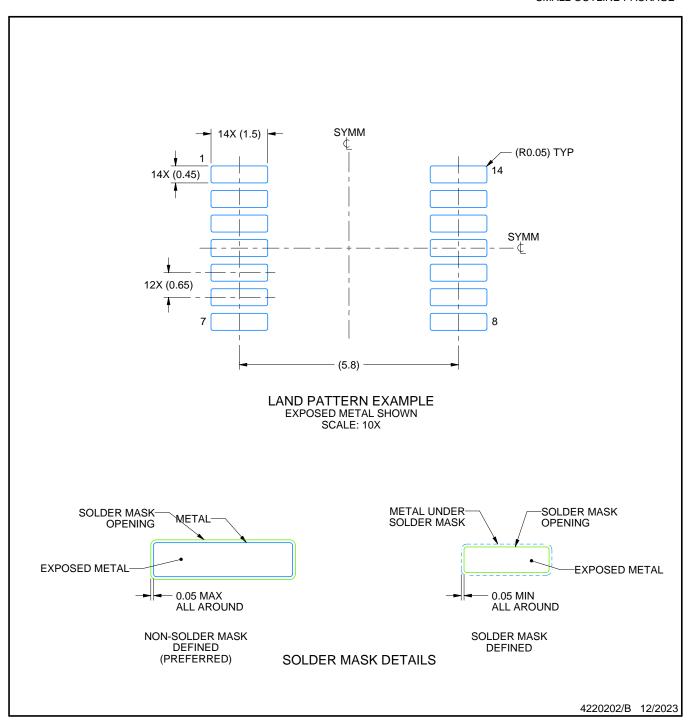

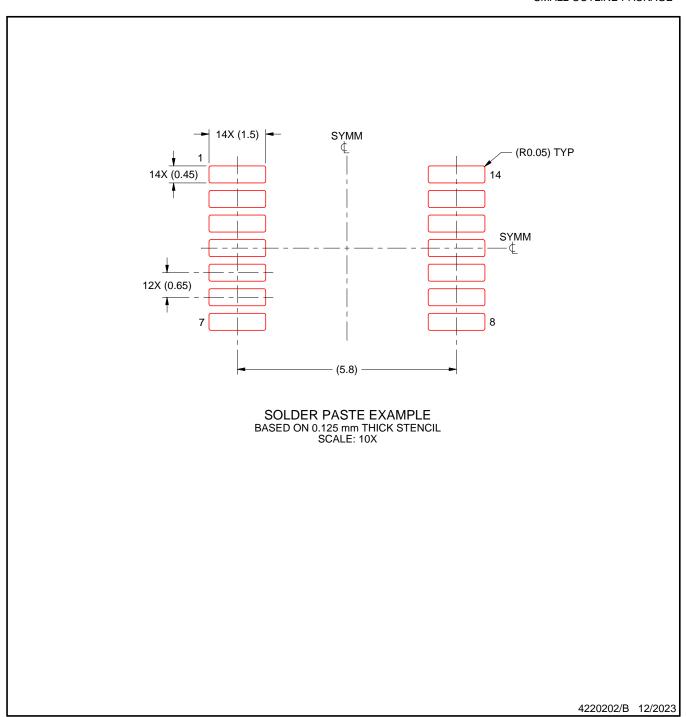

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司