# 混合信号微控制器

#### 特性

- 低电源电压范围: 1.8 V 至 3.6 V

- 超低功耗

- 运行模式: 220 μA (在 1 MHz 频率和 2.2 V 电压条件下)

- 待机模式: 0.5 μA

- 关闭模式 (RAM 保持): 0.1 μA

- 5 种节能模式

- 可在不到 1 µs 的时间里超快速地从待机模式唤醒

- 16 位 RISC 架构、62.5-ns 指令周期时间

- 基本时钟模块配置

- 高达 16 MHz 的内部频率并具有4 种浮动范围在 ±1% 之内的校准频率

- 内部超低功耗低频振荡器

- 具有 2 个捕捉/比较寄存器的 16 位 Timer A

- 用于模拟信号比较功能或者斜率模数 (A/D) 转换的 片载比较器 (只适用于 MSP430G2210)

- 10 位 200-ksps 具有内部基准、取样保持、和自动 扫描的模数 (A/D) 转换器 (只适用于 MSP430G2230)

- 支持 SPI 和 I2C 的通用串行接口 (USI) (仅适用于 MSP430G2230)

- 欠压检测器

- 串行板上编程时,无需外部编程电压,由安全熔丝 (Security Fuse)对可编程代码进行保护

- 具有两线制 (Spy-Bi-Wire) 接口的片上仿真逻辑电路

- 系列成员:

- MSP430G22x0

- 2KB + 256B 闪存

- 128B RAM

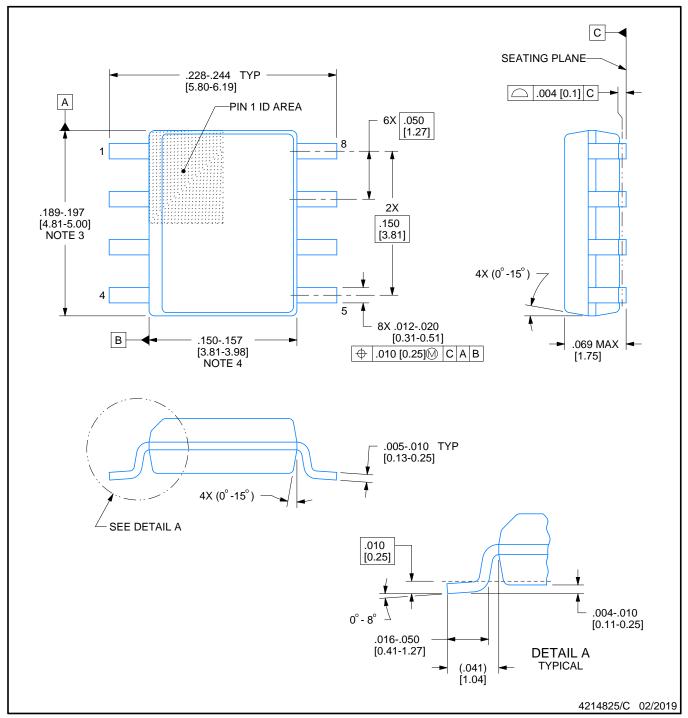

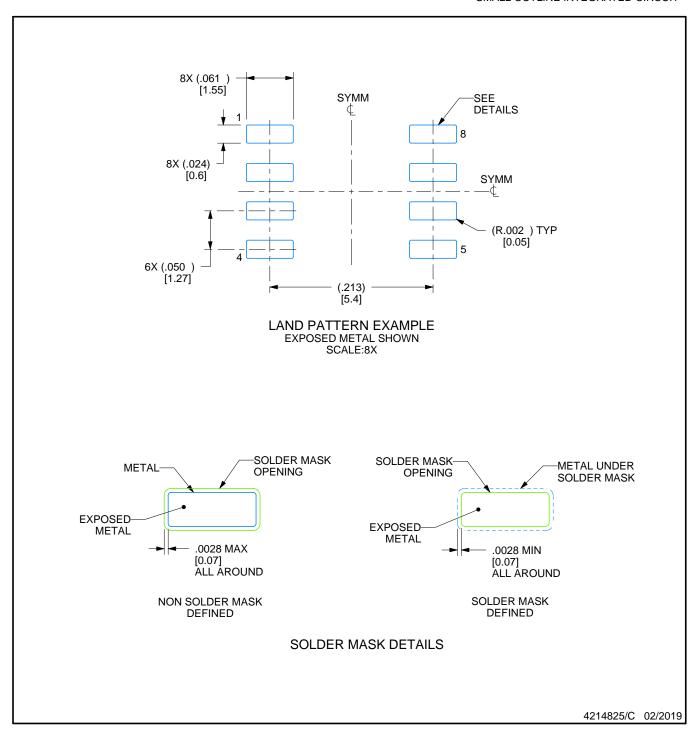

- 采用8引脚塑料封装(D)

- 要获得完整的模块说明, 请参见 MSP430x2xx 系 列产品用户指南 (SLAU144)

#### 说明

德州仪器公司 MSP430™ 系列超低功率微控制器包含几个器件,这些器件特有针对多种应用的不同的外设集。 这种架构与 5 种低功耗模式相组合,专为在便携式测量应用中延长电池使用寿命而优化。 该器件具有一个强大的 16 位 RISC CPU、16 位寄存器和有助于获得最大编码效率的常数发生器。 数字控制振荡器 (DCO) 可在不到 1μs 的时间里完成从低功耗模式至运行模式的唤醒。

MSP430G22x0 系列产品是一款超低功率混合信号微控制器,此微控制器装有一个内置的 16 位定时器和 4 个 I/O 引脚。除此之外, MSP430G2230 还有使用同步协议 (SPI 或者 I2C) 的内置通信功能和一个 10 位 A/D 转换器。 MSP430G2210 装有一个多用途模拟比较器。

表 1. 提供的选项(1)

| <b>T</b>     | 封装的器件 <sup>(2)</sup> |

|--------------|----------------------|

| TA           | 塑料 8 引脚 (D)          |

| -40°C 至 85°C | MSP430G2230ID        |

| -40°C 至 65°C | MSP430G2210ID        |

- (1) 要获得最新的封装和订货信息,请参阅本文档末尾的封装选项附录,或者登录 TI 的网站 www.ti.com.

- (2) 封装图样、热数据和符号可登录 www.ti.com/packaging 获取。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MSP430 is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

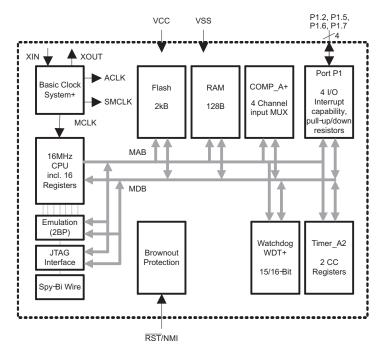

## Device Pinout and Functional Block Diagram, MSP430G2210

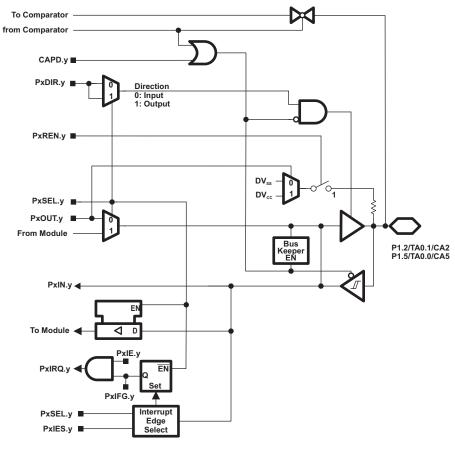

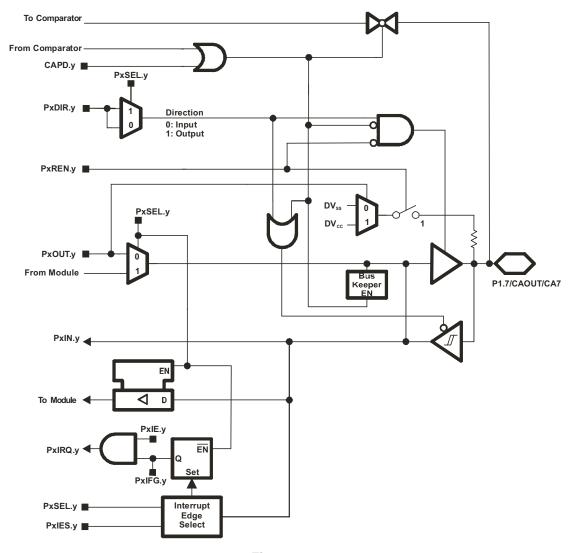

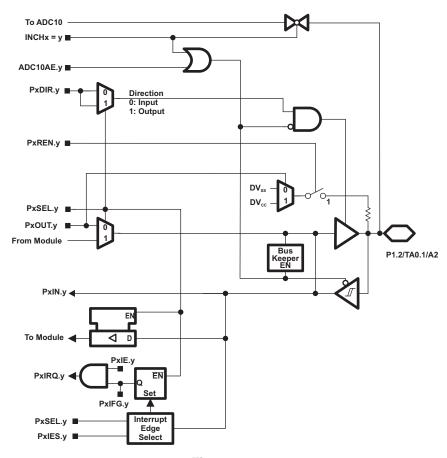

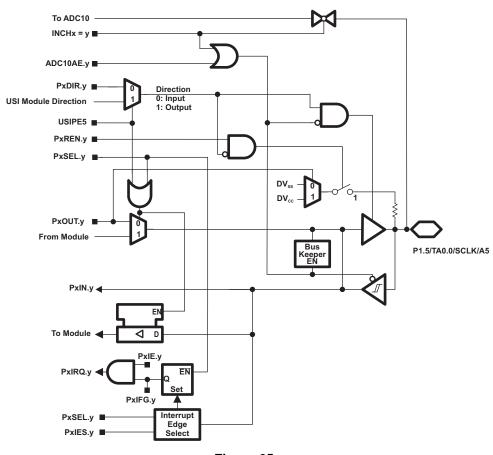

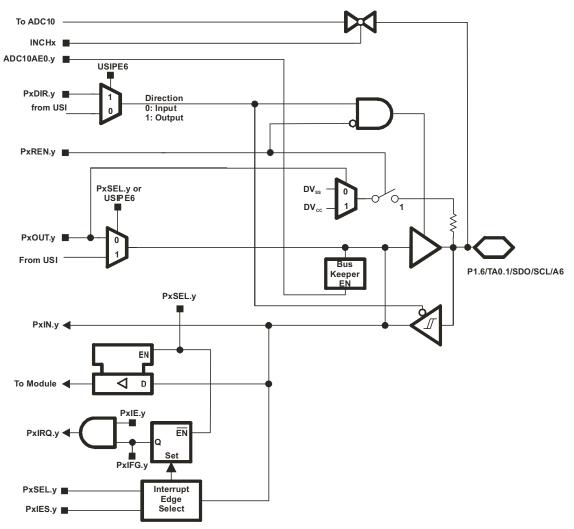

See Application Information for detailed I/O information.

####

Figure 1. Device Pinout, MSP430G2210

Figure 2. Functional Block Diagram, MSP430G2210

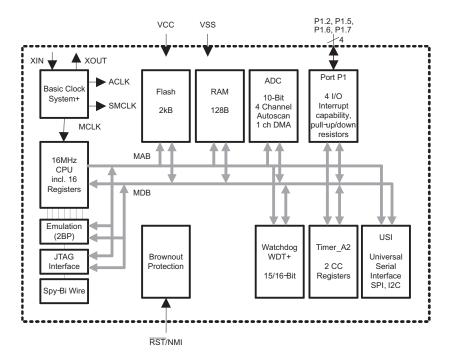

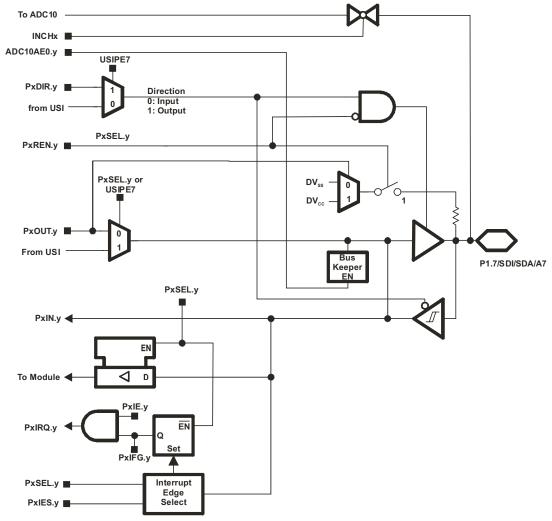

## Device Pinout and Functional Block Diagram, MSP430G2230

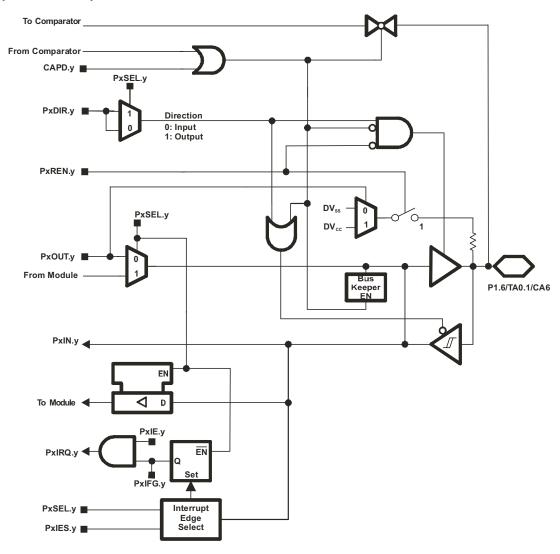

See Application Information for detailed I/O information.

####

Figure 3. Device Pinout, MSP430G2230

Figure 4. Functional Block Diagram, MSP430G2230

## Table 2. Terminal Functions, MSP430G2210<sup>(1)</sup>

| TERMINAL   |   |     |                                                                                             |  |  |  |

|------------|---|-----|---------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.   |   | 1/0 | DESCRIPTION                                                                                 |  |  |  |

|            | D |     |                                                                                             |  |  |  |

| P1.2/      |   |     | General-purpose digital I/O pin                                                             |  |  |  |

| TA0.1/     | 2 | I/O | Timer_A, capture: CCI1A input, compare Out1 output                                          |  |  |  |

| CA2        |   |     | Comparator_A+, CA2 input                                                                    |  |  |  |

| P1.5/      |   |     | General-purpose digital I/O pin                                                             |  |  |  |

| TA0.0/     | 3 | I/O | Timer_A, compare Out0 output                                                                |  |  |  |

| CA5        |   |     | Comparator_A+, CA5 input                                                                    |  |  |  |

| P1.6/      |   |     | General-purpose digital I/O pin                                                             |  |  |  |

| TA0.1/     | 4 | I/O | Timer_A, compare: Out1 output                                                               |  |  |  |

| CA6        |   |     | Comparator_A+, CA6 input                                                                    |  |  |  |

| P1.7/      |   |     | General-purpose digital I/O pin                                                             |  |  |  |

| CAOUT/     | 5 | I/O | Comparator_A+, output                                                                       |  |  |  |

| CA7        |   |     | Comparator_A+, CA7 input                                                                    |  |  |  |

| RST/       |   |     | Reset input                                                                                 |  |  |  |

| NMI/       | 6 | - 1 | Nonmaskable interrupt input                                                                 |  |  |  |

| SBWTDIO    |   |     | Spy-Bi-Wire test data input/output during programming and test                              |  |  |  |

| TEST/      | 7 | 1   | Selects test mode for JTAG pins on Port 1. The device protection fuse is connected to TEST. |  |  |  |

| SBWTCK / I |   | '   | Spy-Bi-Wire test clock input during programming and test                                    |  |  |  |

| DVCC       | 1 |     | Digital supply voltage                                                                      |  |  |  |

| DVSS       | 8 |     | Digital ground reference                                                                    |  |  |  |

<sup>(1)</sup> The GPIOs P1.0, P1.1, P1.3, P1.4, P2.6, and P2.7 are implemented but not available on the device pinout. To avoid floating inputs, these digital I/Os should be properly configured. The pullup or pulldown resistors of the unbounded P1.x GPIOs should be enabled, and the VLO should be selected as the ACLK source (see the MSP430x2xx Family User's Guide (SLAU144)).

## Table 3. Terminal Functions, MSP430G2230<sup>(1)</sup>

| TERMINAL                              |     |     |                                                                                                                                                                   |  |  |  |  |  |

|---------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME                                  | NO. | 1/0 | DESCRIPTION                                                                                                                                                       |  |  |  |  |  |

| NAME                                  | D   | 1/0 |                                                                                                                                                                   |  |  |  |  |  |

| P1.2/<br>TA0.1/<br>A2                 | 2   | I/O | General-purpose digital I/O pin Timer_A, capture: CCI1A input, compare Out1 output ADC10 analog input A2                                                          |  |  |  |  |  |

| P1.5/<br>TA0.0/<br>A5/<br>SCLK        | 3   | I/O | General-purpose digital I/O pin Timer_A, compare Out0 output ADC10 analog input A5 USI: clock input in I2C mode; clock input/output in SPI mode                   |  |  |  |  |  |

| P1.6/<br>TA0.1/<br>A6/<br>SDO/<br>SCL | 4   | I/O | General-purpose digital I/O pin Timer_A, capture: CCI1B input, compare: Out1 output ADC10 analog input A6 USI: Data output in SPI mode USI: I2C clock in I2C mode |  |  |  |  |  |

| P1.7/<br>A7/<br>SDI/<br>SDA           | 5   | I/O | General-purpose digital I/O pin ADC10 analog input A7 USI: Data input in SPI mode USI: Data input in I2C mode                                                     |  |  |  |  |  |

| RST/<br>NMI/<br>SBWTDIO               | 6   | I   | Reset input Nonmaskable interrupt input Spy-Bi-Wire test data input/output during programming and test                                                            |  |  |  |  |  |

| TEST/<br>SBWTCK                       | 7   | I   | Selects test mode for JTAG pins on Port 1. The device protection fuse is connected to TEST.  Spy-Bi-Wire test clock input during programming and test             |  |  |  |  |  |

| DVCC                                  | 1   |     | Digital supply voltage                                                                                                                                            |  |  |  |  |  |

| DVSS                                  | 8   |     | Digital ground reference                                                                                                                                          |  |  |  |  |  |

<sup>(1)</sup> The GPIOs P1.0, P1.1, P1.3, P1.4, P2.6, and P2.7 are implemented but not available on the device pinout. To avoid floating inputs, these digital I/Os should be properly configured. The pullup or pulldown resistors of the unbounded P1.x GPIOs should be enabled, and the VLO should be selected as the ACLK source (see the MSP430x2xx Family User's Guide (SLAU144)).

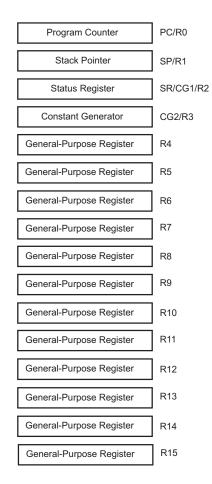

#### SHORT-FORM DESCRIPTION

#### **CPU**

The MSP430 CPU has a 16-bit RISC architecture that is highly transparent to the application. All operations, other than program-flow instructions, are performed as register operations in conjunction with seven addressing modes for source operand and four addressing modes for destination operand.

The CPU is integrated with 16 registers that provide reduced instruction execution time. The register-to-register operation execution time is one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as program counter, stack pointer, status register, and constant generator, respectively. The remaining registers are general-purpose registers.

Peripherals are connected to the CPU using data, address, and control buses, and can be handled with all instructions.

#### **Instruction Set**

The instruction set consists of 51 instructions with three formats and seven address modes. Each instruction can operate on word and byte data. Table 4 shows examples of the three types of instruction formats; Table 5 shows the address modes.

#### **Table 4. Instruction Word Formats**

| INSTRUCTION FORMAT                | EXAMPLE   | OPERATION             |  |

|-----------------------------------|-----------|-----------------------|--|

| Dual operands, source-destination | ADD R4,R5 | R4 + R5> R5           |  |

| Single operands, destination only | CALL R8   | PC>(TOS), R8> PC      |  |

| Relative jump, un/conditional     | JNE       | Jump-on-equal bit = 0 |  |

### **Table 5. Address Mode Descriptions**

| ADDRESS MODE           | S <sup>(1)</sup> | D <sup>(1)</sup> | SYNTAX          | EXAMPLE          | OPERATION                   |

|------------------------|------------------|------------------|-----------------|------------------|-----------------------------|

| Register               | <b>√</b>         | ✓                | MOV Rs,Rd       | MOV R10,R11      | R10> R11                    |

| Indexed                | ✓                | ✓                | MOV X(Rn),Y(Rm) | MOV 2(R5),6(R6)  | M(2+R5)> M(6+R6)            |

| Symbolic (PC relative) | ✓                | ✓                | MOV EDE,TONI    |                  | M(EDE)> M(TONI)             |

| Absolute               | <b>✓</b>         | ✓                | MOV &MEM,&TCDAT |                  | M(MEM)> M(TCDAT)            |

| Indirect               | <b>✓</b>         |                  | MOV @Rn,Y(Rm)   | MOV @R10,Tab(R6) | M(R10)> M(Tab+R6)           |

| Indirect autoincrement | <b>√</b>         |                  | MOV @Rn+,Rm     | MOV @R10+,R11    | M(R10)> R11<br>R10 + 2> R10 |

| Immediate              | ✓                |                  | MOV #X,TONI     | MOV #45,TONI     | #45> M(TONI)                |

(1) S = source, D = destination

### **Operating Modes**

The MSP430 has one active mode and five software-selectable low-power modes of operation. An interrupt event can wake the device from any of the five low-power modes, service the request, and restore back to the low-power mode on return from the interrupt program.

The following six operating modes can be configured by software:

- Active mode (AM)

- All clocks are active

- Low-power mode 0 (LPM0)

- CPU is disabled

- ACLK and SMCLK remain active

- MCLK is disabled

- Low-power mode 1 (LPM1)

- CPU is disabled

- ACLK and SMCLK remain active. MCLK is disabled

- DCO's dc-generator is disabled if DCO not used in active mode

- Low-power mode 2 (LPM2)

- CPU is disabled

- MCLK and SMCLK are disabled

- DCO's dc-generator remains enabled

- ACLK remains active

- Low-power mode 3 (LPM3)

- CPU is disabled

- MCLK and SMCLK are disabled

- DCO's dc-generator is disabled

- ACLK remains active

- Low-power mode 4 (LPM4)

- CPU is disabled

- ACLK is disabled

- MCLK and SMCLK are disabled

- DCO's dc-generator is disabled

- Crystal oscillator is stopped

### **Interrupt Vector Addresses**

The interrupt vectors and the power-up starting address are located in the address range of 0x0FFFF to 0x0FFC0. The vector contains the 16-bit address of the appropriate interrupt handler instruction sequence.

If the reset vector (located at address 0x0FFFE) contains 0x0FFFF (for example, flash is not programmed) the CPU goes into LPM4 immediately after power-up.

**Table 6. Interrupt Sources**

| INTERRUPT SOURCE                                                                           | INTERRUPT FLAG                                              | SYSTEM<br>INTERRUPT                                  | WORD ADDRESS     | PRIORITY        |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|------------------|-----------------|

| Power-up External reset Watchdog Timer+ Flash key violation PC out-of-range <sup>(1)</sup> | PORIFG<br>RSTIFG<br>WDTIFG<br>KEYV <sup>(2)</sup>           | Reset                                                | 0xFFFE           | 31, highest     |

| NMI<br>Oscillator fault<br>Flash memory access violation                                   | NMIIFG<br>OFIFG<br>ACCVIFG <sup>(2)(3)</sup>                | (non)-maskable,<br>(non)-maskable,<br>(non)-maskable | 0xFFFC           | 30              |

|                                                                                            |                                                             |                                                      | 0xFFFA           | 29              |

|                                                                                            |                                                             |                                                      | 0xFFF8           | 28              |

| Comparator_A+<br>(MSP430G2210 Only)                                                        | CAIFG (4)                                                   |                                                      | 0xFFF6           | 27              |

| Watchdog Timer+                                                                            | WDTIFG                                                      | maskable                                             | 0xFFF4           | 26              |

| Timer_A2                                                                                   | TACCR0 CCIFG <sup>(4)</sup>                                 | maskable                                             | 0xFFF2           | 25              |

| Timer_A2                                                                                   | TACCR1 CCIFG, TAIFG <sup>(2)(4)</sup>                       | maskable                                             | 0xFFF0           | 24              |

|                                                                                            |                                                             |                                                      | 0xFFEE           | 23              |

|                                                                                            |                                                             |                                                      | 0xFFEC           | 22              |

| ADC10 (MSP430G2230 Only)                                                                   | ADC10IFG <sup>(4)</sup>                                     | maskable                                             | 0xFFEA           | 21              |

| USI (MSP430G2230 Only)                                                                     | USIIFG, USISTTIFG(2)(4)                                     | maskable                                             | 0xFFE8           | 20              |

|                                                                                            |                                                             |                                                      | 0xFFE6           | 19              |

| I/O Port P1(four flags)                                                                    | P1IFG.2, P1IFG.5, P1IFG.6, and P1IFG.7 <sup>(2)(4)(5)</sup> | maskable                                             | 0xFFE4           | 18              |

|                                                                                            |                                                             |                                                      | 0xFFE2           | 17              |

|                                                                                            |                                                             |                                                      | 0xFFE0           | 16              |

| See (6)                                                                                    |                                                             |                                                      | 0xFFDE to 0xFFC0 | 15 to 0, lowest |

<sup>(1)</sup> A reset is generated if the CPU tries to fetch instructions from within the module register memory address range (0h to 01FFh) or from within unused address ranges.

<sup>(2)</sup> Multiple source flags

<sup>(3) (</sup>non)-maskable: the individual interrupt-enable bit can disable an interrupt event, but the general interrupt enable cannot.

<sup>(4)</sup> Interrupt flags are located in the module.

<sup>(5)</sup> All eight interrupt flags P1IFG.0 to P1IFG.7 are implemented while four are connected to pins.

<sup>(6)</sup> The interrupt vectors at addresses 0xFFDE to 0xFFC0 are not used in this device and can be used for regular program code if necessary.

### **Special Function Registers**

Most interrupt and module enable bits are collected into the lowest address space. Special function register bits not allocated to a functional purpose are not physically present in the device. Simple software access is provided with this arrangement.

**Legend** rw: Bit can be read and written.

rw-0,1: Bit can be read and written. It is reset or set by PUC. rw-(0,1): Bit can be read and written. It is reset or set by POR.

SFR bit is not present in device.

### Table 7. Interrupt Enable Register 1 and 2

| Address | 7                                                                                                                                      | 6                 | 5        | 4     | 3 | 2 | 1    | 0     |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|-------|---|---|------|-------|--|

| 00h     |                                                                                                                                        |                   | ACCVIE   | NMIIE |   |   | OFIE | WDTIE |  |

|         |                                                                                                                                        |                   | rw-0     | rw-0  |   |   | rw-0 | rw-0  |  |

| WDTIE   | Watchdog Timer interrupt enable. Inactive if watchdog mode is selected. Active if Watchdog Timer is configured in interval timer mode. |                   |          |       |   |   |      |       |  |

| OFIE    | Oscillator fault interrupt enable. Set to 0.                                                                                           |                   |          |       |   |   |      |       |  |

| NMIIE   | (Non)maskable interrupt enable                                                                                                         |                   |          |       |   |   |      |       |  |

| ACCVIE  | Flash access v                                                                                                                         | iolation interrup | t enable |       |   |   |      |       |  |

| Address | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

| 01h     |   |   |   |   |   |   |   |   |

### Table 8. Interrupt Flag Register 1 and 2

| Address | 7 | 6 | 5 | 4      | 3      | 2      | 1     | 0      |

|---------|---|---|---|--------|--------|--------|-------|--------|

| 02h     |   |   |   | NMIIFG | RSTIFG | PORIFG | OFIFG | WDTIFG |

|         |   |   |   | rw-∩   | rw-(0) | rw-(1) | rw-1  | rw-(0) |

**WDTIFG** Set on watchdog timer overflow (in watchdog mode) or security key violation.

Reset on V<sub>CC</sub> power-on or a reset condition at the RST/NMI pin in reset mode.

**OFIFG** Flag set on oscillator fault. The XIN/XOUT pins are not available as device terminals.

**PORIFG** Power-On Reset interrupt flag. Set on V<sub>CC</sub> power-up.

**RSTIFG** External reset interrupt flag. Set on a reset condition at RST/NMI pin in reset mode. Reset on V<sub>CC</sub> power-up.

NMIIFG Set by RST/NMI pin

| Address | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |

|---------|---|---|---|---|---|---|---|---|---|

| 03h     |   |   |   |   |   |   |   |   | Ī |

### **Memory Organization**

**Table 9. Memory Organization**

|                                                       |                              | MSP430G22x0                                           |

|-------------------------------------------------------|------------------------------|-------------------------------------------------------|

| Memory<br>Main: interrupt vector<br>Main: code memory | Size<br>Flash<br>Flash       | 2KB Flash<br>0xFFFF-0xFFC0<br>0xFFFF-0xF800           |

| Information memory                                    | Size<br>Flash                | 256 Byte<br>0x10FF - 0x1000                           |

| RAM                                                   | Size                         | 128 Byte<br>0x027F - 0x0200                           |

| Peripherals                                           | 16-bit<br>8-bit<br>8-bit SFR | 0x01FF - 0x0100<br>0x00FF - 0x0010<br>0x000F - 0x0000 |

### **Flash Memory**

The flash memory can be programmed by the Spy-Bi-Wire or JTAG port, or in-system by the CPU. The CPU can perform single-byte and single-word writes to the flash memory. Features of the flash memory include:

- Flash memory has n segments of main memory and four segments of information memory (A to D) of 64 bytes each. Each segment in main memory is 512 bytes in size.

- Segments 0 to n may be erased in one step, or each segment may be individually erased.

- Segments A to D can be erased individually, or as a group with segments 0 to n. Segments A to D are also called *information memory*.

- Segment A contains calibration data. After reset segment A is protected against programming and erasing. It

can be unlocked but care should be taken not to erase this segment if the device-specific calibration data is

required.

www.ti.com.cn

#### **Peripherals**

Peripherals are connected to the CPU through data, address, and control buses and can be handled using all instructions. For complete module descriptions, see the MSP430x2xx Family User's Guide (SLAU144).

#### **Oscillator and System Clock**

The clock system is supported by the basic clock module that includes support for a 32768-Hz watch crystal oscillator, an internal very-low-power low-frequency oscillator and an internal digitally-controlled oscillator (DCO). The basic clock module is designed to meet the requirements of both low system cost and low power consumption. The internal DCO provides a fast turn-on clock source and stabilizes in less than 1 µs. The basic clock module provides the following clock signals:

- Auxiliary clock (ACLK), sourced either from a 32768-Hz watch crystal or the internal LF (VLOCLK) oscillator.

- · Main clock (MCLK), the system clock used by the CPU.

- Sub-Main clock (SMCLK), the sub-system clock used by the peripheral modules.

#### NOTE

The LFXT1 oscillator is not available. LFXT1Sx bits of the BCSCTL3 register should be configured to use VLOCLK (see the MSP430x2xx Family User's Guide (SLAU144)).

Table 10. DCO Calibration Data (Provided From Factory in Flash Information Memory Segment A)

| =                |                         | -    | •       |

|------------------|-------------------------|------|---------|

| DCO<br>FREQUENCY | CALIBRATION<br>REGISTER | SIZE | ADDRESS |

| 1 MHz            | CALBC1_1MHZ             | byte | 010FFh  |

| I IVITZ          | CALDCO_1MHZ             | byte | 010FEh  |

| 0.141.1-         | CALBC1_8MHZ             | byte | 010FDh  |

| 8 MHz            | CALDCO_8MHZ             | byte | 010FCh  |

| 12 MHz           | CALBC1_12MHZ            | byte | 010FBh  |

| 12 IVIDZ         | CALDCO_12MHZ            | byte | 010FAh  |

| 16 MU-           | CALBC1_16MHZ            | byte | 010F9h  |

| 16 MHz           | CALDCO_16MHZ            | byte | 010F8h  |

#### **Brownout**

The brownout circuit is implemented to provide the proper internal reset signal to the device during power on and power off.

#### Digital I/O

There are four pins of one 8-bit I/O port implemented—port P1:

- All individual I/O bits are independently programmable.

- Any combination of input, output, and interrupt condition is possible.

- Edge-selectable interrupt input capability for all the four bits of port P1.

- Read/write access to port-control registers is supported by all instructions.

- Each I/O has an individually programmable pullup/pulldown resistor.

#### Watchdog Timer (WDT+)

The primary function of the watchdog timer (WDT+) module is to perform a controlled system restart after a software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be disabled or configured as an interval timer and can generate interrupts at selected time intervals.

#### Timer\_A2

Timer\_A2 is a 16-bit timer/counter with two capture/compare registers. Timer\_A2 can support multiple capture/compares, PWM outputs, and interval timing. Timer\_A2 also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.

Table 11. Timer\_A2 Signal Connections - MSP430G2210

| INPUT PIN<br>NUMBER | DEVICE INPUT     | MODULE<br>INPUT NAME | MODULE<br>BLOCK | MODULE<br>OUTPUT | OUTPUT PIN<br>NUMBER |

|---------------------|------------------|----------------------|-----------------|------------------|----------------------|

| D                   | SIGNAL           | INPUT NAME           | BLUCK           | SIGNAL           | D                    |

| -                   | TACLK            | TACLK                | Timer           | NA               |                      |

|                     | ACLK             | ACLK                 |                 |                  |                      |

|                     | SMCLK            | SMCLK                |                 |                  |                      |

| -                   | TACLK            | INCLK                |                 |                  |                      |

| -                   | TA0              | CCI0A                | CCR0            | TA0              | 3 - P1.5             |

|                     | ACLK (internal)  | CCI0B                |                 |                  |                      |

|                     | $V_{SS}$         | GND                  |                 |                  |                      |

|                     | V <sub>cc</sub>  | V <sub>CC</sub>      |                 |                  |                      |

| 2 - P1.2            | TA1              | CCI1A                | CCR1            | TA1              | 2 - P1.2             |

|                     | CAOUT (internal) | CCI1B                |                 |                  | 4 - P1.6             |

|                     | V <sub>SS</sub>  | GND                  |                 |                  |                      |

|                     | V <sub>CC</sub>  | $V_{CC}$             | ·               |                  |                      |

Table 12. Timer A2 Signal Connections - MSP430G2230

| INPUT PIN<br>NUMBER | DEVICE INPUT<br>SIGNAL | MODULE<br>INPUT NAME | MODULE<br>BLOCK | MODULE<br>OUTPUT | OUTPUT PIN<br>NUMBER |

|---------------------|------------------------|----------------------|-----------------|------------------|----------------------|

| D                   | SIGNAL                 | INFOI NAME           | BLOCK           | SIGNAL           | D                    |

| -                   | TACLK                  | TACLK                | Timer           | NA               |                      |

|                     | ACLK                   | ACLK                 |                 |                  |                      |

|                     | SMCLK                  | SMCLK                |                 |                  |                      |

| -                   | TACLK                  | INCLK                |                 |                  |                      |

| -                   | TA0                    | CCI0A                | CCR0            | TA0              |                      |

|                     | ACLK (internal)        | CCI0B                |                 |                  |                      |

|                     | V <sub>SS</sub>        | GND                  |                 |                  |                      |

|                     | V <sub>CC</sub>        | V <sub>CC</sub>      |                 |                  |                      |

| 2 - P1.2            | TA1                    | CCI1A                | CCR1            | TA1              | 2 - P1.2             |

| 4 - P1.6            | TA1                    | CCI1B                |                 |                  | 4 - P1.6             |

|                     | V <sub>SS</sub>        | GND                  |                 |                  |                      |

|                     | V <sub>CC</sub>        | V <sub>CC</sub>      |                 |                  |                      |

#### USI (MSP430G2230 Only)

The universal serial interface (USI) module is used for serial data communication and provides the basic hardware for synchronous communication protocols like SPI and I2C.

#### ADC10 (MSP430G2230 Only)

The ADC10 module supports fast 10-bit analog-to-digital conversions. The module implements a 10-bit SAR core, sample select control, reference generator, and data transfer controller (DTC) for automatic conversion result handling, allowing ADC samples to be converted and stored without any CPU intervention.

### Comparator\_A+ (MSP430G2210 Only)

The primary function of the comparator\_A+ module is to support precision slope analog-to-digital conversions, battery-voltage supervision, and monitoring of external analog signals

### **Peripheral File Map**

**Table 13. Peripherals With Word Access**

| ADC10<br>(MSP430G2230 Only) | ADC control 0<br>ADC10 control 1<br>ADC memory                                                                                                              | ADC10CTL0<br>ADC10CTL1<br>ADC10MEM            | 01B0h<br>01B2h<br>01B4h                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|

| Timer_A                     | Capture/compare register Capture/compare register Timer_A register Capture/compare control Capture/compare control Timer_A control Timer_A interrupt vector | TACCR1 TACCR0 TAR TACCTL1 TACCTL0 TACTL TACTL | 0174h<br>0172h<br>0170h<br>0164h<br>0162h<br>0160h<br>012Eh |

| Flash Memory                | Flash control 3<br>Flash control 2<br>Flash control 1                                                                                                       | FCTL3<br>FCTL2<br>FCTL1                       | 012Ch<br>012Ah<br>0128h                                     |

| Watchdog Timer+             | Watchdog/timer control                                                                                                                                      | WDTCTL                                        | 0120h                                                       |

#### **Table 14. Peripherals With Byte Access**

|                                     | •                                                                                                                                                                      | •                                                 |                                                              |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------|

| ADC10<br>(MSP430G2230 Only)         | Analog Enable                                                                                                                                                          | ADC10AE                                           | 04Ah                                                         |

| USI<br>(MSP430G2230 Only)           | USI control 0 USI control 1 USI clock control USI bit counter USI shift register                                                                                       | USICTL0<br>USICTL1<br>USICKCTL<br>USICNT<br>USISR | 078h<br>079h<br>07Ah<br>07Bh<br>07Ch                         |

| Comparator_A+<br>(MSP430G2210 Only) | Comparator_A+ port disable<br>Comparator_A+ control 2<br>Comparator_A+ control 1                                                                                       | CAPD<br>CACTL2<br>CACTL1                          | 05Bh<br>05Ah<br>059h                                         |

| Basic Clock System+                 | Basic clock system control 3 Basic clock system control 2 Basic clock system control 1 DCO clock frequency control                                                     | BCSCTL3<br>BCSCTL2<br>BCSCTL1<br>DCOCTL           | 053h<br>058h<br>057h<br>056h                                 |

| Port P1                             | Port P1 resistor enable Port P1 selection Port P1 interrupt enable Port P1 interrupt edge select Port P1 interrupt flag Port P1 direction Port P1 output Port P1 input | P1REN P1SEL P1IE P1IES P1IFG P1DIR P1OUT P1IN     | 027h<br>026h<br>025h<br>024h<br>023h<br>022h<br>021h<br>020h |

| Special Function                    | SFR interrupt flag 2 SFR interrupt flag 1 SFR interrupt enable 2 SFR interrupt enable 1                                                                                | IFG2<br>IFG1<br>IE2<br>IE1                        | 003h<br>002h<br>001h<br>000h                                 |

### Absolute Maximum Ratings(1)

|       | Voltage applied at V <sub>CC</sub> to V <sub>SS</sub> |                     | -0.3 V to 4.1 V                   |

|-------|-------------------------------------------------------|---------------------|-----------------------------------|

|       | Voltage applied to any pin <sup>(2)</sup>             |                     | -0.3 V to V <sub>CC</sub> + 0.3 V |

|       | Diode current at any device terminal                  |                     | ±2 mA                             |

| _     | C4(3)                                                 | Unprogrammed device | -55°C to 150°C                    |

| I stg | Storage temperature (3)                               | Programmed device   | -40°C to 150°C                    |

- (1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages referenced to V<sub>SS</sub>. The JTAG fuse-blow voltage, V<sub>FB</sub>, is allowed to exceed the absolute maximum rating. The voltage is applied to the TEST pin when blowing the JTAG fuse.

- (3) Higher temperature may be applied during board soldering according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

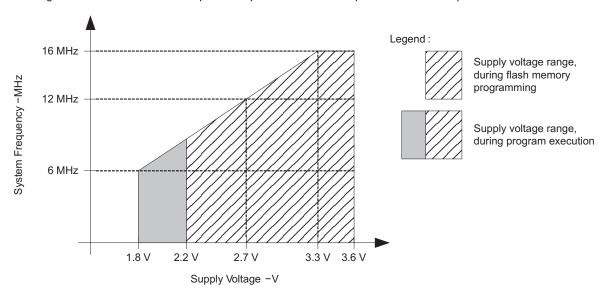

### **Recommended Operating Conditions**

Typical values are specified at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                     |                                                      |                                                       | MIN | NOM | MAX | UNIT |

|---------------------|------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| M                   | Cumply voltage                                       | During program execution                              | 1.8 |     | 3.6 | V    |

| V <sub>CC</sub>     | Supply voltage                                       | During flash program or erase                         | 2.2 |     | 3.6 | V    |

| $V_{SS}$            | Supply voltage                                       |                                                       |     | 0   |     | V    |

| T <sub>A</sub>      | Operating free-air temperature                       |                                                       | -40 |     | 85  | °C   |

|                     |                                                      | $V_{CC} = 1.8 \text{ V},$ Duty cycle = 50% ± 10%      | dc  |     | 6   |      |

| f <sub>SYSTEM</sub> | Processor frequency (maximum MCLK frequency) (1) (2) | $V_{CC} = 2.7 \text{ V},$<br>Duty cycle = 50% ± 10%   | dc  |     | 12  | MHz  |

|                     |                                                      | $V_{CC} \ge 3.3 \text{ V},$<br>Duty cycle = 50% ± 10% | dc  |     | 16  |      |

- (1) The MSP430 CPU is clocked directly with MCLK. Both the high and low phase of MCLK must not exceed the pulse duration of the specified maximum frequency.

- (2) Modules might have a different maximum input clock specification. See the specification of the respective module in this data sheet.

Note: Minimum processor frequency is defined by system clock. Flash program or erase operations require a minimum  $V_{CC}$  of 2.2 V.

Figure 5. Safe Operating Area

#### **Electrical Characteristics**

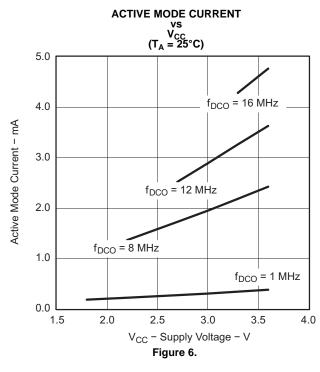

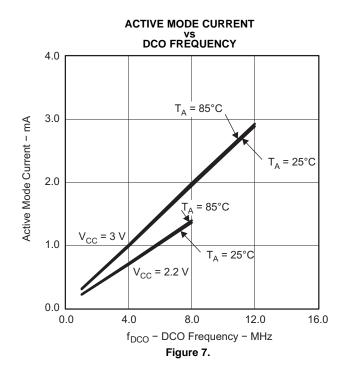

# Active Mode Supply Current Into $V_{\text{CC}}$ Excluding External Current

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)<sup>(1)</sup>

|                      | PARAMETER                           | TEST CONDITIONS                                                                                                                                             | T <sub>A</sub> | V <sub>CC</sub> | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----|-----|-----|------|

|                      |                                     | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 1 \text{ MHz},$                                                                                                           |                | 2.2 V           |     | 220 |     |      |

| I <sub>AM,1MHz</sub> | Active mode (AM)<br>current (1 MHz) | f <sub>ACLK</sub> = 0 Hz,<br>Program executes in flash,<br>BCSCTL1 = CALBC1_1MHZ,<br>DCOCTL = CALDCO_1MHZ,<br>CPUOFF = 0, SCG0 = 0,<br>SCG1 = 0, OSCOFF = 0 |                | 3 V             |     | 300 | 370 | μА   |

(1) All inputs are tied to 0 V or to  $V_{CC}$ . Outputs do not source or sink any current.

# Typical Characteristics – Active Mode Supply Current (Into V<sub>CC</sub>)

# Low-Power Mode Supply Currents (Into V<sub>CC</sub>) Excluding External Current

| F                      | PARAMETER                                         | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                 | T <sub>A</sub> | V <sub>cc</sub> | MIN TYP | MAX | UNIT |

|------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|---------|-----|------|

| I <sub>LPM0,1MHz</sub> | Low-power mode 0<br>(LPM0) current <sup>(2)</sup> | $\begin{array}{l} f_{\text{MCLK}} = 0 \text{ MHz}, \\ f_{\text{SMCLK}} = f_{\text{DCO}} = 1 \text{ MHz}, \\ f_{\text{ACLK}} = 32,768 \text{ Hz}, \\ \text{BCSCTL1} = \text{CALBC1\_1MHZ}, \\ \text{DCOCTL} = \text{CALDCO\_1MHZ}, \\ \text{CPUOFF} = 1, \text{SCG0} = 0, \\ \text{SCG1} = 0, \text{OSCOFF} = 0 \end{array}$     | 25°C           | 2.2 V           | 65      |     | μА   |

| I <sub>LPM2</sub>      | Low-power mode 2<br>(LPM2) current <sup>(3)</sup> | $\begin{split} &f_{\text{MCLK}} = f_{\text{SMCLK}} = 0 \text{ MHz, } f_{\text{DCO}} = 1 \\ &\text{MHz,} \\ &f_{\text{ACLK}} = 32,768 \text{ Hz,} \\ &\text{BCSCTL1} = \text{CALBC1\_1MHZ,} \\ &\text{DCOCTL} = \text{CALDCO\_1MHZ,} \\ &\text{CPUOFF} = 1, \text{SCG0} = 0, \\ &\text{SCG1} = 1, \text{OSCOFF} = 0 \end{split}$ | 25°C           | 2.2 V           | 22      | 29  | μA   |

| I <sub>LPM3,VLO</sub>  | Low-power mode 3 (LPM3) current <sup>(3)</sup>    | $\begin{split} f_{DCO} &= f_{MCLK} = f_{SMCLK} = 0 \text{ MHz}, \\ f_{ACLK} \text{ from internal LF oscillator} \\ \text{(VLO)}, \\ \text{CPUOFF} &= 1, \text{SCG0} = 1, \\ \text{SCG1} &= 1, \text{OSCOFF} = 0 \end{split}$                                                                                                    | 25°C           | 2.2 V           | 0.5     | 0.7 | μА   |

|                        |                                                   | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 0 \text{ MHz},$                                                                                                                                                                                                                                                                               | 25°C           |                 | 0.1     | 0.5 |      |

| I <sub>LPM4</sub>      | Low-power mode 4<br>(LPM4) current <sup>(4)</sup> | f <sub>ACLK</sub> = 0 Hz,<br>CPUOFF = 1, SCG0 = 1,<br>SCG1 = 1, OSCOFF = 1                                                                                                                                                                                                                                                      | 85°C           | 2.2 V           | 0.8     | 1.5 | μA   |

All inputs are tied to 0 V or to  $V_{CC}$ . Outputs do not source or sink any current. Current for brownout and WDT clocked by SMCLK included. Current for brownout and WDT clocked by ACLK included.

Current for brownout included.

## **Schmitt-Trigger Inputs (Port P1)**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                   | PARAMETER                                                       | TEST CONDITIONS                                                    | V <sub>CC</sub> | MIN                  | TYP | MAX                  | UNIT     |

|-------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|-----------------|----------------------|-----|----------------------|----------|

| V                 | Positive-going input threshold voltage                          |                                                                    |                 | 0.45 V <sub>CC</sub> |     | 0.75 V <sub>CC</sub> | ٧        |

| $V_{IT+}$         | Positive-going input tilleshold voltage                         |                                                                    | 3 V             | 1.35                 |     | 2.25                 |          |

| V                 | Negative going input threehold valtage                          |                                                                    |                 | 0.25 V <sub>CC</sub> |     | 0.55 V <sub>CC</sub> | <b>V</b> |

| V <sub>IT-</sub>  | Negative-going input threshold voltage                          |                                                                    | 3 V             | 0.75                 |     | 1.65                 | V        |

| V <sub>hys</sub>  | Input voltage hysteresis (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                                                    | 3 V             | 0.3                  |     | 1.0                  | ٧        |

| R <sub>Pull</sub> | Pullup/pulldown resistor                                        | For pullup: $V_{IN} = V_{SS}$ ,<br>For pulldown: $V_{IN} = V_{CC}$ |                 | 20                   | 35  | 50                   | kΩ       |

| C <sub>I</sub>    | Input capacitance                                               | $V_{IN} = V_{SS}$ or $V_{CC}$                                      |                 |                      | 5   |                      | pF       |

## **Leakage Current (Port P1)**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                        | PARAMETER                      | TEST CONDITIONS | V <sub>CC</sub> | MIN MAX | UNIT |

|------------------------|--------------------------------|-----------------|-----------------|---------|------|

| I <sub>lkg(Px.y)</sub> | High-impedance leakage current | (1) (2)         | /3 V            | ±50     | nA   |

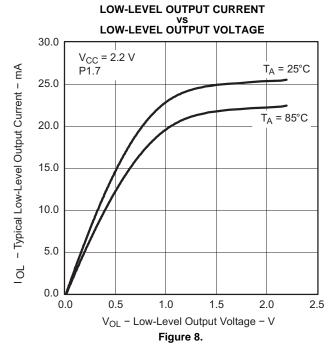

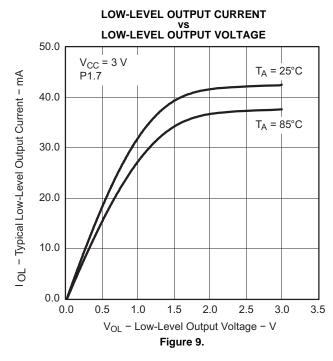

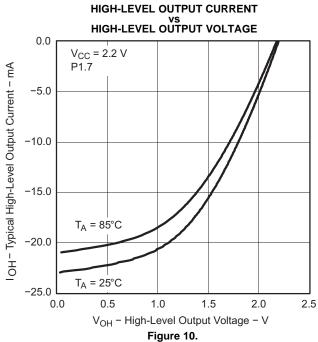

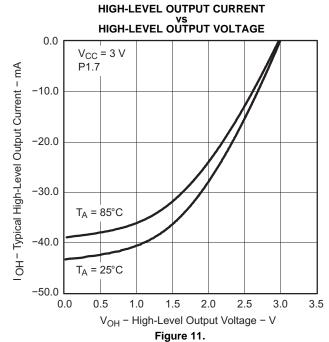

### **Outputs (Port P1)**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|          | PARAMETER                 | TEST CONDITIONS                     | V <sub>CC</sub> | MIN                   | TYP MAX               | UNIT |

|----------|---------------------------|-------------------------------------|-----------------|-----------------------|-----------------------|------|

| $V_{OH}$ | High-level output voltage | $I_{(OHmax)} = -6 \text{ mA}^{(1)}$ | 3 V             | V <sub>CC</sub> - 0.6 | $V_{CC}$              | V    |

| $V_{OL}$ | Low-level output voltage  | $I_{(OLmax)} = 6 \text{ mA}^{(1)}$  | 3 V             | V <sub>SS</sub>       | V <sub>SS</sub> + 0.6 | V    |

<sup>(1)</sup> The maximum total current, I<sub>(OHmax)</sub>, and I<sub>(OLmax)</sub>, for all outputs combined should not exceed ±48 mA to hold the maximum voltage drop specified.

### **Output Frequency (Port P1)**

|                       | PARAMETER                         | TEST CONDITIONS                                          | V <sub>CC</sub> | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------|----------------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>Px.y</sub>     | Port output frequency (with load) | $C_L = 20 \text{ pF}, R_L = 1 \text{ k}\Omega^{(1)}$ (2) | 3 V             |     |     | 12  | MHz  |

| f <sub>Port°CLK</sub> | Clock output frequency            | $C_L = 20 \text{ pF}^{(2)}$                              | 3 V             |     |     | 16  | MHz  |

A resistive divider with two 0.5-kΩ resistors between V<sub>CC</sub> and V<sub>SS</sub> is used as load. The output is connected to the center tap of the

The leakage current is measured with  $V_{SS}$  or  $V_{CC}$  applied to the corresponding pin(s), unless otherwise noted. The leakage of the digital port pins is measured individually. The port pin is selected for input and the pullup/pulldown resistor is disabled.

The output voltage reaches at least 10% and 90% V<sub>CC</sub> at the specified toggle frequency.

## **Typical Characteristics - Outputs**

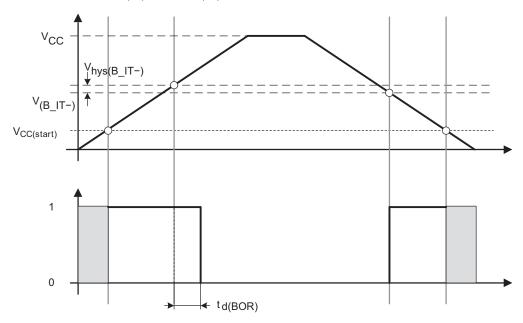

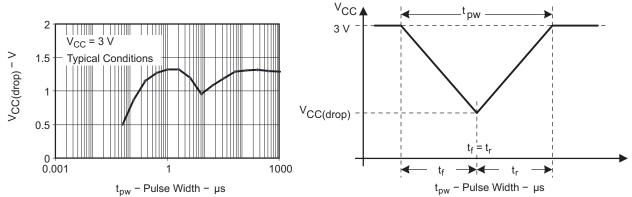

## POR and BOR<sup>(1)(2)</sup>

|                         | PARAMETER                                                       | TEST CONDITIONS              | V <sub>cc</sub> | MIN TYP                              | MAX  | UNIT |

|-------------------------|-----------------------------------------------------------------|------------------------------|-----------------|--------------------------------------|------|------|

| V <sub>CC(start)</sub>  | See Figure 12                                                   | dV <sub>CC</sub> /dt ≤ 3 V/s |                 | 0.7 <b>x</b><br>V <sub>(B_IT-)</sub> |      | ٧    |

| V <sub>(B_IT-)</sub>    | See Figure 12 through Figure 14                                 | dV <sub>CC</sub> /dt ≤ 3 V/s |                 | 1.35                                 | 1    | V    |

| V <sub>hys(B_IT-)</sub> | See Figure 12                                                   | dV <sub>CC</sub> /dt ≤ 3 V/s |                 | 140                                  |      | mV   |

| t <sub>d(BOR)</sub>     | See Figure 12                                                   |                              |                 |                                      | 2000 | μs   |

| t <sub>(reset)</sub>    | Pulse duration needed at RST/NMI pin to accept reset internally |                              | 3 V             | 2                                    |      | μs   |

- The current consumption of the brownout module is already included in the I<sub>CC</sub> current consumption data. The voltage level V<sub>(B\_IT-)</sub> + V<sub>hys(B\_IT-)</sub>is ≤ 1.8 V.

- (2) During power up, the CPU begins code execution following a period of t<sub>d(BOR)</sub> after V<sub>CC</sub> = V<sub>(B\_IT-)</sub> + V<sub>hys(B\_IT-)</sub>. The default DCO settings must not be changed until V<sub>CC</sub> ≥ V<sub>CC(min)</sub>, where V<sub>CC(min)</sub> is the minimum supply voltage for the desired operating frequency.

Figure 12. POR and BOR vs Supply Voltage

# Typical Characteristics - POR and BOR

Figure 13. V<sub>CC(drop)</sub> Level With a Square Voltage Drop to Generate a POR or BOR Signal

Figure 14.  $V_{CC(drop)}$  Level With a Triangle Voltage Drop to Generate a POR or BOR Signal

#### **Main DCO Characteristics**

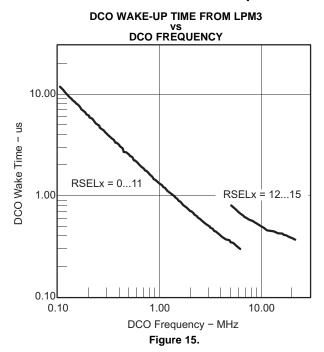

- All ranges selected by RSELx overlap with RSELx + 1: RSELx = 0 overlaps RSELx = 1, ... RSELx = 14 overlaps RSELx = 15.

- DCO control bits DCOx have a step size as defined by parameter S<sub>DCO</sub>.

- Modulation control bits MODx select how often  $f_{DCO(RSEL,DCO+1)}$  is used within the period of 32 DCOCLK cycles. The frequency  $f_{DCO(RSEL,DCO)}$  is used for the remaining cycles. The frequency is an average equal to:  $\frac{32 \times f_{DCO(RSEL,DCO)} \times f_{DCO(RSEL,DCO+1)}}{f_{average}} = \frac{32 \times f_{DCO(RSEL,DCO)} \times f_{DCO(RSEL,DCO+1)}}{f_{DCO(RSEL,DCO)}}$

$$f_{average} = \frac{\frac{32 \text{ MDCO(RSEL,DCO)} \text{ MDCO(RSEL,DCO+1)}}{\text{MOD} \times f_{DCO(RSEL,DCO)} + (32 - \text{MOD)} \times f_{DCO(RSEL,DCO+1)}}$$

### **DCO Frequency**

|                        | PARAMETER                                    | TEST CONDITIONS                                    | V <sub>CC</sub> | MIN  | TYP   | MAX  | UNIT  |

|------------------------|----------------------------------------------|----------------------------------------------------|-----------------|------|-------|------|-------|

|                        |                                              | RSELx < 14                                         |                 | 1.8  |       | 3.6  |       |

| $V_{CC}$               | Supply voltage                               | RSELx = 14                                         |                 | 2.2  |       | 3.6  | V     |

|                        |                                              | RSELx = 15                                         |                 | 3.0  |       | 3.6  |       |

| f <sub>DCO(0,0)</sub>  | DCO frequency (0, 0)                         | RSELx = 0, $DCOx = 0$ , $MODx = 0$                 | 3 V             | 0.06 |       | 0.14 | MHz   |

| f <sub>DCO(0,3)</sub>  | DCO frequency (0, 3)                         | RSELx = 0, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.12  |      | MHz   |

| f <sub>DCO(1,3)</sub>  | DCO frequency (1, 3)                         | RSELx = 1, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.15  |      | MHz   |

| f <sub>DCO(2,3)</sub>  | DCO frequency (2, 3)                         | RSELx = 2, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.21  |      | MHz   |

| f <sub>DCO(3,3)</sub>  | DCO frequency (3, 3)                         | RSELx = 3, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.30  |      | MHz   |

| f <sub>DCO(4,3)</sub>  | DCO frequency (4, 3)                         | RSELx = 4, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.41  |      | MHz   |

| f <sub>DCO(5,3)</sub>  | DCO frequency (5, 3)                         | RSELx = 5, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.58  |      | MHz   |

| f <sub>DCO(6,3)</sub>  | DCO frequency (6, 3)                         | RSELx = 6, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 0.80  |      | MHz   |

| f <sub>DCO(7,3)</sub>  | DCO frequency (7, 3)                         | RSELx = 7, $DCOx = 3$ , $MODx = 0$                 | 3 V             | 0.80 |       | 1.50 | MHz   |

| f <sub>DCO(8,3)</sub>  | DCO frequency (8, 3)                         | RSELx = 8, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 1.6   |      | MHz   |

| f <sub>DCO(9,3)</sub>  | DCO frequency (9, 3)                         | RSELx = 9, $DCOx = 3$ , $MODx = 0$                 | 3 V             |      | 2.3   |      | MHz   |

| f <sub>DCO(10,3)</sub> | DCO frequency (10, 3)                        | RSELx = 10, DCOx = 3, MODx = 0                     | 3 V             |      | 3.4   |      | MHz   |

| f <sub>DCO(11,3)</sub> | DCO frequency (11, 3)                        | RSELx = 11, DCOx = 3, MODx = 0                     | 3 V             |      | 4.25  |      | MHz   |

| f <sub>DCO(12,3)</sub> | DCO frequency (12, 3)                        | RSELx = 12, $DCOx = 3$ , $MODx = 0$                | 3 V             | 4.3  |       | 7.30 | MHz   |

| f <sub>DCO(13,3)</sub> | DCO frequency (13, 3)                        | RSELx = 13, $DCOx = 3$ , $MODx = 0$                | 3 V             |      | 7.8   |      | MHz   |

| f <sub>DCO(14,3)</sub> | DCO frequency (14, 3)                        | RSELx = 14, $DCOx = 3$ , $MODx = 0$                | 3 V             | 8.6  |       | 13.9 | MHz   |

| f <sub>DCO(15,3)</sub> | DCO frequency (15, 3)                        | RSELx = 15, DCOx = 3, MODx = 0                     | 3 V             |      | 15.25 |      | MHz   |

| f <sub>DCO(15,7)</sub> | DCO frequency (15, 7)                        | RSELx = 15, DCOx = 7, MODx = 0                     | 3 V             |      | 21    |      | MHz   |

| S <sub>RSEL</sub>      | Frequency step between range RSEL and RSEL+1 | $S_{RSEL} = f_{DCO(RSEL+1,DCO)}/f_{DCO(RSEL,DCO)}$ | 3 V             |      | 1.35  |      | ratio |

| S <sub>DCO</sub>       | Frequency step between tap DCO and DCO+1     | $S_{DCO} = f_{DCO(RSEL,DCO+1)}/f_{DCO(RSEL,DCO)}$  | 3 V             |      | 1.08  |      | ratio |

|                        | Duty cycle                                   |                                                    | 3 V             |      | 50    |      | %     |

## Calibrated DCO Frequencies - Tolerance Over Temperature 0°C to 85°C

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER                         | TEST CONDITIONS                                                                | T <sub>A</sub> | V <sub>cc</sub> | MIN | TYP  | MAX | UNIT |

|-----------------------------------|--------------------------------------------------------------------------------|----------------|-----------------|-----|------|-----|------|

| 1-MHz tolerance over temperature  | BCSCTL1= CALBC1_1MHZ,<br>DCOCTL = CALDCO_1MHZ,<br>calibrated at 30°C and 3 V   | 0°C to 85°C    | 3 V             | -3  | ±0.5 | 3   | %    |

| 8-MHz tolerance over temperature  | BCSCTL1= CALBC1_8MHZ,<br>DCOCTL = CALDCO_8MHZ,<br>calibrated at 30°C and 3 V   | 0°C to 85°C    | 3 V             | -3  | ±1.0 | 3   | %    |

| 12-MHz tolerance over temperature | BCSCTL1= CALBC1_12MHZ,<br>DCOCTL = CALDCO_12MHZ,<br>calibrated at 30°C and 3 V | 0°C to 85°C    | 3 V             | -3  | ±1.0 | 3   | %    |

| 16-MHz tolerance over temperature | BCSCTL1= CALBC1_16MHZ,<br>DCOCTL = CALDCO_16MHZ,<br>calibrated at 30°C and 3 V | 0°C to 85°C    | 3 V             | -3  | ±2.0 | 3   | %    |

## Calibrated DCO Frequencies - Tolerance Over Supply Voltage V<sub>CC</sub>

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER                             | TEST CONDITIONS                                                                | TA   | V <sub>cc</sub> | MIN | TYP | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------------------------------|------|-----------------|-----|-----|-----|------|

| 1-MHz tolerance over V <sub>CC</sub>  | BCSCTL1= CALBC1_1MHZ,<br>DCOCTL = CALDCO_1MHZ,<br>calibrated at 30°C and 3 V   | 25°C | 1.8 V to 3.6 V  | -3  | ±2  | +3  | %    |

| 8-MHz tolerance over V <sub>CC</sub>  | BCSCTL1= CALBC1_8MHZ,<br>DCOCTL = CALDCO_8MHZ,<br>calibrated at 30°C and 3 V   | 25°C | 1.8 V to 3.6 V  | -3  | ±2  | +3  | %    |

| 12-MHz tolerance over V <sub>CC</sub> | BCSCTL1= CALBC1_12MHZ,<br>DCOCTL = CALDCO_12MHZ,<br>calibrated at 30°C and 3 V | 25°C | 2.2 V to 3.6 V  | -3  | ±2  | +3  | %    |

| 16-MHz tolerance over V <sub>CC</sub> | BCSCTL1= CALBC1_16MHZ,<br>DCOCTL = CALDCO_16MHZ,<br>calibrated at 30°C and 3 V | 25°C | 3 V to 3.6 V    | -6  | ±2  | +3  | %    |

## **Calibrated DCO Frequencies - Overall Tolerance**

| PARAMETER                | TEST CONDITIONS                                                                | T <sub>A</sub>   | V <sub>CC</sub> | MIN | TYP | MAX | UNIT |

|--------------------------|--------------------------------------------------------------------------------|------------------|-----------------|-----|-----|-----|------|

| 1-MHz tolerance overall  | BCSCTL1= CALBC1_1MHZ,<br>DCOCTL = CALDCO_1MHZ,<br>calibrated at 30°C and 3 V   | I: -40°C to 85°C | 1.8 V to 3.6 V  | -5  | ±2  | +5  | %    |

| 8-MHz tolerance overall  | BCSCTL1= CALBC1_8MHZ,<br>DCOCTL = CALDCO_8MHZ,<br>calibrated at 30°C and 3 V   | I: -40°C to 85°C | 1.8 V to 3.6 V  | -5  | ±2  | +5  | %    |

| 12-MHz tolerance overall | BCSCTL1= CALBC1_12MHZ,<br>DCOCTL = CALDCO_12MHZ,<br>calibrated at 30°C and 3 V | I: -40°C to 85°C | 2.2 V to 3.6 V  | -5  | ±2  | +5  | %    |

| 16-MHz tolerance overall | BCSCTL1= CALBC1_16MHZ,<br>DCOCTL = CALDCO_16MHZ,<br>calibrated at 30°C and 3 V | I: -40°C to 85°C | 3 V to 3.6 V    | -6  | ±3  | +6  | %    |

## Wake-Up From Lower-Power Modes (LPM3, LPM4)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                         | PARAMETER                                         | TEST CONDITIONS                                  | V <sub>cc</sub> | MIN | TYP              | MAX | UNIT |

|-------------------------|---------------------------------------------------|--------------------------------------------------|-----------------|-----|------------------|-----|------|

|                         |                                                   | BCSCTL1 = CALBC1_1MHZ,<br>DCOCTL = CALDCO_1MHZ   |                 |     | 2                |     |      |

|                         | DCO clock wake-up time                            | BCSCTL1 = CALBC1_8MHZ,<br>DCOCTL = CALDCO_8MHZ   | 2.2 V, 3 V      |     | 1.5              |     |      |

| <sup>T</sup> DCO,LPM3/4 | from LPM3 or LPM4 <sup>(1)</sup>                  | BCSCTL1 = CALBC1_12MHZ,<br>DCOCTL = CALDCO_12MHZ |                 |     | 1                | μs  |      |

|                         |                                                   | BCSCTL1 = CALBC1_16MHZ,<br>DCOCTL = CALDCO_16MHZ | 3 V             |     | 1                |     |      |

| t <sub>CPU,LPM3/4</sub> | CPU wake-up time from LPM3 or LPM4 <sup>(2)</sup> |                                                  |                 |     | CLK +<br>,LPM3/4 |     |      |

<sup>(1)</sup> The DCO clock wake-up time is measured from the edge of an external wake-up signal (for example, port interrupt) to the first clock edge observable externally on a clock pin (MCLK or SMCLK).

## Typical Characteristics - DCO Clock Wake-Up Time From LPM3/4

<sup>(2)</sup> Parameter applicable only if DCOCLK is used for MCLK.

## Internal Very-Low-Power Low-Frequency Oscillator (VLO)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                                     | PARAMETER                                         | T <sub>A</sub> | V <sub>cc</sub> | MIN | TYP | MAX | UNIT |

|-------------------------------------|---------------------------------------------------|----------------|-----------------|-----|-----|-----|------|

| $f_{VLO}$                           | VLO frequency                                     | -40°C to 85°C  | 3 V             | 4   | 12  | 20  | kHz  |

| df <sub>VLO</sub> /dT               | VLO frequency temperature drift <sup>(1)</sup>    | -40°C to 85°C  | 3 V             |     | 0.5 |     | %/°C |

| df <sub>VLO</sub> /dV <sub>CC</sub> | VLO frequency supply voltage drift <sup>(2)</sup> | 25°C           | 1.8 V to 3.6 V  |     | 4   |     | %/V  |

Calculated using the box method: (MAX(-40 to  $85^{\circ}$ C) – MIN(-40 to  $85^{\circ}$ C)) / MIN(-40 to  $85^{\circ}$ C) / ( $85^{\circ}$ C – (-40°C)) Calculated using the box method: (MAX(1.8 to 3.6 V) – MIN(1.8 to 3.6 V)) / MIN(1.8 to 3.6 V) / (3.6 V – 1.8 V)

#### Timer\_A

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                     | PARAMETER               | TEST CONDITIONS                                                     | $v_{cc}$ | MIN | TYP MA              | X UNIT |

|---------------------|-------------------------|---------------------------------------------------------------------|----------|-----|---------------------|--------|

| $f_{TA}$            | Timer_A clock frequency | Internal: SMCLK<br>External: TACLK, INCLK<br>Duty cycle = 50% ± 10% |          |     | f <sub>SYSTEM</sub> | MHz    |

| t <sub>TA,cap</sub> | Timer_A capture timing  | TAx                                                                 | 3 V      | 20  |                     | ns     |

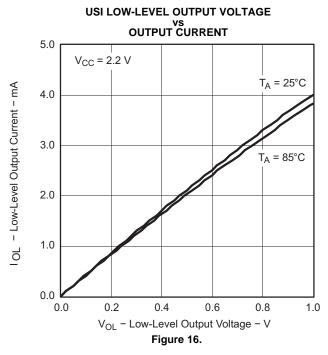

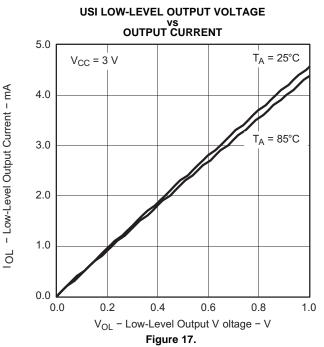

### USI, Universal Serial Interface (MSP430G2230 Only)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                    | PARAMETER                               | TEST CONDITIONS                                                                                                         | V <sub>CC</sub> | MIN             | TYP          | MAX                   | UNIT |

|--------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|-----------------------|------|

| f <sub>USI</sub>   | USI clock frequency                     | External: SCLK,                                                                                                         |                 |                 | $f_{SYSTEM}$ |                       | MHz  |

| V <sub>OL,I2</sub> | Low-level output voltage on SDA and SCL | Duty cycle = $50\% \pm 10\%$ ,<br>SPI slave mode USI module in I <sup>2</sup> C mode,<br>$I_{(OLmax)} = 1.5 \text{ mA}$ | 3 V             | V <sub>SS</sub> |              | V <sub>SS</sub> + 0.4 | >    |

# Typical Characteristics, USI Low-Level Output Voltage on SDA and SCL (MSP430G2230 Only)

24

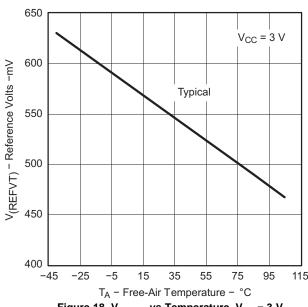

## Comparator\_A+ (MSP430G2210 Only)

|                                       | PARAMETER                                                | TEST CONDITIONS                                                       | V <sub>CC</sub> | MIN | TYP  | MAX                | UNIT |

|---------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------|-----------------|-----|------|--------------------|------|

| I <sub>(DD)</sub> <sup>(1)</sup>      |                                                          | CAON = 1, CARSEL = 0, CAREF = 0                                       | 3 V             |     | 45   |                    | μA   |

| I <sub>(Refladder/</sub><br>RefDiode) |                                                          | CAON = 1, CARSEL = 0, CAREF = 1/2/3,<br>No load at CA0 and CA1        | 3 V             |     | 45   |                    | μΑ   |

| V <sub>(IC)</sub>                     | Common-mode input voltage                                | CAON = 1                                                              | 3 V             | 0   |      | V <sub>CC</sub> -1 | V    |

| V <sub>(Ref025)</sub>                 | (Voltage at 0.25 V <sub>CC</sub> node) / V <sub>CC</sub> | PCA0 = 1, CARSEL = 1, CAREF = 1,<br>No load at CA0 and CA1            | 3 V             |     | 0.24 |                    |      |

| V <sub>(Ref050)</sub>                 | (Voltage at 0.5 V <sub>CC</sub> node) / V <sub>CC</sub>  | PCA0 = 1, CARSEL = 1, CAREF = 2,<br>No load at CA0 and CA1            | 3 V             |     | 0.48 |                    |      |

| V <sub>(RefVT)</sub>                  | See Figure 18 and Figure 19                              | PCA0 = 1, CARSEL = 1, CAREF = 3,<br>No load at CA0 and CA1, TA = 85°C | 3 V             |     | 490  |                    | mV   |

| V <sub>(offset)</sub>                 | Offset voltage (2)                                       |                                                                       | 3 V             |     | ±10  |                    | mV   |

| V <sub>hys</sub>                      | Input hysteresis                                         | CAON = 1                                                              | 3 V             |     | 0.7  |                    | mV   |

|                                       | Response time                                            | T <sub>A</sub> = 25°C, Overdrive 10 mV,<br>Without filter: CAF = 0    | 2.1/            |     | 120  |                    | ns   |

| t(response)                           | (low-to-high and high-to-low)                            | T <sub>A</sub> = 25°C, Overdrive 10 mV,<br>With filter: CAF = 1       | 3 V             |     | 1.5  |                    | μs   |

The leakage current for the Comparator\_A+ terminals is identical to I<sub>lkg(Px.y)</sub> specification.

The input offset voltage can be cancelled by using the CAEX bit to invert the Comparator\_A+ inputs on successive measurements. The two successive measurements are then summed together.

# Typical Characteristics - Comparator\_A+ (MSP430G2210 Only)

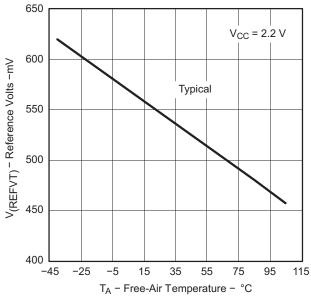

Figure 18.  $V_{(RefVT)}$  vs Temperature,  $V_{CC} = 3 V$

Figure 19.  $V_{(RefVT)}$  vs Temperature,  $V_{CC}$  = 2.2 V

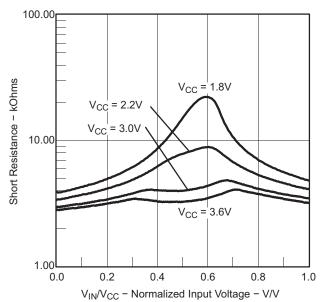

Figure 20. Short Resistance vs V<sub>IN</sub>/V<sub>CC</sub>

## 10-Bit ADC, Power Supply and Input Range Conditions (MSP430G2230 Only)

|                     | PARAMETER                                                          | TEST CONDITIONS                                                                                              | T <sub>A</sub> | V <sub>cc</sub> | MIN | TYP  | MAX      | UNIT |

|---------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----|------|----------|------|

| V <sub>CC</sub>     | Analog supply voltage                                              | V <sub>SS</sub> = 0 V                                                                                        |                |                 | 2.2 |      | 3.6      | V    |

| V <sub>Ax</sub>     | Analog input voltage (2)                                           | All Ax terminals, Analog inputs selected in ADC10AE register                                                 |                | 3 V             | 0   |      | $V_{CC}$ | V    |

| I <sub>ADC10</sub>  | ADC10 supply current <sup>(3)</sup>                                | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 1, REFON = 0,<br>ADC10SHT0 = 1, ADC10SHT1 = 0,<br>ADC10DIV = 0 | 25°C           | 3 V             |     | 0.6  |          | mA   |

|                     | Reference supply current,                                          | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REF2_5V = 0,<br>REFON = 1, REFOUT = 0                       | 2500           | 2.1/            |     | 0.25 |          | A    |

| I <sub>REF+</sub>   | Reference supply current, reference buffer disabled <sup>(4)</sup> | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REF2_5V = 1,<br>REFON = 1, REFOUT = 0                       | 25°C           | 3 V             |     | 0.25 |          | mA   |

| I <sub>REFB,0</sub> | Reference buffer supply current with ADC10SR = $0^{(4)}$           | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REFON = 1,<br>REF2_5V = 0, REFOUT = 1,<br>ADC10SR = 0       | 25°C           | 3 V             |     | 1.1  |          | mA   |

| I <sub>REFB,1</sub> | Reference buffer supply current with ADC10SR = 1 (4)               | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REFON = 1,<br>REF2_5V = 0, REFOUT = 1,<br>ADC10SR = 1       | 25°C           | 3 V             |     | 0.5  |          | mA   |

| Cı                  | Input capacitance                                                  | Only one terminal Ax can be selected at one time                                                             | 25°C           | 3 V             |     |      | 27       | pF   |

| $R_{l}$             | Input MUX ON resistance                                            | $0 \text{ V} \leq \text{V}_{Ax} \leq \text{V}_{CC}$                                                          | 25°C           | 3 V             |     | 1000 |          | Ω    |

The leakage current is defined in the leakage current table with Px.y/Ax parameter.

The analog input voltage range must be within the selected reference voltage range  $V_{R+}$  to  $V_{R-}$  for valid conversion results.

The internal reference supply current is not included in current consumption parameter  $I_{ADC10}$ . The internal reference current is supplied by terminal  $V_{CC}$ . Consumption is independent of the ADC10ON control bit, unless a conversion is active. The REFON bit enables the built-in reference to settle before starting an A/D conversion.

## 10-Bit ADC, Built-In Voltage Reference (MSP430G2230 Only)

|                       | PARAMETER                                                 | TEST CONDITIONS                                                                                                                   | V <sub>cc</sub> | MIN  | TYP | MAX  | UNIT |

|-----------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----|------|------|

| V                     | Positive built-in reference                               | I <sub>VREF+</sub> ≤ 1 mA, REF2_5V = 0                                                                                            |                 | 2.2  |     |      | V    |

| $V_{CC,REF+}$         | analog supply voltage range                               | I <sub>VREF+</sub> ≤ 1 mA, REF2_5V = 1                                                                                            |                 | 2.9  |     |      | V    |

| V                     | Positive built-in reference                               | $I_{VREF+} \le I_{VREF+} max$ , REF2_5V = 0                                                                                       | 3 V             | 1.41 | 1.5 | 1.59 | V    |

| V <sub>REF+</sub>     | voltage                                                   | $I_{VREF+} \le I_{VREF+} max$ , REF2_5V = 1                                                                                       | 3 V             | 2.35 | 2.5 | 2.65 | V    |

| I <sub>LD,VREF+</sub> | Maximum VREF+ load current                                |                                                                                                                                   | 3 V             |      |     | ±1   | mA   |

|                       | VDEE , load regulation                                    | $I_{VREF+}$ = 500 μA ± 100 μA,<br>Analog input voltage $V_{Ax}$ ≈ 0.75 V,<br>REF2_5V = 0                                          | 3 V             |      |     | ±2   | LSB  |

|                       | VREF+ load regulation                                     | $I_{VREF+}$ = 500 μA ± 100 μA,<br>Analog input voltage $V_{Ax}$ ≈ 1.25 V,<br>REF2_5V = 1                                          | 3 V             |      |     | ±2   | LSB  |

|                       | V <sub>REF+</sub> load regulation response time           | $I_{VREF+} = 100 \mu A \rightarrow 900 \mu A,$ $V_{AX} \approx 0.5 \times VREF+,$ Error of conversion result ≤ 1 LSB, ADC10SR = 0 | 3 V             |      |     | 400  | ns   |

| C <sub>VREF+</sub>    | Maximum capacitance at pin VREF+                          | I <sub>VREF+</sub> ≤ ±1 mA, REFON = 1, REFOUT = 1                                                                                 | 3 V             |      |     | 100  | pF   |

| TC <sub>REF+</sub>    | Temperature coefficient (1)                               | I <sub>VREF+</sub> = const with 0 mA ≤ I <sub>VREF+</sub> ≤ 1 mA                                                                  | 3 V             |      |     | ±100 | ppm/ |

| <sup>t</sup> REFON    | Settling time of internal reference voltage to 99.9% VREF | $I_{VREF+}$ = 0.5 mA, REF2_5V = 0,<br>REFON = 0 $\rightarrow$ 1                                                                   | 3.6 V           |      |     | 30   | μs   |

| <sup>t</sup> REFBURST | Settling time of reference<br>buffer to 99.9% VREF        | I <sub>VREF+</sub> = 0.5 mA,<br>REF2_5V = 1, REFON = 1,<br>REFBURST = 1, ADC10SR = 0                                              | 3 V             |      |     | 2    | μs   |

<sup>(1)</sup> Calculated using the box method: (MAX(-40 to 85°C) – MIN(-40 to 85°C)) / MIN(-40 to 85°C) / (85°C – (-40°C))

## 10-Bit ADC, External Reference (MSP430G2230 Only)(1)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)