Instruments

**MCF8315A** ZHCSPQ3A - DECEMBER 2022 - REVISED APRIL 2023

# MCF8315A 无传感器磁场定向控制 (FOC)集成 FET BLDC 驱动器

# 1 特性

- 采用集成无传感器电机控制算法的三相 BLDC 电机 驱动器

- 无代码场定向控制 (FOC)

- 模拟、PWM 和基于频率的速度输入模式:仅当 MCF8315A 配置为待机器件 (DEV MODE = 0b) 时可用

- 基于 I<sup>2</sup>C 的速度输入模式:在睡眠 (DEV\_MODE = 1b) 和待机器件 (DEV\_MODE = 0b) 中均可

- 使用电机参数提取工具 (MPET) 离线测量电机参

- 5点可配置速度配置文件支持

- 通过正向重新同步和反向驱动支持风力机

- 抗电压浪涌 (AVS) 保护

- 通过自动死区时间补偿提高了声学性能

- 4.5V至35V工作电压(绝对最大值40V)

- 高输出电流能力:4A 峰值

- 低 MOSFET 导通状态电阻

- T<sub>A</sub> = 25°C 时的 R<sub>DS(ON)</sub> (HS + LS): 240mΩ(典型值)

- 低功耗睡眠模式:请参阅表 7-6

- V<sub>VM</sub> = 24V、T<sub>A</sub> = 25°C 时为 5µA (最大值)

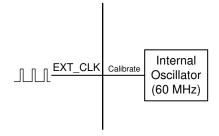

- 速度环路精度:3% 使用内部时钟,1% 使用外部时 钟参考

- 支持高达 75kHz 的 PWM 频率,以支持低电感电机

- 不需要外部电流检测电阻;使用内置电流检测功能

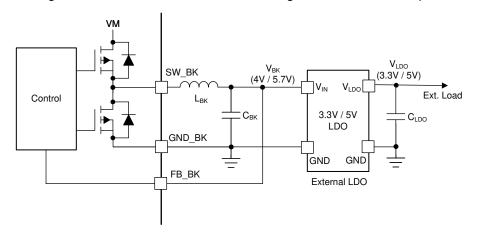

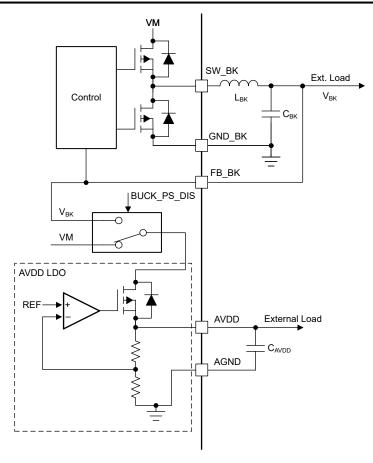

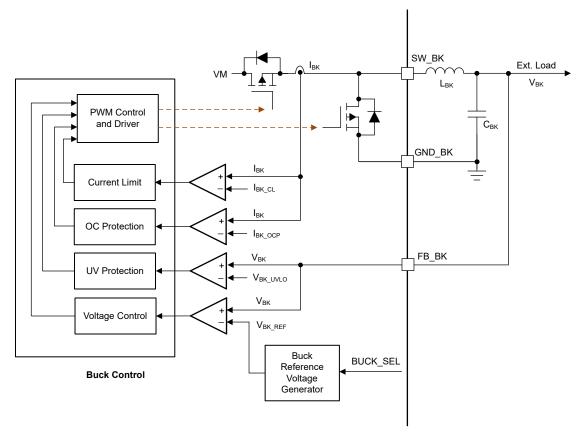

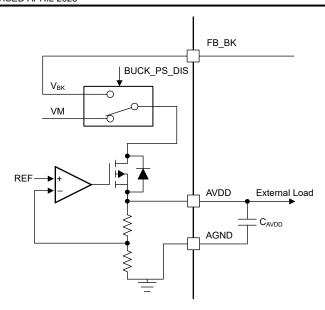

- 内置 3.3V, 20mA LDO 稳压器

- 内置 3.3V/5V、170mA 降压稳压器

- 专用 DRVOFF 引脚以禁用(高阻态)输出

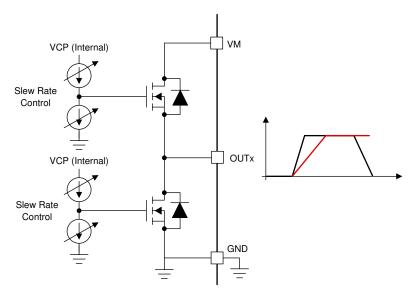

- 展频和压摆率,用于降低 EMI

- 整套集成保护特性

- 电源欠压锁定 (UVLO)

- 电源过压保护 (OVP)

- 电机锁定检测(5种不同类型)

- 过流保护 (OCP)

- 热警告和热关断 (OTW/TSD)

- 故障条件指示引脚 (nFAULT)

- 可选择通过 I<sup>2</sup>C 接口进行故障诊断

# 2 应用

- 无刷直流 (BLDC) 电机模块

- 住宅和起居风扇

- 空气净化器和加湿器风扇

- 洗衣机和洗碗机泵

- 汽车风扇和风机

- CPAP 呼吸机

# 3 说明

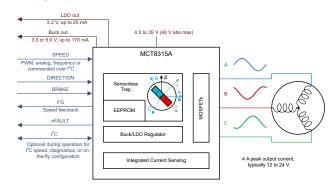

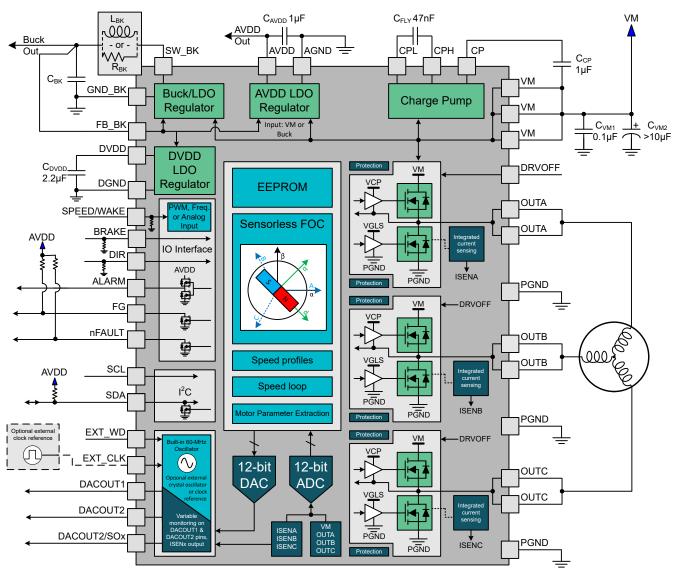

MCF8315A 为驱动峰值电流高达 4A 的速度受控型 12V 至 24V 无刷直流电机 (BLDC) 或永磁同步电机 (PMSM) 的客户提供了一个单芯片无代码无传感器 FOC 解决方案。MCF8315A 集成了三个 ½ 桥,具有 40V 的绝对最大电压和 240m  $\Omega$  的低  $R_{DS(ON)}$  (高边 + 低边 FET)。MCF8315A集成了电源管理电路,包括 可用于为外部电路供电的电压可调节降压稳压器 (3.3V/5V, 170mA)和LDO(3.3V/20mA)。

FOC 算法配置可存储在非易失性 EEPROM 中,从而 允许器件在配置后独立运行。该器件通过 PWM 输入、 模拟电压、可变频率方波或 I2C 命令接收速度命令。 MCF8315A 集成多种保护特性,旨在出现故障事件时 保护该器件、电机和系统。

#### 备注

TI 建议在发出速度命令之前,在器件上电或 从睡眠状态唤醒后添加 200ms 延迟。

# 器件信息(1)

| 器件型号       | 封装        | 封装尺寸(标称值)       |

|------------|-----------|-----------------|

| MCF8315A1V | VQFN (40) | 7.00mm x 5.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

### 参考文档:

- 参考 MCF8315A 调优指南

- 请参阅 MCF8315A EVM GUI

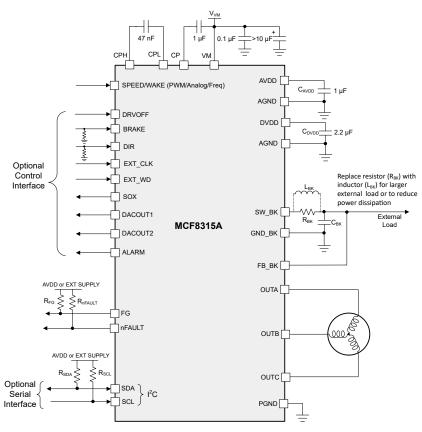

简化原理图

# **Table of Contents**

| 1 特性                                           | 1  | 7.6 EEPROM access and I <sup>2</sup> C interface | 76  |

|------------------------------------------------|----|--------------------------------------------------|-----|

|                                                |    | 7.7 EEPROM (Non-Volatile) Register Map           | 82  |

| - <i>—,,,</i><br>3 说明                          |    | 7.8 RAM (Volatile) Register Map                  | 135 |

| 4 Revision History                             |    | 8 Application and Implementation                 | 193 |

| 5 Pin Configuration and Functions              |    | 8.1 Application Information                      | 193 |

| 6 Specifications                               |    | 8.2 Typical Applications                         | 193 |

| 6.1 Absolute Maximum Ratings                   |    | 9 Power Supply Recommendations                   | 200 |

| 6.2 ESD Ratings                                |    | 9.1 Bulk Capacitance                             | 200 |

| 6.3 Recommended Operating Conditions           |    | 10 Layout                                        | 201 |

| 6.4 Thermal Information                        |    | 10.1 Layout Guidelines                           | 201 |

| 6.5 Electrical Characteristics                 | 6  | 10.2 Layout Example                              | 202 |

| 6.6 Characteristics of the SDA and SCL bus for |    | 10.3 Thermal Considerations                      | 203 |

| Standard and Fast mode                         | 11 | 11 Device and Documentation Support              | 204 |

| 6.7 Typical Characteristics                    |    | 11.1 支持资源                                        | 204 |

| 7 Detailed Description                         |    | 11.2 Trademarks                                  | 204 |

| 7.1 Overview                                   |    | 11.3 静电放电警告                                      | 204 |

| 7.2 Functional Block Diagram                   |    | 11.4 术语表                                         | 204 |

| 7.3 Feature Description                        |    | 12 Mechanical, Packaging, and Orderable          |     |

| 7.4 Device Functional Modes                    | 73 | Information                                      | 204 |

| 7.5 External Interface                         |    |                                                  |     |

|                                                |    |                                                  |     |

# **4 Revision History**

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2022 | *        | Initial Release |

| C | hanges from Revision * (December 2022) to Revision A (April 2023)                        | Page |

|---|------------------------------------------------------------------------------------------|------|

| • | Updated I <sup>2</sup> C Data Word section to clarify default I <sup>2</sup> C Target ID | 77   |

|   | Updated CRC Byte Calculation section with CRC initial value                              |      |

Product Folder Links: MCF8315A

# **5 Pin Configuration and Functions**

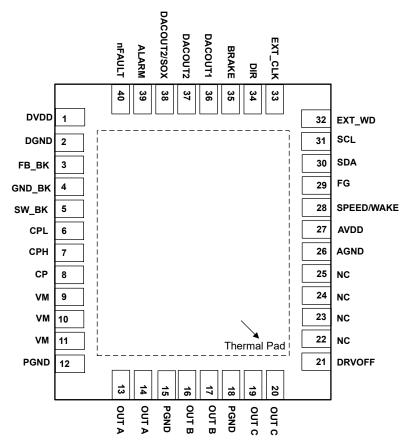

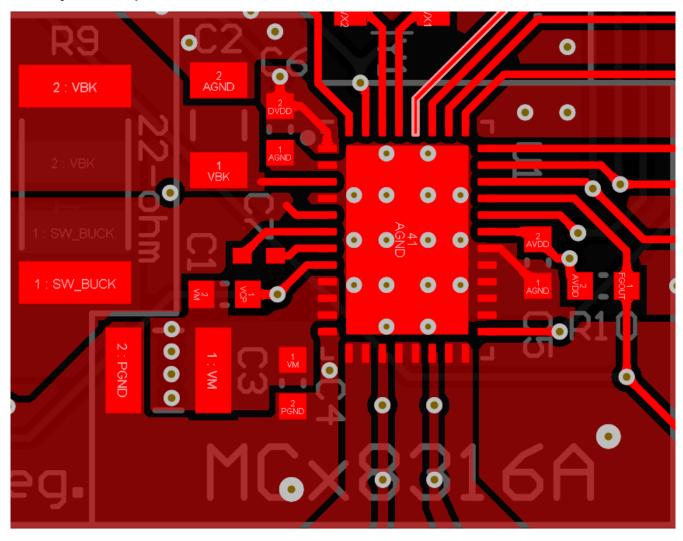

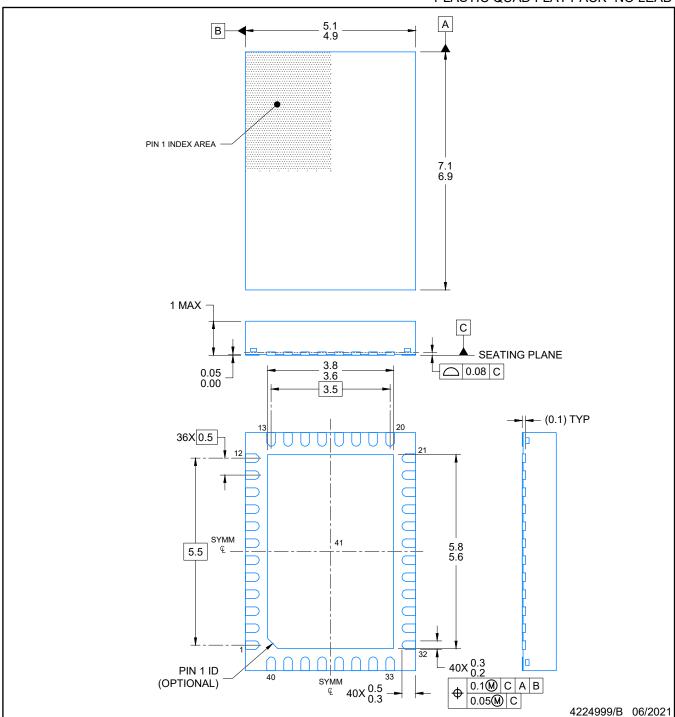

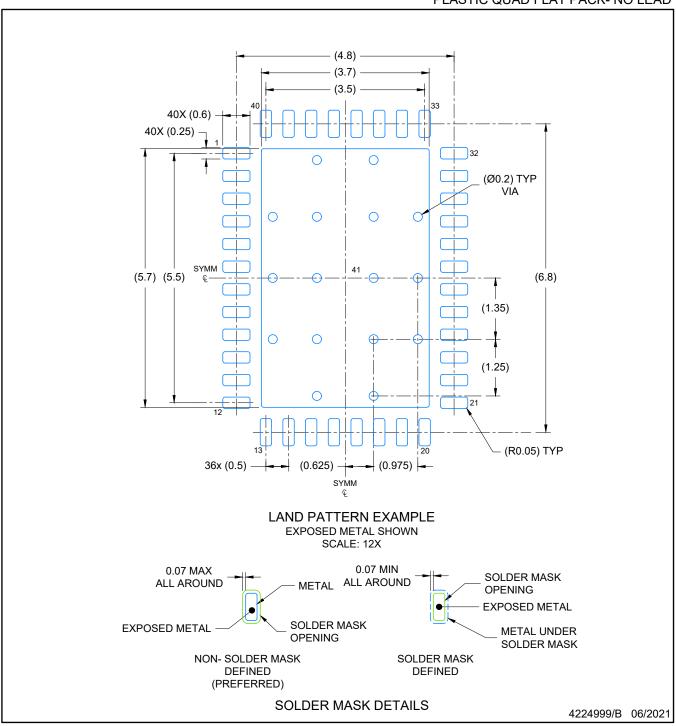

图 5-1. MCF8315A, 40-Pin VQFN With Exposed Thermal Pad, Top View

表 5-1. Pin Functions

| PIN     | 40-pin Package | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                           |  |  |

|---------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | MCF8315A       | ITPE(")             | DESCRIPTION                                                                                                                                                                                           |  |  |

| AGND    | 26             | GND                 | Device analog ground. Refer Layout Guidelines for connection recommendation.                                                                                                                          |  |  |

| ALARM   | 39             | 0                   | Alarm signal: push-pull output. Pulled logic high during fault condition, if enabled. If ALARM pin is not used, leave it floating.                                                                    |  |  |

| AVDD    | 27             | circuits.           |                                                                                                                                                                                                       |  |  |

| BRAKE   | 35             | I                   | High → Brake the motor Low → Normal motor operation If BRAKE pin is not used, connect to AGND directly. If BRAKE pin is used to brake the motor, use an external 100-kΩ pull-down resistor (to AGND). |  |  |

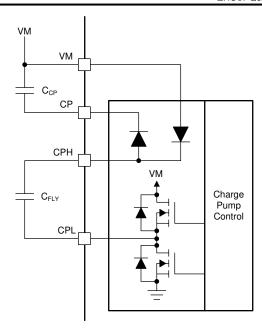

| СР      | 8              | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the CP and VM pins.                                                                                                    |  |  |

| CPH     | 7              | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, ceramic capacitor between                                                                                                                    |  |  |

| CPL     | 6              | PWR                 | the CPH and CPL pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the device.                                                                             |  |  |

| DACOUT1 | 36             | 0                   | Coutput DACOUT1                                                                                                                                                                                       |  |  |

| DACOUT2 | 37             | 0                   | DAC output DACOUT2                                                                                                                                                                                    |  |  |

# 表 5-1. Pin Functions (continued)

| PIN             | 40-pin Package |                     | 3-1. First unctions (continueu)                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------|----------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | MCF8315A       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DACOUT2/S<br>OX | 38             | 0                   | Multi-purpose pin: DAC output when configured as DACOUT2 CSA output when configured as SOX                                                                                                                                                                                                                                                                                                                                  |  |

| DGND            | 2              | GND                 | Device digital ground. Refer Layout Guidelines for connection recommendation.                                                                                                                                                                                                                                                                                                                                               |  |

| DIR             | 34             | I                   | Direction of motor spinning; When low, phase driving sequence is OUT A $\rightarrow$ OUT C $\rightarrow$ OUT B When high, phase driving sequence is OUT A $\rightarrow$ OUT B $\rightarrow$ OUT C If DIR pin is not used, connect to AGND or AVDD directly (depending on phase driving sequence needed). If DIR pin is used for changing motor spin direction, use an external 100-k $\Omega$ pull-down resistor (to AGND). |  |

| DRVOFF          | 21             | I                   | Coast (Hi-Z) all six MOSFETs when DRVOFF is high.                                                                                                                                                                                                                                                                                                                                                                           |  |

| DVDD            | 1              | PWR                 | 1.5-V internal regulator output. Connect a X5R or X7R, 2.2-µF, 6.3-V ceramic capacitor between the DVDD and DGND pins.                                                                                                                                                                                                                                                                                                      |  |

| EXT_CLK         | 33             | I                   | External clock reference input in external clock reference mode.                                                                                                                                                                                                                                                                                                                                                            |  |

| EXT_WD          | 32             | I                   | External watchdog input.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

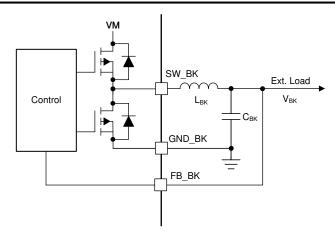

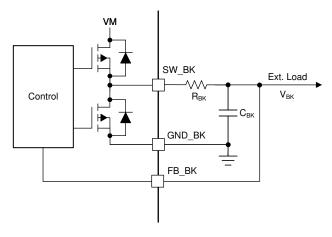

| FB_BK           | 3              | PWR I/O             | Feedback for buck regulator output control. Connect to buck regulator output after the inductor/resistor.                                                                                                                                                                                                                                                                                                                   |  |

| FG              | 29             | 0                   | Motor speed indicator : open-drain output; requires an external pull-up resistor to 1.8-V to 5.0-V.                                                                                                                                                                                                                                                                                                                         |  |

| GND_BK          | 4              | GND                 | Buck regulator ground. Refer Layout Guidelines for connection recommendation.                                                                                                                                                                                                                                                                                                                                               |  |

| NC              | 22, 23, 24, 25 | -                   | No connection. Leave these pins floating.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| nFAULT          | 40             | 0                   | Fault indicator. Pulled logic-low with fault condition; Open-drain output requires an external pull-up resistor to 1.8 V to 5.0 V.                                                                                                                                                                                                                                                                                          |  |

| OUTA            | 13, 14         | PWR O               | Half-bridge output A                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| OUTB            | 16, 17         | PWR O               | Half-bridge output B                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| OUTC            | 19, 20         | PWR O               | Half-bridge output C                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| PGND            | 12, 15, 18     | GND                 | Device power ground. Refer Layout Guidelines for connection recommendation.                                                                                                                                                                                                                                                                                                                                                 |  |

| SCL             | 31             | I                   | I <sup>2</sup> C clock input                                                                                                                                                                                                                                                                                                                                                                                                |  |

| SDA             | 30             | I/O                 | I <sup>2</sup> C data line                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SPEED/<br>WAKE  | 28             | I                   | Device speed input; supports analog, PWM or frequency based speed input. The speed pin input can be configured through SPEED_MODE.                                                                                                                                                                                                                                                                                          |  |

| SW_BK           | 5              | PWR                 | Buck switch node. Connect this pin to an inductor or resistor.                                                                                                                                                                                                                                                                                                                                                              |  |

| VM              | 9, 10, 11      | PWR I               | Device and motor power supply. Connect to motor supply voltage; bypass to PGND with one $0.1$ - $\mu$ F capacitor plus one bulk capacitor. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the device.                                                                                                                                                                              |  |

| Thermal pad     |                | GND                 | Must be connected to AGND.                                                                                                                                                                                                                                                                                                                                                                                                  |  |

(1) I = input, O = output, GND = ground, PWR = power, NC = no connect

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating ambient temperature range (unless otherwise noted)(1)

|                                                                                | MIN   | MAX                  | UNIT |

|--------------------------------------------------------------------------------|-------|----------------------|------|

| Power supply pin voltage (VM)                                                  | - 0.3 | 40                   | V    |

| Voltage difference between ground pins (GND_BK, DGND, PGND, AGND)              | - 0.3 | 0.3                  | V    |

| Charge pump voltage (CPH, CP)                                                  | - 0.3 | V <sub>VM</sub> + 6  | V    |

| Charge pump negative switching pin voltage (CPL)                               | - 0.3 | V <sub>VM</sub> +0.3 | V    |

| Switching node pin voltage (SW_BK)                                             | - 0.3 | V <sub>VM</sub> +0.3 | V    |

| Analog regulators pin voltage (AVDD)                                           | - 0.3 | 4                    | V    |

| Analog regulators pin voltage (DVDD)                                           | - 0.3 | 1.7                  | V    |

| Logic pin input voltage (BRAKE, DRVOFF, DIR, EXT_CLK, EXT_WD, SCL, SDA, SPEED) | - 0.3 | 6                    | V    |

| Open drain pin output voltage (nFAULT, FG)                                     | - 0.3 | 6                    | V    |

| Output pin voltage (OUTA, OUTB, OUTC)                                          | - 1   | V <sub>VM</sub> + 1  | V    |

| Ambient temperature, T <sub>A</sub>                                            | - 40  | 125                  | °C   |

| Junction temperature, T <sub>J</sub>                                           | - 40  | 150                  | °C   |

| Storage tempertaure, T <sub>stg</sub>                                          | - 65  | 150                  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime

# 6.2 ESD Ratings

|   |        |               |                                                                           | VALUE | UNIT |

|---|--------|---------------|---------------------------------------------------------------------------|-------|------|

|   | 1      | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>         | ±2000 | V    |

| ' | V(ESD) | discharge     | Charged device model (CDM), per JEDEC specification JS-002 <sup>(2)</sup> | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                       |                                      |                                                      | MIN   | NOM | MAX | UNIT |

|-----------------------|--------------------------------------|------------------------------------------------------|-------|-----|-----|------|

| $V_{VM}$              | Power supply voltage                 | $V_{VM}$                                             | 4.5   | 24  | 35  | V    |

| I <sub>OUT</sub> (1)  | Peak output winding current          | OUTA, OUTB, OUTC                                     |       |     | 4   | Α    |

| V <sub>IN_LOGIC</sub> | Logic input voltage                  | BRAKE, DRVOFF, DIR, EXT_CLK, EXT_WD, SPEED, SDA, SCL | - 0.1 |     | 5.5 | V    |

| V <sub>OD</sub>       | Open drain pullup voltage            | nFAULT, FG                                           | - 0.1 |     | 5.5 | V    |

| I <sub>OD</sub>       | Open drain output current capability | nFAULT, FG                                           |       |     | 5   | mA   |

| T <sub>A</sub>        | Operating ambient temperature        |                                                      | - 40  |     | 125 | °C   |

| TJ                    | Operating junction temperature       |                                                      | - 40  |     | 150 | °C   |

(1) Power dissipation and thermal limits must be observed

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.4 Thermal Information**

|                        |                                              | MCF8315A   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RGF (VQFN) | UNIT |

|                        |                                              | 40 Pins    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 28         | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.7       | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 8.9        | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 1.8        | °C/W |

| Ψ ЈВ                   | Junction-to-board characterization parameter | 8.9        | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.5        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

$T_J$  =  $-40^{\circ}$ C to +150°C,  $V_{VM}$  = 4.5 to 35 V (unless otherwise noted). Typical limits apply for  $T_A$  = 25°C,  $V_{VM}$  = 24 V

|                   | PARAMETER                      | TEST CONDITIONS                                                                                                                                                        | MIN   | TYP  | MAX   | UNIT |

|-------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| POWER:            | SUPPLIES                       |                                                                                                                                                                        |       |      |       |      |

| ı                 | VM sleep mode current          | V <sub>VM</sub> > 6 V, V <sub>SPEED</sub> = 0, T <sub>A</sub> = 25 °C                                                                                                  |       | 3    | 5     | μA   |

| $I_{VMQ}$         | VW sleep filode current        | V <sub>SPEED</sub> = 0, T <sub>A</sub> = 125 °C                                                                                                                        |       | 3.5  | 7     | μΑ   |

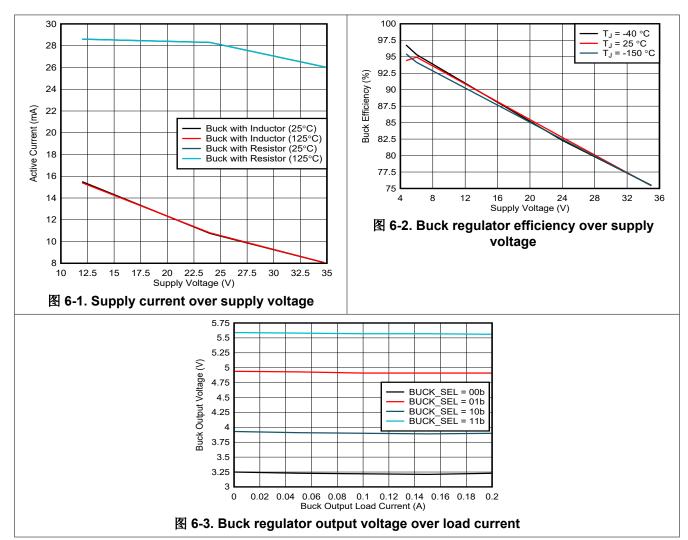

|                   |                                | $V_{VM} \geqslant$ 12 V, Standby Mode, DRVOFF = High, $T_A$ = 25 °C, $L_{BK}$ = 47 uH, $C_{BK}$ = 22 $\mu$ F                                                           |       | 8    | 16    | mA   |

| I <sub>VMS</sub>  | VM standby mode current        | $V_{VM}$ > 6 V, Standby Mode, DRVOFF = High, $T_A$ = 25 °C, $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F                                                             |       | 25   | 29    | mA   |

|                   |                                | $V_{VM} \geqslant$ 12 V, Standby Mode, DRVOFF = High, $L_{BK}$ = 47 uH, $C_{BK}$ = 22 $\mu$ F                                                                          |       | 8    | 16.5  | mA   |

|                   |                                | $V_{VM}$ > 6 V, Standby Mode, DRVOFF = High, $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F                                                                            |       | 25   | 29    | mA   |

|                   | VM operating mode current      | $V_{VM}$ > 6 V, $V_{SPEED}$ > $V_{EX\_SL}$ ,<br>PWM_FREQ_OUT = 0011b (25 kHz),<br>$T_A$ = 25 °C, $L_{BK}$ = 47 uH, $C_{BK}$ = 22 μF,<br>No Motor Connected             |       | 11   | 18    | mA   |

|                   |                                | $V_{VM}$ > 6 V, $V_{SPEED}$ > $V_{EX\_SL}$ ,<br>PWM_FREQ_OUT = 0011b (25 kHz),<br>$T_A$ = 25 °C, $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F, No<br>Motor Connected |       | 27   | 30.5  | mA   |

| I <sub>∨M</sub>   |                                | $V_{VM}$ > 6 V, $V_{SPEED}$ > $V_{EX\_SL}$ ,<br>PWM_FREQ_OUT = 0011b (25 kHz),<br>$L_{BK}$ = 47 uH, $C_{BK}$ = 22 $\mu$ F, No Motor<br>Connected                       |       | 11   | 17    | mA   |

|                   |                                | $V_{VM}$ > 6 V, $V_{SPEED}$ > $V_{EX\_SL}$ ,<br>PWM_FREQ_OUT = 0011b (25 kHz),<br>$R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F, No Motor<br>Connected                |       | 28   | 30.5  | mA   |

| V <sub>AVDD</sub> | Analog regulator voltage       | $0~\text{mA} \leqslant I_{\text{AVDD}} \leqslant 20~\text{mA}$                                                                                                         | 3.125 | 3.3  | 3.465 | V    |

| I <sub>AVDD</sub> | External analog regulator load |                                                                                                                                                                        |       |      | 20    | mA   |

| $V_{DVDD}$        | Digital regulator voltage      |                                                                                                                                                                        | 1.4   | 1.55 | 1.65  | V    |

| $V_{VCP}$         | Charge pump regulator voltage  | VCP with respect to VM                                                                                                                                                 | 4.0   | 4.7  | 5.5   | V    |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

$T_J = -40$ °C to +150°C,  $V_{VM} = 4.5$  to 35 V (unless otherwise noted). Typical limits apply for  $T_A = 25$ °C,  $V_{VM} = 24$  V

|               | PARAMETER                                                                      | TEST CONDITIONS                                                                                                                                      | MIN            | TYP                                                                       | MAX | UNIT |

|---------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------|-----|------|

| BUCK RE       | GULATOR                                                                        |                                                                                                                                                      |                |                                                                           |     |      |

|               |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leqslant$ $I_{BK}$ $\leqslant$ 170 mA, BUCK_SEL = 00b                                                                         | 3.1            | 3.3                                                                       | 3.5 | V    |

|               |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leqslant$ $I_{BK}$ $\leqslant$ 170 mA, BUCK_SEL = 01b                                                                         | 4.6            | 5.0                                                                       | 5.4 | V    |

| $V_{BK}$      | Buck regulator average voltage ( $L_{BK}$ = 47 $\mu$ H, $C_{BK}$ = 22 $\mu$ F) | $V_{VM}$ > 6 V, 0 mA $\leq$ $I_{BK}$ $\leq$ 170 mA, BUCK_SEL = 10b                                                                                   | 3.7            | 4.0                                                                       | 4.3 | V    |

|               |                                                                                | $V_{VM}$ > 6.7 V, 0 mA $\leqslant$ I <sub>BK</sub> $\leqslant$ 170 mA, BUCK_SEL = 11b                                                                | 5.2            | 5.7                                                                       | 6.2 | V    |

|               |                                                                                | $V_{VM}$ < 6.0 V (BUCK_SEL = 00b, 01b, 10b, 11b), 0 mA $\leq$ I <sub>BK</sub> $\leq$ 170 mA                                                          | I <sub>E</sub> | V <sub>VM</sub> -<br><sub>BK</sub> *(R <sub>LBK</sub><br>+2) <sup>1</sup> |     | V    |

|               |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leq$ $I_{BK}$ $\leq$ 20 mA, BUCK_SEL = 00b                                                                                    | 3.1            | 3.3                                                                       | 3.5 | V    |

|               | Buck regulator average voltage ( $L_{BK}$ = 22 $\mu$ H, $C_{BK}$ = 22 $\mu$ F) | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 20 mA, BUCK_SEL = 01b                                                                             | 4.6            | 5.0                                                                       | 5.4 | V    |

| $V_{BK}$      |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leq$ $I_{BK}$ $\leq$ 20 mA, BUCK_SEL = 10b                                                                                    | 3.7            | 4.0                                                                       | 4.3 | V    |

|               |                                                                                | $V_{VM}$ > 6.7 V, 0 mA $\leqslant$ I <sub>BK</sub> $\leqslant$ 20 mA, BUCK_SEL = 11b                                                                 | 5.2            | 5.7                                                                       | 6.2 | V    |

|               |                                                                                | $V_{VM}$ < 6.0 V (BUCK_SEL = 00b, 01b, 10b, 11b), 0 mA $\leq$ $I_{BK}$ $\leq$ 20 mA                                                                  | Ię             | V <sub>VM</sub> -<br><sub>BK</sub> *(R <sub>LBK</sub><br>+2) <sup>1</sup> |     | V    |

|               |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 10 mA, BUCK_SEL = 00b                                                                             | 3.1            | 3.3                                                                       | 3.5 | V    |

|               | Buck regulator average voltage $(R_{BK} = 22 \Omega, C_{BK} = 22 \mu F)$       | $V_{VM}$ > 6 V, 0 mA $\leq$ $I_{BK}$ $\leq$ 10 mA, BUCK_SEL = 01b                                                                                    | 4.6            | 5.0                                                                       | 5.4 | V    |

| $V_{BK}$      |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leq$ $I_{BK}$ $\leq$ 10 mA, BUCK_SEL = 10b                                                                                    | 3.7            | 4.0                                                                       | 4.3 | V    |

|               |                                                                                | $V_{VM}$ > 6.7 V, 0 mA $\leqslant$ I <sub>BK</sub> $\leqslant$ 10 mA, BUCK_SEL = 11b                                                                 | 5.2            | 5.7                                                                       | 6.2 | V    |

|               |                                                                                | $V_{VM}$ < 6.0 V (BUCK_SEL = 00b, 01b, 10b, 11b), 0 mA $\leq$ $I_{BK}$ $\leq$ 10 mA                                                                  |                | V <sub>VM</sub> -<br>I <sub>BK</sub> *(R <sub>BK</sub><br>+2)             |     | V    |

|               | Buck regulator ripple voltage                                                  | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 170 mA, Buck regulator with inductor, L <sub>BK</sub> = 47 uH, C <sub>BK</sub> = 22 $\mu$ F       | - 100          |                                                                           | 100 | mV   |

| $V_{BK\_RIP}$ |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 20 mA, Buck regulator with inductor, L <sub>BK</sub> = 22 uH, C <sub>BK</sub> = 22 µF             | - 100          |                                                                           | 100 | mV   |

|               |                                                                                | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 10 mA, Buck regulator with resistor; R <sub>BK</sub> = 22 $\Omega$ , C <sub>BK</sub> = 22 $\mu$ F | - 100          |                                                                           | 100 | mV   |

$T_J = -40$ °C to +150°C,  $V_{VM} = 4.5$  to 35 V (unless otherwise noted). Typical limits apply for  $T_A = 25$ °C,  $V_{VM} = 24$  V

|                        | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TEST CONDITIONS                                                                                                                                                    | MIN             | TYP              | MAX                        | UNIT                 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------------------|----------------------|

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L <sub>BK</sub> = 47 uH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 1b                                                                                              |                 |                  | 170                        | mA                   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L <sub>BK</sub> = 47 uH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 0b                                                                                              |                 |                  | 170 -<br>I <sub>AVDD</sub> | mA                   |

| 1                      | External busic regulator land                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | L <sub>BK</sub> = 22 uH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 1b                                                                                              |                 |                  | 20                         | mA                   |

| I <sub>BK</sub>        | External buck regulator load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L <sub>BK</sub> = 22 uH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 0b                                                                                              |                 |                  | 20 -<br>I <sub>AVDD</sub>  | mA                   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R <sub>BK</sub> = 22 Ω, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 1b                                                                                               |                 |                  | 10                         | mA                   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R <sub>BK</sub> = 22 Ω, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 0b                                                                                               |                 |                  | 10 -<br>I <sub>AVDD</sub>  | mA                   |

|                        | Dool on the state of the state | Regulation Mode                                                                                                                                                    | 20              |                  | 535                        | kHz                  |

| f <sub>SW_BK</sub>     | Buck regulator switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Linear Mode                                                                                                                                                        | 20              |                  | 535                        | kHz                  |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> rising, BUCK_SEL = 00b                                                                                                                             | 2.7             | 2.8              | 2.95                       | V                    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> falling, BUCK_SEL = 00b                                                                                                                            | 2.5             | 2.6              | 2.7                        | V                    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> rising, BUCK_SEL = 01b                                                                                                                             | 4.3             | 4.4              | 4.55                       | V                    |

| .,                     | Buck regulator undervoltage lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>BK</sub> falling, BUCK_SEL = 01b                                                                                                                            | 4.1             | 4.2              | 4.36                       | V                    |

| V <sub>BK_UV</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> rising, BUCK_SEL = 10b                                                                                                                             | 2.7             | 2.8              | 2.95                       | V                    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> falling, BUCK_SEL = 10b                                                                                                                            | 2.5             | 2.6              | 2.7                        | V                    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> rising, BUCK_SEL = 11b                                                                                                                             | 4.3             | 4.4              | 4.55                       | V                    |

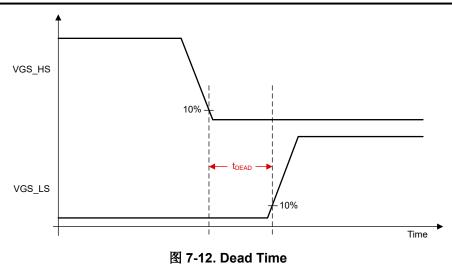

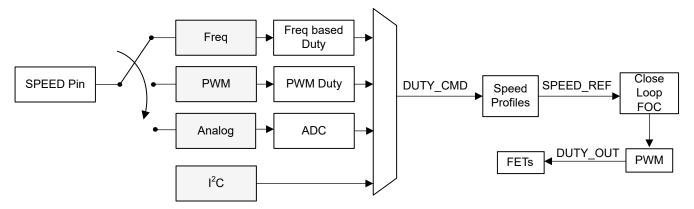

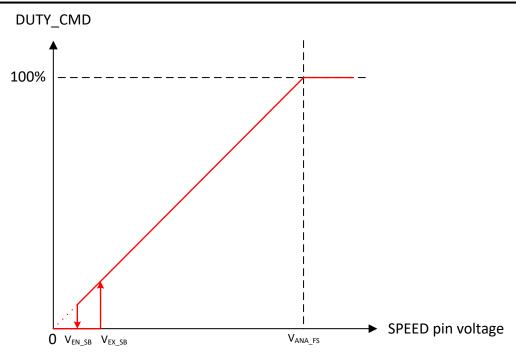

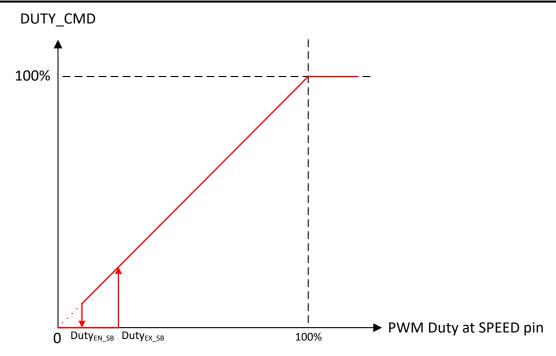

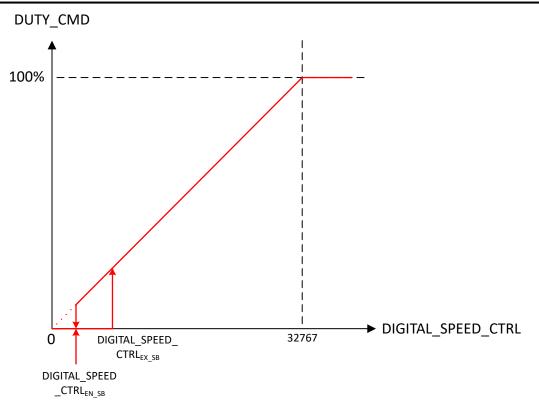

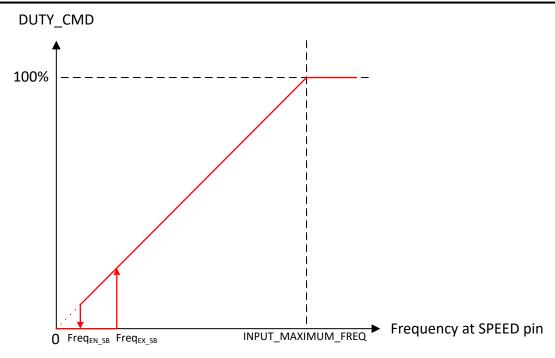

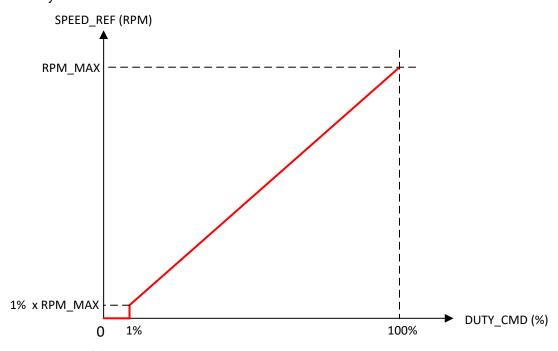

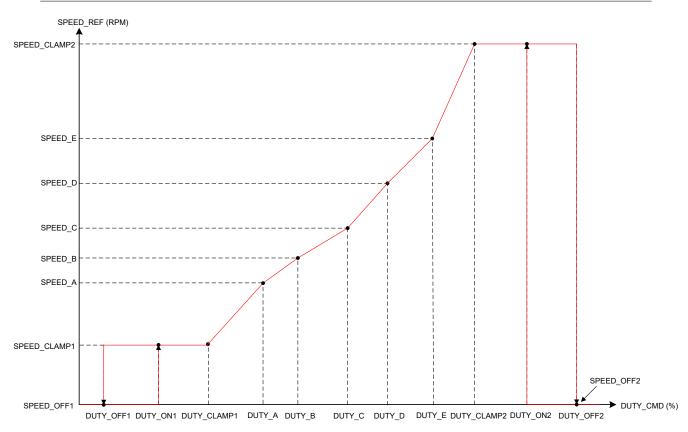

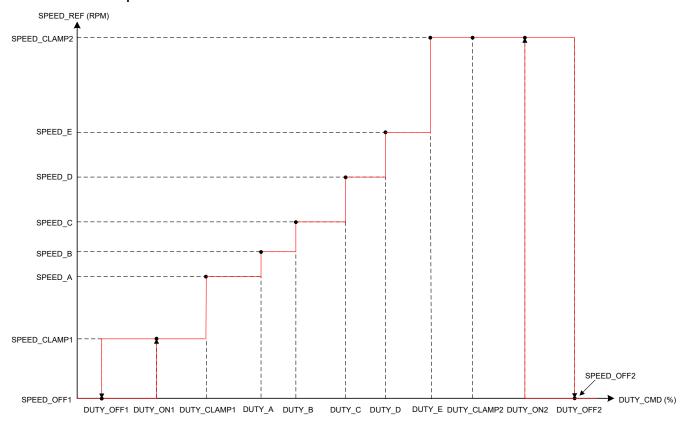

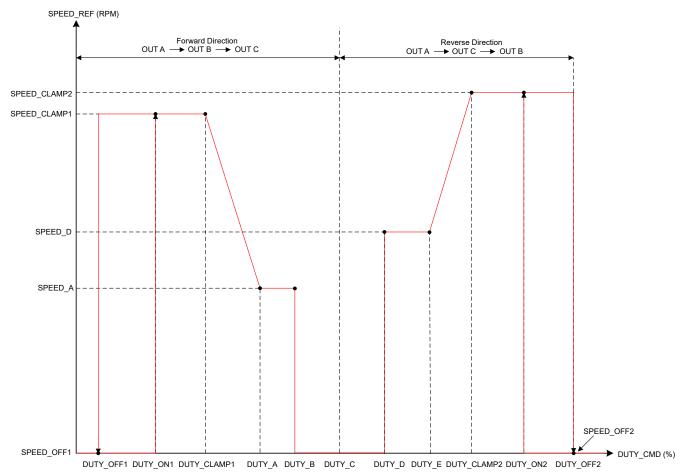

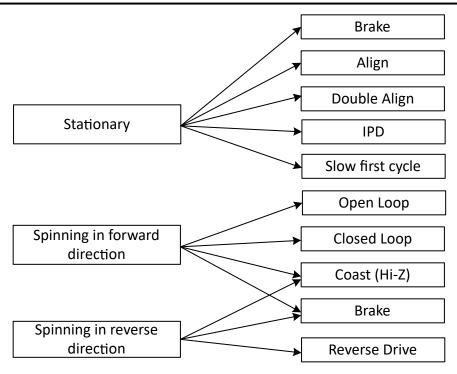

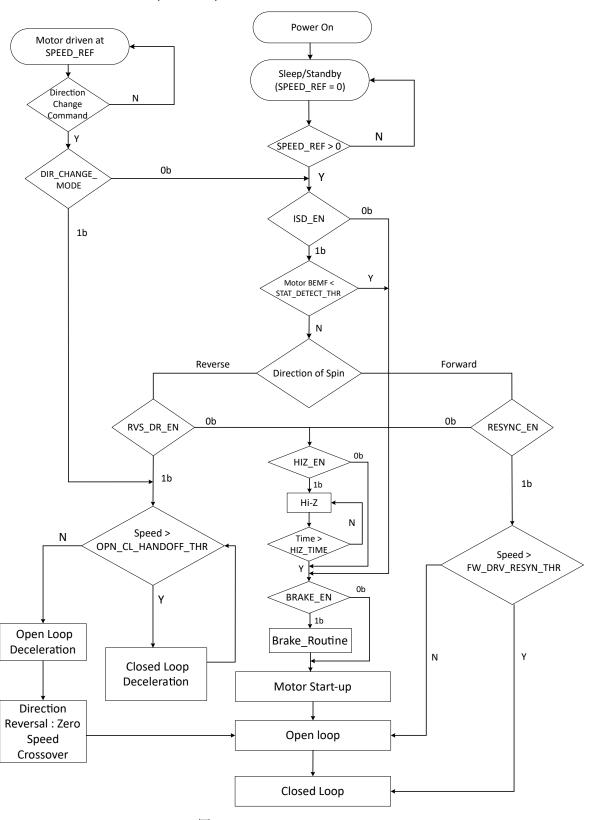

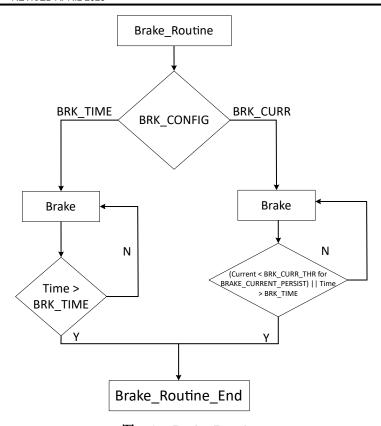

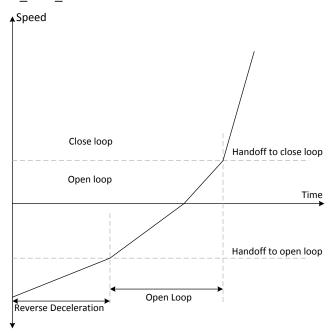

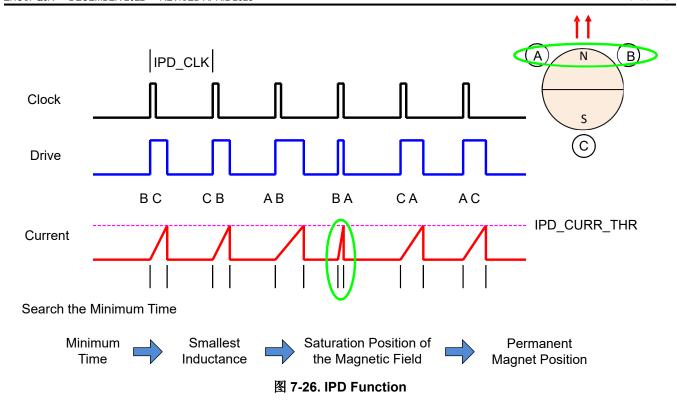

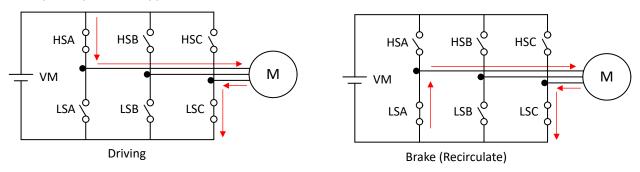

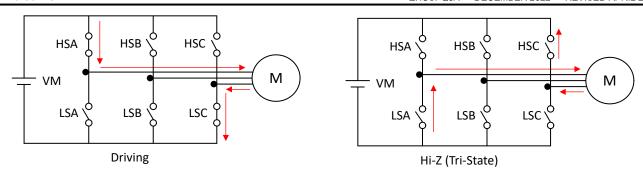

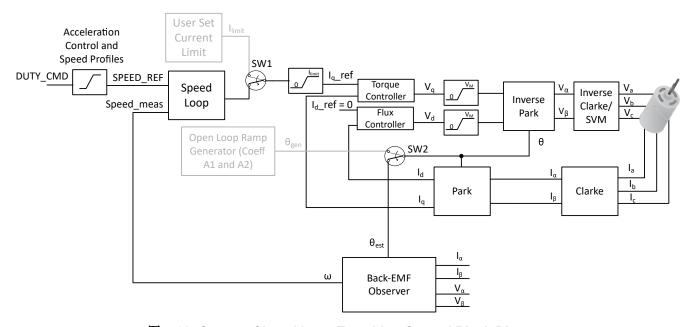

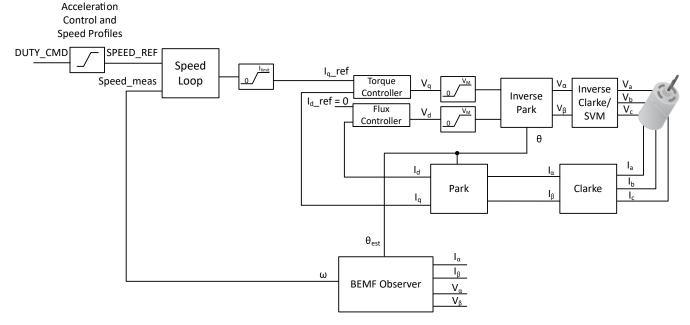

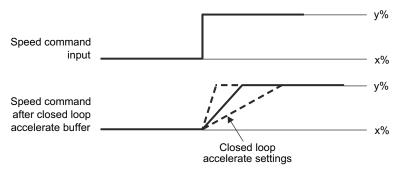

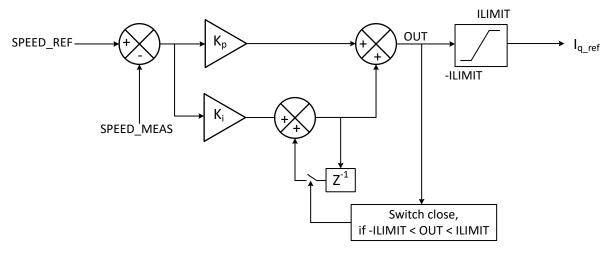

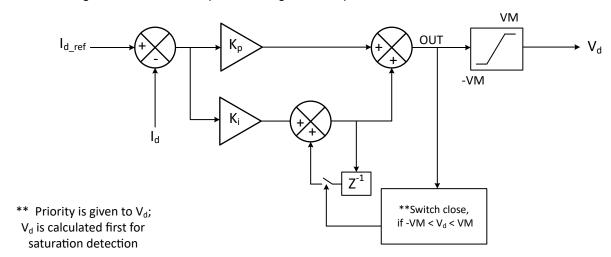

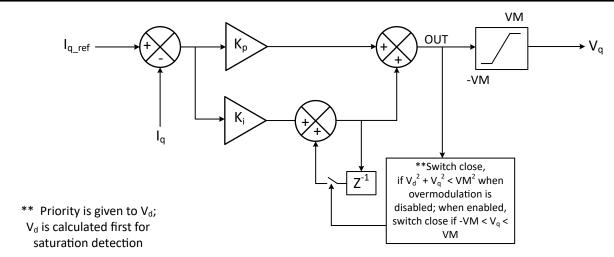

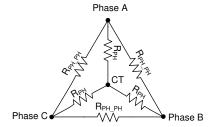

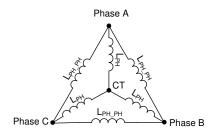

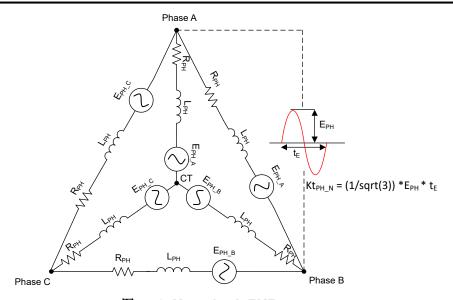

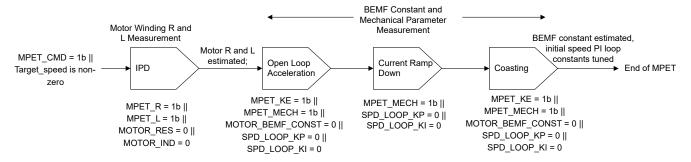

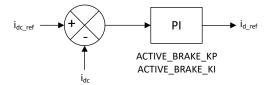

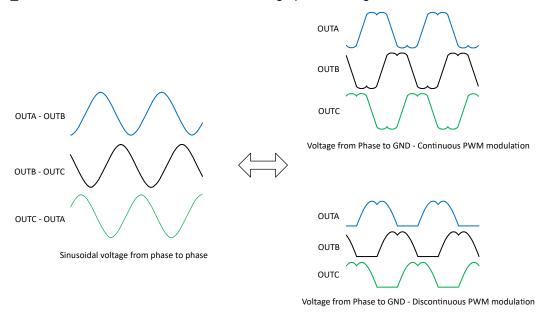

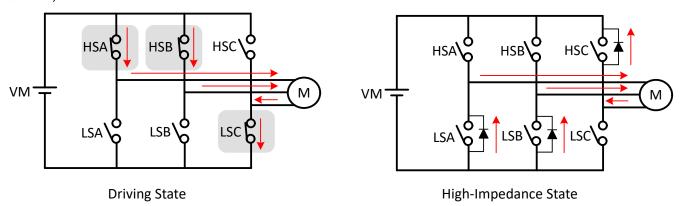

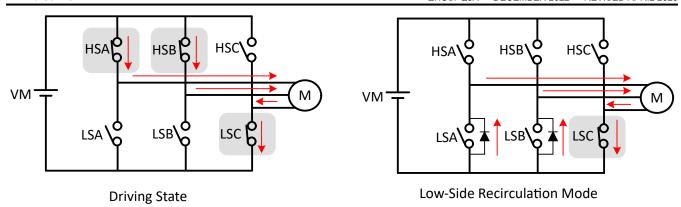

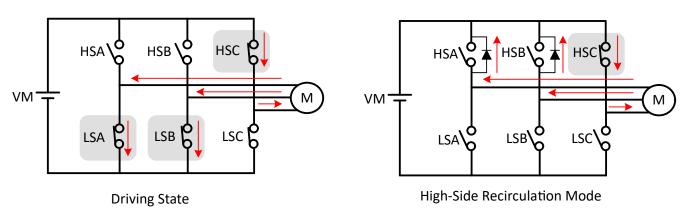

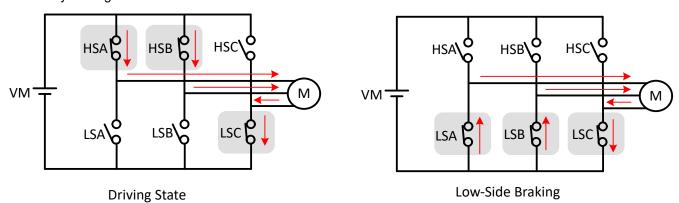

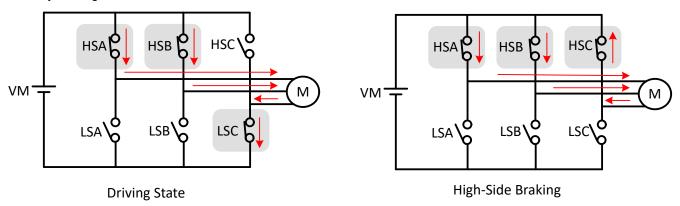

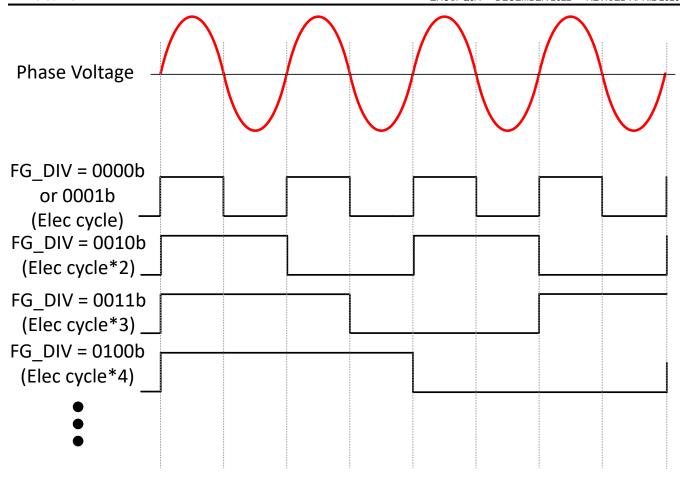

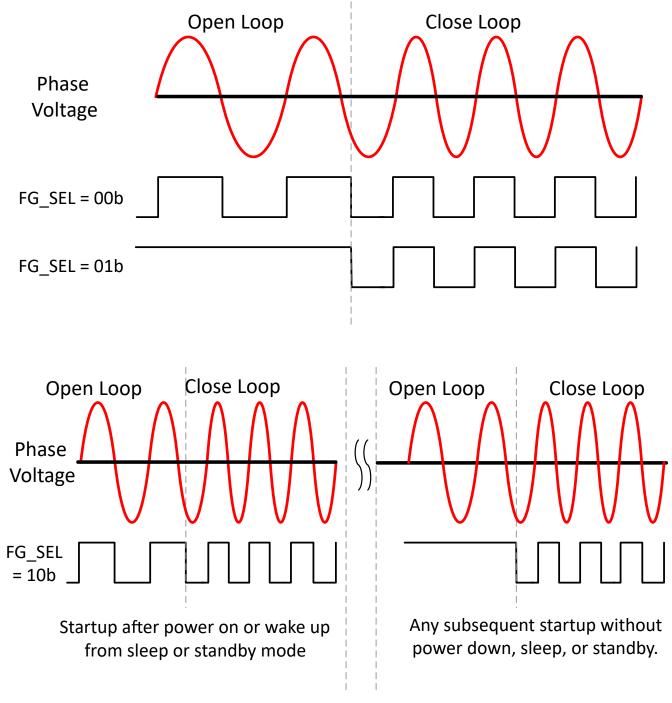

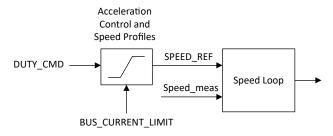

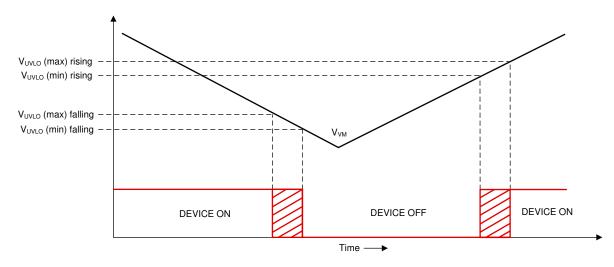

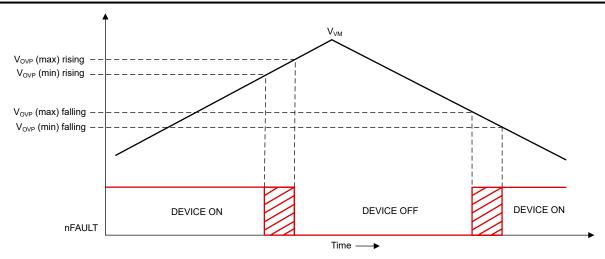

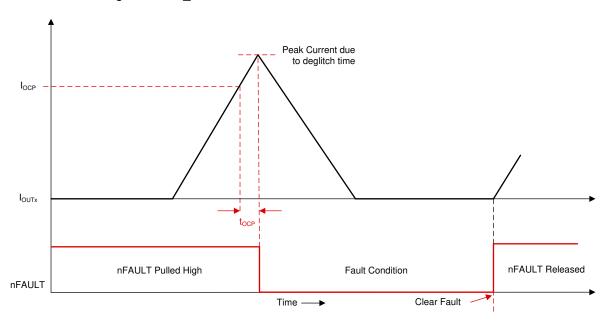

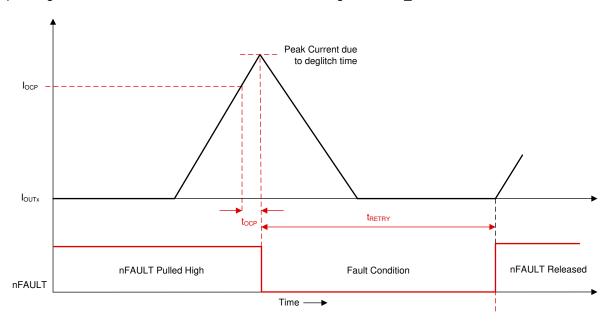

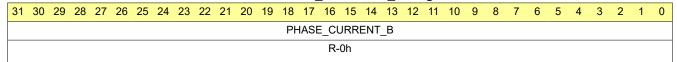

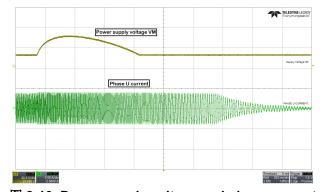

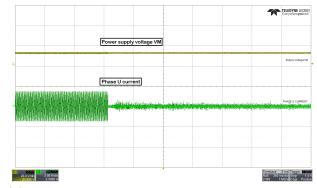

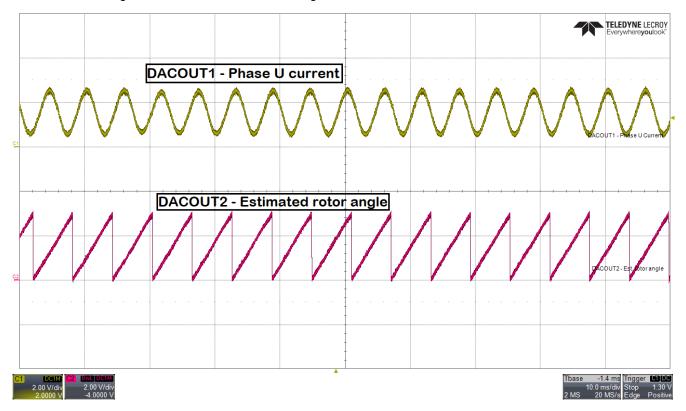

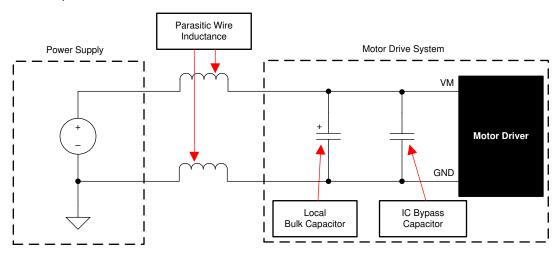

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> falling, BUCK_SEL = 11b                                                                                                                            | 4.1             | 4.2              | 4.36                       | V                    |