LP873220-Q1

ZHCSGT7A - SEPTEMBER 2017 - REVISED JUNE 2021

# LP873220-Q1 双路高电流降压转换器和双路线性稳压器

# 1 特性

Texas

INSTRUMENTS

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1:-40°C 至+125°C 环境工作 温度范围

- 输入电压: 2.8V 至 5.5V

- 两个高效降压直流/直流转换器:

- 输出电压: 0.7V 至 3.36V

- 最大输出电流为 2A

- 可编程输出电压压摆率范围:0.5mV/µs 至 10mV/µs

- 2MHz 开关频率

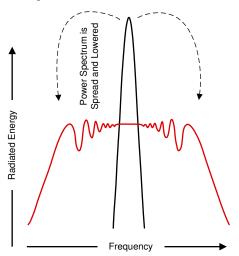

- 用于降低 EMI 的扩频模式和相位交错

- 两个线性稳压器:

- 输入电压: 2.5V 至 5.5V

- 输出电压: 0.8V 至 3.3V

- 最大输出电流为 300mA

- 可配置通用输出信号(GPO、GPO2)

- 具有可编程屏蔽的中断功能

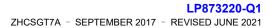

- 可编程电源正常信号 (PGOOD)

- 输出短路和过载保护

- 过热警告和保护

- 过压保护 (OVP) 和欠压锁定 (UVLO)

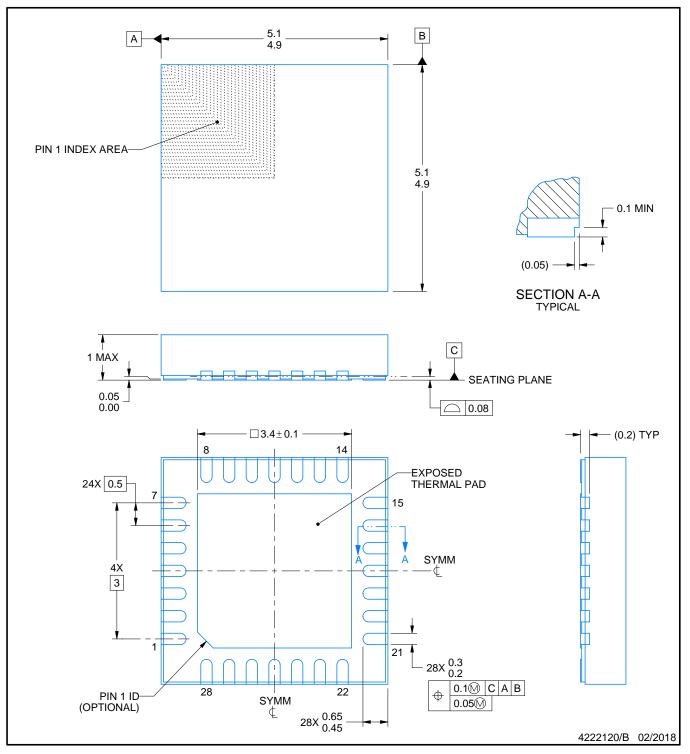

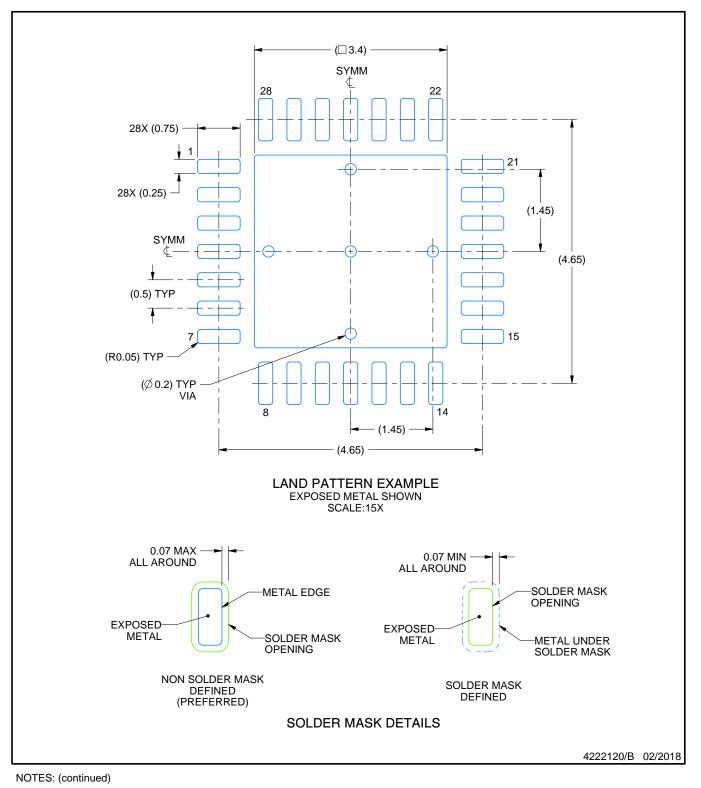

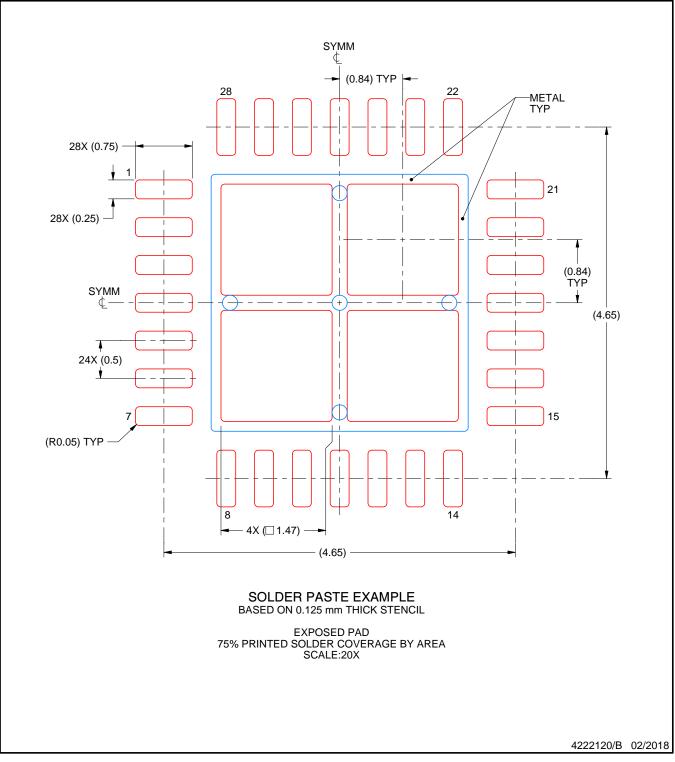

- 具有可湿性侧面的 28 引脚、5mm × 5mm VQFN 封 装

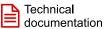

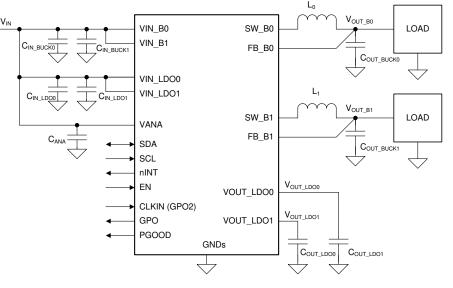

# 简化版原理图

# 2 应用

- 汽车音响主机和仪表组

- 汽车摄像头模块

- 环视系统 ECU

- 雷达系统 ECU

- 汽车显示屏

# 3 说明

LP873220-Q1 旨在满足汽车摄像头和雷达应用中新型 处理器和平台的电源管理要求。该器件具有两个降压直 流/直流转换器、两个线性稳压器以及两个通用数字输 出信号。该器件由 I<sup>2</sup>C 兼容串行接口和使能信号进行控 制。

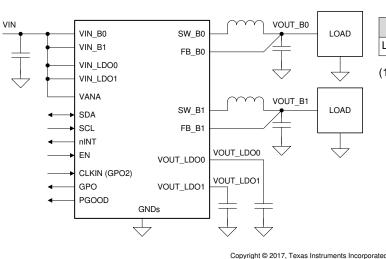

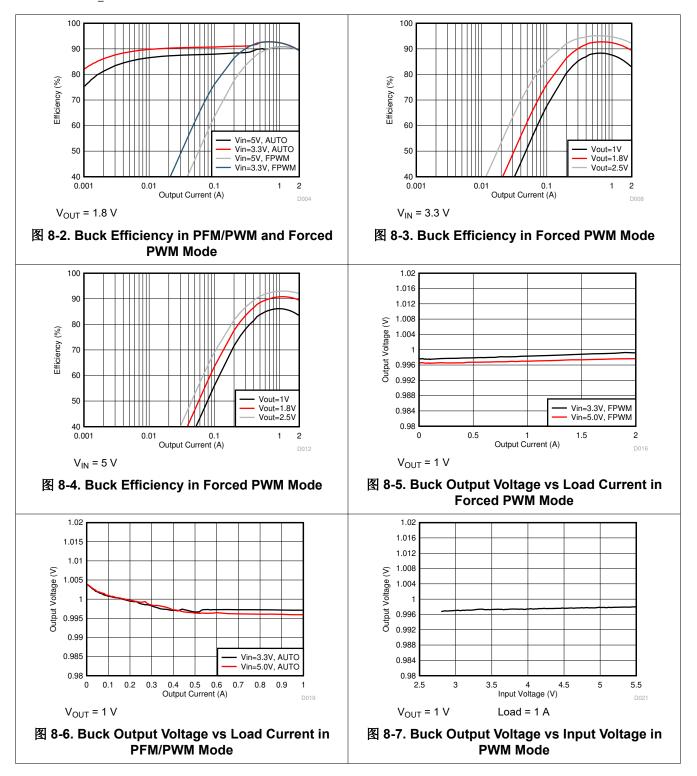

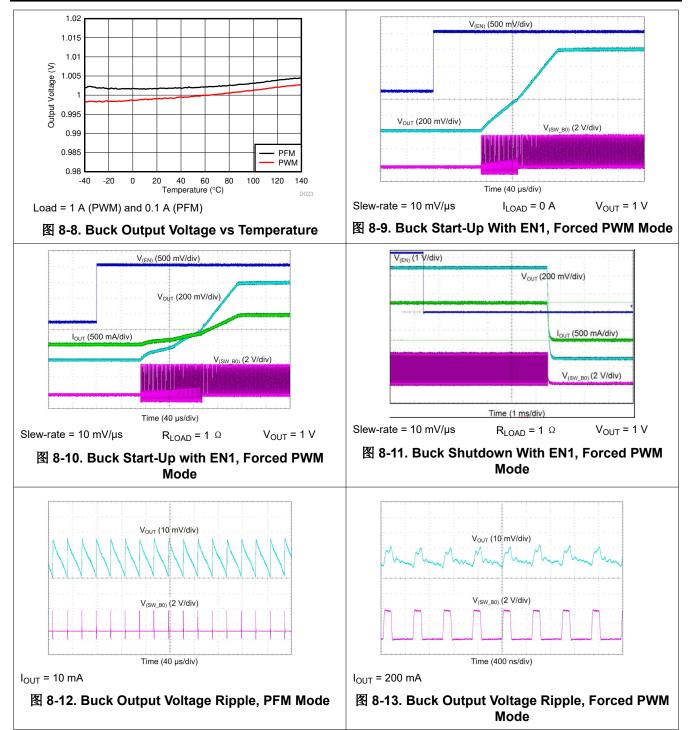

自动 PWM/PFM (AUTO 模式)运行,可在较宽输出 电流范围内提供高效率。LP873220-Q1 支持远程电压 感应,可补偿稳压器输出与负载点 (POL) 之间的 IR 压 降,从而提高输出电压的精度。此外,可以强制开关时 钟进入 PWM 模式以及将其与外部时钟同步,从而更大 限度地降低干扰。

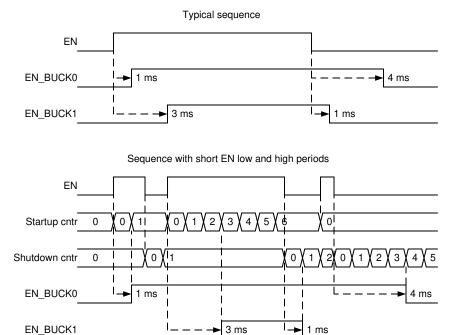

LP873220-Q1 器件还支持可编程启动、关断延迟与时 序控制(包括与使能信号同步的 GPO 信号)。在启动 和电压变化期间,器件会对输出转换率进行控制,从而 更大限度地减小输出电压过冲和浪涌电流。

器件信息<sup>(1)</sup>

| 器件型号        | 封装        | 封装尺寸(标称值)       |

|-------------|-----------|-----------------|

| LP873220-Q1 | VQFN (28) | 5.00mm × 5.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1) 录。

直流/直流效率与输出电流间的关系

# **Table of Contents**

| 1 | 特性                                                  | 1 |

|---|-----------------------------------------------------|---|

| 2 | 应用                                                  | 1 |

| 3 | 说明                                                  | 1 |

|   | Revision History                                    |   |

|   | Pin Configuration and Functions                     |   |

| 6 | Specifications                                      | 5 |

|   | 6.1 Absolute Maximum Ratings                        | 5 |

|   | 6.2 ESD Ratings                                     |   |

|   | 6.3 Recommended Operating Conditions                | 5 |

|   | 6.4 Thermal Information                             | 6 |

|   | 6.5 Electrical Characteristics                      | 6 |

|   | 6.6 I <sup>2</sup> C Serial Bus Timing Parameters 1 |   |

|   | 6.7 Typical Characteristics1                        | 4 |

| 7 | Detailed Description1                               | 5 |

|   | 7.1 Overview1                                       | 5 |

|   | 7.2 Functional Block Diagram1                       | 6 |

|   | 7.3 Feature Description1                            |   |

|   | 7.4 Device Functional Modes                         | 5 |

|   |                                                     |   |

| 7.5 Programming                                      | 36 |

|------------------------------------------------------|----|

| 7.6 Register Maps                                    |    |

| 8 Application and Implementation                     |    |

| 8.1 Application Information                          |    |

| 8.2 Typical Application                              |    |

| 9 Power Supply Recommendations                       |    |

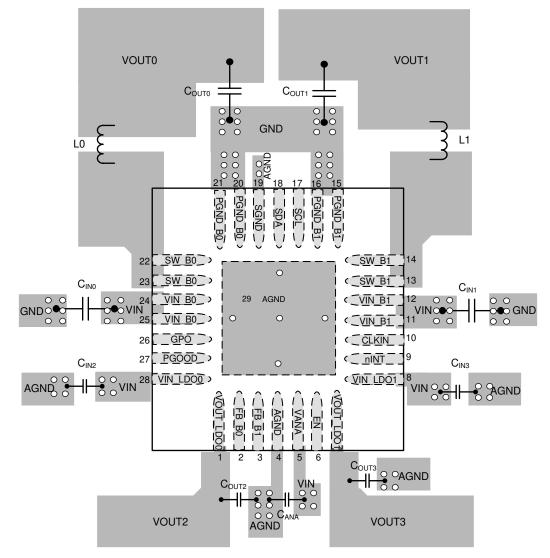

| 10 Layout                                            | 70 |

| 10.1 Layout Guidelines                               |    |

| 10.2 Layout Example                                  | 71 |

| 11 Device and Documentation Support                  | 72 |

| 11.1 Device Support                                  | 72 |

| 11.2 Receiving Notification of Documentation Updates | 72 |

| 11.3 支持资源                                            | 72 |

| 11.4 Trademarks                                      | 72 |

| 11.5 Electrostatic Discharge Caution                 | 72 |

| 11.6 Glossary                                        |    |

| 12 Mechanical, Packaging, and Orderable              |    |

| Information                                          | 72 |

|                                                      |    |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| Cł | Changes from Revision * (September 2017) to Revision A (June 2021) | Page |

|----|--------------------------------------------------------------------|------|

| •  | • 更新了整个文档中的表、图和交叉参考的编号格式                                           | 1    |

| •  | Updated the LDO Output Capacitor Selection section                 |      |

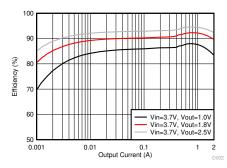

# **5** Pin Configuration and Functions

图 5-1. RHD Package 28-Pin VQFN With Thermal Pad Top View

#### 表 5-1. Pin Functions

| PIN<br>NUMBER NAME |           |       | DESCRIPTION                                                                                                                                                                 |  |

|--------------------|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    |           |       | DESCRIPTION                                                                                                                                                                 |  |

| 1                  | VOUT_LDO0 | P/O   | LDO0 output. If the LDO0 is not used, leave the pin floating.                                                                                                               |  |

| 2                  | FB_B0     | A     | out voltage feedback (positive) for Buck 0.                                                                                                                                 |  |

| 3                  | FB_B1     | A     | ut voltage feedback (positive) for Buck 1                                                                                                                                   |  |

| 4                  | AGND      | G     | nd.                                                                                                                                                                         |  |

| 5                  | VANA      | P/I   | ly voltage for analog and digital blocks. Must be connected to same node with VIN_Bx.                                                                                       |  |

| 6                  | EN        | D/I   | Programmable enable signal for regulators and GPOs. If the pin is not used, leave the pin floating.                                                                         |  |

| 7                  | VOUT_LDO1 | P/O   | LDO1 output. If LDO1 is not used, leave the pin floating.                                                                                                                   |  |

| 8                  | VIN_LDO1  | P/I   | Power input for LDO1. If LDO1 is not used, connect the pin to VANA.                                                                                                         |  |

| 9                  | nINT      | D/O   | pen-drain interrupt output. Active LOW. If the pin is not used, connect the pin to ground.                                                                                  |  |

| 10                 | CLKIN     | D/I/O | ternal clock input. Alternative function is general-purpose digital output (GPO2). If the pin is t used, leave the pin floating.                                            |  |

| 11, 12             | VIN_B1    | P/I   | Input for Buck 1. The separate power pins VIN_Bx are not connected together internally - VIN_Bx pins must be connected together in the application and be locally bypassed. |  |

| 13, 14             | SW_B1     | P/O   | Buck 1 switch node. If the Buck 1 is not used, leave the pin floating.                                                                                                      |  |

| 15, 16             | PGND_B1   | P/G   | Power ground for Buck 1.                                                                                                                                                    |  |

| 17                 | SCL       | D/I   | Serial interface clock input for I <sup>2</sup> C access. Connect a pullup resistor. If the I <sup>2</sup> C interface is not used, connect the pin to Ground.              |  |

| 18                 | SDA       | D/I/O | Serial interface data input and output for I <sup>2</sup> C access. Connect a pullup resistor. If the I <sup>2</sup> C interface is not used, connect the pin to Ground.    |  |

| 19                 | SGND      | G     | Ground.                                                                                                                                                                     |  |

| 20, 21             | PGND_B0   | P/G   | Power ground for Buck 0.                                                                                                                                                    |  |

| 22, 23             | SW_B0     | P/O   | Buck 0 switch node. If the Buck 0 is not used, leave the pin floating.                                                                                                      |  |

#### 表 5-1. Pin Functions (continued)

|                | PIN      | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                 |

|----------------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER         | NAME     |                     | DESCRIPTION                                                                                                                                                                 |

| 24, 25 VIN_B0  |          | P/I                 | Input for Buck 0. The separate power pins VIN_Bx are not connected together internally - VIN_Bx pins must be connected together in the application and be locally bypassed. |

| 26 GPO         |          | D/O                 | General-purpose digital output. If the pin is not used, leave the pin floating.                                                                                             |

| 27             | PGOOD D/ |                     | Power-good indication signal. If the pin is not used, leave the pin floating.                                                                                               |

| 28 VIN_LDO0    |          | P/I                 | Power input for LDO0. If the LDO0 is not used, connect the pin to VANA.                                                                                                     |

| Thermal<br>Pad | _        | _                   | Connect to PCB ground plane using multiple vias for good thermal performance.                                                                                               |

(1) A: Analog Pin, D: Digital Pin, G: Ground Pin, P: Power Pin, I: Input Pin, and O: Output Pin.

# **6** Specifications

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup> (2)

|                             |                                                               | MIN   | MAX                                    | UNIT |

|-----------------------------|---------------------------------------------------------------|-------|----------------------------------------|------|

| VIN_Bx, VANA                | Voltage on power connections (must use the same input supply) | - 0.3 | 6                                      | V    |

| VIN_LDOx                    | Voltage on power connections                                  | - 0.3 | 6                                      | V    |

| SW_Bx                       | Voltage on buck switch nodes                                  | - 0.3 | (VIN_Bx + 0.3 V) with 6-V<br>maximum   | V    |

| FB_Bx                       | Voltage on buck voltage sense nodes                           | - 0.3 | (VANA + 0.3 V) with 6-V<br>maximum     | V    |

| VOUT_LDOx                   | Voltage on LDO output                                         | -0.3  | (VIN_LDOx + 0.3 V) with 6-V<br>maximum | V    |

| SDA, SCL, nINT, EN          | Voltage on logic pins (input or output pins)                  | - 0.3 | 6                                      | V    |

| PGOOD, GPO, CLKIN<br>(GPO2) | Voltage on logic pins (input or output pins)                  | - 0.3 | (VANA + 0.3 V) with 6-V<br>maximum     | V    |

| T <sub>J-MAX</sub>          | Junction temperature                                          | -40   | 150                                    |      |

| T <sub>stg</sub>            | Storage temperature                                           | - 65  | 150                                    | °C   |

| Maximum lead temperat       | ture (soldering, 10 seconds)                                  |       | 260                                    |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under # 6.3. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground.

# 6.2 ESD Ratings

|                    |                         |                                                         |                                           | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                           | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC                     | All pins                                  | ±500  | v    |

| - (250)            |                         | Q100-011                                                | Corner pins (1, 7, 8, 14, 15, 21, 22, 28) | ±750  | -    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                  |                                                                                                             | MIN | MAX                        | UNIT |

|------------------|-------------------------------------------------------------------------------------------------------------|-----|----------------------------|------|

| INPUT VOLTAGE    |                                                                                                             |     |                            |      |

| VIN_Bx, VANA     | Voltage on power connections (must use the same input supply)                                               | 2.8 | 5.5                        | V    |

| VIN_LDOx         | Voltage on LDO inputs                                                                                       | 2.5 | 5.5                        | V    |

| EN, nINT         | Voltage on logic pins (input or output pins)                                                                | 0   | 5.5                        | V    |

| CLKIN            | Voltage on logic pins (input pin)                                                                           | 0   | VANA with 5.5-V<br>maximum | V    |

| PGOOD, GPO, GPO2 | Voltage on logic pins (output pins)                                                                         | 0   | VANA                       | V    |

|                  | Voltage on I2C interface, Standard (100 kHz), Fast (400 kHz), Fast+ (1 MHz), and High-Speed (3.4 MHz) Modes | 0   | 1.95                       | V    |

| SCL, SDA         | Voltage on I2C interface, Standard (100 kHz), Fast (400 kHz), and Fast+ (1 MHz) Modes                       | 0   | VANA with 3.6-V<br>maximum | V    |

| TEMPERATURE      |                                                                                                             |     |                            |      |

| TJ               | Junction temperature                                                                                        | -40 | 140                        | °C   |

| T <sub>A</sub>   | Ambient temperature                                                                                         | -40 | 125                        | °C   |

# 6.4 Thermal Information

|                      |                                              | LP873220-Q1 |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHD (VQFN)  | UNIT |

|                      |                                              | 28 PINS     |      |

| R <sub>θ JA</sub>    | Junction-to-ambient thermal resistance       | 36.7        | °C/W |

| R <sub>0</sub> JCtop | Junction-to-case (top) thermal resistance    | 26.6        | °C/W |

| R <sub>θ JB</sub>    | Junction-to-board thermal resistance         | 8.9         | °C/W |

| ΨJT                  | Junction-to-top characterization parameter   | 0.4         | °C/W |

| ψ <sub>JB</sub>      | Junction-to-board characterization parameter | 8.8         | °C/W |

| R <sub>0</sub> JCbot | Junction-to-case (bottom) thermal resistance | 2.2         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

# **6.5 Electrical Characteristics**

Limits apply over the junction temperature range  $-40^{\circ}C \leq T_J \leq +140^{\circ}C$ , specified V<sub>VANA</sub>, V<sub>VIN\_Bx</sub>, V<sub>VIN\_LDOx</sub>, V<sub>VOUT\_Bx</sub>, V<sub>VOUT\_LDOx</sub> and I<sub>OUT</sub> range, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, V<sub>VANA</sub> = V<sub>VIN\_Bx</sub> = V<sub>VIN\_LDOx</sub> = 3.7 V, and V<sub>OUT</sub> = 1 V, unless otherwise noted<sup>(1) (2)</sup>.

|                                                | PARAMETER                                                 | TEST CONDITIONS                                                                                                                                                                                      | MIN   | TYP  | MAX              | UNIT |

|------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------------------|------|

| EXTERNAL C                                     | COMPONENTS                                                |                                                                                                                                                                                                      |       |      |                  |      |

| C <sub>IN_BUCK</sub>                           | Input filtering<br>capacitance for buck<br>regulators     | Effective capacitance, connected from VIN_Bx to PGND_Bx                                                                                                                                              | 1.9   | 10   |                  | μF   |

| C <sub>OUT_BUCK</sub>                          | Output filtering<br>capacitance for buck<br>regulators    | Effective capacitance                                                                                                                                                                                | 10    | 22   | 500              | μF   |

| C <sub>POL_BUCK</sub>                          | Point-of-load (POL)<br>capacitance for buck<br>regulators | Optional POL capacitance                                                                                                                                                                             |       | 22   |                  | μF   |

| C <sub>OUT-</sub><br>TOTAL_BUCK                | Buck output capacitance, total (local and POL)            | Total output capacitance                                                                                                                                                                             |       |      | 500              | μF   |

| C <sub>IN_LDO</sub>                            | Input filtering<br>capacitance for LDO<br>regulators      | $\begin{array}{l} \mbox{Effective capacitance, connected from} \\ \mbox{VIN\_LDOx to AGND. } C_{\rm IN\_LDO} \mbox{ must be at least} \\ \mbox{two times larger than } C_{\rm OUT\_LDO} \end{array}$ | 0.6   | 2.2  |                  | μF   |

| C <sub>OUT_LDO</sub>                           | Output filtering<br>capacitance for LDO<br>regulators     | Effective capacitance                                                                                                                                                                                | 0.4   | 1    | 2.7              | μF   |

| ESR <sub>C</sub>                               | Input and output capacitor ESR                            | [1-10] MHz                                                                                                                                                                                           |       | 2    | 10               | mΩ   |

| L                                              | Inductor                                                  | Inductance of the inductor                                                                                                                                                                           |       | 0.47 |                  | μH   |

| -                                              | inductor                                                  |                                                                                                                                                                                                      | - 30% |      | 30%              | P    |

| DCRL                                           | Inductor DCR                                              |                                                                                                                                                                                                      |       | 25   |                  | mΩ   |

| BUCK REGU                                      | LATORS                                                    |                                                                                                                                                                                                      |       |      |                  |      |

| V <sub>(VIN_Bx)</sub> ,<br>V <sub>(VANA)</sub> | Input voltage range                                       | VIN_Bx and VANA pins must be connected to the same supply line                                                                                                                                       | 2.8   | 3.7  | 5.5              | V    |

|                                                |                                                           | Programmable voltage range                                                                                                                                                                           | 0.7   | 1    | 3.36             | V    |

| M                                              |                                                           | Step size, 0.7 V $\leq$ V <sub>OUT</sub> < 0.73 V                                                                                                                                                    |       | 10   |                  |      |

| V <sub>OUT_Bx</sub>                            | Output voltage                                            | Step size, 0.73 V $\leq$ V <sub>OUT</sub> < 1.4 V                                                                                                                                                    |       | 5    |                  | mV   |

|                                                |                                                           | Step size, 1.4 V $\leqslant$ V_{OUT} $\leqslant$ 3.36 V                                                                                                                                              |       | 20   |                  |      |

| I <sub>OUT_Bx</sub>                            | Output current                                            | Output current                                                                                                                                                                                       |       |      | 2 <sup>(3)</sup> | А    |

|                                                | Input and Output voltage difference                       | Minimum voltage between $V_{(VIN\_Bx)}$ and $V_{OUT}$ to fulfill the electrical characteristics                                                                                                      | 0.8   |      |                  | V    |

Limits apply over the junction temperature range  $-40^{\circ}C \leq T_{J} \leq +140^{\circ}C$ , specified V<sub>VANA</sub>, V<sub>VIN\_Bx</sub>, V<sub>VIN\_LDOx</sub>, V<sub>VOUT\_Bx</sub>, V<sub>VOUT\_LDOx</sub> and I<sub>OUT</sub> range, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, V<sub>VANA</sub> = V<sub>VIN\_Bx</sub> = V<sub>VIN\_LDOx</sub> = 3.7 V, and V<sub>OUT</sub> = 1 V, unless otherwise noted<sup>(1) (2)</sup>.

| Р                          | PARAMETER                                                                               | TEST CONDITIONS                                                                                                                            | MIN   | TYP   | MAX           | UNIT              |

|----------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------|-------------------|

|                            |                                                                                         | Force PWM mode, V <sub>OUT</sub> < 1 V                                                                                                     | - 20  |       | 20            | mV                |

|                            | DC output voltage                                                                       | Force PWM mode, $V_{OUT} \ge 1 V$                                                                                                          | - 2%  |       | 2%            |                   |

| V <sub>OUT_Bx_DC</sub>     | accuracy, includes<br><sub>DC</sub> voltage reference, DC<br>load and line regulations, | PFM mode, V <sub>OUT</sub> < 1 V, the average output voltage level is increased by max. 20 mV                                              | - 20  |       | 40            | mV                |

|                            | process and temperature                                                                 | PFM mode, $V_{OUT} \ge 1 \text{ V}$ , the average output voltage level is increased by max. 20 mV                                          | - 2%  |       | 2% + 20<br>mV |                   |

|                            | Disala serita as                                                                        | PWM mode                                                                                                                                   |       | 10    |               |                   |

|                            | Ripple voltage                                                                          | PFM mode, I <sub>OUT</sub> = 10 mA                                                                                                         |       | 25    |               | mV <sub>p-p</sub> |

| DC <sub>LNR</sub>          | DC line regulation                                                                      | I <sub>OUT</sub> = 1 A                                                                                                                     |       | ±0.05 |               | %/V               |

| DC <sub>LDR</sub>          | DC load regulation in PWM mode                                                          | $V_{OUT_Bx}$ = 1 V, I <sub>OUT</sub> from 0 to I <sub>OUT(max)</sub>                                                                       |       | 0.3%  |               |                   |

| T <sub>LDSR</sub>          | Transient load step response                                                            | $I_{OUT}$ = 0.1 A to 2 A, $T_R$ = $T_F$ = 400 ns, PWM mode                                                                                 |       | ±55   |               | mV                |

| T <sub>LNSR</sub>          | Transient line response                                                                 | $V_{(VIN\_Bx)}$ stepping 3 V $\leftrightarrow$ 3.5 V, T <sub>R</sub> = T <sub>F</sub> = 10 µs,<br>I <sub>OUT</sub> = I <sub>OUT(max)</sub> |       | ±10   |               | mV                |

|                            |                                                                                         | Programmable range                                                                                                                         | 1.5   |       | 3             | ^                 |

|                            | Forward current limit per<br>phase (peak for every<br>switching cycle)                  | Step size                                                                                                                                  |       | 0.5   |               | A                 |

| LIM FWD                    |                                                                                         | Accuracy, $V_{(VIN_Bx)} \ge 3 \text{ V}$ , $I_{LIM} = 3 \text{ A}$                                                                         | - 5%  | 7.5%  | 20%           |                   |

|                            |                                                                                         | Accuracy, 2.8 V $\leq$ V <sub>(VIN_Bx)</sub> < 3 V, I <sub>LIM</sub> = 3 A                                                                 | - 20% | 7.5%  | 20%           |                   |

| ILIM NEG                   | Negative current limit per phase                                                        |                                                                                                                                            | 1.6   | 2.0   | 3.0           | А                 |

| R <sub>DS(ON)</sub> HS FET | On-resistance, high-side<br>FET                                                         | Each phase, between VIN_Bx and SW_Bx pins (I = 1 A)                                                                                        |       | 50    | 110           | mΩ                |

| R <sub>DS(ON)</sub> LS FET | On-resistance, low-side<br>FET                                                          | Each phase, between SW_Bx and PGND_Bx pins (I = 1 A)                                                                                       |       | 45    | 90            | mΩ                |

| f <sub>sw</sub>            | Switching frequency                                                                     | PWM mode                                                                                                                                   | 1.8   | 2     | 2.2           | MHz               |

|                            | Start-up time (soft start)                                                              | From ENx to $V_{OUT_Bx} = 0.35 V$ (slew-rate control begins)                                                                               |       | 120   |               | μs                |

|                            |                                                                                         | SLEW_RATEx[2:0] = 010, C <sub>OUT-TOTAL_BUCK</sub> < 80 μF                                                                                 |       | 10    |               |                   |

|                            |                                                                                         | SLEW_RATEx[2:0] = 011, C <sub>OUT-TOTAL_BUCK</sub> < 130 μF                                                                                |       | 7.5   |               |                   |

|                            | Output voltage slew-                                                                    | SLEW_RATEx[2:0] = 100, C <sub>OUT-TOTAL_BUCK</sub> < 250 μF                                                                                | - 15% | 3.8   | 15%           | mV/µs             |

|                            | rate <sup>(4)</sup>                                                                     | SLEW_RATEx[2:0] = 101, C <sub>OUT-TOTAL_BUCK</sub><br>< 500 μF                                                                             | - 15% | 1.9   | 1070          | inv/µc            |

|                            |                                                                                         | SLEW_RATEx[2:0] = 110, C <sub>OUT-TOTAL_BUCK</sub><br>< 500 μF                                                                             |       | 0.94  |               |                   |

|                            |                                                                                         | SLEW_RATEx[2:0] = 111, C <sub>OUT-TOTAL_BUCK</sub><br>< 500 μF                                                                             |       | 0.47  |               |                   |

| I <sub>PFM-PWM</sub>       | PFM-to-PWM - current threshold <sup>(5)</sup>                                           |                                                                                                                                            |       | 550   |               | mA                |

| I <sub>PWM-PFM</sub>       | PWM-to-PFM - current threshold <sup>(5)</sup>                                           |                                                                                                                                            |       | 290   |               | mA                |

| R <sub>DIS_Bx</sub>        | Output pulldown resistance                                                              | Regulator disabled                                                                                                                         | 150   | 250   | 350           | Ω                 |

Limits apply over the junction temperature range  $-40^{\circ}C \leq T_{J} \leq +140^{\circ}C$ , specified V<sub>VANA</sub>, V<sub>VIN\_Bx</sub>, V<sub>VIN\_LDOx</sub>, V<sub>VOUT\_Bx</sub>, V<sub>VOUT\_LDOx</sub> and I<sub>OUT</sub> range, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, V<sub>VANA</sub> = V<sub>VIN\_Bx</sub> = V<sub>VIN\_LDOx</sub> = 3.7 V, and V<sub>OUT</sub> = 1 V, unless otherwise noted<sup>(1) (2)</sup>.

| F                        | PARAMETER                                                                                         | TEST CONDITIONS                                                                                                                              | MIN  | TYP      | MAX  | UNIT                 |

|--------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|----------------------|

|                          |                                                                                                   | $V_{(VIN\_Bx)}$ and $V_{(VANA)}$ fixed 3.7 V                                                                                                 |      |          |      |                      |

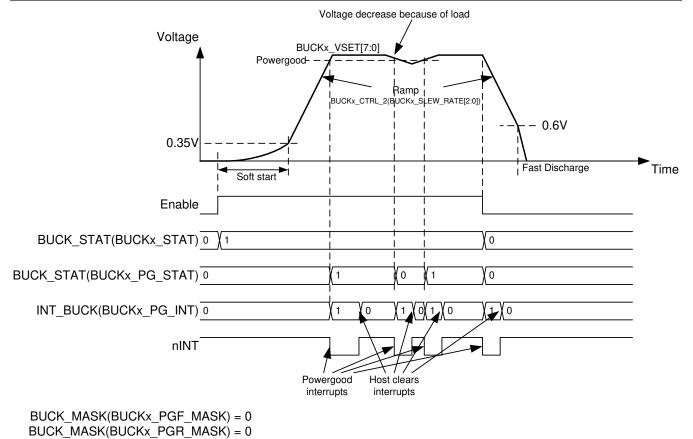

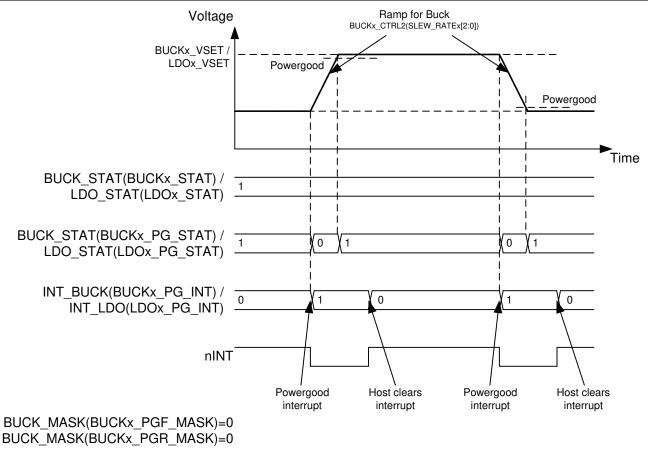

|                          | Output voltage<br>monitoring for PGOOD                                                            | Overvoltage threshold (compared to DC output voltage level, V <sub>VOUT_Bx_DC</sub> )                                                        | 39   | 50       | 64   | mV                   |

|                          | pin and for power-good<br>Interrupt                                                               | Undervoltage threshold (compared to DC output voltage level, V <sub>VOUT_Bx_DC</sub> )                                                       | - 53 | - 40     | - 29 | mv                   |

|                          |                                                                                                   | Deglitch time during operation and after voltage change                                                                                      | 4    |          | 15   | μs                   |

|                          | Gating time for PGOOD<br>signal after regulator<br>enable or voltage change                       | PGOOD_MODE = 0                                                                                                                               |      | 800      |      | μs                   |

| LDO REGULA               | TORS                                                                                              | · · · · · ·                                                                                                                                  |      |          | 1    |                      |

| V <sub>IN_LDOx</sub>     | Input voltage range for LDO power inputs                                                          | $V_{\text{IN\_LDOx}}$ can be higher or lower than $V_{(\text{VANA})}$                                                                        | 2.5  | 3.7      | 5.5  | V                    |

| \ <i>\</i>               | Outerstand                                                                                        | Programmable voltage range                                                                                                                   | 0.8  |          | 3.3  |                      |

| V <sub>OUT_LDOx</sub>    | Output voltage                                                                                    | Step size                                                                                                                                    |      | 0.1      |      | V                    |

| I <sub>OUT_LDOx</sub>    | Output current                                                                                    |                                                                                                                                              |      |          | 300  | mA                   |

|                          | Dropout voltage                                                                                   | $V_{(VIN\_LDOx)} - V_{(VOUT\_LDOx)}, I_{OUT} = I_{OUT(max)},$<br>Programmed output voltage is higher than<br>$V_{(VIN\_LDOx)}$               |      |          | 200  | mV                   |

|                          | DC output voltage                                                                                 | V <sub>OUT</sub> < 1 V                                                                                                                       | - 20 |          | 20   | mV                   |

| V <sub>OUT_LDO_DC</sub>  | accuracy, includes<br>voltage reference, DC<br>load and line regulations,<br>process, temperature | $V_{OUT} \ge 1 V$                                                                                                                            | - 2% |          | 2%   |                      |

| DC <sub>LNR</sub>        | DC line regulation                                                                                | I <sub>OUT</sub> = 1 mA                                                                                                                      |      | 0.1      |      | %/V                  |

| DC <sub>LDR</sub>        | DC load regulation                                                                                | I <sub>OUT</sub> = 1 mA to I <sub>OUT(max)</sub>                                                                                             |      | 0.8%     |      |                      |

| T <sub>LDSR</sub>        | Transient load step response                                                                      | $I_{OUT}$ = 1 mA to 300 mA, $T_R$ = $T_F$ = 1 µs                                                                                             |      | - 50/+40 |      | mV                   |

| T <sub>LNSR</sub>        | Transient line response                                                                           | $V_{(VIN\_LDOx)}$ stepping 3 V $\leftrightarrow$ 3.5 V, T <sub>R</sub> = T <sub>F</sub> = 10<br>µs, I <sub>OUT</sub> = I <sub>OUT(max)</sub> |      | ±7       |      | mV                   |

| PSRR                     | Power supply ripple rejection                                                                     | $f = 10 \text{ kHz}, \text{ I}_{\text{OUT}} = \text{I}_{\text{OUT}(\text{max})}$                                                             |      | 53       |      | dB                   |

|                          | Noise                                                                                             | 10 Hz < F < 100 kHz, I <sub>OUT</sub> = I <sub>OUT(max)</sub>                                                                                |      | 82       |      | $\mu V_{\text{rms}}$ |

| I <sub>SHORT(LDOx)</sub> | LDO current limit                                                                                 | V <sub>OUT</sub> = 0 V                                                                                                                       | 400  | 500      | 600  | mA                   |

|                          | Start-up time                                                                                     | From enable to valid output voltage                                                                                                          |      | 300      |      | μs                   |

|                          | Slew rate during start-up                                                                         |                                                                                                                                              |      | 15       |      | mV/μs                |

| R <sub>DIS_LDOx</sub>    | Output pulldown resistance                                                                        | Regulator disabled                                                                                                                           | 150  | 250      | 350  | Ω                    |

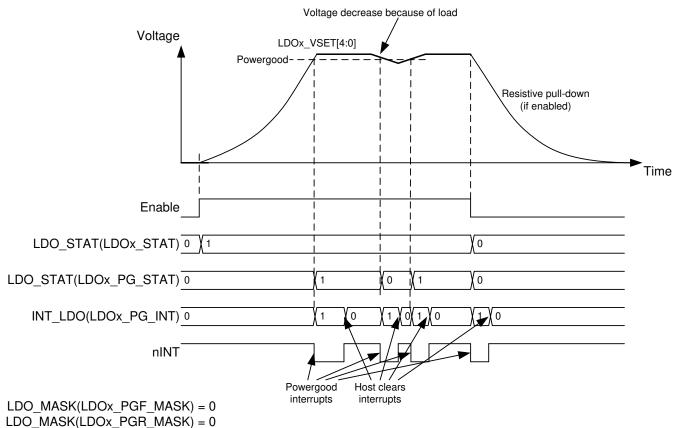

|                          |                                                                                                   | Overvoltage monitoring, voltage rising<br>(compared to DC output voltage level,<br>V <sub>OUT_LDO_DC</sub> )                                 | 106% | 108%     | 110% |                      |

|                          | Output voltage                                                                                    | Overvoltage monitoring, hysteresis                                                                                                           | 3%   | 3.5%     | 4%   |                      |

|                          | monitoring for PGOOD<br>pin and for power-good<br>interrupt                                       | Undervoltage monitoring, voltage falling<br>(compared to DC output voltage level,<br>V <sub>OUT_LDO_DC</sub> )                               | 90%  | 92%      | 94%  |                      |

|                          |                                                                                                   | Undervoltage monitoring, hysteresis                                                                                                          | 3%   | 3.5%     | 4%   |                      |

|                          |                                                                                                   | Deglitch time during operation and after voltage change                                                                                      | 4    |          | 15   | μs                   |

Limits apply over the junction temperature range  $-40^{\circ}C \leq T_{J} \leq +140^{\circ}C$ , specified V<sub>VANA</sub>, V<sub>VIN\_Bx</sub>, V<sub>VIN\_LDOx</sub>, V<sub>VOUT\_Bx</sub>, V<sub>VOUT\_LDOx</sub> and I<sub>OUT</sub> range, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, V<sub>VANA</sub> = V<sub>VIN\_Bx</sub> = V<sub>VIN\_LDOx</sub> = 3.7 V, and V<sub>OUT</sub> = 1 V, unless otherwise noted<sup>(1) (2)</sup>.

|                      | PARAMETER                                                                                                                            | TEST CONDITIONS                                                   | MIN   | TYP  | MAX   | UNIT    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|------|-------|---------|

|                      | Gating time for PGOOD<br>signal after regulator<br>enable or voltage change                                                          | PGOOD_MODE = 0                                                    |       | 800  |       | μs      |

| EXTERNAL (           | CLOCK AND PLL                                                                                                                        |                                                                   |       |      |       |         |

|                      |                                                                                                                                      | Nominal frequency                                                 | 1     | 24   | 24    | N 41 1- |

| f <sub>EXT_CLK</sub> | External input clock <sup>(6)</sup>                                                                                                  | Nominal frequency step size                                       |       | 1    |       | MHz     |

|                      |                                                                                                                                      | Required accuracy from nominal frequency                          | - 30% |      | 10%   |         |

|                      | External clock detection                                                                                                             | Delay for missing clock detection                                 |       |      | 1.8   |         |

|                      |                                                                                                                                      | Delay and debounce for clock detection                            |       |      | 20    | μs      |

|                      | Clock change delay<br>(internal to external)                                                                                         | Delay from valid clock detection to use of external clock         |       | 600  |       | μs      |

|                      | PLL output clock jitter                                                                                                              | Cycle to cycle                                                    |       | 300  |       | ps, p-p |

| PROTECTIO            | N FUNCTIONS                                                                                                                          |                                                                   |       |      |       |         |

|                      |                                                                                                                                      | Temperature rising, TDIE_WARN_LEVEL = 0                           | 115   | 125  | 135   |         |

|                      | Thermal warning                                                                                                                      | Temperature rising, TDIE_WARN_LEVEL = 1                           | 127   | 137  | 147   | °C      |

|                      |                                                                                                                                      | Hysteresis                                                        |       | 20   |       |         |

|                      | Thermal shutdown                                                                                                                     | Temperature rising                                                | 140   | 150  | 160   | °C      |

|                      | Thermal shakeown                                                                                                                     | Hysteresis                                                        |       | 20   |       | 0       |

| VANA <sub>ovp</sub>  | VANA overvoltage                                                                                                                     | Voltage rising                                                    | 5.6   | 5.8  | 6.1   | V       |

|                      |                                                                                                                                      | Voltage falling                                                   | 5.45  | 5.73 | 5.96  |         |

|                      |                                                                                                                                      | Hysteresis                                                        | 40    |      |       | mV      |

| VANA <sub>UVLO</sub> | VANA undervoltage<br>lockout                                                                                                         | Voltage rising                                                    | 2.51  | 2.63 | 2.75  | V       |

|                      |                                                                                                                                      | Voltage falling                                                   | 2.5   | 2.6  | 2.7   |         |

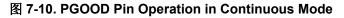

|                      | Buck short-circuit detection                                                                                                         | Threshold                                                         | 280   | 360  | 440   | mV      |

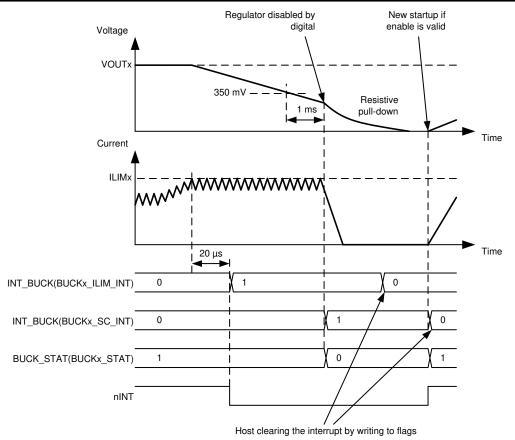

|                      | LDO short-circuit detection                                                                                                          | Threshold                                                         | 190   | 300  | 450   | mV      |

| LOAD CURR            | ENT MEASUREMENT FOR                                                                                                                  | BUCK REGULATORS                                                   |       |      |       |         |

|                      | Current measurement range                                                                                                            | Maximum code                                                      |       |      | 10.22 | А       |

|                      | Resolution                                                                                                                           | LSB                                                               |       | 20   |       | mA      |

|                      | Measurement accuracy                                                                                                                 | I <sub>OUT</sub> > 1 A                                            |       | <10% |       |         |

|                      | Measurement time                                                                                                                     | PFM mode (automatically changing to PWM mode for the measurement) |       | 45   |       | μs      |

|                      |                                                                                                                                      | PWM mode                                                          |       | 4    |       |         |

| CURRENT C            | ONSUMPTION                                                                                                                           |                                                                   |       |      |       |         |

|                      | Standby current consumption, regulators disabled                                                                                     |                                                                   |       | 9    |       | μΑ      |

|                      | Active current<br>consumption, one buck<br>regulator enabled in auto<br>mode, internal RC<br>oscillator, PGOOD<br>monitoring enabled | I <sub>OUT_Bx</sub> = 0 mA, not switching                         |       | 58   |       | μA      |

Limits apply over the junction temperature range  $-40^{\circ}C \leq T_{J} \leq +140^{\circ}C$ , specified V<sub>VANA</sub>, V<sub>VIN\_Bx</sub>, V<sub>VIN\_LDOx</sub>, V<sub>VOUT\_Bx</sub>, V<sub>VOUT\_LDOx</sub> and I<sub>OUT</sub> range, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, V<sub>VANA</sub> = V<sub>VIN\_Bx</sub> = V<sub>VIN\_LDOx</sub> = 3.7 V, and V<sub>OUT</sub> = 1 V, unless otherwise noted<sup>(1) (2)</sup>.

|                  | PARAMETER                                                                                                                             | TEST CONDITIONS                                                           | MIN                        | TYP | MAX               | UNIT |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------|-----|-------------------|------|

|                  | Active current<br>consumption, two buck<br>regulators enabled in<br>auto mode, internal RC<br>oscillator, PGOOD<br>monitoring enabled | I <sub>OUT_Bx</sub> = 0 mA, not switching                                 |                            | 100 |                   | μA   |

|                  | Active current<br>consumption during<br>PWM operation, one<br>buck regulator enabled                                                  | I <sub>OUT_Bx</sub> = 0 mA                                                |                            | 15  |                   | mA   |

|                  | Active current<br>consumption during<br>PWM operation, two<br>buck regulators enabled                                                 | I <sub>OUT_Bx</sub> = 0 mA                                                |                            | 30  |                   | mA   |

|                  | LDO regulator enabled                                                                                                                 | Additional current consumption per LDO,<br>I <sub>OUT_LDOx</sub> = 0 mA   |                            | 86  |                   | μA   |

|                  | PLL and clock detector<br>current consumption                                                                                         | f <sub>EXT_CLK</sub> = 1 MHz, Additional current consumption when enabled |                            | 2   |                   | mA   |

| DIGITAL IN       | NPUT SIGNALS EN, SCL, SDA                                                                                                             | , CLKIN                                                                   |                            |     |                   |      |

| V <sub>IL</sub>  | Input low level                                                                                                                       |                                                                           |                            |     | 0.4               | V    |

| V <sub>IH</sub>  | Input high level                                                                                                                      |                                                                           | 1.2                        |     |                   | v    |

| V <sub>HYS</sub> | Hysteresis of Schmitt<br>Trigger inputs                                                                                               |                                                                           | 10                         | 80  | 200               | mV   |

|                  | EN/CLKIN pulldown<br>resistance                                                                                                       | EN_PD/CLKIN_PD = 1                                                        |                            | 500 |                   | kΩ   |

| DIGITAL O        | UTPUT SIGNALS nINT, SDA                                                                                                               |                                                                           |                            |     |                   |      |

| V <sub>OL</sub>  | Output low level                                                                                                                      | nINT: I <sub>SOURCE</sub> = 2 mA                                          |                            |     | 0.4               | V    |

| ♥ OL             |                                                                                                                                       | SDA: I <sub>SOURCE</sub> = 20 mA                                          |                            |     | 0.4               | V    |

| R <sub>P</sub>   | External pullup resistor for nINT                                                                                                     | To VIO Supply                                                             |                            | 10  |                   | kΩ   |

| DIGITAL O        | UTPUT SIGNALS PGOOD, GP                                                                                                               | PO, GPO2                                                                  |                            |     |                   |      |

| V <sub>OL</sub>  | Output low level                                                                                                                      | I <sub>SOURCE</sub> = 2 mA                                                |                            |     | 0.4               | V    |

| V <sub>OH</sub>  | Output high level, configured to push-pull                                                                                            | I <sub>SINK</sub> = 2 mA                                                  | V <sub>VANA</sub> -<br>0.4 |     | V <sub>VANA</sub> | V    |

| V <sub>PU</sub>  | Supply voltage for<br>external pullup resistor,<br>configured to open-drain                                                           |                                                                           |                            |     | V <sub>VANA</sub> | V    |

| R <sub>PU</sub>  | External pullup resistor, configured to open-drain                                                                                    |                                                                           |                            | 10  |                   | kΩ   |

| ALL DIGIT        | AL INPUTS                                                                                                                             |                                                                           | •                          |     | I                 |      |

| ILEAK            | Input current                                                                                                                         | All logic inputs over pin voltage range                                   | -1                         |     | 1                 | μA   |

(1) All voltage values are with respect to network ground.

(2) Minimum (MIN) and Maximum (MAX) limits are specified by design, test, or statistical analysis. Typical (TYP) numbers are not verified, but do represent the most likely norm.

(3) The maximum output current can be limited by the forward current limit I<sub>LIM FWD</sub>. The power dissipation inside the die increases the junction temperature and limits the maximum current depending of the length of the current pulse, efficiency, board and ambient temperature.

(4) The slew-rate can be limited by the current limit (forward or negative current limit), output capacitance and load current.

(5) The final PFM-to-PWM and PWM-to-PFM switchover current varies slightly and is dependent on the output voltage, input voltage and the inductor current level.

(6) The external clock frequency must be selected so that buck switching frequency is above 1.7 MHz.

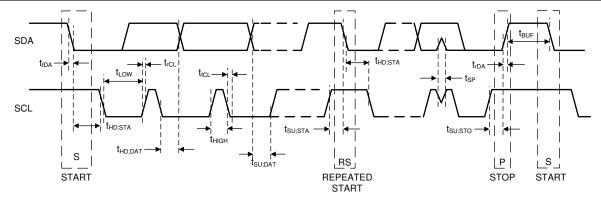

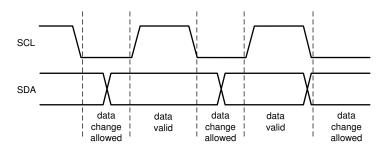

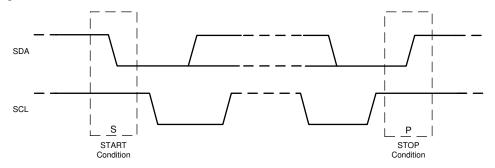

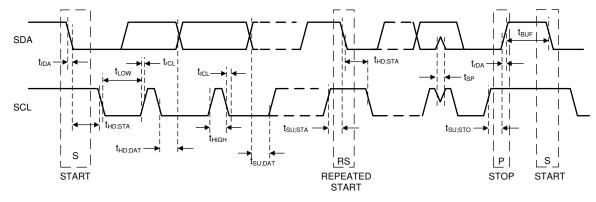

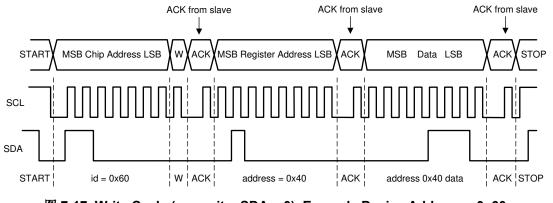

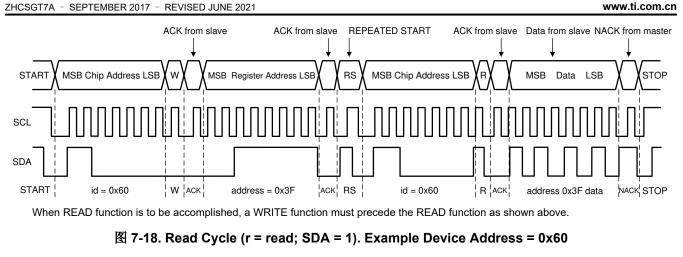

# 6.6 I<sup>2</sup>C Serial Bus Timing Parameters

These specifications are ensured by design. Unless otherwise noted,  $V_{IN_Bx} = 3.7 \text{ V}$  (see <sup>(1)</sup>). See 8 6-1 for details about the I<sup>2</sup>C-Compatible Timing diagram.

|                     |                                                  |                                          | MIN  | MAX  | UNIT  |  |

|---------------------|--------------------------------------------------|------------------------------------------|------|------|-------|--|

|                     |                                                  | Standard mode                            |      | 100  | kHz   |  |

|                     |                                                  | Fast mode                                |      | 400  | KI IZ |  |

| SCL                 | Serial clock frequency                           | Fast mode+                               |      | 1    |       |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 100 pF |      | 3.4  | MHz   |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 400 pF |      | 1.7  |       |  |

|                     |                                                  | Standard mode                            | 4.7  |      |       |  |

|                     |                                                  | Fast mode                                | 1.3  |      |       |  |

| LOW                 | SCL low time                                     | Fast mode+                               | 0.5  |      | μs    |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 100 pF | 0.16 |      |       |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 400 pF | 0.32 |      |       |  |

|                     |                                                  | Standard mode                            | 4    |      |       |  |

|                     |                                                  | Fast mode                                | 0.6  |      | μs    |  |

| thigh               | GH SCL high time                                 | Fast mode+                               | 0.26 |      |       |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 100 pF | 0.06 |      |       |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 400 pF | 0.12 |      |       |  |

|                     |                                                  | Standard mode                            | 250  |      |       |  |

|                     | Dete estur time                                  | Fast mode                                | 100  |      |       |  |

| <sup>I</sup> SU;DAT | Data setup time                                  | Fast mode+                               | 50   |      | ns    |  |

|                     |                                                  | High-speed mode                          | 10   |      |       |  |

|                     |                                                  | Standard mode                            | 10   | 3450 |       |  |

|                     |                                                  | Fast mode                                | 10   | 900  |       |  |

| HD;DAT              | Data hold time                                   | Fast mode+                               | 10   |      | ns    |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 100 pF | 10   | 70   |       |  |

|                     |                                                  | High-speed mode, C <sub>b</sub> = 400 pF | 10   | 150  |       |  |

|                     |                                                  | Standard mode                            | 4.7  |      | +     |  |

|                     | Setup time for a start or                        | Fast mode                                | 0.6  |      |       |  |

| SU;STA              | a repeated start condition                       | Fast mode+                               | 0.26 |      | μs    |  |

|                     |                                                  | High-speed mode                          | 0.16 |      |       |  |

|                     |                                                  | Standard mode                            | 4    |      |       |  |

|                     | Hold time for a start or a                       | Fast mode                                | 0.6  |      |       |  |

| <sup>I</sup> HD;STA | repeated start condition                         | Fast mode+                               | 0.26 |      | μs    |  |

|                     |                                                  | High-speed mode                          | 0.16 |      |       |  |

|                     |                                                  | Standard mode                            | 4.7  |      |       |  |

| t                   | Bus free time between a stop and start condition | Fast mode                                | 1.3  |      | μs    |  |

|                     |                                                  | Fast mode +                              | 0.5  |      |       |  |

|                     |                                                  | Standard mode                            | 4    |      |       |  |

|                     | Setup time for a stop                            | Fast mode                                | 0.6  |      |       |  |

| SU;STO              | condition                                        | Fast mode+                               | 0.26 |      | μs    |  |

|                     |                                                  | High-speed mode                          | 0.16 |      |       |  |

# 6.6 I<sup>2</sup>C Serial Bus Timing Parameters (continued)

These specifications are ensured by design. Unless otherwise noted,  $V_{IN_Bx} = 3.7 \text{ V}$  (see <sup>(1)</sup>). See  $\boxtimes$  6-1 for details about the I<sup>2</sup>C-Compatible Timing diagram.

|                   |                                                                                                |                                               | MIN                               | MAX  | UNIT |

|-------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------|------|------|

|                   |                                                                                                | Standard mode                                 |                                   | 1000 |      |

|                   |                                                                                                | Fast mode                                     | 20                                | 300  |      |

| t <sub>rDA</sub>  | Rise time of SDA signal                                                                        | Fast mode+                                    |                                   | 120  | ns   |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 100 pF      | 10                                | 80   |      |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 400 pF      | 20                                | 160  |      |

|                   |                                                                                                | Standard mode                                 |                                   | 300  |      |

|                   |                                                                                                | Fast mode                                     | 20 × (V <sub>DD</sub> / 5.5<br>V) | 300  |      |

| t <sub>fDA</sub>  | Fall time of SDA signal                                                                        | Fast mode+                                    | 20 × (V <sub>DD</sub> / 5.5<br>V) | 120  | ns   |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 100 pF      | 10                                | 80   |      |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 400 pF      | 30                                | 160  |      |

|                   |                                                                                                | Standard mode                                 |                                   | 1000 | ns   |

|                   |                                                                                                | Fast mode                                     | 20                                | 300  |      |

| t <sub>rCL</sub>  | Rise time of SCL signal                                                                        | Fast mode+                                    |                                   | 120  |      |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 100 pF      | 10                                | 40   |      |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 400 pF      | 20                                | 80   |      |

|                   | Rise time of SCL signal                                                                        | High-speed mode, $C_b$ = 100 pF               | 10                                | 80   |      |

| t <sub>rCL1</sub> | after a repeated start<br>condition and after an<br>acknowledge bit                            | High-speed mode, C <sub>b</sub> = 400 pF      | 20                                | 160  | ns   |

|                   |                                                                                                | Standard mode                                 |                                   | 300  |      |

|                   |                                                                                                | Fast mode                                     | 20 × (V <sub>DD</sub> / 5.5<br>V) | 300  |      |

| t <sub>fCL</sub>  | Fall time of a SCL signal                                                                      | Fast mode+                                    | 20 × (V <sub>DD</sub> / 5.5<br>V) | 120  | ns   |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 10 - 100 pF | 10                                | 40   |      |

|                   |                                                                                                | High-speed mode, C <sub>b</sub> = 400 pF      | 20                                | 80   | 30   |

| C <sub>b</sub>    | Capacitive load for each bus line (SCL and SDA)                                                |                                               |                                   | 400  | pF   |

|                   | Pulse width of spike                                                                           | Standard mode, fast mode, and fast mode+      |                                   | 50   |      |

| t <sub>SP</sub>   | suppressed (SCL and<br>SDA spikes that are less<br>then the indicated width<br>are suppressed) | High-speed mode                               |                                   | 10   | ns   |

(1) C<sub>b</sub> refers to the capacitance of one bus line.

图 6-1. I<sup>2</sup>C-Compatible Timing

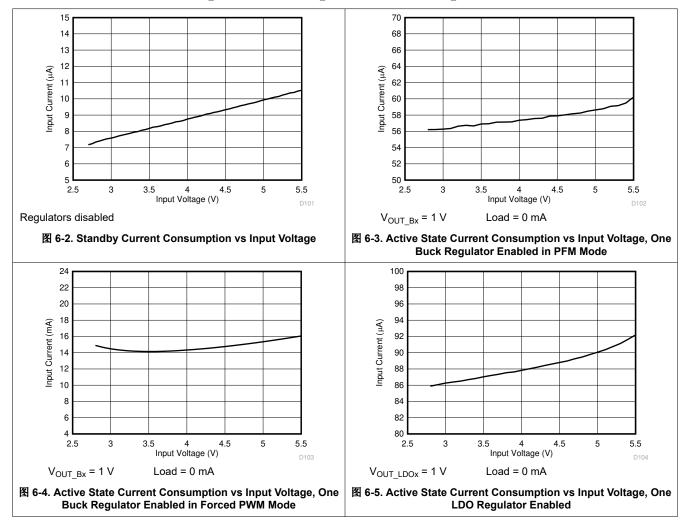

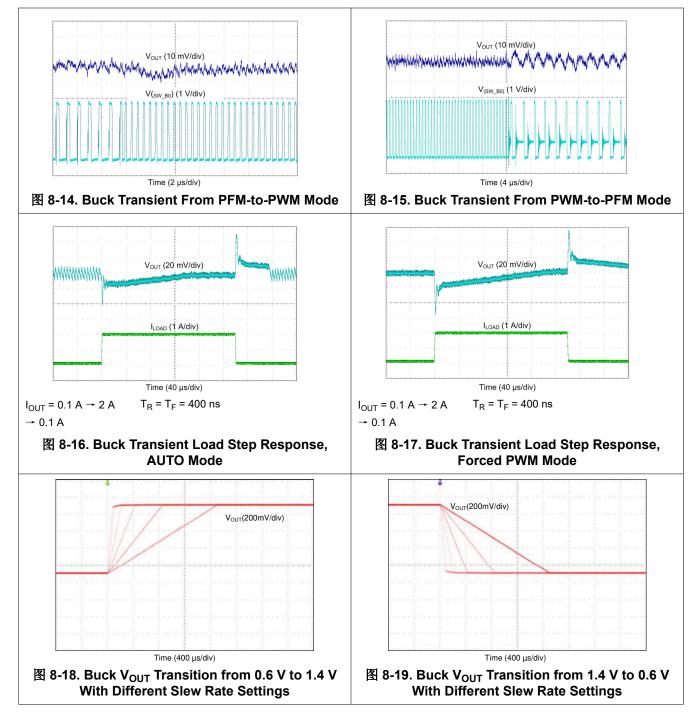

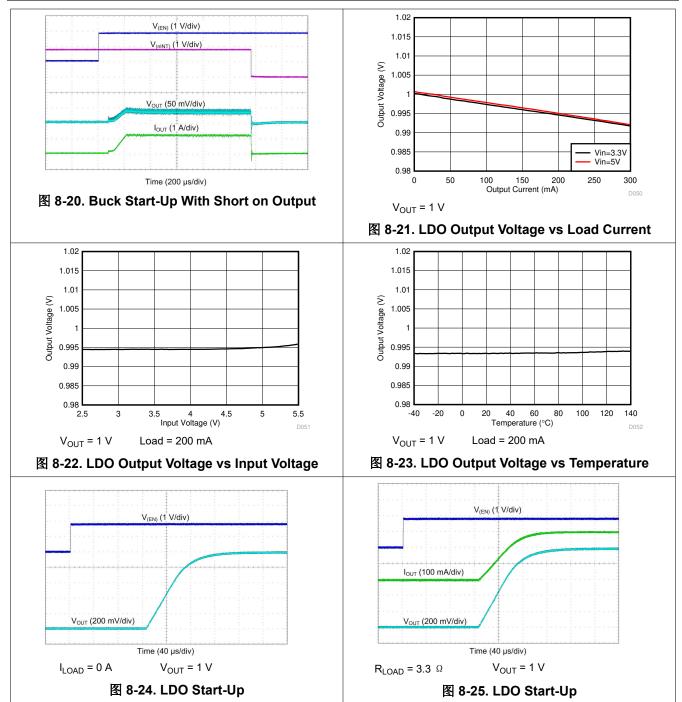

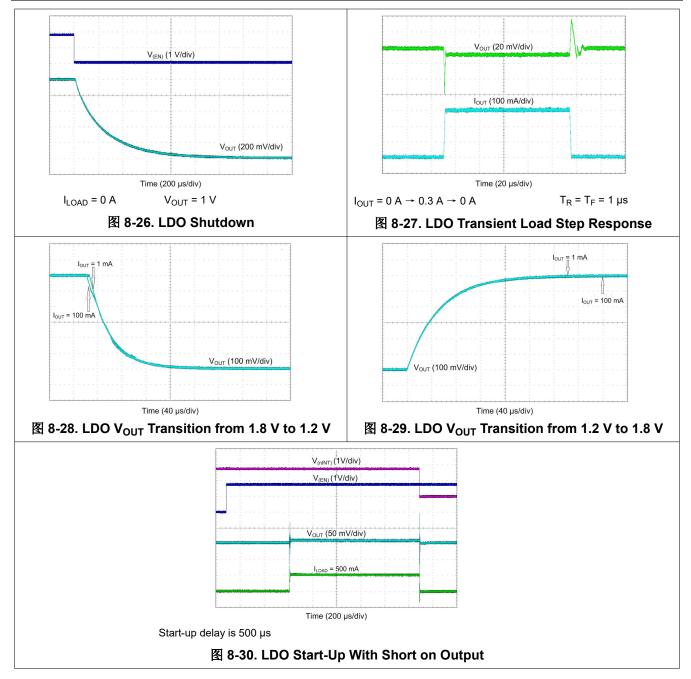

# **6.7 Typical Characteristics**

Unless otherwise specified:  $V_{(VIN\_Bx)} = V_{(VIN\_LDOx)} = V_{(VANA)} = 3.7 \text{ V}, V_{OUT\_Bx} = 1 \text{ V}, V_{OUT\_LDO} = 1 \text{ V}, T_A = 25^{\circ}\text{C}, L = 0.47 \text{ }\mu\text{H}$  (TOKO DFE252012PD-R47M),  $C_{OUT\_BUCK} = 22 \text{ }\mu\text{F}$ ,  $C_{POL\_BUCK} = 22 \text{ }\mu\text{F}$ , and  $C_{OUT\_LDO} = 1 \text{ }\mu\text{F}$ .

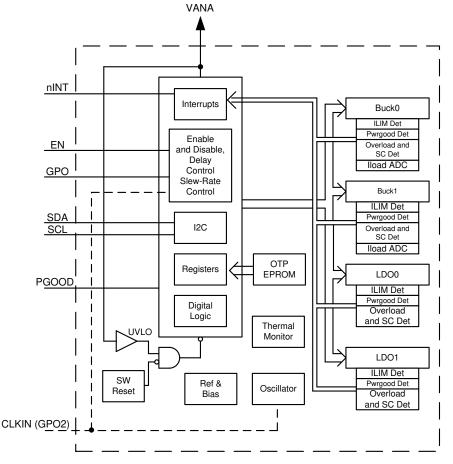

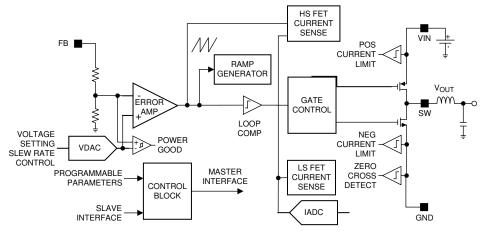

# 7 Detailed Description

## 7.1 Overview

The LP873220-Q1 is a high-efficiency, high-performance flexible power supply device with two step-down DC/DC converter cores (Buck0 and Buck1) and two low-dropout (LDO) linear regulators (LDO0 and LDO1) for automotive applications.  $\gtrsim$  7-1 lists the output characteristics of the regulators.

| SUPPLY | OUTPUT                     | OUTPUT                                                              |                                              |  |  |  |  |

|--------|----------------------------|---------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| SUPPLI | V <sub>OUT</sub> RANGE (V) | RESOLUTION (mV)                                                     | I <sub>MAX</sub> MAXIMUM OUTPUT CURRENT (mA) |  |  |  |  |

| Buck0  | 0.7 to 3.36                | 10 (0.7 V to 0.73 V)<br>5 (0.73 V to 1.4 V)<br>20 (1.4 V to 3.36 V) | 2000                                         |  |  |  |  |

| Buck1  | 0.7 to 3.36                | 10 (0.7 V to 0.73 V)<br>5 (0.73 V to 1.4 V)<br>20 (1.4 V to 3.36 V) | 2000                                         |  |  |  |  |

| LDO0   | 0.8 to 3.3                 | 100                                                                 | 300                                          |  |  |  |  |

| LDO1   | 0.8 to 3.3                 | 100                                                                 | 300                                          |  |  |  |  |

#### 表 7-1. Supply Specification

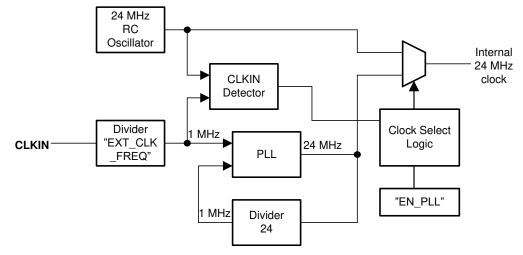

The LP873220-Q1 also supports switching clock synchronization to an external clock (CLKIN pin). The nominal frequency of the external clock can be from 1 MHz to 24 MHz with 1-MHz steps.

Additional features include:

- Soft-start

- Input voltage protection:

- Undervoltage lockout

- Overvoltage protection

- Output voltage monitoring and protection:

- Overvoltage monitoring

- Undervoltage monitoring

- Overload protection

- Thermal warning

- Thermal shutdown