ZHCSGU2A – JULY 2017 – REVISED SEPTEMBER 2017

LP5569

# 带引擎控制和电荷泵的 LP5569 九通道 I<sup>2</sup>C RGB LED 驱动器

## 1 特性

- 电源电压范围: 2.5V-5.5V

- 九个高精度电流源

- 每个通道最大 25.5mA

- 8 位独立的电流控制

- 12 位 20kHz 内部单独 PWM 控制 (无音频噪声)

- 三个可编程 LED Engines

- 独立照明控制(无有源微控制器控制)

- 在多个器件之间实现同步

- SRAM 存储器中具有多达 256 条指令,用于存储照明图案序列

- 与 LP5523 和 LP55231 器件兼容的命令集

- 灵活的调光控制

- I<sup>2</sup>C 调光控制

- PWM 直接输入调光

- PWM 输入频率: 100Hz 至 20kHz

- 用于通过低电池电压驱动高 V<sub>F</sub> LED 的自适应高效 电荷泵控制

- 主增益调节器控制通过仅对一个寄存器进行写入来 对多个 LED 进行调光,从而降低 I<sup>2</sup>C 总线流量

- 2μA 低待机电流,在自动省电模式下为 10μA(当 LED 不活动时)

- POR、UVLO 和 TSD 保护

#### 2 应用

用于以下设备的 LED 照明、指示灯和闪烁光:

- 智能扬声器

- 智能家用电器

- 门铃

- 电子锁

- 烟雾探测器

- 恒温器

- 机顶盒

- 智能路由器

- 蓝牙<sup>®</sup>耳机

- 手机

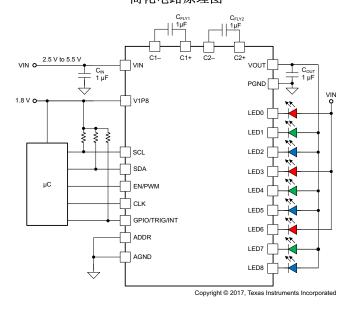

## 3 说明

LP5569 器件是一款可编程、易于使用的 9 通道 I<sup>2</sup>C LED 驱动器,用于为各种 应用制造灯光效果。LED 驱动器配备了一个用于存储用户编程的序列的内部 SRAM 存储器,以及三个允许在无处理器控制的情况下运行的可编程 LED Engines。将处理器置于睡眠模式时,自主运行可以降低系统功耗。

高效电荷泵支持通过高 V<sub>F</sub>(甚至通过 2.5V 输入电压)驱动 LED。LP5569 LED 驱动器可以根据 LED 正向电压要求自主选择最佳的电荷泵增益,从而在宽工作电压范围内保持高效率。

当 LED 未激活时,LP5569 器件进入省电模式,从而显著降低空闲电流消耗。灵活的数字接口允许连接多达八个 LP5569 器件,每个器件在同一系统中具有唯一的 I<sup>2</sup>C 从器件地址,从而支持所有器件之间的灯光效果同步。

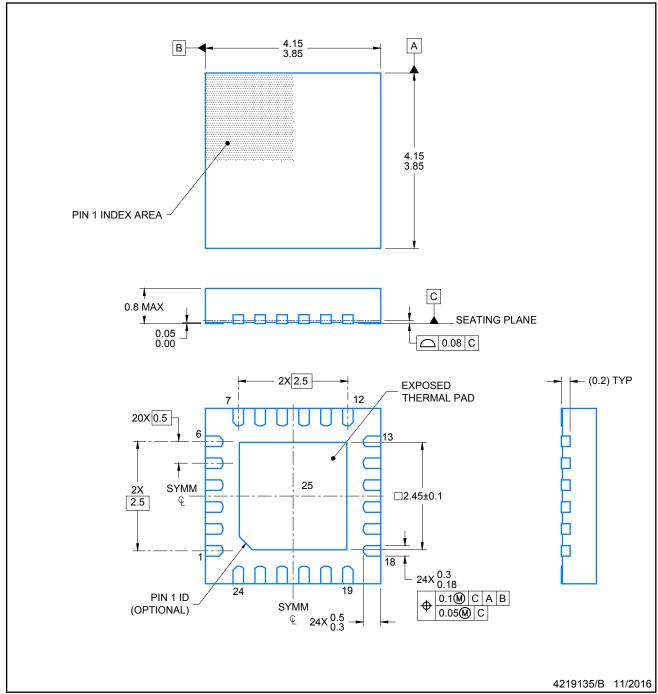

### 器件信息(1)

| 器件型号   | 封装        | 封装尺寸 (标称值)      |

|--------|-----------|-----------------|

| LP5569 | WQFN (24) | 4.00mm x 4.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

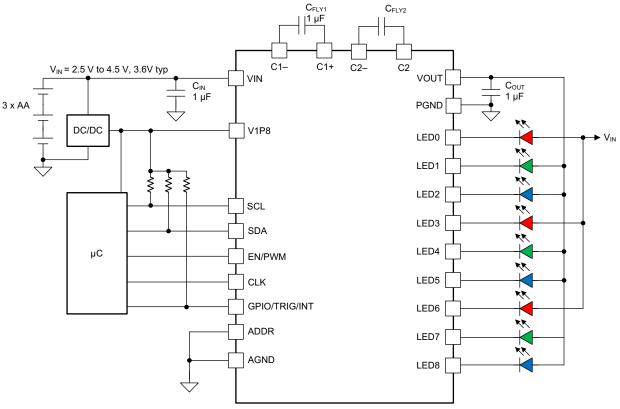

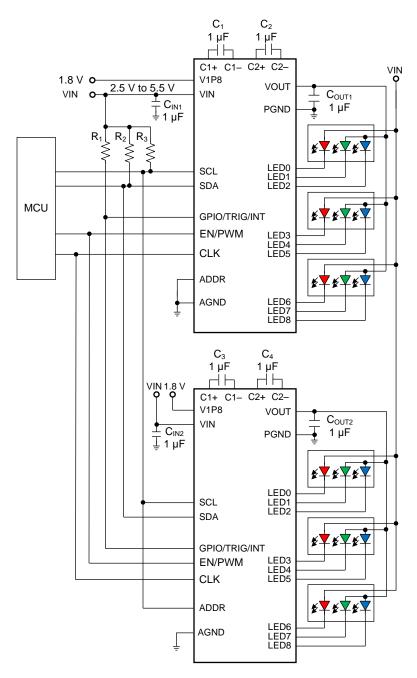

## 简化电路原理图

|                                 | Ę                                                      | 目录 |                  |

|---------------------------------|--------------------------------------------------------|----|------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 特性                                                     |    | 8.1 Overview     |

| 8                               | 7.12 Typical Characteristics                           |    | 13 机械、封装和可订购信息85 |

|                                 | 修订历史记录<br>nges from Original (July 2017) to Revision A |    | Page             |

## 5 Device Comparison Table

| PART NUMBER | GROUP | I <sup>2</sup> C SLAVE ADDRESS                          |

|-------------|-------|---------------------------------------------------------|

| LP5569      | 0     | 32h–35h and 40h (see I <sup>2</sup> C Slave Addressing) |

| LP5569A     | 1     | 42h–45h and 40h (see I <sup>2</sup> C Slave Addressing) |

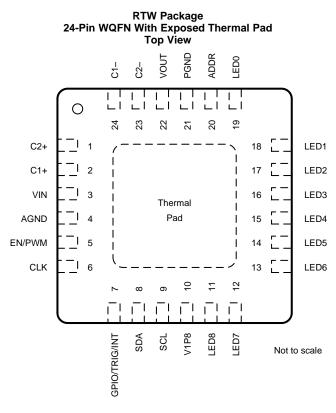

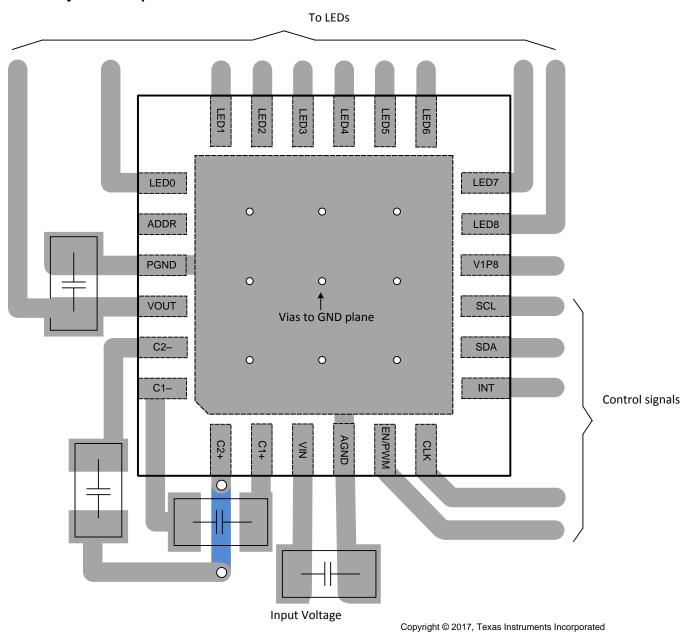

## 6 Pin Configuration and Functions

**Pin Functions**

| PIN      |    | 40                  |                                                                                                                       |  |  |

|----------|----|---------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                           |  |  |

| ADDR     | 20 | I                   | $I^2C$ slave-address selection pin. See $I^2C$ Slave Addressing for more details. This pin must not be left floating. |  |  |

| AGND     | 4  | G                   | Analog and digital ground. Connect to PGND, exposed thermal pad, and common ground plane.                             |  |  |

| C1-      | 24 | А                   | Negative pin of charge-pump flying capacitor 1. If charge pump is not used, this pin must be left floating.           |  |  |

| C1+      | 2  | А                   | Positive pin of charge-pump flying capacitor 1. If charge pump is not used, this pin must be left floating.           |  |  |

| C2-      | 23 | А                   | Negative pin of charge-pump flying capacitor 2. If charge pump is not used, this pin must be left floating.           |  |  |

| C2+      | 1  | А                   | Positive pin of charge-pump flying capacitor 2. If charge pump is not used, this pin must be left floating.           |  |  |

| CLK      | 6  | I, OD               | Clock input/output. By default this pin is a clock input. If not used, this pin must be connected to GND or VIN.      |  |  |

| EN/PWM   | 5  | I                   | Chip enable and PWM input pin.                                                                                        |  |  |

(1) A: analog pin; G: ground pin; P: power pin; I: input pin; OD: open-drain output pin

## Pin Functions (continued)

| PIN                 |     | TYPF <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                              |  |

|---------------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | NO. | IYPE                | DESCRIPTION                                                                                                                                                                                                                                                                              |  |

| GPIO/TRIG/INT       | 7   | I, OD               | General-purpose input or open-drain output, or trigger input or open-drain output, or interrupt open-drain output. This pin function is configured in the I <sup>2</sup> C registers. By default this pin is a general-purpose output (open-drain) and can be left floating if not used. |  |

| LED0                | 19  | А                   | LED current sink 0. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED1                | 18  | А                   | LED current sink 1. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED2                | 17  | Α                   | LED current sink 2. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED3                | 16  | Α                   | LED current sink 3. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED4                | 15  | Α                   | LED current sink 4. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED5                | 14  | Α                   | LED current sink 5. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED6                | 13  | Α                   | LED current sink 6. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED7                | 12  | Α                   | LED current sink 7. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| LED8                | 11  | Α                   | LED current sink 8. If not used, this pin can be left floating.                                                                                                                                                                                                                          |  |

| PGND                | 21  | G                   | Charge-pump power ground. Connect to AGND, exposed thermal pad, and common ground plane.                                                                                                                                                                                                 |  |

| SCL                 | 9   | I                   | I <sup>2</sup> C bus clock line. If not used, this pin must be connected to GND or VIN.                                                                                                                                                                                                  |  |

| SDA                 | 8   | I, OD               | I <sup>2</sup> C bus data line. If not used, this pin must be connected to GND or VIN.                                                                                                                                                                                                   |  |

| V1P8                | 10  | Р                   | Input power for digital circuitry.                                                                                                                                                                                                                                                       |  |

| VIN                 | 3   | Р                   | Input power, a 1-µF capacitor must be connected between PGND and this pin.                                                                                                                                                                                                               |  |

| VOUT                | 22  | А                   | Charge-pump output voltage. If charge pump is used, a 1-µF capacitor must be connected between PGND and this pin. If charge pump is not used or is used in 1x mode only, the capacitor can be omitted.                                                                                   |  |

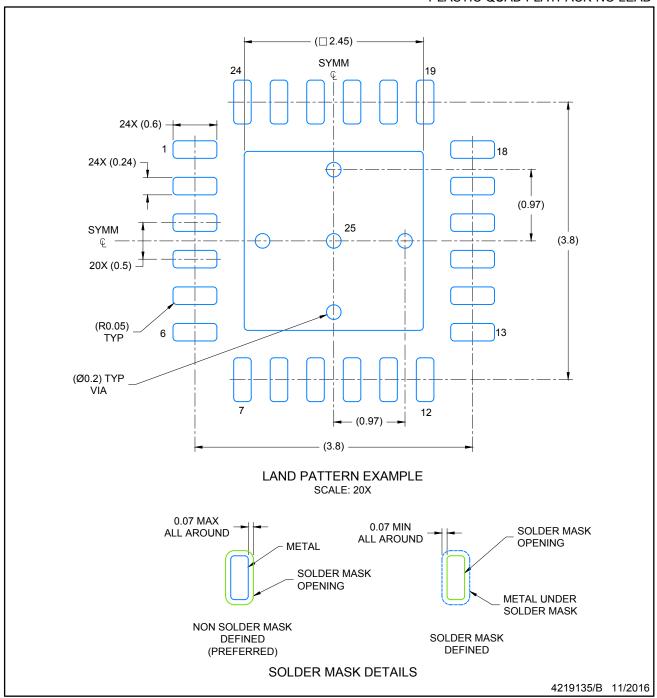

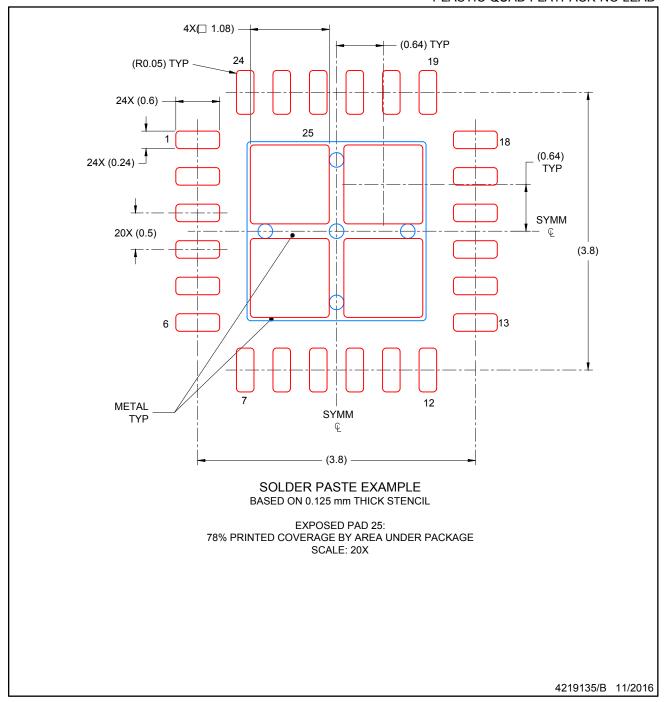

| Exposed thermal pad | _   | _                   | Must be connected to AGND (pin 4), PGND (pin 21), and common ground plane. See<br>Layout Example. Must be soldered to achieve appropriate power dissipation and mechanical reliability.                                                                                                  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                      | MIN                | MAX                             | UNIT |

|----------------------------------------------------------------------|--------------------|---------------------------------|------|

| Voltage on VIN, CLK, ADDR, EN/PWM, GPIO/TRIG/INT, SCL, SDA, VOUT (2) | -0.3               | 6                               | V    |

| Voltage on LED0 to LED8, C1-, C2-, C1+, C2+                          | -0.3               | $V_{VIN}$ + 0.3 V with 6 V max. | V    |

| Voltage on V1P8                                                      | -0.3               | 2                               | V    |

| Continuous power dissipation                                         | Internally limited | Internally limited              |      |

| Junction temperature, T <sub>J-MAX</sub>                             | -40                | 125                             | °C   |

| Storage temperature, T <sub>stg</sub>                                | -65                | 150                             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) VOUT cannot be forced to a power supply during device shutdown.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                                                              | MIN  | MAX              | UNIT |

|--------------------------------------------------------------|------|------------------|------|

| Input voltage on VIN                                         | 2.5  | 5.5              | V    |

| Voltage on LED0 to LED8, C1-, C2-, C1+, C2+, VOUT            | 0    | $V_{\text{VIN}}$ | V    |

| Voltage on CLK, ADDR, EN/PWM, GPIO/TRIG/INT, SDA, SCL        | 0    | $V_{VIN}$        | V    |

| Input voltage on V1P8                                        | 1.65 | 1.95             | V    |

| Output current on VOUT                                       | 0    | 160              | mA   |

| Operating ambient temperature, T <sub>A</sub> <sup>(1)</sup> | -40  | 85               | °C   |

<sup>(1)</sup> In applications where high power dissipation and/or poor PCB cooling status is present, the maximum ambient temperature might require derating. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the device in the application (R<sub>θJA</sub>), as given by the equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

## 7.4 Thermal Information

|                      |                                              | LP5569     |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTW (WQFN) | UNIT |

|                      |                                              | 24 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 35.8       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 26.7       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 13.1       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.4        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 13.1       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 4.6        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

<sup>2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.5 Electrical Characteristics

Unless otherwise noted, specifications apply to the LP5569 device in a circuit per the typical application diagram for the single device with  $V_{VIN}=3.6~V$ ,  $V_{1P8}=1.8~V$ ,

|                   | PARAMETER                                     | TEST CONDITIONS                                                          | MIN  | TYP | MAX | UNIT |

|-------------------|-----------------------------------------------|--------------------------------------------------------------------------|------|-----|-----|------|

|                   |                                               | V <sub>EN/PWM</sub> = 0 V, chip_en (bit) = 0                             |      | 0.2 | 1   |      |

|                   | Standby supply current                        | V <sub>EN/PWM</sub> = 3.3 V, chip_en (bit) = 0, external CLK not running |      | 1   | 2   | μΑ   |

|                   |                                               | V <sub>EN/PWM</sub> = 3.3 V, chip_en (bit) = 0, external CLK running     |      | 2   | 4   |      |

|                   |                                               | External CLK running, charge pump and current sinks disabled             |      | 56  | 70  |      |

| $I_{VIN}$         | Normal-mode supply current                    | Charge pump in 1x mode, no load, current sinks disabled                  |      | 65  | 90  | μΑ   |

|                   |                                               | Charge pump in 1.5x mode, no load, current-<br>sink outputs disabled     |      | 1.8 |     | mA   |

|                   | Power-save mode supply                        | External CLK running, see Automatic Power-<br>Save Mode                  |      | 10  | 15  | μA   |

|                   | current                                       | Internal oscillator running                                              |      | 10  | 15  | μ    |

|                   |                                               | V <sub>EN/PWM</sub> = 0 V, chip_en(bit) = 0                              |      | 0.2 | 1   | μΑ   |

|                   | Standby supply current                        | V <sub>EN/PWM</sub> = 3.3 V, chip_en (bit) = 0, external CLK not running |      | 0.2 | 2   | μΑ   |

|                   |                                               | V <sub>EN/PWM</sub> = 3.3 V, chip_en (bit) = 0, external CLK running     |      | 1   | 4   | μΑ   |

| I <sub>V1P8</sub> | Normal-mode supply current                    | External CLK running, charge pump and current sinks disabled             |      | 174 | 190 | μΑ   |

|                   |                                               | Charge pump in 1x mode, no load, current sinks disabled                  |      | 174 | 190 | μΑ   |

|                   |                                               | Charge pump in 1.5x mode, no load, current-<br>sink- outputs disabled    |      | 180 |     | μΑ   |

|                   | Powersave-mode supply                         | External CLK running                                                     |      | 1   | 5   | μΑ   |

|                   | current                                       | Internal oscillator running                                              |      | 1   | 5   | μΑ   |

| $f_{ m OSC}$      | 32-kHz internal oscillator frequency accuracy | T <sub>A</sub> = 25°C                                                    | -10% |     | 10% |      |

|                   | 10-MHz internal oscillator frequency accuracy |                                                                          | -7%  |     | 7%  |      |

| V                 | Lindon voltago lookout                        | V <sub>VIN</sub> falling                                                 |      | 2.2 |     | V    |

| $V_{UVLO}$        | Undervoltage lockout                          | V <sub>VIN</sub> rising                                                  |      | 2.3 |     | V    |

### 7.6 Charge-Pump Electrical Characteristics

|                  | PARAMETER                        | TEST CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT |

|------------------|----------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| <u> </u>         | Charry average autout registeres | Gain = 1x, V <sub>VIN</sub> = 4.2 V                                      |      | 1    |      | 0    |

| R <sub>OUT</sub> | Charge-pump output resistance    | Gain = 1.5x, V <sub>VIN</sub> = 3.7 V                                    |      | 3.5  |      | Ω    |

| V <sub>OUT</sub> |                                  | $V_{VIN} = 3.7 \text{ V}, I_{OUT} = 160 \text{ mA},$ gain = 1.5x         | 4.41 | 4.5  | 4.59 | V    |

| $f_{\sf SW}$     | Switching frequency              |                                                                          |      | 1.25 |      | MHz  |

| I <sub>CL</sub>  | Output current limit             | $V_{OUT} = 0 \text{ V}, V_{VIN} = 3.7 \text{ V},$<br>$CP\_CONFIG = 0xFF$ |      | 600  |      | mA   |

| t <sub>ON</sub>  | V <sub>OUT</sub> turnon time     | $I_{OUT} = 0$ mA, $V_{IN} \ge 3$ V, $V_{OUT} > 4.1$ V, gain = 1.5x       |      | 100  |      | μs   |

|                  |                                  | V <sub>VIN</sub> > 3.1 V, V <sub>OUT</sub> dropped<br>10%, gain = 1.5×   |      | 200  |      | A    |

| lout             | Maximum output current           | $V_{IN}$ > 2.5 V, $V_{OUT}$ dropped 10%, gain = 1.5x                     |      | 150  |      | mA   |

### 7.7 LED Current Sinks Electrical Characteristics

|                        | PARAMETER                            | TEST CONDITIONS                    | MIN   | TYP  | MAX  | UNIT |

|------------------------|--------------------------------------|------------------------------------|-------|------|------|------|

| I <sub>LEAKAGE</sub>   | Leakage current (LED0 to LED8)       | PWM = 0%, V <sub>LED</sub> = 5 V   |       |      | 1    | μΑ   |

| I <sub>MAX</sub>       | Maximum sink current                 |                                    | 24.5  | 25.5 | 26.5 | mA   |

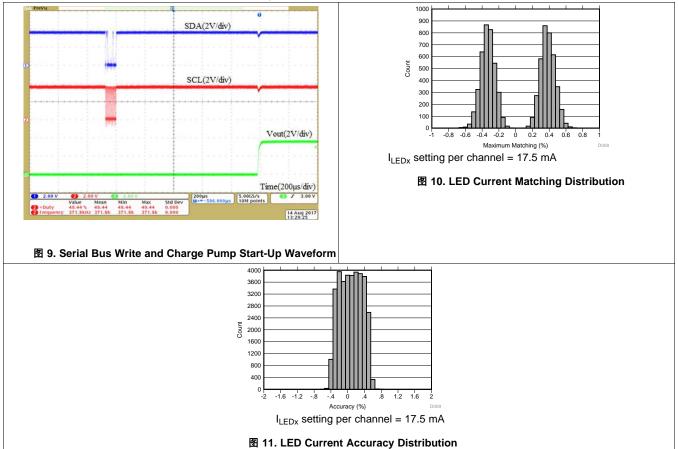

| I <sub>LED_ACC</sub>   | Sink current accuracy <sup>(1)</sup> | Current set to 17.5 mA. PWM = 100% | -4.5% |      | 4.5% |      |

| I <sub>LED_MATCH</sub> | Matching <sup>(1)</sup>              | Current set to 17.5 mA             |       | 1%   | 2.5% |      |

| $f_{LED}$              | LED switching frequency              |                                    |       | 19.5 |      | kHz  |

| $V_{SAT}$              | Saturation voltage (2)               | Output current set to 25.5 mA      |       | 90   | 110  | mV   |

<sup>(1)</sup> Output-current accuracy is the difference between the actual value of the output current and the programmed value of this current. Matching is the maximum difference from the average. For the constant-current outputs on the device (LED0 to LED8), the following are determined: the maximum output current (MAX), the minimum output current (MIN), and the average output current of all outputs (AVG). The matching number is calculated: (MAX – MIN) / AVG. The typical specification provided is the most likely norm of the matching figure for all devices. Note that some manufacturers have different definitions in use.

(2) Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at 1 V.

## 7.8 Logic Interface Characteristics

| 1.0              | .o Logic interface characteristics     |                                                                  |      |     |     |      |  |

|------------------|----------------------------------------|------------------------------------------------------------------|------|-----|-----|------|--|

|                  | PARAMETER                              | TEST CONDITIONS                                                  | MIN  | TYP | MAX | UNIT |  |

| LOG              | LOGIC INPUT (EN/PWM, SCL, ADDR)        |                                                                  |      |     |     |      |  |

| $V_{IL}$         | Input low level                        |                                                                  |      |     | 0.4 | V    |  |

| $V_{IH}$         | Input high level                       |                                                                  | 1.25 |     |     | V    |  |

| I <sub>lkg</sub> | Input leakage current                  | $V_{I} \leq V_{VIN}$                                             | -1   |     | 1   | μΑ   |  |

| LOG              | LOGIC OUTPUT (SDA, GPIO/TRIG/INT, CLK) |                                                                  |      |     |     |      |  |

| $V_{IL}$         | Input low level                        | Pin configured as input                                          |      |     | 0.4 | V    |  |

| $V_{IH}$         | Input high level                       | Pin configured as input                                          | 1.25 |     |     | V    |  |

| I <sub>lkg</sub> | Input leakage current                  | Pin configured as input, $V_{VIN}$<br>= 5.5 V, $V_I \le V_{VIN}$ | -1   |     | 1   | μΑ   |  |

| $V_{OL}$         | Output low level                       | I <sub>PULLUP</sub> = 3 mA                                       |      | 0.2 | 0.5 | V    |  |

| IL               | Output leakage current                 | Pin configured as output, Hi-Z state                             |      |     | 1   | μΑ   |  |

### 7.9 Timing Requirements (EN/PWM)

|                          |                                                                              | MIN | TYP | MAX | UNIT |

|--------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>EN</sub>          | Enable time, EN/PWM first rising edge until first I <sup>2</sup> C access    |     | 2   | 3   | ms   |

| t <sub>EN_TIMEOUT</sub>  | EN timeout, EN/PWM = low time while in standby mode (enable function)        |     | 15  |     | ms   |

| t <sub>PWM_TIMEOUT</sub> | PWM timeout, EN/PWM = low time while in normal mode (PWM function)           |     | 15  |     | ms   |

| PWM <sub>res</sub>       | Resolution for EN/PWM input when configured as PWM, f <sub>PWM</sub> =10 kHz |     | 10  |     | bits |

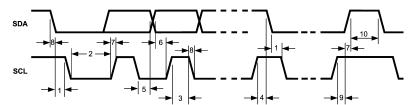

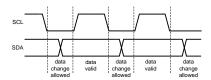

## 7.10 Serial-Bus Timing Requirements (SDA, SCL), See 🛭 1

I<sup>2</sup>C fast mode

| 0 1400 1      | o lace mode                                        |            |     |      |  |  |

|---------------|----------------------------------------------------|------------|-----|------|--|--|

|               |                                                    | MIN        | MAX | UNIT |  |  |

| $f_{\sf SCL}$ | Clock frequency                                    | 0          | 400 | kHz  |  |  |

| 1             | Hold time (repeated) START condition               | 0.6        |     | μs   |  |  |

| 2             | Clock low time                                     | 1.3        |     | μs   |  |  |

| 3             | Clock high time                                    | 600        |     | ns   |  |  |

| 4             | Setup time for a repeated START condition          | 600        |     | ns   |  |  |

| 5             | Data hold time                                     | 0          |     | ns   |  |  |

| 6             | Data setup time                                    | 100        |     | ns   |  |  |

| 7             | Rise time of SDA and SCL                           | 20 + 0.1Cb | 300 | ns   |  |  |

| 8             | Fall time of SDA and SCL                           | 15 + 0.1Cb | 300 | ns   |  |  |

| 9             | Setup time for STOP condition                      | 600        |     | ns   |  |  |

| 10            | Bus-free time between a STOP and a START condition | 1.3        |     | μs   |  |  |

| Cb            | Capacitive load for each bus line                  | 10         | 200 | pF   |  |  |

|               |                                                    |            |     |      |  |  |

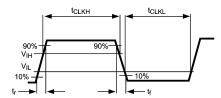

## 7.11 External Clock Timing Requirements (CLK), See 图 2

over operating ambient temperature range (unless otherwise noted)

|                   |                                                       | MIN | TYP  | MAX | UNIT |

|-------------------|-------------------------------------------------------|-----|------|-----|------|

| $f_{CLK}$         | Clock frequency                                       |     | 32.7 |     | kHz  |

| t <sub>CLKH</sub> | High time                                             | 6   |      |     | μs   |

| t <sub>CLKL</sub> | Low time                                              | 6   |      |     | μs   |

| t <sub>r</sub>    | Clock rise time, 10% rising edge to 90% rising edge   |     |      | 2   | μs   |

| t <sub>f</sub>    | Clock fall time, 90% falling edge to 10% falling edge |     |      | 2   | μs   |

图 1. Timing Parameters

图 2. External Clock Signal

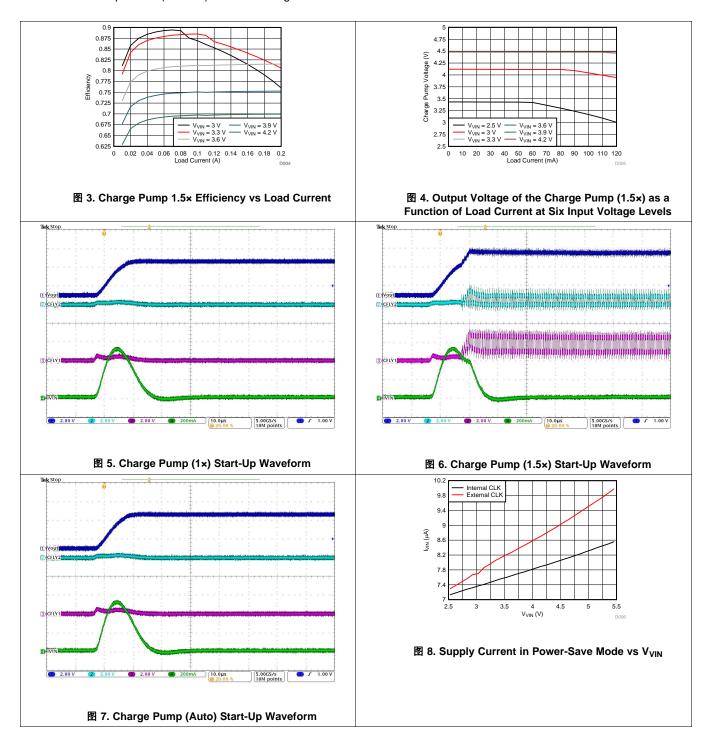

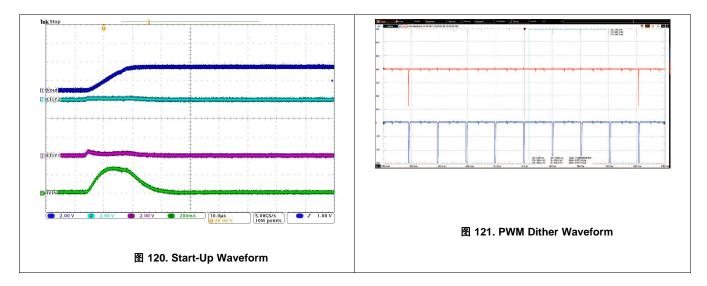

## 7.12 Typical Characteristics

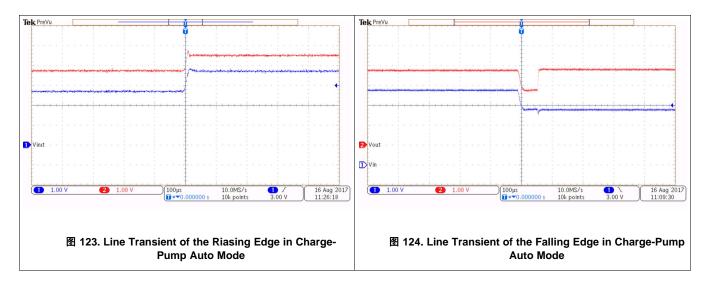

Unless otherwise specified:  $V_{VIN}$  = 3.6 V,  $C_{IN}$  =  $C_{OUT}$  = 1  $\mu$ F, C1 = C2 = 1  $\mu$ F,  $T_A$  = 25°C.  $C_{IN}$ ,  $C_{OUT}$ , C1, C2: Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

## Typical Characteristics (接下页)

Unless otherwise specified:  $V_{VIN}$  = 3.6 V,  $C_{IN}$  =  $C_{OUT}$  = 1  $\mu$ F, C1 = C2 = 1  $\mu$ F,  $T_A$  = 25°C.  $C_{IN}$ ,  $C_{OUT}$ , C1, C2: Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

## 8 Detailed Description

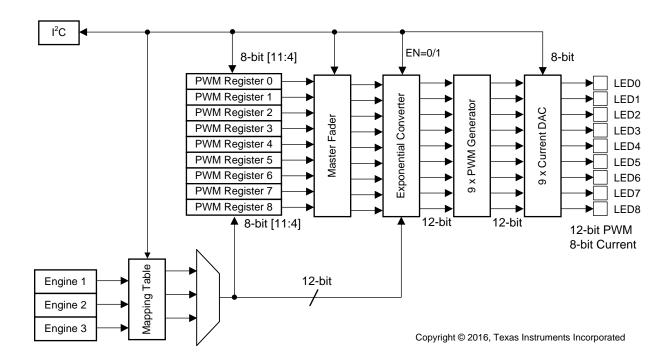

#### 8.1 Overview

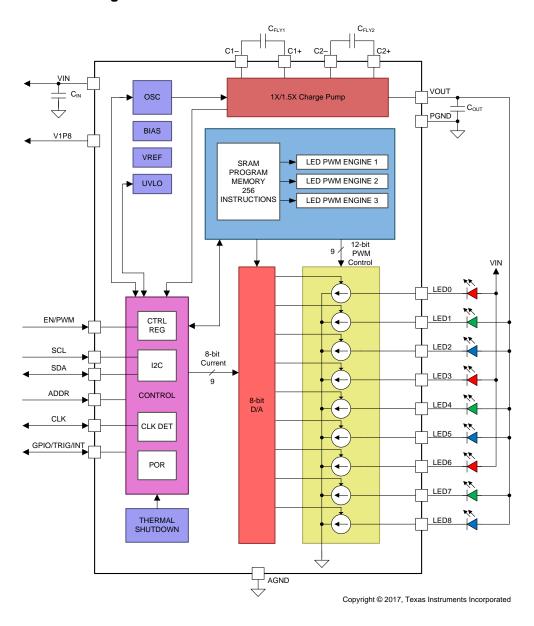

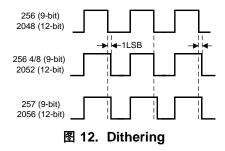

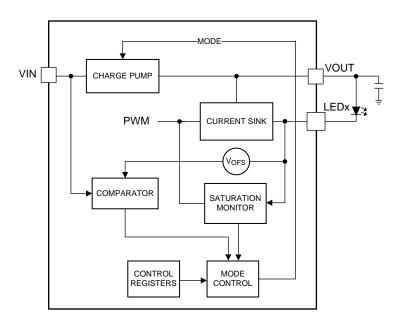

The LP5569 device is a fully integrated lighting management unit for producing lighting effects for various LED applications. The LP5569 device includes all necessary power management, low-side current sinks, two-wire serial I<sup>2</sup>C-compatible interface, and programmable LED engines. The overall maximum current for each of the nine drivers is set with 8-bit resolution. The LP5569 device controls LED luminance with a pulse-width modulation (PWM) scheme with a resolution of 12 bits at 20 kHz, which is achieved by using 3-bit dithering.

#### 8.1.1 Programming

The LP5569 device provides flexibility and programmability for dimming and sequencing control. Each LED can be controlled directly and independently through the serial interface, or LED drivers can be grouped together for preprogrammed flashing patterns. The device has three independent program execution engines. Each engine can control 1 to 9 LED driver outputs, but more than one engine cannot simultaneously control the same LED driver output. Any engine can be used as the master fader for all three engines.

#### 8.1.2 Energy Efficiency

An integrated 1x or 1.5x charge pump with adaptive control provides supply voltage for LEDs when operating with low input voltage. Because the LED drivers are low-side sinks, some or all LEDs can be powered from an external source if available. The LP5569 device has very low standby current and an automatic power-save mode when the LEDs are inactive.

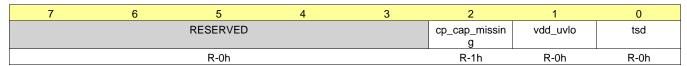

#### 8.1.3 Protection Features

Protection features include power-on reset, charge-pump input-current limiter, thermal shutdown (TSD), and undervoltage lockout (UVLO).

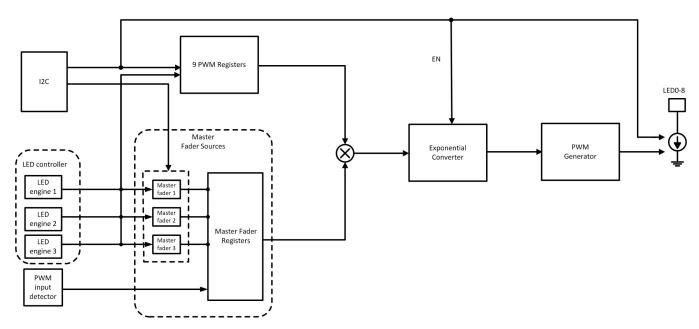

## 8.2 Functional Block Diagram

## 8.3 Feature Description

#### 8.3.1 Current Sinks

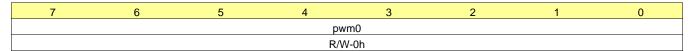

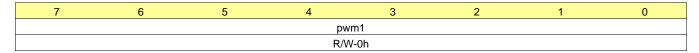

#### 8.3.1.1 Overview

The LP5569 LED drivers are constant-current sources. Maximum output-current scale can be programmed by control registers up to 25.5 mA. The overall maximum current is set by 8-bit output current-control registers with  $100-\mu A$  step size. Each of the 9 LED drivers has a separate output-current control register. The LED luminance pattern (dimming) is controlled with a PWM technique, which has 12-bit resolution during ramping and 8-bit user control. The LED current-sink PWM frequency is 20 kHz.

High 20-kHz PWM frequency and 12-bit control accuracy are achieved by using 3-bit dithering for PWM control. There is a 9-bit pure PWM resolution generated in the PWM generators, and one least-significant bit (1 LSB) is toggled in eight periods to output a smaller average step. For 3-bit dithering, every eighth pulse is made 1 LSB longer to increase the average value by 1 / 8th. ₹ 12 shows an example of 9-bit PWM value, step of 4 / 8 (0.5) and its 12-bit representation.

A phase-shift PWM scheme allows delaying the time when each LED driver is active. When the LED drivers are not activated simultaneously, the peak load current from the charge-pump output is greatly decreased. This also reduces input-current ripple and ceramic-capacitor audible ringing. LED drivers are grouped into three different phases. In phase 1, the rising edge of the PWM pulse is fixed in time. In phase 2, the middle point of the PWM pulse is fixed, and the pulse spreads to both directions when PWM duty cycle is increased. Phase 3 has a fixed falling edge, that is, the rising edge of the pulse is changed when the duty cycle changes.

图 13. LED Phase Shift

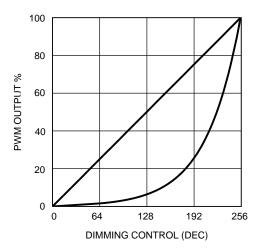

LED dimming is controlled according to an exponential or linear scale (see <a>§</a> 14) In exponential mode, the PWM output percent can be approximated by the following two equations:

- Less than or equal to code 64: y = 0.0125x 0.0066.

- Greater than code 64:  $y = 0.7835e^{0.0217x}$

## Feature Description (接下页)

图 14. 8-Bit User PWM Control, Exponential and Linear Dimming

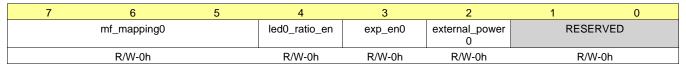

#### 8.3.1.2 Controlling the Low-Side Current Sinks

#### 8.3.1.2.1 Direct Register Control

All LP5569 LED drivers, LED0 to LED8, can be controlled independently through the two-wire serial I<sup>2</sup>C-compatible interface. For each low-side driver there is an 8-bit PWM control register which can be used to control the LED PWM duty-cycle value. This register cannot be written when the program execution engine is active, which could result in undesirable behavior. Care should be taken to update these registers only when the program execution engine is idle.

#### 8.3.1.2.2 Controlling by Program Execution Engines

Engine control is used when the user wants to create programmed sequences. The program execution engine updates the direct-control registers when active. Therefore, if the user has set the PWM register to a certain value, it is automatically overridden when the program execution engine controls the driver. LED control and program-execution-engine operation is described in *Programming*.

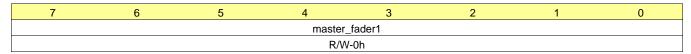

#### 8.3.1.2.3 Master Fader Control

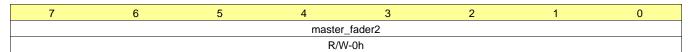

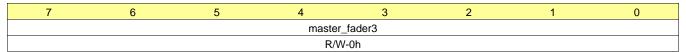

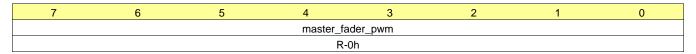

In addition to LED-by-LED PWM register control, the LP5569 device is equipped with a master-fader control, which allows the user to fade in or fade out multiple LEDs from the EN/PWM pin or by writing to the master fader registers. This is a useful function to minimize serial bus traffic between the MCU and the LP5569 device. The LP5569 device has three master fader registers, so it is possible to form three master fader groups. Either writing master fader registers through the I<sup>2</sup>C interface directly or through LED engine control can set the master fader register values. The final output PWM duty cycle is the PWM register duty-cycle value multiplied by the duty-cycle value of the master fader register.

## Feature Description (接下页)

图 15. Simplified Data Flow of Master Fader

#### 8.3.1.2.3.1 PWM Master Fader on EN/PWM Pin

The EN/PWM pin provides a dual-function input. On power up, the pin functions as the device enable (EN) function, where the first rising edge enables the LP5569 device. After the chip\_en bit is set high in the CONFIG register, the pin is reconfigured for PWM master-fader control of the LEDs. The LEDx\_CONTROL register (addresses 07h–0Fh) MF\_MAPPINGx bits = 5h configures LEDx for PWM control.

The PWM input is a sampled input which converts the input duty-cycle information into an 11-bit code. The use of a sampled input eliminates any noise and current ripple that is typical of traditional PWM-controlled LED drivers. The PWM input uses logic-level thresholds with  $V_{IH\_MIN} = 1.25 \text{ V}$  and  $V_{IL\_MAX} = 0.4 \text{ V}$ . Because this is a sampled input, there are limits on the maximum PWM input frequency as well as the resolution that can be achieved.

#### 8.3.1.2.3.2 PWM Master Fader Resolution and Input Frequency Range

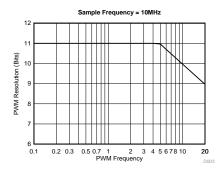

The PWM input frequency range is 100 Hz to 20 kHz. To achieve the full 11-bit maximum resolution of PWM duty cycle to the code, the input PWM duty cycle must be  $\geq$  11 bits, and the PWM sample period (1 /  $f_{SAMPLE}$ ) must be smaller than the minimum PWM input pulse duration.  $\boxtimes$  16 shows the possible brightness code resolutions based on the input PWM frequency.

图 16. PWM Resolution vs PWM Input Frequency

## Feature Description (接下页)

#### 8.3.1.2.3.3 PWM Master Fader Hysteresis

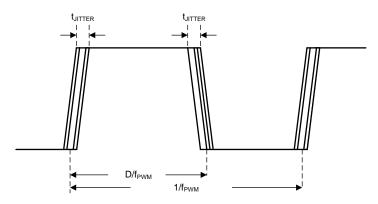

To prevent jitter on the input PWM signal from feeding through the PWM path and causing oscillations in the LED current, the LP5569 device offers seven selectable hysteresis settings. The hysteresis works by forcing a specific number of 11-bit LSB code transitions to occur in the input duty cycle before the LED current changes. 表 1 describes the hysteresis. The hysteresis only applies during a change in direction of brightness currents. Once the change in direction has taken place, the PWM input must overcome the required LSB(s) of the hysteresis setting before the brightness change takes effect. Once the initial hysteresis has been overcome and the direction in brightness change remains the same, the PWM-to-current response changes with no hysteresis.

表 1. PWM Input Hysteresis

|                                               |                                                                                                                                                      | MIN. CHANGE                                                                  |                  |             |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|-------------|--|

| HYSTERESIS<br>SETTING<br>(0x80 bits<br>[2:0]) | MIN. CHANGE IN PWM PULSE<br>DURATION (\(\Delta\)t) REQUIRED TO<br>CHANGE LED CURRENT,<br>AFTER DIRECTION CHANGE<br>(for f <sub>PWM</sub> < 11.7 kHz) | IN PWM DUTY CYCLE (AD) REQUIRED TO CHANGE LED CURRENT AFTER DIRECTION CHANGE | EXPONENTIAL MODE | LINEAR MODE |  |

| 000 (0 LSB)                                   | 1 / (f <sub>PWM</sub> × 2047)                                                                                                                        | 0.05%                                                                        | 0.3%             | 0.05%       |  |

| 001 (1 LSB)                                   | 1 / (f <sub>PWM</sub> × 1023)                                                                                                                        | 0.1%                                                                         | 0.61%            | 0.1%        |  |

| 010 (2 LSB)                                   | 1 / (f <sub>PWM</sub> × 511)                                                                                                                         | 0.2%                                                                         | 1.21%            | 0.2%        |  |

| 011 (3 LSB)                                   | 1 / (f <sub>PWM</sub> × 255)                                                                                                                         | 0.39%                                                                        | 2.4%             | 0.39%       |  |

| 100 (4 LSB)                                   | 1 / (f <sub>PWM</sub> × 127)                                                                                                                         | 0.78%                                                                        | 4.74%            | 0.78%       |  |

| 101 (5 LSB)                                   | 1 / (f <sub>PWM</sub> × 63)                                                                                                                          | 1.56%                                                                        | 9.26%            | 1.56%       |  |

| 110 (6 LSB)                                   | 1 / (f <sub>PWM</sub> × 31)                                                                                                                          | 3.12%                                                                        | 17.66%           | 3.12%       |  |

- D is  $t_{JITTER}$  x  $f_{PWM}$  or equal to #LSB's =  $\Delta D$  x 2048 codes.

- For 11-bit resolution, #LSBs is equal to a hysteresis setting of LN(#LSB's)/LN(2).

- For example, with a t<sub>JITTER</sub> of 1 μs and a f<sub>PWM</sub> of 5 kHz, the hysteresis setting should be: LN(1 μ s x 5 kHz x 2048)/LN(2) = 3.35 (4 LSBs).

Copyright © 2016, Texas Instruments Incorporated

图 17. PWM Hysteresis Example

#### 8.3.1.2.4 EN/PWM Input Timeout

The EN/PWM input timeout feature has two operating modes as follows:

• STANDBY state: EN/PWM low for > 15 ms shuts down the LP5569 device and returns to the DISABLED state (see 图 20).

### 8.3.2 Charge Pump

#### 8.3.2.1 Overview

The LP5569 device includes a pre-regulated switched-capacitor charge pump with a programmable voltage multiplication of  $1\times$  or  $1.5\times$ . In  $1.5\times$  mode, by combining the principles of a switched-capacitor charge pump and a linear regulator, a regulated 4.5-V output is generated from the VIN input within its normal voltage range. A two-phase non-overlapping clock, generated internally, controls the operation of the charge pump. During the charge phase, both flying capacitors (CFLY1 and CFLY2) are charged from input voltage. In the pump phase that follows, the flying capacitors are discharged to the output. A traditional switched-capacitor charge pump operating in this manner uses switches with very low on-resistance, ideally  $0\ \Omega$ , to generate an output voltage that is  $1.5\times$  the input voltage. The LP5569 device regulates the output voltage by controlling the resistance of the input-connected pass-transistor switches in the charge pump.

#### 8.3.2.2 Pre-Regulation

The very low input-current ripple of the LP5569 device, resulting from internal pre-regulation, adds minimal noise to the input line. The core of the LP5569 device is very similar to that of a basic switched-capacitor charge pump: it is composed of switches and two flying capacitors (external). Regulation is achieved by controlling the current through the switches connected to the VIN pin (one switch in each phase). The regulation occurs before the voltage multiplication, giving rise to the term *pre-regulation*. It is pre-regulation that eliminates most of the input-current ripple that is a typical and undesirable characteristic of a many switched-capacitor converters.

#### 8.3.2.3 Input Current Limit

The LP5569 device contains current-limit circuitry that protects the device in the event of excessive input current and/or output shorts to ground. The input current is limited to 600 mA (typical) when the output is shorted directly to ground. When the LP5569 device is current limiting, power dissipation in the device is likely to be quite high. In this event, thermal cycling should be expected.

#### 8.3.2.4 Output Discharge

The LP5569 device provides a feature to discharge the charge-pump output capacitor. The charge-pump output pulldown is not enabled when the MISC2 register (address 33h) CP\_DIS\_DISCH bit = 1. The charge pump output pulldown is enabled when the CP\_DIS\_DISCH bit = 0. The pulldown draws a minimal current from the output capacitor (300  $\mu$ A typical) when in the SHUTDOWN and STANDBY states.

#### 8.3.2.5 Controlling the Charge Pump

The charge pump is controlled with two CP\_MODE bits in the MISC register (address 2Fh). When both of the bits are low, the charge pump is disabled, and output voltage is pulled down as described in *Output Discharge*. The charge pump can be forced to the bypass mode, so the battery voltage is connected directly to the current source; in 1.5x mode the output voltage is boosted to 4.5 V. In automatic mode, the charge-pump operation mode is determined by saturation of the constant-current drivers described in *LED Forward Voltage Monitoring*.

#### 8.3.2.6 LED Forward Voltage Monitoring

When the charge-pump automatic-mode selection is enabled, voltages on the LED current sinks LED0 to LED8 are monitored. If the current sinks do not have enough headroom, the charge pump gain is set to 1.5x and remains in 1.5x mode until one of the following occurs:

- The LP5569 device enters the SHUTDOWN state and goes through the INITIALIZATION or STARTUP state.

- The charge-pump mode is forced to 1x mode via the MISC register.

- The LP5569 device exits power save when the charge pump is in automatic mode (CP\_MODE bits = 3h). A current-sink saturation monitor is selectable to one of four fixed voltage thresholds. The charge-pump gain is set to 1x when the battery voltage is high enough to supply all LEDs. Note: forward-voltage monitoring is disabled when the LEDx\_CONTROL (addresses 07h-0Fh) register EXTERNAL\_POWERx bit = 1.

Copyright © 2016, Texas Instruments Incorporated

#### 图 18. Forward-Voltage-Monitoring and Gain-Control Block

### 8.3.3 Energy Efficiency

## 8.3.3.1 LED Powering

The red LED (R) element of an RGB LED typically has a forward voltage of about 2 V. These LEDs can be powered directly from the input voltage because battery voltage is typically high enough to drive red LEDs over the whole operating voltage range. This allows driving of three RGB LEDs with good efficiency because the red LEDs do not load the charge pump. When the LEDx\_CONTROL (address 07h–0Fh) register EXTERNAL\_POWERx bit = 1, the LEDx output is configured for external supply, and forward-voltage monitoring is disabled.

### 8.3.4 Automatic Power-Save Mode

When the LED outputs are not active, the LP5569 device is able to enter the power-save mode automatically, thus lowering idle-current consumption down to 10  $\mu$ A (typical). Automatic power-save mode is enabled when the MISC register (address 2Fh) POWERSAVE\_EN bit = 1. Almost all analog blocks are powered down in power save, if an external clock signal is used. The charge pump enters the weak 1x mode using a passive current-limited keep-alive switch, which keeps the output voltage at the battery level to reduce output-voltage transients.

During program execution, the LP5569 device can enter power save if there is no PWM activity in any of the LED driver outputs. To prevent short power-save sequences during program execution, the device has an instruction look-ahead filter. In power-save mode, program execution continues without interruption. When an instruction that requires PWM activity is executed, a fast internal start-up sequence is started automatically.

#### 8.3.5 Protection Features

#### 8.3.5.1 Thermal Shutdown (TSD)

The LP5569 device implements a thermal shutdown mechanism to protect the device from damage due to overheating. When the junction temperature rises to 150°C (typical), the device switches into shutdown mode. The LP5569 device releases thermal shutdown when the junction temperature of the device decreases to 130°C (typical).

Thermal shutdown is most often triggered by self-heating, which occurs when there is excessive power dissipation in the device and/or insufficient thermal dissipation. LP5569 power dissipation increases with increased output current and input voltage. When self-heating brings on thermal shutdown, thermal cycling is the typical result. Thermal cycling is the repeating process where the part self-heats, enters thermal shutdown (where internal power dissipation is practically zero), cools, turns on, and then heats up again to the thermal shutdown threshold. Thermal cycling is recognized by a pulsing output voltage and can be stopped by reducing the internal power dissipation (reduce input voltage and/or output current) or the ambient temperature. If thermal cycling occurs under desired operating conditions, thermal dissipation performance must be improved to accommodate the power dissipation of the LP5569 device. The QFN package is designed to have excellent thermal properties that, when soldered to a PCB designed to aid thermal dissipation, allows the LP5569 device to operate under very demanding power-dissipation conditions.

### 8.3.5.2 Undervoltage Lockout (UVLO)

The LP5569 device has an internal comparator that monitors the voltage at VIN. If the input voltage drops to 2.2 V (nominal), undervoltage is detected, the LED outputs and the charge pump shut down, and the corresponding fault bit is set in the fault register. Hysteresis is implemented for the threshold level to avoid continuous triggering of a fault when the threshold is reached. If the input voltage rises above 2.3 V (nominal), the LP5569 device resumes normal operation.

#### 8.3.5.3 Power-On Reset (POR)

The LP5569 device has internal comparators that monitor the voltages at VIN and V1P8. When  $V_{VIN}$  is below 2.2 V or V1P8 is below 1.3 V, reset is active and the LP5569 device is in the DISABLED state.

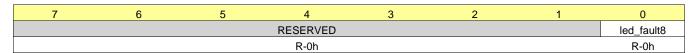

#### 8.3.5.4 LED Fault Detection

The LP5569 device contains both open-LED and shorted-LED fault detection. These fault detections are designed to be used in production-level testing and not normal operation. For the fault flags to operate, they must be enabled via the MISC2 register (address 33h) LED\_OPEN\_TEST and LED\_SHORT\_TEST bits. The fault flags are shared by both open-LED and shorted-LED tests so only one can be enabled at a time. The default LED-fault status is ready in the LED\_FAULT1 and LED\_FAULT2 registers (addresses 81h and 82h). The following sections detail the proper procedure for reading back open and short faults in the LED strings.

#### 8.3.5.4.1 Open LED

The LP5569 device features one fault flag per LED, indicating one or more of the active low-voltage LED strings are open. An open in a low-voltage LED string is flagged if the voltage at the input to any active low-voltage current sink goes below the drv\_headroom[1:0] setting in the MISC2 register. The procedure for detecting an open-LED fault is:

- 1. Set the LP5569 device in the STANDBY state.

- 2. Configure the charge pump in the 1.5x mode.

- 3. Set the LED\_OPEN\_TEST bit = 1 in the MISC2 register (address 33h).

- 4. Set the chip\_en bit = 1 in the CONTROL register (address 0h) with the LP5569 device in the NORMAL state.

- Wait at least 500 µs.

- 6. Enable all LEDs, and set all LEDs to 100% brightness.

- 7. Wait at least 500 µs.

- 8. Check the fault status of the LED\_FAULT1 and LED\_FAULT2 registers.

- 9. Set the LED OPEN TEST bit = 0 in the MISC2 register (address 33h).

- 10. Set all LEDs to 0% brightness.

#### 8.3.5.4.2 Shorted LED

The LP5569 device features one fault flag per LED, indicating when any active LED is shorted (anode to cathode). During the LED short test, the charge pump is forced to the  $1\times$  mode. A short in the LED is determined when the LED voltage ( $V_{IN} - V_{LEDx}$ ) falls below 1 V. The procedure for detecting a shorted-LED fault is:

- 1. Set the LP5569 device in the STANDBY state.

- 2. Configure the charge pump in the 1x mode, set LED PWM (0x16–0x1E) and LED current (0x22–0x2A) to maximum value, depending on the LED channel being tested.

- 3. Set the chip\_en bit in the CONFIG register = 1 and the LP5569 device to the NORMAL state.

- 4. Wait at least 500 µs.

- 5. Enable all LEDs, and set brightness to 100%.

- 6. Set the LED\_SHORT\_TEST bit = 1 in the MISC2 register (address 33h).

- 7. Wait at least 500 µs.

- 8. Check the fault status of the LED Fault1 and LED Fault2 registers.

- 9. Set the LED\_SHORT\_TEST bit = 0 in in the MISC2 register (address 33h).

- 10. Set all LEDs to 0% brightness.

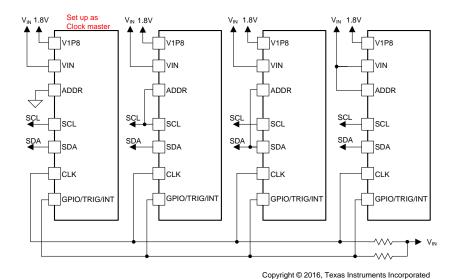

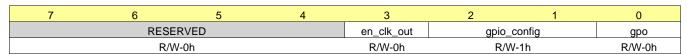

## 8.3.6 Clock Generation and Synchronization

The LP5569 device can generate a 32-kHz clock signal and use it for synchronizing multiple devices. The CLK pin is configured as an input by default. When the EN\_CLK\_OUT bit = 1 in the IO\_CONTROL register (address 3Dh) the LP5569 device drives the CLK pin using its 32-kHz oscillator.

图 19. Synchronizing Multiple Devices Using the Clock Generator

#### 8.3.7 GPIO/TRIG/INT Multifunctional I/O

The GPIO/TRIG/INT pin is configured by the GPIO\_CONFIG bits in the IO\_CONTROL register (address 3Dh). The default configuration for this pin is the INT function.

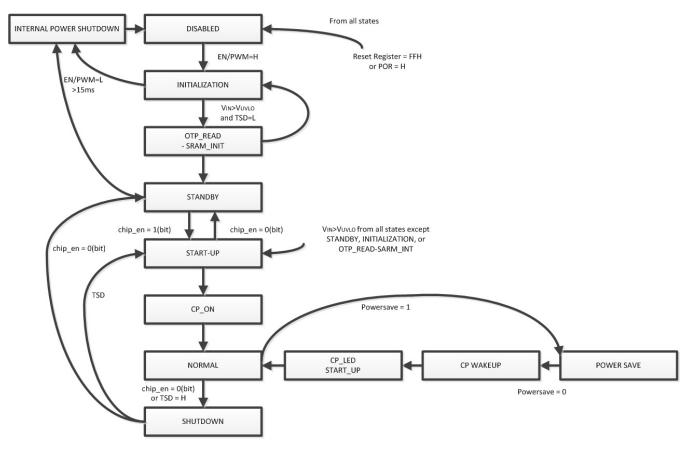

#### 8.4 Device Functional Modes

## 8.4.1 Modes Of Operation

- CP\_LED\_STARTUP: LED drivers are enabled. The device enters NORMAL after 300 µs (typical).

- **CP\_ON:** Charge pump is enabled per CP\_MODE bits, and charge-pump output voltage is within regulation after 300 µs (typical).

- CP\_WAKEUP After the power-save condition is no longer met, the device enters the CP\_WAKEUP state. The device enters CP\_LED\_STARTUP after 100 µs (typical).

- **DISABLED:** The device enters this state when logic receives POR or the EN/PWM pin is low for longer than 15 ms (typical). The internal logic is disabled in this state to minimize power consumption. The mode changes to INITIALIZATION when a rising edge has been detected in the EN/PWM pin and TSD is inactive.

- **INITIALIZATION:** This state duration is 2 ms (typical). The device enters the OTP\_READ–SRAM\_INIT state if  $V_{VIN}$  is above the  $V_{UVLO}$  level, and the temperature is below TSD. If  $V_{VIN}$  is below  $V_{UVLO}$  or TSD is active, the device remains in INITIALIZATION unless EN/PWM is low for 15 ms (typical), then the device enters the DISABLED mode.

- INTERNAL POWER SHUTDOWN: In INTERNAL POWER SHUTDOWN mode, the internal LDO is shutdown.

- **NORMAL:** After startup has been completed the device enters the NORMAL mode. Users can drive LEDs and execute programs in this mode.

- **OTP\_READ SRAM\_INIT:** The OTP\_READ mode is followed by SRAM\_INIT, which initializes SRAM. When initialization is complete, the device enters the STANDBY state. If V<sub>IN</sub> is below V<sub>UVLO</sub> while in this state, the device returns to INITIALIZATION.

- **POWER SAVE:** In POWER SAVE mode, analog blocks are disabled to minimize power consumption. After the power-save condition is no longer met, the device exits the POWER SAVE mode. See *Automatic Power-Save Mode* section for further information.

- **SHUTDOWN:** During shutdown, the charge-pump and LED drivers are disabled. The device enters the shutdown state if disabled (chip\_en = 0) or if a TSD fault is active. The device enters STANDBY after 1 ms (typical).

- **STANDBY:** The STANDBY mode is a low-power-consumption mode and is entered if the register bit chip\_en is zero and Reset is not active. Register and SRAM access is available via I<sup>2</sup>C.

- **START-UP:** During a fault condition, device operation is halted, and the device waits in STARTUP mode until no faults are present. UVLO detection returns the device to STARTUP from all states with the exception of STANDBY, INITIALIZATION, and OTP\_READ SRAM\_INIT.

## Device Functional Modes (接下页)

图 20. LP5569 Function State Machine

## 8.5 Programming

#### 8.5.1 I<sup>2</sup>C Interface

The I<sup>2</sup>C-compatible two-wire serial interface provides access to the programmable functions and registers on the device. This protocol uses a two-wire interface for bidirectional communications between the devices connected to the bus. The two interface lines are the serial data line (SDA) and the serial clock line (SCL). Every device on the bus is assigned a unique address and acts as either a master or a slave depending on whether it generates or receives the serial clock, SCL. The SCL and SDA lines should each have a pullup resistor placed somewhere on the line and remain HIGH even when the bus is idle. Note: the CLK pin is not used for serial bus data transfer.

#### 8.5.1.1 Data Validity

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when clock signal is LOW.

图 21. Data Validity Diagram

#### 8.5.1.2 Start and Stop Conditions

START and STOP conditions classify the beginning and the end of the data transfer session. A START condition is defined as the SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The bus master always generates START and STOP conditions. The bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the bus master can generate repeated START conditions. First START and repeated START conditions are functionally equivalent.

## 8.5.1.3 Transferring Data

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data must be followed by an acknowledge bit. The acknowledge-related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LP5569 device pulls down the SDA line during the ninth clock pulse, signifying an acknowledge. The LP5569 device generates an acknowledge after each byte has been received.

There is one exception to the *acknowledge after every byte* rule. When the master is the receiver, it must indicate to the transmitter an end of data by not-acknowledging (*negative acknowledge*) the last byte clocked out of the slave. This *negative acknowledge* still includes the acknowledge clock pulse (generated by the master), but the SDA line is not pulled down.

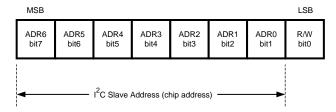

After the START condition, the bus master sends a device address. This address is seven bits long followed by an eighth bit which is a data direction bit (READ or WRITE). For the eighth bit, a 0 indicates a WRITE, and a 1 indicates a READ. The second byte selects the register to which the data is to be written. The third byte contains data to write to the selected register.

## 8.5.1.4 PC Slave Addressing

The LP5569 slave address is defined by connecting GND, SCL, SDA, or VIN to the ADDR pin. A total of four slave addresses can be realized by combinations when GND, SCL, SDA, or VIN is connected to the ADDR pin (see 表 2).

The LP5569 device is available in two versions (LP5569 and LP5569A). Each version has four possible address settings, which allows up to eight devices sharing the same I<sup>2</sup>C bus as shown in 表 2. Values are in 7-bit slave ID format. The LP5569 device responds to slave address 40h regardless of the setting of the ADDR pin and device version. Global writes to address 40h can be used for configuring all devices simultaneously. The LP5569 device supports global read using slave address 40h; however, the data read is only valid if all LP5569 devices on the I<sup>2</sup>C bus contain the same value in the register read.

| 表っ    | I P5569 | Slave-Address  | Combinations |

|-------|---------|----------------|--------------|

| 1X Z. | LFJJUJ  | Siave-Audi ess | COMBINATIONS |

| SLAVE ID    | VERSION | ADDR |

|-------------|---------|------|

| 32h and 40h |         | GND  |

| 33h and 40h |         | SCL  |

| 34h and 40h |         | SDA  |

| 35h and 40h |         | VIN  |

| 42h and 40h | A       | GND  |

| 43h and 40h | A       | SCL  |

| 44h and 40h | А       | SDA  |

| 45h and 40h | Α       | VIN  |

图 22. LP5569 Chip Address

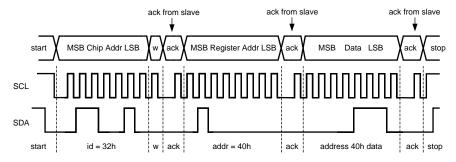

### 8.5.1.5 Control Register Write Cycle

- 1. The master device generates a start condition.

- 2. The master device sends the slave address (7 bits) and the data direction bit ( $R\overline{W} = 0$ ).

- 3. The slave device sends an acknowledge signal if the slave address is correct.

- 4. The master device sends the control register address (8 bits).

- 5. The slave device sends an acknowledge signal.

- 6. The master device sends the data byte to be written to the addressed register.

- 7. The slave device sends an acknowledge signal.

- 8. If the master device sends further data bytes, the control register address of the slave is incremented by 1 after the acknowledge signal. In order to reduce program load time, the LP5569 device supports address auto incrementation. The register address is incremented after each 8 data bits. For example, the whole program memory page can be written in one serial-bus write sequence.

- 9. The write cycle ends when the master device creates a stop condition.

图 23. Write Cycle (W = Write; SDA = 0)

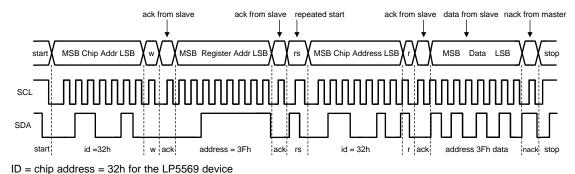

## 8.5.1.6 Control Register Read Cycle

- 1. The master device generates a start condition.

- 2. The master device sends the slave address (7 bits) and the data direction bit ( $R/\overline{W} = 0$ ).

- 3. The slave device sends an acknowledge signal if the slave address is correct.

- 4. The master device sends the control register address (8 bits).

- 5. The slave device sends an acknowledge signal.

- 6. The master device generates a repeated-start condition.

- 7. The master device sends the slave address (7 bits) and the data direction bit ( $R/\overline{W} = 1$ ).

- 8. The slave device sends an acknowledge signal if the slave address is correct.

- 9. The slave device sends the data byte from the addressed register.

- 10. If the master device sends an acknowledge signal, the control register address is incremented by 1. The slave device sends the data byte from the addressed register.

- 11. The read cycle ends when the master device does not generate an acknowledge signal after a data byte and generates a stop condition.

图 24. Read Cycle (R = Read; SDA = 1)

#### 8.5.1.7 Auto-Increment Feature

The auto-increment feature allows writing several consecutive registers within one transmission. Every time an 8-bit word is sent to the LP5569 device, the internal address index counter is incremented by 1, and the next register is written. The auto-increment feature is enabled by default and can be disabled by setting the EN\_AUTO\_INCR bit = 0 in the MISC register (address 2Fh).

### 8.5.2 Execution Engine Programming

The LP5569 device provides flexibility and programmability for dimming and sequencing control. Each LED can be controlled directly and independently through the serial bus, or LED drivers can be grouped together for preprogrammed flashing patterns.

The LP5569 device has three independent program execution engines, so it is possible to form three independently programmable LED banks. LED drivers can be grouped based on their function so that, for example, the first bank of drivers can be assigned to the keypad illumination, the second bank to the *funlights*, and the third group to the indicator LED(s). Each bank can contain 1 to 9 LED driver outputs. Instructions for program execution engines are stored in the program memory. The total amount of the program memory is 255 instructions, and the user can allocate the instructions as required by the engines; however, a single engine can only allocate up to ½ the memory (128 instructions).

## 8.5.2.1 SRAM Memory

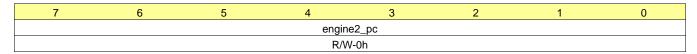

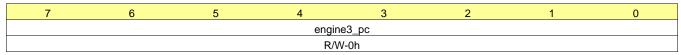

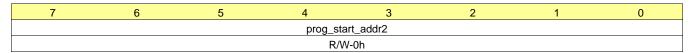

The LP5569 device has internal SRAM for the three LED engines. SRAM can contain up to 255 16-bit instructions (addresses 0 through 254) with a maximum size of 128 16-bit instructions for a single engine. SRAM memory address 255 is reserved and must not be allocated to any LED engine. Memory allocation among the three LED engines is done dynamically, so that each LED engine has a separate start address and program counter (PC) that are set in the ENGINEx\_PROG\_START registers (addresses 4Bh, 4Ch, 4Dh) and ENGINEx\_PC registers (addresses 30h, 31h, 32h). This allows flexible memory allocation among the LED engines, and multiple engines can recall the same memory address. The program counter uses relative memory addressing; when the PC is zero the engine is executing an instruction at its start address.

The SRAM is loaded via the I<sup>2</sup>C interface in 33-byte-length pages. The first byte contains the program-memory-page-select (address 4Fh) followed by up to 32 bytes containing compiled program execution engine instructions (address 50h thru 6Fh). Engines must be set to load the program mode (register 01h) before writing the SRAM.

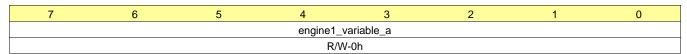

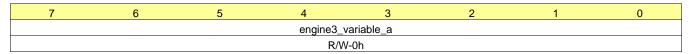

#### 8.5.2.2 Variables

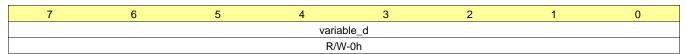

The LP5569 device has four LED engine variables which are divided into local and global variables. Variables A and B are engine-specific local variables and each of the three engines has separate A and B variables, so there is a total of six A and B variables. Variable A can be read and written via I²C registers 42h–44h. Local variable B is not available via I²C and can only be accessed by the LED engine. Variables C and D are global variables which are shared by all three LED engines. Global variable C is not available via I²C and can only be accessed by the LED engines. The D variable can be read and written via I²C register 3Eh. Variables are referenced to instructions with 2 bits, see 表 3 for details. Note that some instructions (ld, add, sub) can use only variables A, B, and C as target variables.

表 3. LED Engine Variables

| VARIABLE | BITS | LOCAL/GLOBAL |

|----------|------|--------------|

| Α        | 00   | Local        |

| В        | 01   | Local        |

| С        | 10   | Global       |

| D        | 11   | Global       |

#### 8.5.2.3 Instruction Set

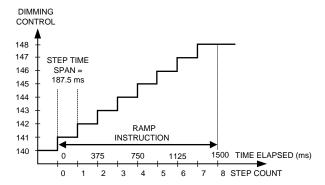

The LP5569 device has three independent programmable execution engines. All the program execution engines have their own program memory block allocated by the user. The maximum program size for any one engine is limited to 128 locations. At least one engine must be in the load-program mode with the engine-busy bit cleared before writing to any program memory address. Program execution is clocked with a 32.768-kHz clock. Instruction execution takes sixteen clock cycles (488 μs). This applies also to ramp and wait instructions where execution time is a multiple of 488 μs. This clock can be generated internally or an external clock can be supplied to the CLK pin. Using an external clock enables synchronization of LED timing to the external clock signal and is also more power-efficient. The supported instruction set is listed in  $\frac{1}{8}$ 4 through  $\frac{1}{8}$ 6. The LP5569 device is fully compatible with the LP5523 instruction set. A command compiler is available for easy sequence programming. With the command compiler it is possible to write sequences with simple ASCII commands, which are then converted to binary or hex format.

#### 表 4. LED Driver Instructions

| INSTRUCTION            | USAGE                                                                                                                                                                                                         | COMPILER EXAMPLE                                                            |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| ramp <sup>(1)</sup>    | Generate a programmable PWM ramp to mapped LED driver(s) from the current value to a new value in steps of +1 or -1 with programmed step time.                                                                | ramp 0.6, 255; ramp to full scale in 0.6 s                                  |

| ramp <sup>(2)</sup>    | ramp var1, prescale, var2 var1 is a variable (ra, rb, rc, rd); prescale is a boolean constant (pre = 0 or pre = 1); Var2 is a variable (ra, rb, rc, rd). Output PWM with increasing or decreasing duty cycle. | ld ra, 31 ld rb, 255 ramp ra, pre=0, +rb; ramp up to full scale over 3.9 s. |

| set_pwm <sup>(1)</sup> | Set PWM or current value to mapped LED driver(s), effective immediately.                                                                                                                                      | set_pwm 128; set duty cycle to 50%.                                         |

| set_pwm <sup>(2)</sup> | set_pwm var1 Var1 is a variable (ra, rb, rc, rd). Generate a continuous PWM output.                                                                                                                           | Id rc, 128; set_pwm rc; set PWM duty cycle to 50%.                          |

| wait                   | Wait for a given time. Time span is from 0.488 ms to 484 ms.                                                                                                                                                  | wait 0.4; wait for 0.4 s; wait for 0.4 s                                    |

<sup>(1)</sup> This opcode is used with numerical operands.

<sup>(2)</sup> This opcode is used with variables.

## 表 5. LED Mapping Instructions

| INSTRUCTION <sup>(1)</sup> | ACT <sup>(2)</sup> | USAGE                                                                              | COMPILER EXAMPLE                        |

|----------------------------|--------------------|------------------------------------------------------------------------------------|-----------------------------------------|

| load_start                 |                    | Define the LED mapping-table start address in SRAM.                                | load_start 01h; starting address at 01h |

| map_start                  | х                  | Define the LED mapping-table start address in SRAM and set that address active.    | map_start 01h; starting address at 01h  |

| load_end                   |                    | Define the last address of the LED mapping table in SRAM.                          | load_end 03h; last address at 03h       |

| map_sel                    | х                  | Connect one LED driver to the LED engine.                                          | map_sel 0; select LED0 as output        |

| map_clr                    | х                  | Clear the LED driver mappings in an engine                                         | map_clr                                 |

| map_next                   | х                  | Select the next address in the LED mapping table and set that address active.      | map_next                                |

| map_prev                   | х                  | Select the previous address in the LED mapping table and set that address active.  | map_prev                                |

| load_next                  |                    | Move the mapping-table pointer to the next address.                                | load_next                               |

| load_prev                  |                    | Move the mapping-table pointer to the previous address.                            | load_prev                               |

| load_addr                  |                    | Set the mapping-table pointer to the assigned address.                             | load_addr 02h; set pointer to 02h       |

| map_addr                   | х                  | Set the mapping-table pointer to the assigned address and set that address active. | map_addr 02h; set mapping to 02h        |

- (1) These instructions are compatible with the LP5523 and LP55231 mux\_\* LED mapping instructions.

(2) x The instruction activates LED mapping to the driver when the instruction is executed.

### 表 6. Branch Instructions

| INSTRUCTION               | USAGE                                                                                                                                                    | COMPILER EXAMPLE                                       |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

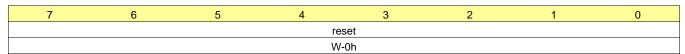

| rst                       | Reset program counter to zero.                                                                                                                           | Reset                                                  |

| branch <sup>(1)</sup>     | Branch to address. The number of loops can be set to a value or do an infinite loop.                                                                     | branch 20, loop1; do 20 loops to loop1 label           |

| branch <sup>(2)</sup>     | Branch to address. The loop count can be one of four variables A, B, C, or D.                                                                            | Id ra, 20 branch ra, loop1; do 20 loops to loop1 label |

| int                       | Send an interrupt to the host system by pulling the GPIO/TRIG/INT pin low.                                                                               | int                                                    |

| end                       | End program execution and reset the program counter to zero. Can also the set GPIO/TRIG/INT pin high and/or reset mapped LED PWM and engine LED mapping. | end; end and reset LEDs.                               |

| trigger                   | Wait or send trigger. The trigger can be sent or received from an external pin or another engine.                                                        | trigger w{e}; wait for external trigger                |

| trig_clear <sup>(3)</sup> | Clear pending triggers.                                                                                                                                  | trig_clear                                             |

| jne                       | Jump if not equal. A != B                                                                                                                                | Jump to loop1 if A != B: jne ra, rb, loop1             |

| jl                        | Jump if less. A < B                                                                                                                                      | Jump to loop1 if A < B : jl ra, rb, loop1              |

| jge                       | Jump if greater or equal. A ≥ B                                                                                                                          | Jump to loop1 if A >= B: jge ra, rb, loop1             |

| je                        | Jump if equal. A = B                                                                                                                                     | Jump to loop1 if A = B: je ra, rb, loop1               |

- This opcode is used with numerical operands.

- This opcode is used with variables.

This is a new instruction, not available in LP5523 or LP55231

#### 表 7. Data Transfer and Arithmetic

| INSTRUCTION        | USAGE                                                                                                                                                        | COMPILER EXAMPLE                                                 |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Id <sup>(1)</sup>  | Assign a value to a variable.                                                                                                                                | Id ra, 33; load value 33h to local variable A                    |

| add <sup>(1)</sup> | Add the 8-bit value to the variable value.                                                                                                                   | add ra, 11; add value 11h to local variable A                    |

| add <sup>(2)</sup> | Add the value of variable 3 (global variable D) to the value of variable 2 (global variable C) and store the result in variable 1 (local variable A).        | add ra, rc, rd; add the value in rd to rc and store in ra        |

| sub <sup>(1)</sup> | Subtract the 8-bit value from the variable value.                                                                                                            | sub ra, 11; subtract value 11h from local variable A             |

| sub <sup>(2)</sup> | Subtract the value of variable 3 (global variable D) from the value of variable 2 (global variable C) and store the result in variable 1 (local variable A). | sub ra, rc, rd; subtract the value in rd from rc and store in ra |

- (1) This opcode is used with numerical operands.

- (2) This opcode is used with variables.

#### 8.5.2.4 LED Driver Instructions

#### 表 8. LP5569 LED Driver Instructions

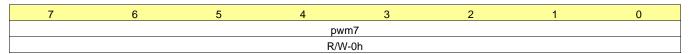

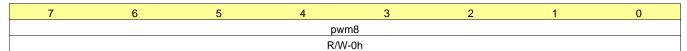

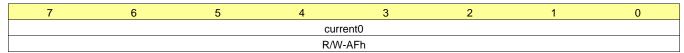

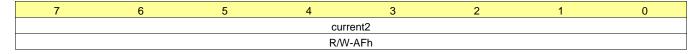

| INST.                  | Bit<br>[15] | Bit<br>[14]   | Bit<br>[13] | Bit<br>[12] | Bit<br>[11] | Bit<br>[10] | Bit<br>[9] | Bit<br>[8] | Bit<br>[7]        | Bit<br>[6] | Bit<br>[5]    | Bit<br>[4] | Bit<br>[3] | Bit<br>[2] | Bit<br>[1] | Bit<br>[0]    |