🕳 Order

Now

ZHCSA22C - OCTOBER 2011 - REVISED JUNE 2019

Support &

Community

20

# 采用 WSON 封装的 LMR10520 5.5V 输入电压、2A 降压稳压器

Technical

Documents

## 1 特性

- 输入电压范围: 3V 至 5.5V

- 输出电压范围: 0.6V 至 4.5V

- 输出电流高达 2A

- 1.6MHz (LMR10520X) 和 3MHz (LMR10520Y) 开 关频率

- 低关断 I<sub>Q</sub>: 30nA 典型值

- 内部软启动

- 内部补偿

- 电流模式 PWM 操作

- 热关断

- 微型整体解决方案降低了系统成本

- WSON (3 × 3 × 0.8mm) 封装

- 使用 LMR10520 并借助 WEBENCH<sup>®</sup> 电源设计器 创建定制设计方案

## 2 应用

- 从 3.3V 和 5V 电源轨到负载点的转换

- 空间受限型 应用

- 电池供电类设备

- 工业分布式电源 应用

- 功率计

- 便携式手持仪器

## 3 说明

🧷 Tools &

Software

LMR10520 稳压器是一款采用 6 引脚 WSON 封装的 单片、高频、PWM 降压直流/直流转换器。它提供所 有有效功能,从而在尽可能最小的 PCB 区域内提供具 有快速瞬态响应和精确调节功能的本地直流/直流转 换。LMR10520 具有最少的外部组件,因而易于使 用。该器件能够通过内部 150mΩ PMOS 开关来驱动 2A 负载,从而实现最佳的功率密度。该世界一流的控 制电路可实现低至 30ns 的导通时间,从而在整个 3V 至 5.5V 输入工作电压范围内支持极高频转换,最低输 出电压为 0.6V。LMR10520 进行了内部补偿,因此易 于使用,并且无需外部组件。尽管工作频率很高,但仍 可以轻松实现高达 93% 的效率。包括外部关断功能, 该功能具有 30nA 的超低待机电流。LMR10520 使用 电流模式控制和内部补偿在各种运行条件下提供高性能 调节。其他 功能 包括用于减小浪涌电流的内部软启动 电路、逐脉冲电流限制、热关断和输出过压保护。

器件信息<sup>(1)</sup>

| 器件型号     | 封装       | 封装尺寸(标称值)       |

|----------|----------|-----------------|

| LMR10520 | WSON (6) | 3.00mm × 3.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

| 目录 |

|----|

|----|

| 21100/ 22    | 0010BER 2011 | NEVIOLD JOINE 2015 |  |

|--------------|--------------|--------------------|--|

|              |              |                    |  |

|              |              |                    |  |

|              |              |                    |  |

|              |              |                    |  |

|              |              |                    |  |

|              |              |                    |  |

|              |              |                    |  |

| <u>ل</u> ا ا | L+ ML        |                    |  |

| 1 4          | 守性           |                    |  |

| 1 | 特性   |                               | 1              |

|---|------|-------------------------------|----------------|

| 2 | 应用   | l                             | 1              |

| 3 | 说明   |                               | 1              |

| 4 | 修订   | 历史记录                          | 2              |

| 5 | Pin  | Configuration and Functions   | 3              |

| 6 | Spe  | cifications                   | 4              |

|   | 6.1  | Absolute Maximum Ratings      | 4              |

|   | 6.2  | Recommended Operating Ratings | 4              |

|   | 6.3  | Electrical Characteristics    | 5              |

|   |      | Typical Characteristics       |                |

| 7 | Deta | ailed Description             | 8              |

|   | 7.1  | Overview                      | <mark>8</mark> |

|   | 7.2  | Functional Block Diagram      | 9              |

|   | 7.3  | Feature Description           | 10             |

| 8 | Арр  | lication and Implementation   | 11             |

|    | 8.1  | Application Information | 11 |

|----|------|-------------------------|----|

|    | 8.2  | Typical Application     | 11 |

| 9  | Layo | out                     | 19 |

|    | 9.1  | Layout Guidelines       | 19 |

|    | 9.2  | Layout Example          | 19 |

|    | 9.3  | Thermal Definitions     | 20 |

|    | 9.4  | WSON Package            | 21 |

| 10 | 器件   | 和文档支持                   | 22 |

|    | 10.1 | 器件支持                    | 22 |

|    | 10.2 | 接收文档更新通知                | 22 |

|    | 10.3 | 社区资源                    | 22 |

|    | 10.4 | 商标                      | 22 |

|    | 10.5 | 静电放电警告                  | 22 |

|    | 10.6 | Glossary                | 22 |

| 11 | 机械   | 、封装和可订购信息               | 23 |

|    |      |                         |    |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Changes from Revision B (April 2013) to Revision C | Page |

|----------------------------------------------------|------|

| • 仅有编辑更改; 添加了 WEBENCH 链接                           | 1    |

| Changes from Revision A (April 2013) to Revision B | Page |

| 已更改 将美国国家半导体数据表的布局更改为 TI 格式                        | 1    |

www.ti.com.cn

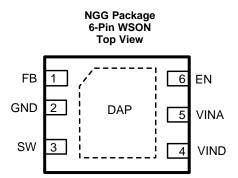

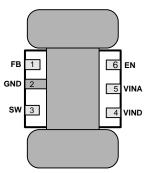

## 5 Pin Configuration and Functions

## **Pin Descriptions**

| PIN |                | DESCRIPTION                                                                                                         |  |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME           | DESCRIPTION                                                                                                         |  |

| 1   | FB             | Feedback pin. Connect to external resistor divider to set output voltage.                                           |  |

| 2   | GND            | Signal and power ground pin. Place the bottom resistor of the feedback network as close as possible to this pin.    |  |

| 3   | SW             | Switch node. Connect to the inductor and catch diode.                                                               |  |

| 4   | VIND           | Power input supply.                                                                                                 |  |

| 5   | VINA           | Control circuitry supply voltage. Connect VINA to VIND on PC board.                                                 |  |

| 6   | EN             | Enable control input. Logic high enables operation. Do not allow this pin to float or be greater than VINA + 0.3 V. |  |

| DAP | Die Attach Pad | Connect to system ground for low thermal impedance, but it cannot be used as a primary GND connection.              |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

See (1)(2).

| VIN                                                         | -0.5V to 7V     |

|-------------------------------------------------------------|-----------------|

| FB Voltage                                                  | -0.5V to 3V     |

| EN Voltage                                                  | -0.5V to 7V     |

| SW Voltage                                                  | -0.5V to 7V     |

| ESD Susceptibility                                          | 2kV             |

| Junction Temperature <sup>(3)</sup>                         | 150°C           |

| Storage Temperature                                         | −65°C to +150°C |

| Soldering Information                                       |                 |

| For soldering specifications: http://www.ti.com/lit/SNOA549 |                 |

(1) If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(2) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating Range indicates conditions for which the device is intended to be functional, but does not ensure specific performance limits. For ensured specifications and test conditions, see *Electrical Characteristics*.

(3) Thermal shutdown occurs if the junction temperature exceeds the maximum junction temperature of the device.

## 6.2 Recommended Operating Ratings

| VIN                  | 3V to 5.5V      |

|----------------------|-----------------|

| Junction Temperature | -40°C to +125°C |

## 6.3 Electrical Characteristics

$V_{IN} = 5$  V unless otherwise indicated under the **TEST CONDITIONS** column. Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in **boldface type** apply over the junction temperature ( $T_J$ ) range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. Minimum and Maximum limits are ensured through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only.<sup>(1)(2)</sup>

|                        | PARAMETER                                             | TEST CONDITIONS                  | MIN   | ТҮР   | MAX   | UNIT  |  |

|------------------------|-------------------------------------------------------|----------------------------------|-------|-------|-------|-------|--|

| $V_{FB}$               | Feedback Voltage                                      |                                  | 0.588 | 0.600 | 0.612 | V     |  |

| $\Delta V_{FB}/V_{IN}$ | Feedback Voltage Line Regulation                      | $V_{IN} = 3V$ to $5V$            |       | 0.02  |       | %/V   |  |

| Ι <sub>Β</sub>         | Feedback Input Bias Current                           |                                  |       | 0.1   | 100   | nA    |  |

|                        |                                                       | V <sub>IN</sub> Rising           |       | 2.73  | 2.90  | V     |  |

| UVLO                   | Undervoltage Lockout                                  | V <sub>IN</sub> Falling          | 1.85  | 2.3   |       |       |  |

|                        | UVLO Hysteresis                                       |                                  |       | 0.43  |       | V     |  |

| -                      |                                                       | LMR10520-X                       | 1.2   | 1.6   | 1.95  | N411- |  |

| F <sub>SW</sub>        | Switching Frequency                                   | LMR10520-Y                       | 2.25  | 3.0   | 3.75  | MHz   |  |

|                        | Mariana Data Quala                                    | LMR10520-X                       | 86%   | 94%   |       |       |  |

| D <sub>MAX</sub>       | Maximum Duty Cycle                                    | LMR10520-Y                       | 82%   | 90%   |       |       |  |

| D                      | Minimum Duty Quela                                    | LMR10520-X                       |       | 5%    |       |       |  |

| D <sub>MIN</sub>       | Minimum Duty Cycle                                    | LMR10520-Y                       |       | 7%    |       |       |  |

| R <sub>DS(ON)</sub>    | Switch On Resistance                                  |                                  |       | 150   |       | mΩ    |  |

| I <sub>CL</sub>        | Switch Current Limit                                  | V <sub>IN</sub> = 3.3V           | 2.4   | 3.25  |       | А     |  |

| 14                     | Shutdown Threshold Voltage                            |                                  |       |       | 0.4   | V     |  |

| $V_{EN_{TH}}$          | Enable Threshold Voltage                              |                                  | 1.8   |       |       | V     |  |

| I <sub>SW</sub>        | Switch Leakage                                        |                                  |       | 100   |       | nA    |  |

| I <sub>EN</sub>        | Enable Pin Current                                    | Sink/Source                      |       | 100   |       | nA    |  |

|                        | Quieses at Quart (quitabies)                          | LMR10520X V <sub>FB</sub> = 0.55 |       | 3.3   | 5     |       |  |

| Ι <sub>Q</sub>         | Quiescent Current (switching)                         | LMR10520Y V <sub>FB</sub> = 0.55 |       | 4.3   | 6.5   | mA    |  |

|                        | Quiescent Current (shutdown)                          | All Options V <sub>EN</sub> = 0V |       | 30    |       | nA    |  |

| $\theta_{JA}$          | Junction to Ambient<br>0 LFPM Air Flow <sup>(3)</sup> |                                  |       | 80    |       | °C/W  |  |

| $\theta_{JC}$          | Junction to Case                                      |                                  |       | 18    |       | °C/W  |  |

| T <sub>SD</sub>        | Thermal Shutdown Temperature                          |                                  |       | 165   |       | °C    |  |

(1) Minimum and Maximum limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely parametric norm.

(3) Applies for packages soldered directly onto a 3" × 3" PC board with 2 oz. copper on 4 layers in still air.

LMR10520 ZHCSA22C-OCTOBER 2011-REVISED JUNE 2019

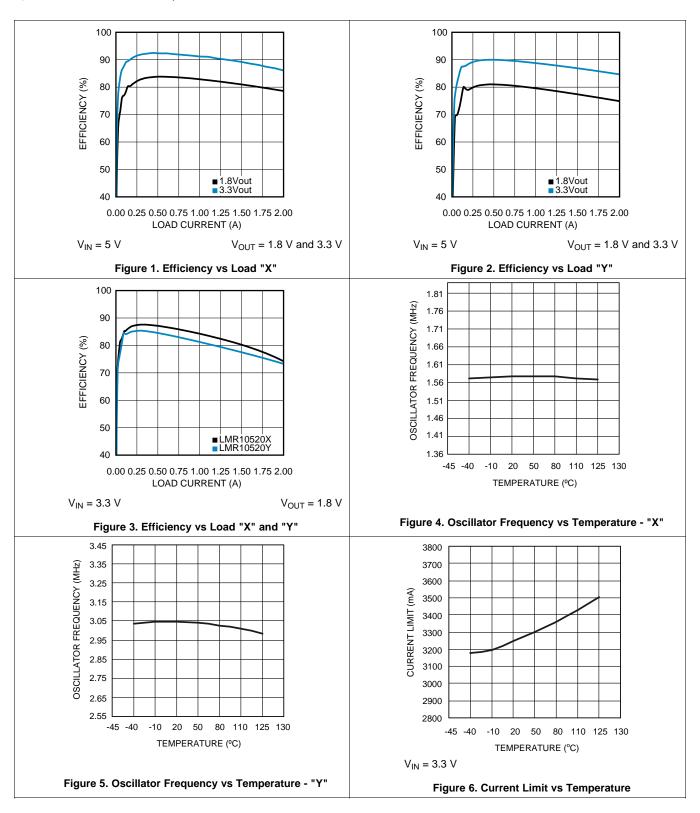

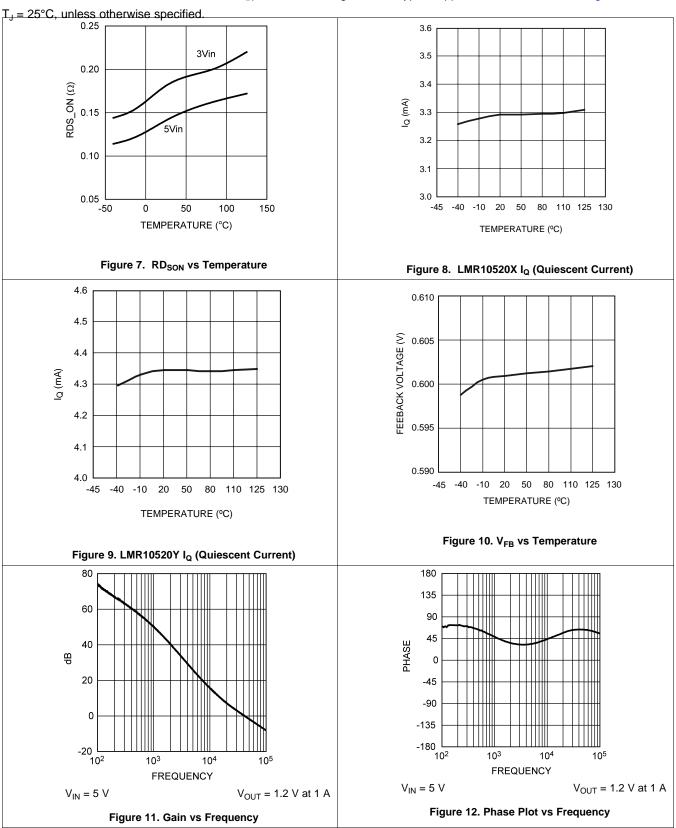

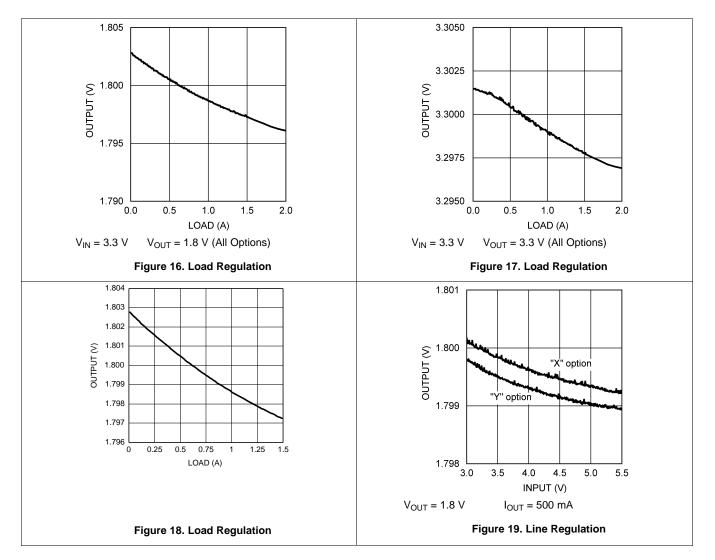

## 6.4 Typical Characteristics

Unless stated otherwise, all curves taken at  $V_{IN} = 5$  V with configuration in typical application circuit shown in Figure 14.  $T_J = 25^{\circ}$ C, unless otherwise specified.

## **Typical Characteristics (continued)**

Unless stated otherwise, all curves taken at  $V_{IN} = 5$  V with configuration in typical application circuit shown in Figure 14.

## 7 Detailed Description

## 7.1 Overview

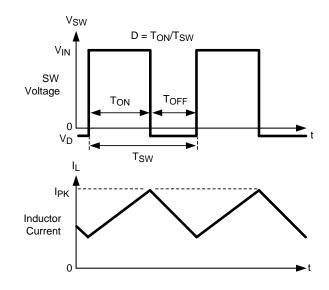

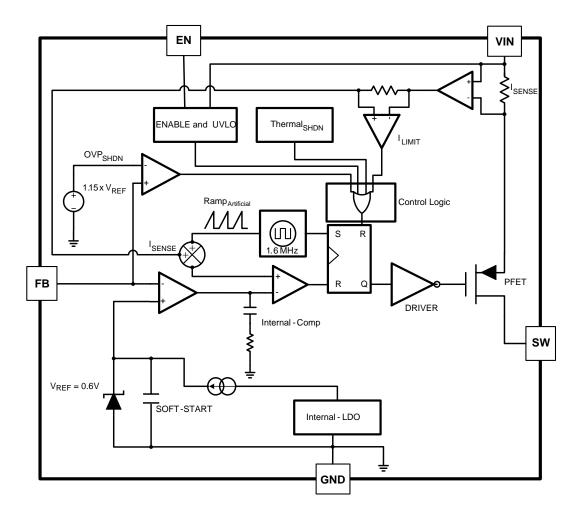

The following operating description of the LMR10520 refers to *Functional Block Diagram* and to the waveforms in Figure 13. The LMR10520 supplies a regulated output voltage by switching the internal PMOS control switch at constant frequency and variable duty cycle. A switching cycle begins at the falling edge of the reset pulse generated by the internal oscillator. When this pulse goes low, the output control logic turns on the internal PMOS control switch. During this on-time, the SW pin voltage ( $V_{SW}$ ) swings up to approximately  $V_{IN}$ , and the inductor current ( $I_L$ ) increases with a linear slope.  $I_L$  is measured by the current sense amplifier, which generates an output proportional to the switch current. The sense signal is summed with the regulator's corrective ramp and compared to the error amplifier's output, which is proportional to the difference between the feedback voltage and  $V_{REF}$ . When the PWM comparator output goes high, the output switch turns off until the next switching cycle begins. During the switch off-time, inductor current discharges through the Schottky catch diode, which forces the SW pin to swing below ground by the forward voltage ( $V_D$ ) of the Schottky catch diode. The regulator loop adjusts the duty cycle (D) to maintain a constant output voltage.

Figure 13. Typical Waveforms

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Soft-Start

This function forces  $V_{OUT}$  to increase at a controlled rate during start-up. During soft start, the error amplifier's reference voltage ramps from 0 V to its nominal value of 0.6 V in approximately 600 µs. This forces the regulator output to ramp up in a controlled fashion, which helps reduce inrush current.

## 7.3.2 Output Overvoltage Protection

The overvoltage comparator compares the FB pin voltage to a voltage that is 15% higher than the internal reference  $V_{REF}$ . Once the FB pin voltage goes 15% above the internal reference, the internal PMOS control switch is turned off, which allows the output voltage to decrease toward regulation.

## 7.3.3 Undervoltage Lockout

Undervoltage lockout (UVLO) prevents the LMR10520 from operating until the input voltage exceeds 2.73 V (typical). The UVLO threshold has approximately 430 mV of hysteresis, so the part will operate until  $V_{IN}$  drops below 2.3 V (typical). Hysteresis prevents the part from turning off during power-up if  $V_{IN}$  is non-monotonic.

## 7.3.4 Current Limit

The LMR10520 uses cycle-by-cycle current limiting to protect the output switch. During each switching cycle, a current limit comparator detects if the output switch current exceeds 2.5 A (typical), and turns off the switch until the next switching cycle begins.

## 7.3.5 Thermal Shutdown

Thermal shutdown limits total power dissipation by turning off the output switch when the IC junction temperature exceeds 165°C. After thermal shutdown occurs, the output switch doesn't turn on until the junction temperature drops to approximately 150°C.

## 8 Application and Implementation

## NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

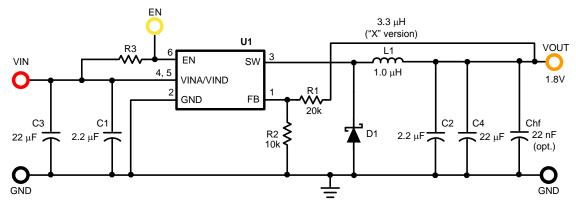

The LMR10520 is internally compensated, so it is simple to use and requires few external components. The regulator has a preset switching frequency of 1.6 MHz or 3 MHz. This high frequency allows the LMR10520 to operate with small surface mount capacitors and inductors, resulting in a DC/DC converter that requires a minimum amount of board space

## 8.2 Typical Application

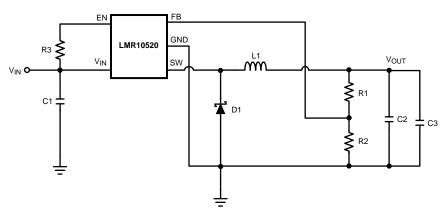

Figure 14. Typical Application Schematic

## 8.2.1 Detailed Design Procedure

## 8.2.1.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMR10520 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- · Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

## **Typical Application (continued)**

## 8.2.1.2 Inductor Selection

The duty cycle (D) can be approximated quickly using the ratio of output voltage (V<sub>O</sub>) to input voltage (V<sub>IN</sub>):

The catch diode (D1) forward-voltage drop and the voltage drop across the internal PMOS must be included to calculate a more accurate duty cycle. Calculate D by using the following formula:

$$D = \frac{V_{OUT} + V_D}{V_{IN} + V_D - V_{SW}}$$

(1)

V<sub>SW</sub> can be approximated by:

$$V_{SW} = I_{OUT} \times R_{DSON}$$

(2)

(3)

The diode forward drop  $(V_D)$  can range from 0.3 V to 0.7 V depending on the quality of the diode. The lower the  $V_D$ , the higher the operating efficiency of the converter. The inductor value determines the output ripple current. Lower inductor values decrease the size of the inductor, but increase the output ripple current. An increase in the inductor value will decrease the output ripple current.

One must ensure that the minimum current limit (2.4A) is not exceeded, so the peak current in the inductor must be calculated. The peak current ( $I_{LPK}$ ) in the inductor is calculated by:

$$I_{LPK} = I_{OUT} + \Delta i_L$$

$$\frac{V_{\rm IN} - V_{\rm OUT}}{L} = \frac{2\Delta i_{\rm L}}{DT_{\rm S}}$$

<sup>(4)</sup>

In general,

$$\Delta i_L = 0.1 \text{ x} (I_{OUT}) \rightarrow 0.2 \text{ x} (I_{OUT})$$

(5)

If  $\Delta i_L = 20\%$  of 2 A, the peak current in the inductor will be 2.4A. The minimum ensured current limit over all operating conditions is 2.4 A. One can either reduce  $\Delta i_L$ , or make the engineering judgment that zero margin will be safe enough. The typical current limit is 3.25 A.

The LMR10520 operates at frequencies allowing the use of ceramic output capacitors without compromising transient response. Ceramic capacitors allow higher inductor ripple without significantly increasing output ripple. See the *Output Capacitor* section for more details on calculating output voltage ripple. Now that the ripple current is determined, the inductance is calculated by:

$$L = \left(\frac{DT_{S}}{2\Delta i_{L}}\right) \times (V_{IN} - V_{OUT})$$

where

$$T_{S} = \frac{1}{f_{S}}$$

(7)

When selecting an inductor, make sure that it is capable of supporting the peak output current without saturating. Inductor saturation will result in a sudden reduction in inductance and prevent the regulator from operating correctly. Because of the speed of the internal current limit, the peak current of the inductor need only be specified for the required maximum output current. For example, if the designed maximum output current is 1 A, and the peak current is 1.25 A, then the inductor should be specified with a saturation current limit of > 1.25 A. There is no need to specify the saturation or peak current of the inductor at the 3.25 A typical switch current limit. The difference in inductor size is a factor of 5. Because of the operating frequency of the LMR10520, ferrite based inductors are preferred to minimize core losses. This presents little restriction since the variety of ferrite-based inductors is huge. Lastly, inductors with lower series resistance ( $R_{DCR}$ ) will provide better operating efficiency. For recommended inductors, see *Other System Examples*.

## 8.2.1.3 Input Capacitor

An input capacitor is necessary to ensure that  $V_{IN}$  does not drop excessively during switching transients. The primary specifications of the input capacitor are capacitance, voltage, RMS current rating, and equivalent series inductance (ESL). The recommended input capacitance is 22 µF. The input voltage rating is specifically stated by the capacitor manufacturer. Make sure to check any recommended deratings and also verify if there is any significant change in capacitance at the operating input voltage and the operating temperature. The input capacitor maximum RMS input current rating (I<sub>RMS-IN</sub>) must be greater than:

$$I_{\text{RMS}_{\text{IN}}} \sqrt{D \left[ I_{\text{OUT}}^2 (1-D) + \frac{\Delta i^2}{3} \right]}$$

(8)

Neglecting inductor ripple simplifies the above equation to:

$$I_{\rm RMS_IN} = I_{\rm OUT} \times \sqrt{D(1 - D)}$$

<sup>(9)</sup>

It can be shown from the above equation that maximum RMS capacitor current occurs when D = 0.5. Always calculate the RMS at the point where the duty cycle D is closest to 0.5. The ESL of an input capacitor is usually determined by the effective cross sectional area of the current path. A large leaded capacitor will have high ESL and a 0805 ceramic chip capacitor will have very low ESL. At the operating frequencies of the LMR10520, leaded capacitors may have an ESL so large that the resulting impedance ( $2\pi$ fL) will be higher than that required to provide stable operation. As a result, surface mount capacitors are strongly recommended.

Sanyo POSCAP, Tantalum or Niobium, Panasonic SP, and multilayer ceramic capacitors (MLCC) are all good choices for both input and output capacitors and have very low ESL. For MLCCs it is recommended to use X7R or X5R type capacitors due to their tolerance and temperature characteristics. Consult capacitor manufacturer datasheets to see how rated capacitance varies over operating conditions.

## 8.2.1.4 Output Capacitor

The output capacitor is selected based upon the desired output ripple and transient response. The initial current of a load transient is provided mainly by the output capacitor. The output ripple of the converter is:

$$\Delta V_{OUT} = \Delta I_{L} \left( \mathsf{R}_{\mathsf{ESR}} + \frac{1}{8 \, \mathsf{x} \, \mathsf{F}_{\mathsf{SW}} \, \mathsf{x} \, \mathsf{C}_{\mathsf{OUT}}} \right) \tag{10}$$

When using MLCCs, the ESR is typically so low that the capacitive ripple may dominate. When this occurs, the output ripple will be approximately sinusoidal and 90° phase shifted from the switching action. Given the availability and quality of MLCCs and the expected output voltage of designs using the LMR10520, there is really no need to review any other capacitor technologies. Another benefit of ceramic capacitors is their ability to bypass high frequency noise. A certain amount of switching edge noise will couple through parasitic capacitances in the inductor to the output. A ceramic capacitor will bypass this noise while a tantalum will not. Since the output capacitor is one of the two external components that control the stability of the regulator control loop, most applications will require a minimum of  $22 \,\mu$ F of output capacitance. Capacitance often, but not always, can be increased significantly with little detriment to the regulator stability. Like the input capacitor, recommended multilayer ceramic capacitors are X7R or X5R types.

## **Typical Application (continued)**

#### 8.2.1.5 Catch Diode

The catch diode (D1) conducts during the switch off-time. A Schottky diode is recommended for its fast switching times and low forward voltage drop. The catch diode should be chosen so that its current rating is greater than:

$$I_{D1} = I_{OUT} \times (1-D)$$

(11)

The reverse breakdown rating of the diode must be at least the maximum input voltage plus appropriate margin. To improve efficiency, choose a Schottky diode with a low forward voltage drop.

## 8.2.1.6 Output Voltage

The output voltage is set using the following equation where R2 is connected between the FB pin and GND, and R1 is connected between  $V_0$  and the FB pin. A good value for R2 is  $10k\Omega$ . When designing a unity gain converter (Vo = 0.6V), R1 should be between  $0\Omega$  and  $100\Omega$ , and R2 should be equal or greater than  $10k\Omega$ .

$$R1 = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) \times R2$$

$$V_{REF} = 0.60V$$

(12)

(13)

#### 8.2.1.7 Calculating Efficiency and Junction Temperature

The complete LMR10520 DC/DC converter efficiency can be calculated in the following manner.

$$\eta = \frac{\mathsf{P}_{\mathsf{OUT}}}{\mathsf{P}_{\mathsf{IN}}}$$

(14)

Or

$$\eta = \frac{P_{OUT}}{P_{OUT} + P_{LOSS}}$$

(15)

Calculations for determining the most significant power losses are shown below. Other losses totaling less than 2% are not discussed.

Power loss ( $P_{LOSS}$ ) is the sum of two basic types of losses in the converter: switching and conduction. Conduction losses usually dominate at higher output loads, whereas switching losses remain relatively fixed and dominate at lower output loads. The first step in determining the losses is to calculate the duty cycle (D):

$$D = \frac{V_{OUT} + V_D}{V_{IN} + V_D - V_{SW}}$$

(16)

V<sub>SW</sub> is the voltage drop across the internal PFET when it is on, and is equal to:

$$V_{SW} = I_{OUT} \times R_{DSON}$$

$V_{\text{D}}$  is the forward voltage drop across the Schottky catch diode. It can be obtained from the diode manufactures Electrical Characteristics section. If the voltage drop across the inductor ( $V_{\text{DCR}}$ ) is accounted for, the equation becomes:

$$D = \frac{V_{OUT} + V_D + V_{DCR}}{V_{IN} + V_D + V_{DCR} - V_{SW}}$$

(18)

The conduction losses in the free-wheeling Schottky diode are calculated as follows:

$$P_{\text{DIODE}} = V_{\text{D}} \times I_{\text{OUT}} \times (1-D)$$

(19)

Often this is the single most significant power loss in the circuit. Care should be taken to choose a Schottky diode that has a low forward voltage drop.

(16)

(17)

## **Typical Application (continued)**

Another significant external power loss is the conduction loss in the output inductor. The equation can be simplified to:

$$P_{\rm IND} = I_{\rm OUT}^2 \times R_{\rm DCR}$$

<sup>(20)</sup>

The LMR10520 conduction loss is mainly associated with the internal PFET:

,

$$P_{\text{COND}} = (I_{\text{OUT}}^2 \times D) \left( 1 + \frac{1}{3} \times \left( \frac{\Delta i_{\text{L}}}{I_{\text{OUT}}} \right)^2 \right) R_{\text{DSON}}$$

(21)

If the inductor ripple current is fairly small, the conduction losses can be simplified to:

$$P_{COND} = I_{OUT}^2 \times R_{DSON} \times D$$

<sup>(22)</sup>

Switching losses are also associated with the internal PFET. They occur during the switch on and off transition periods, where voltages and currents overlap resulting in power loss. The simplest means to determine this loss is to empirically measuring the rise and fall times (10% to 90%) of the switch at the switch node.

Switching Power Loss is calculated as follows:

| P <sub>SWR</sub> = 1/2(V <sub>IN</sub> x I <sub>OUT</sub> x F <sub>SW</sub> x T <sub>RISE</sub> ) | (23) |

|---------------------------------------------------------------------------------------------------|------|

| P <sub>SWF</sub> = 1/2(V <sub>IN</sub> x I <sub>OUT</sub> x F <sub>SW</sub> x T <sub>FALL</sub> ) | (24) |

| $P_{SW} = P_{SWR} + P_{SWF}$                                                                      | (25) |

| Another loss is the power required for operation of the internal circuitry:                       |      |

$$P_Q = I_Q \times V_{IN}$$

I<sub>Q</sub> is the quiescent operating current, and is typically around 3.3 mA for the 1.6-MHz frequency option.

Typical application power losses are:

| V <sub>IN</sub>                                 | 5 V                      |                    |         |  |

|-------------------------------------------------|--------------------------|--------------------|---------|--|

| V <sub>OUT</sub>                                | 3.3 V                    | P <sub>OUT</sub>   | 5.78 W  |  |

| I <sub>OUT</sub>                                | 1.75 A                   |                    |         |  |

| V <sub>D</sub>                                  | 0.45 V                   | P <sub>DIODE</sub> | 262 mW  |  |

| F <sub>SW</sub>                                 | 1.6 MHz                  |                    |         |  |

| l <sub>Q</sub>                                  | 3.3 mA                   | Pq                 | 16.5 mW |  |

| T <sub>RISE</sub>                               | 4 ns                     | P <sub>SWR</sub>   | 28 mW   |  |

| T <sub>FALL</sub>                               | 4 ns                     | P <sub>SWF</sub>   | 28 mW   |  |

| R <sub>DS(ON)</sub>                             | 150 mΩ                   | P <sub>COND</sub>  | 306 mW  |  |

| IND <sub>DCR</sub>                              | 50 mΩ                    | P <sub>IND</sub>   | 153 mW  |  |

| D                                               | 0.667                    | P <sub>LOSS</sub>  | 794 mW  |  |

| η                                               | 88%                      | PINTERNAL          | 379 mW  |  |

| $\Sigma P_{COND} + P_{SW} + P_{DIODE} + P_{II}$ | $_{ND} + P_Q = P_{LOSS}$ |                    | (2      |  |

## **Table 1. Power Loss Tabulation**

$\Sigma P_{COND} + P_{SW} + P_{DIODE} + P_{IND} + P_{Q} = P_{LOSS}$  $\Sigma P_{COND} + P_{SWF} + P_{SWR} + P_{Q} = P_{INTERNAL}$

$P_{INTERNAL} = 379 mW$

(28)

(29)

(26)

LMR10520 ZHCSA22C-OCTOBER 2011-REVISED JUNE 2019

www.ti.com.cn

## 8.2.2 Application Curves

#### 8.2.3 Other System Examples

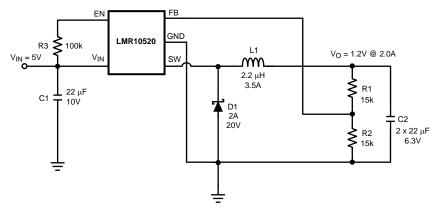

#### 8.2.3.1 LMR10520X Design Example 1

Figure 20. LMR10520x (1.6 MHz):  $V_{IN}$  = 5 V,  $V_{OUT}$  = 1.2 V at 2 A

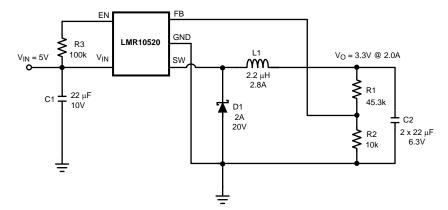

## 8.2.3.2 LMR10510X Design Example 2

Figure 21. LMR10520X (1.6 MHz):  $V_{IN}$  = 5 V,  $V_{OUT}$  = 3.3 V at 2 A

TEXAS INSTRUMENTS

www.ti.com.cn

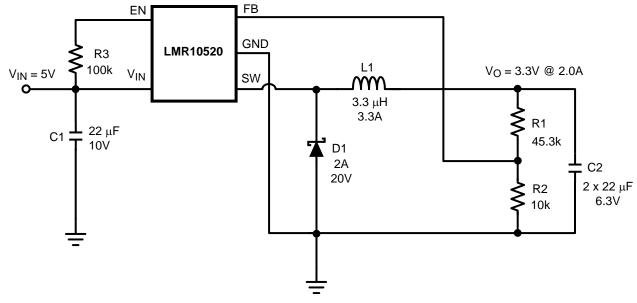

## 8.2.3.3 LMR10510Y Design Example 3

Figure 22. LMR10520Y (3 MHz):  $V_{IN}$  = 5 V,  $V_{OUT}$  = 3.3 V at 2 A

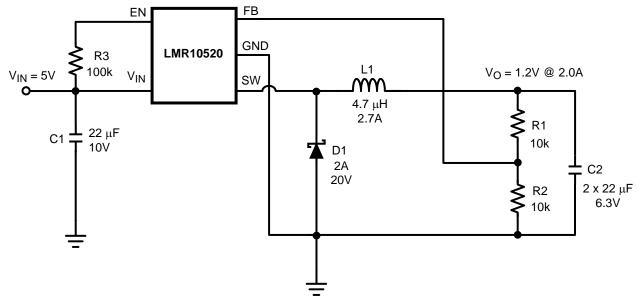

8.2.3.4 LMR10510Y Design Example 4

Figure 23. LMR10520Y (3 MHz):  $V_{IN}$  = 5 V,  $V_{OUT}$  = 1.2 V at 2 A

## 9 Layout

## 9.1 Layout Guidelines

When planning layout there are a few things to consider when trying to achieve a clean, regulated output. The most important consideration is the close coupling of the GND connections of the input capacitor and the catch diode D1. Place these ground ends close to one another and be connected to the GND plane with at least two through-holes. Place these components as close to the IC as possible. Next in importance is the location of the GND connection of the output capacitor, which should be near the GND connections of CIN and D1. There should be a continuous ground plane on the bottom layer of a two-layer board except under the switching node island. The FB pin is a high impedance node and care should be taken to make the FB trace short to avoid noise pickup and inaccurate regulation. Place the feedback resistors as close as possible to the GND of R1 placed as close as possible to the GND of the IC. Route the  $V_{\rm IN}$ , SW and  $V_{\rm OUT}$  traces, so they should be as short and wide as possible. However, making the traces wide increases radiated noise, so the designer must make this trade-off. Radiated noise can be decreased by choosing a shielded inductor. The remaining components should also be placed as close as possible to the IC. See

Application Note AN-1229 for further considerations and the LMR10520 demo board as an example of a good layout.

## 9.2 Layout Example

Figure 24. 6-Lead WSON PCB Dog-Bone Layout

## 9.3 Thermal Definitions

$T_{1}$  = Chip junction temperature

$T_A$  = Ambient temperature

$R_{\theta,IC}$  = Thermal resistance from chip junction to device case

$R_{\theta,JA}$  = Thermal resistance from chip junction to ambient air

Heat in the LMR10520 due to internal power dissipation is removed through conduction and/or convection.

Conduction: Heat transfer occurs through cross sectional areas of material. Depending on the material, the transfer of heat can be considered to have poor to good thermal conductivity properties (insulator vs. conductor).

Heat Transfer goes as:

Silicon  $\rightarrow$  package  $\rightarrow$  lead frame  $\rightarrow$  PCB

Convection: Heat transfer is by means of airflow. This could be from a fan or natural convection. Natural convection occurs when air currents rise from the hot device to cooler air.

Thermal impedance is defined as:

$$R_{\theta} = \frac{\Delta T}{Power}$$

(30)

Thermal impedance from the silicon junction to the ambient air is defined as:

$$\mathsf{R}_{\theta \mathsf{J}\mathsf{A}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{A}}}{\mathsf{Power}}$$

(31)

The PCB size, weight of copper used to route traces and ground plane, and number of layers within the PCB can greatly effect R<sub>0JA</sub>. The type and number of thermal vias can also make a large difference in the thermal impedance. Thermal vias are necessary in most applications. They conduct heat from the surface of the PCB to the ground plane. Four to six thermal vias should be placed under the exposed pad to the ground plane.

Thermal impedance also depends on the thermal properties of the application operating conditions (Vin, Vo, Io etc), and the surrounding circuitry.

## Silicon Junction Temperature Determination Method 1:

To accurately measure the silicon temperature for a given application, two methods can be used. The first method requires the user to know the thermal impedance of the silicon junction to case temperature.

R<sub>e.IC</sub> is approximately 18°C/Watt for the 6-pin WSON package with the exposed pad. Knowing the internal dissipation from the efficiency calculation given previously, and the case temperature, which can be empirically measured on the bench we have:

$$R_{\theta JC} = \frac{T_J - T_C}{Power}$$

where

$T_{c}$  is the temperature of the exposed pad and can be measured on the bottom side of the PCB. (32)

Therefore:

20

| $T_j = (R_{\theta JC} \times P_{LOSS}) + T_C$ | (33) |

|-----------------------------------------------|------|

| From the previous example:                    |      |

| $T_i = (R_{AIC} \times P_{INTERNAL}) + T_C$   | (34) |

| $f_{j} = (f_{ij} c_{ij} c_{ij$ | (01) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $T_j = 18^{\circ}C/W \times 0.213W + T_C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (35) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

The second method can give a very accurate silicon junction temperature.

Copyright © 2011–2019, Texas Instruments Incorporated

## **Thermal Definitions (continued)**

The first step is to determine  $R_{\theta JA}$  of the application. The LMR10520 has over-temperature protection circuitry. When the silicon temperature reaches 165°C, the device stops switching. The protection circuitry has a hysteresis of about 15°C. Once the silicon temperature has decreased to approximately 150°C, the device will start to switch again. Knowing this, the  $R_{\theta JA}$  for any application can be characterized during the early stages of the design one may calculate the  $R_{\theta JA}$  by placing the PCB circuit into a thermal chamber. Raise the ambient temperature in the given working application until the circuit enters thermal shutdown. If the SW-pin is monitored, it will be obvious when the internal PFET stops switching, indicating a junction temperature of 165°C. Knowing the internal power dissipation from the above methods, the junction temperature, and the ambient temperature  $R_{\theta JA}$  can be determined.

$$R_{\theta JA} = \frac{165^{\circ} - Ta}{P_{INTERNAL}}$$

(36)

Once this is determined, the maximum ambient temperature allowed for a desired junction temperature can be found.

An example of calculating  $R_{\theta JA}$  for an application using the LMR10520 is shown below.

A sample PCB is placed in an oven with no forced airflow. The ambient temperature was raised to 120°C, and at that temperature, the device went into thermal shutdown.

From the previous example:

$$\mathsf{P}_{\mathsf{INTERNAL}} = 379 \; \mathsf{mW} \tag{37}$$

$$R_{\theta JA} = \frac{165^{\circ} C - 120^{\circ} C}{379 \text{ mW}} = 119^{\circ} C/W$$

(38)

Since the junction temperature must be kept below 125°C, then the maximum ambient temperature can be calculated as:

$$T_{j} - (R_{\theta JA} \times P_{LOSS}) = T_{A}$$

(39)

125°C - (119°C/W × 379 mW) = 80°C (40)

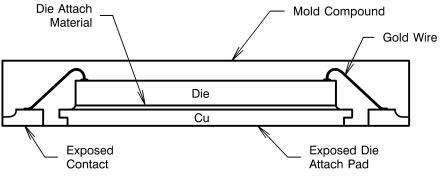

## 9.4 WSON Package

For certain high power applications, the PCB land may be modified to a "dog bone" shape (see Figure 24). By increasing the size of ground plane, and adding thermal vias, the  $R_{\theta JA}$  for the application can be reduced.

Figure 25. Internal WSON Connection

INSTRUMENTS

Texas

## 10 器件和文档支持

## 10.1 器件支持

## 10.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

## 10.1.2 开发支持

## 10.1.2.1 使用 WEBENCH® 工具创建定制设计

单击此处,使用 LMR10520 器件并借助 WEBENCH® 电源设计器创建定制设计方案。

- 1. 首先输入输入电压 (V<sub>IN</sub>)、输出电压 (V<sub>OUT</sub>) 和输出电流 (I<sub>OUT</sub>) 要求。

- 2. 使用优化器拨盘优化该设计的关键参数,如效率、尺寸和成本。

- 3. 将生成的设计与德州仪器 (TI) 的其他可行的解决方案进行比较。

WEBENCH 电源设计器可提供定制原理图以及罗列实时价格和组件供货情况的物料清单。

在多数情况下,可执行以下操作:

- 运行电气仿真,观察重要波形以及电路性能

- 运行热性能仿真,了解电路板热性能

- 将定制原理图和布局方案以常用 CAD 格式导出

- 打印设计方案的 PDF 报告并与同事共享

有关 WEBENCH 工具的详细信息,请访问 www.ti.com.cn/WEBENCH。

## 10.2 接收文档更新通知

要接收文档更新通知,请导航至 TI.com.cn 上的器件产品文件夹。单击右上角的通知我 进行注册,即可每周接收产 品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

## 10.3 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 10.4 商标

E2E is a trademark of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 10.5 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

## 10.6 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 11 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更, 恕不另行通知, 且 不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。

## **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       | (1)    | (2)           |                |                       | (3)  | (4)                           | (5)                        |              | (0)              |

| LMR10520XSD/NOPB      | Active | Production    | WSON (NGG)   6 | 1000   SMALL T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520XSD/NOPB.A    | Active | Production    | WSON (NGG)   6 | 1000   SMALL T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520XSD/NOPB.B    | Active | Production    | WSON (NGG)   6 | 1000   SMALL T&R      | -    | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520XSDE/NOPB     | Active | Production    | WSON (NGG)   6 | 250   SMALL T&R       | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520XSDE/NOPB.A   | Active | Production    | WSON (NGG)   6 | 250   SMALL T&R       | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520XSDX/NOPB     | Active | Production    | WSON (NGG)   6 | 4500   LARGE T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520XSDX/NOPB.A   | Active | Production    | WSON (NGG)   6 | 4500   LARGE T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L266B            |

| LMR10520YSD/NOPB      | Active | Production    | WSON (NGG)   6 | 1000   SMALL T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

| LMR10520YSD/NOPB.A    | Active | Production    | WSON (NGG)   6 | 1000   SMALL T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

| LMR10520YSD/NOPB.B    | Active | Production    | WSON (NGG)   6 | 1000   SMALL T&R      | -    | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

| LMR10520YSDE/NOPB     | Active | Production    | WSON (NGG)   6 | 250   SMALL T&R       | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

| LMR10520YSDE/NOPB.A   | Active | Production    | WSON (NGG)   6 | 250   SMALL T&R       | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

| LMR10520YSDX/NOPB     | Active | Production    | WSON (NGG)   6 | 4500   LARGE T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

| LMR10520YSDX/NOPB.A   | Active | Production    | WSON (NGG)   6 | 4500   LARGE T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 125   | L267B            |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

www.ti.com

## PACKAGE OPTION ADDENDUM

24-Jul-2025

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

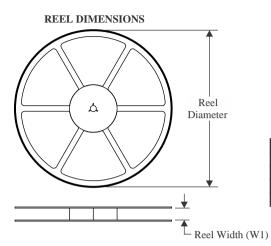

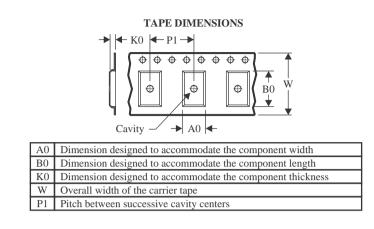

## TAPE AND REEL INFORMATION

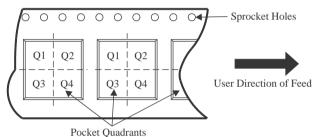

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LMR10520XSD/NOPB            | WSON            | NGG                | 6 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LMR10520XSDE/NOPB           | WSON            | NGG                | 6 | 250  | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LMR10520XSDX/NOPB           | WSON            | NGG                | 6 | 4500 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LMR10520YSD/NOPB            | WSON            | NGG                | 6 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LMR10520YSDE/NOPB           | WSON            | NGG                | 6 | 250  | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LMR10520YSDX/NOPB           | WSON            | NGG                | 6 | 4500 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

www.ti.com

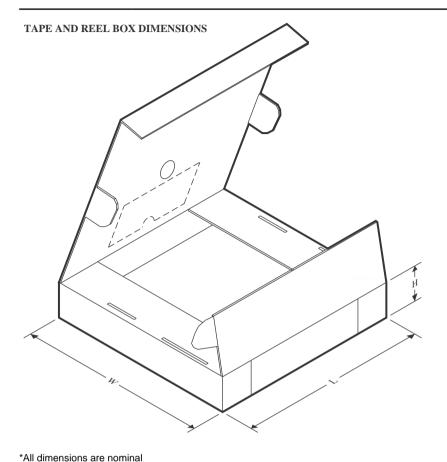

# PACKAGE MATERIALS INFORMATION

31-Jul-2025

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMR10520XSD/NOPB  | WSON         | NGG             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LMR10520XSDE/NOPB | WSON         | NGG             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LMR10520XSDX/NOPB | WSON         | NGG             | 6    | 4500 | 356.0       | 356.0      | 36.0        |

| LMR10520YSD/NOPB  | WSON         | NGG             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LMR10520YSDE/NOPB | WSON         | NGG             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LMR10520YSDX/NOPB | WSON         | NGG             | 6    | 4500 | 356.0       | 356.0      | 36.0        |

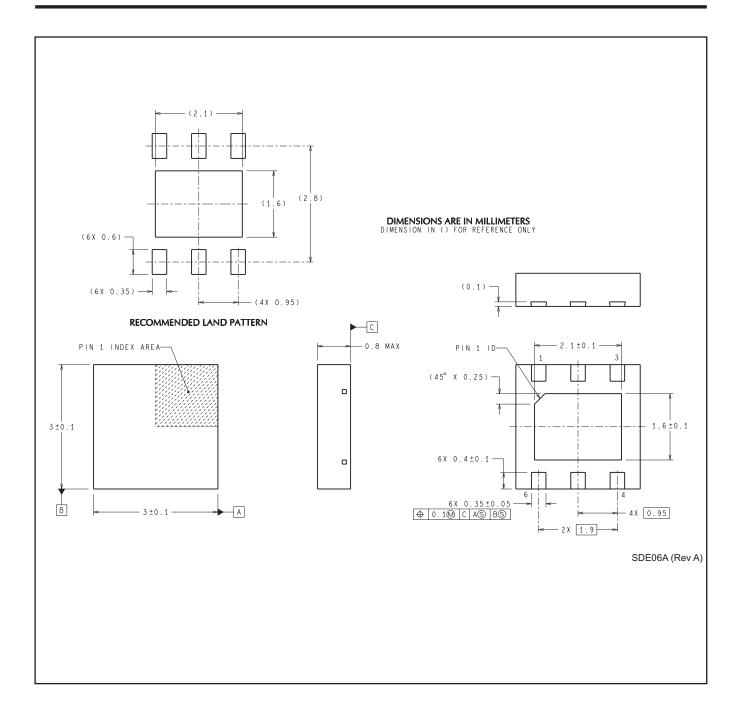

# **MECHANICAL DATA**

# NGG0006A

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行 复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索 赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司