Sample &

Buy

#### LMP91002

ZHCSAU0B-APRIL 2012-REVISED OCTOBER 2015

LMP91002 传感器模拟前端 (AFE) 系统:针对低功耗化学感测应用的可配 置 AFE 稳压器

#### 特性 1

- 典型值, T<sub>A</sub>=25°C

- 电源电压范围: 2.7V 至 3.6V

- 电源电流(一段时间内的平均值) < 10µA

- 电池调节电流高达 10mA

- 基准电极偏置电流 (85°C) 900pA (最大值)

- 输出驱动电流 750µA

- 与大多数非偏置气体传感器对接的完整稳压器电路

- 低偏置电压漂移 ٠

- 可编程互阻放大器 (TIA) 增益: 2.75kΩ 至 350kΩ

- 兼容 I<sup>2</sup>C 的数字接口

- 环境工作温度范围: -40℃ 至 85℃

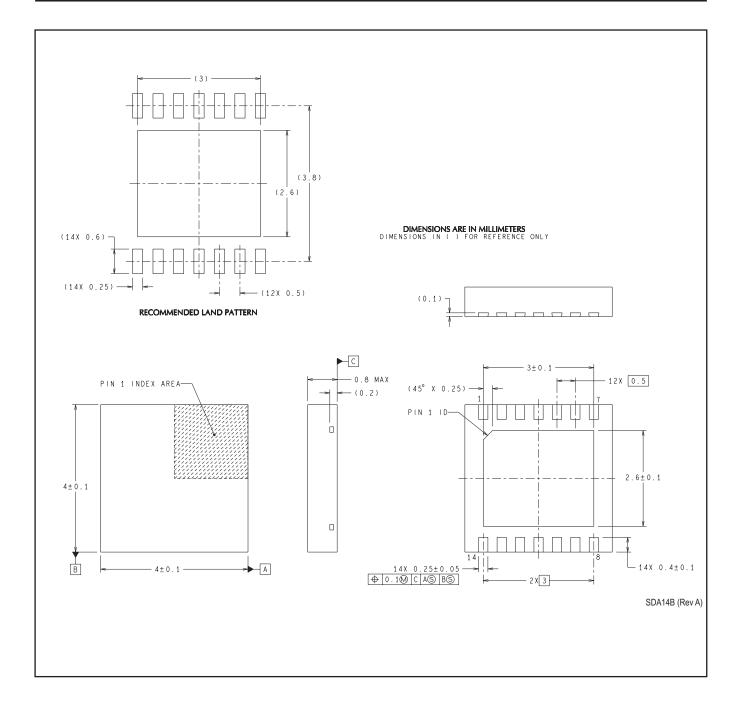

- 14 引脚晶圆级小外形无引线 (WSON) 封装

- 由 Webench 传感器 AFE 设计工具提供支持

## 2 应用

- 气体检测器 •

- 电流计应用

- 电化学血糖仪

3 说明

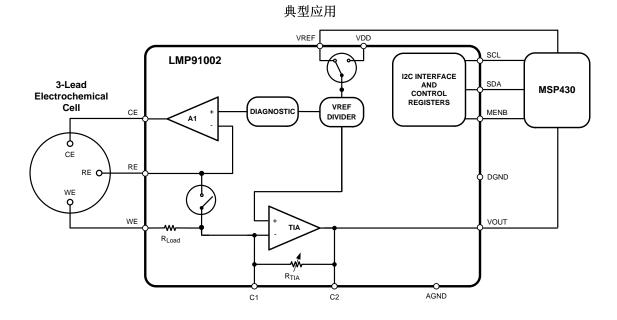

LMP91002 器件是一款适用于微功耗电化学感测应用 的可编程模拟前端 (AFE)。 它可提供非偏置气体传感 器与微控制器之间的完整信号路径解决方案,此方案能 够生成与电池电流成比例的输出电压。

LMP91002 的可编程性使它能够用一种单一设计支持 非偏置电化学气体传感器。 LMP91002 支持 0.5nA/ppm 至 9500nA/ppm 范围内的气体灵敏度。 该 器件还可在 5µA 至 750µA 的满量程电流范围内实现简 单转换。 LMP91002 的互阻抗放大器 (TIA) 增益可通 过 I<sup>2</sup>C 接口进行编程。 I<sup>2</sup>C 接口也可用于传感器诊断。 LMP91002 针对微功耗应用进行了优化,其工作电压 范围为 2.7V 至 3.6V, 总流耗低于 10µA。 可通过关闭 TIA 放大器以及使用一个内部开关将参比电极与工作电 极短接来进一步节能。

| 器件信息 <sup>(1</sup> | ) |

|--------------------|---|

|--------------------|---|

| 部件号      | 封装        | 封装尺寸(标称值)       |  |  |  |  |

|----------|-----------|-----------------|--|--|--|--|

| LMP91002 | WSON (14) | 4.00mm x 4.00mm |  |  |  |  |

|          |           |                 |  |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

## 目录

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   | 1                                  |

| 3 | 说明   | 1                                  |

| 4 | 修订   | 历史记录 2                             |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications                        |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 4              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | I <sup>2</sup> C Interface         |

|   | 6.7  | Timing Characteristics7            |

|   | 6.8  | Typical Characteristics 8          |

| 7 | Deta | ailed Description 10               |

|   | 7.1  | Overview 10                        |

|   | 7.2  | Functional Block Diagram 10        |

|   | 7.3  | Feature Description 10             |

### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Cł | anges from Revision A | A (March 2013) | to Revision B |          |           |       | F     | Page |

|----|-----------------------|----------------|---------------|----------|-----------|-------|-------|------|

| •  | 已添加 ESD 额定值表,         | 特性描述部分,        | 器件功能模式,       | 应用和实施部分, | 电源相关建议部分, | 布局部分, | 器件和文档 |      |

支持部分以及机械、封装和可订购信息部分。......1

#### Changes from Original (March 2013) to Revision A

2

7.4 Device Functional Modes..... 12

Application and Implementation ...... 17

8.1 Application Information...... 17 8.2 Typical Application ...... 19 Power Supply Recommendations ...... 22

9.1 Power Consumption...... 22 10 Layout...... 22 10.1 Layout Guidelines ..... 22 10.2 Layout Example ..... 23 11 器件和文档支持...... 25 商标......25

11.3 静电放电警告...... 25 11.4 Glossary ...... 25 12 机械、封装和可订购信息...... 25

Programming...... 12 Register Maps ..... 14

#### www.ti.com.cn

| Page |

|------|

|------|

Page

7.5

7.6

11.2

8

9

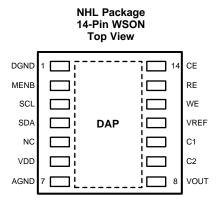

### Pin Functions<sup>(1)</sup>

| Р   | PIN  |     | DESCRIPTION                                                                    |  |  |

|-----|------|-----|--------------------------------------------------------------------------------|--|--|

| NO. | NAME | I/O | DESCRIPTION                                                                    |  |  |

| 1   | DGND | G   | Connect to ground                                                              |  |  |

| 2   | MENB | D   | Module Enable. Active Low                                                      |  |  |

| 3   | SCL  | D   | l <sup>2</sup> C Clock                                                         |  |  |

| 4   | SDA  | D   | I <sup>2</sup> C Data                                                          |  |  |

| 5   | NC   | —   | Do not connect. Not internally connected                                       |  |  |

| 6   | VDD  | Р   | Voltage supply                                                                 |  |  |

| 7   | AGND | GND | Analog GND                                                                     |  |  |

| 8   | VOUT | А   | Analog voltage representing sensor output                                      |  |  |

| 9   | C2   | А   | Optional External component node 2 for TIA (filter capacitor or gain resistor) |  |  |

| 10  | C1   | А   | Optional External component node 1 for TIA (filter capacitor or gain resistor) |  |  |

| 11  | VREF | А   | External Reference voltage input                                               |  |  |

| 12  | WE   | А   | Working Electrode of the sensor.                                               |  |  |

| 13  | RE   | А   | Reference Electrode of the sensor.                                             |  |  |

| 14  | CE   | А   | Counter Electrode of the sensor.                                               |  |  |

| _   | DAP  | GND | Die attached pad. Connect to GND.                                              |  |  |

(1) A = analog, D = digital, P = power, G = GND

### 6 Specifications

### 6.1 Absolute Maximum Ratings

See (1)(2)(3)

|                                          | MIN | MAX | UNIT |

|------------------------------------------|-----|-----|------|

| Voltage between any two pins             |     | 6   | V    |

| Current through VDD or VSS               |     | 50  | mA   |

| Current sunk and sourced by CE pin       |     | 10  | mA   |

| Current out of other pins <sup>(4)</sup> |     | 5   | mA   |

| Junction temperature <sup>(5)</sup>      |     | 150 | °C   |

| Storage temperature, T <sub>stg</sub>    | -65 | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) For soldering specifications, see SNOA549.

(3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(4) All non-power pins of this device are protected against ESD by snapback devices. Voltage at such pins will rise beyond absmax if current is forced into pin.

(5) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>DMAX</sub> = (T<sub>J(MAX)</sub> - T<sub>A</sub>)/ θ<sub>JA</sub> All numbers apply for packages soldered directly onto a PCB.

### 6.2 ESD Ratings

|                    |                            |                                                                                | VALUE | UNIT |

|--------------------|----------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)(2)</sup>           | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(3)</sup> | ±1000 | V    |

|                    | a.coa.go                   | Machine Model (MM)                                                             | ±200  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JESD2) Field Jackwood Charge Davise Model, applicable std. JESD22 (2010) C (ESD EICDM std. of JESD2)

JEDEC) Field- Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

(3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

|                                     | MIN | MAX | UNIT |

|-------------------------------------|-----|-----|------|

| Supply voltage $V_S = (VDD - AGND)$ | 2.7 | 3.6 | V    |

| Temperature <sup>(1)</sup>          | -40 | 85  | °C   |

The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>DMAX</sub> = (T<sub>J(MAX)</sub> - T<sub>A</sub>)/ θ<sub>JA</sub> All numbers apply for packages soldered directly onto a PCB.

### 6.4 Thermal Information

|                                                                        | LMP91002   |      |

|------------------------------------------------------------------------|------------|------|

| THERMAL METRIC <sup>(1)</sup>                                          | NHL (WSON) | UNIT |

|                                                                        | 14 PINS    |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance <sup>(2)</sup> | 44         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>DMAX</sub> = (T<sub>J(MAX)</sub> - T<sub>A</sub>)/ θ<sub>JA</sub> All numbers apply for packages soldered directly onto a PCB.

#### 6.5 Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V_S = (V_{DD} - AGND)$ ,  $V_S = 3.3$  V and AGND = DGND = 0 V,  $V_{REF} = 0.0000$ 2.5 V, Internal Zero = 20%  $V_{RFF}$ .<sup>(1)</sup>

|                      | PARAMETER                                                      | TEST CO                                                  | ONDITIONS                   | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |

|----------------------|----------------------------------------------------------------|----------------------------------------------------------|-----------------------------|--------------------|--------------------|--------------------|-------|

| POWER SI             | JPPLY SPECIFICATION                                            |                                                          |                             |                    |                    |                    |       |

|                      |                                                                | 3-lead amperometric cell                                 | T <sub>A</sub> = 25°C       |                    | 10                 | 13.5               |       |

|                      |                                                                | mode<br>MODECN = 0x03                                    | At the temperature extremes |                    |                    | 15                 |       |

|                      |                                                                | Standby mode                                             | T <sub>A</sub> = 25°C       |                    | 6.5                | 8                  |       |

| I <sub>S</sub>       | Supply current                                                 | MODECN = 0x02                                            | At the temperature extremes |                    |                    | 10                 | μA    |

|                      |                                                                | Deep sleep mode                                          | T <sub>A</sub> = 25°C       |                    | 0.6                | 0.85               |       |

|                      |                                                                | MODECN = 0x00                                            | At the temperature extremes |                    |                    | 1                  |       |

| POTENTIO             | STAT                                                           |                                                          |                             |                    |                    |                    |       |

|                      |                                                                | VDD = 2.7 V:                                             | T <sub>A</sub> = 25°C       | -90                |                    | 90                 |       |

| I <sub>RE</sub>      | Input bias current at RE pin                                   | Internal zero 50% VDD                                    | At the temperature extremes | -800               |                    | 800                | ۶A    |

|                      |                                                                | VDD = 3.6 V;                                             | T <sub>A</sub> = 25°C       | -90                |                    | 90                 | рА    |

|                      |                                                                | Internal zero 50% VDD                                    | At the temperature extremes | -900               |                    | 900                |       |

|                      | Minimum operating current                                      | Sink                                                     |                             |                    | 750                |                    | μA    |

| l                    | capability                                                     | Source                                                   |                             |                    | 750                |                    | μΑ    |

| I <sub>CE</sub>      | Minimum charging capability <sup>(4)</sup>                     | Sink                                                     |                             |                    | 10                 |                    | mA    |

|                      |                                                                | Source                                                   |                             |                    | 10                 |                    | ША    |

|                      | Open-loop voltage gain of                                      | 300 mV ≤ VCE ≤                                           | T <sub>A</sub> = 25°C       |                    | 120                |                    |       |

| AOL_A1               | control loop operational amplifier (A1)                        | Vs – 300 mV, –750 μA ≤<br>ICE ≤ 750 μA                   | At the temperature extremes | 104                |                    |                    | dB    |

| en_RW                | Low frequency integrated<br>noise between RE pin and<br>WE pin | 0.1 Hz to 10 Hz <sup>(5)</sup>                           |                             |                    | 3.4                |                    | µVpp  |

|                      |                                                                | 0% VREF, internal zero = 2<br>at the temperature extreme |                             | -550               |                    | 550                |       |

| V <sub>OS_RW</sub>   | WE voltage offset referred to RE                               | 0% VREF, internal zero =                                 |                             | -550               |                    | 550                | μV    |

|                      |                                                                | 0% VREF, internal zero = at the temperature extreme      |                             | -550               |                    | 550                |       |

|                      | WE voltage offset drift                                        | 0% VREF, internal zero =                                 | 20% VREF                    | -4                 |                    | 4                  |       |

| TcV <sub>OS_RW</sub> | referred to RE from -40°C to                                   | 0% VREF, internal zero =                                 | 50% VREF                    | -4                 |                    | 4                  | µV/°C |

|                      | 85°C <sup>(6)</sup>                                            | 0% VREF, internal zero =                                 | 67% VREF                    | -4                 |                    | 4                  |       |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No ensured specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>. Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- At such currents no accuracy of the output voltage can be expected.

- (5) This parameter includes both A1 and TIA's noise contribution.

- Offset voltage temperature drift is determined by dividing the change in VOS at the temperature extremes by the total temperature change. Starting from the measured voltage offset at temperature T1 ( $V_{OS_RW}(T1)$ ), the voltage offset at temperature T2 ( $V_{OS_RW}(T2)$ ) is (6) calculated according the following formula: V<sub>OS\_RW</sub>(T2)=V<sub>OS\_RW</sub>(T1)+ABS(T2-T1)\* TcV<sub>OS\_RW</sub>.

ZHCSAU0B-APRIL 2012-REVISED OCTOBER 2015

www.ti.com.cn

### **Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V_S = (V_{DD} - AGND)$ ,  $V_S = 3.3 \text{ V}$  and AGND = DGND = 0 V,  $V_{REF} = 2.5 \text{ V}$ , Internal Zero = 20%  $V_{REF}$ .<sup>(1)</sup>

|          | PARAMETER                                 | TEST                               | CONDITIONS                    | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|----------|-------------------------------------------|------------------------------------|-------------------------------|--------------------|--------------------|--------------------|------|

|          | Transimpedance gain accuracy              |                                    |                               |                    | 5%                 |                    |      |

|          | Linearity                                 |                                    |                               |                    | ±0.05%             |                    |      |

| TIA_GAIN | Programmable TIA gains                    | 7 programmable gain res            | / programmable gain resistors |                    |                    |                    | kΩ   |

|          |                                           | Maximum external gain r            | esistor                       |                    | 350                |                    |      |

| TIA_ZV   |                                           | 3 programmable percentages of VREF |                               |                    | 20%<br>50%<br>67%  |                    |      |

|          | Internal zero voltage                     | 3 programmable percentages of VDD  |                               |                    | 20%<br>50%<br>67%  |                    |      |

|          | Internal zero voltage<br>accuracy         |                                    |                               |                    | ±0.04%             |                    |      |

|          | Load resistor                             |                                    |                               |                    | 10                 |                    | Ω    |

| RL       | Load accuracy                             |                                    |                               |                    | 5%                 |                    |      |

|          |                                           |                                    | Internal zero 20% VREF        | 80                 | 110                |                    |      |

| PSRR     | Power supply rejection ratio<br>at RE pin | 2.7 V ≤ VDD ≤ 5.25 V               | Internal zero 50% VREF        | 80                 | 110                |                    | dB   |

|          |                                           |                                    | Internal zero 67% VREF        | 80                 | 110                |                    |      |

| EXTERNA  | L REFERENCE SPECIFICATIO                  | ON <sup>(7)</sup>                  |                               |                    |                    |                    |      |

| VREF     | External voltage reference range          |                                    |                               | 1.5                |                    | VDD                | V    |

|          | Input impedance                           |                                    |                               |                    | 10                 |                    | MΩ   |

(7) In case of external reference connected, the noise of the reference has to be added.

### 6.6 I<sup>2</sup>C Interface

Unless otherwise specified, all limits ensured for at  $T_A = 25^{\circ}$ C,  $V_S = (VDD - AGND)$ , 2.7 V <V<sub>S</sub>< 3.6 V and AGND = DGND = 0 V, VREF = 2.5 V.<sup>(1)</sup>

|                 | PARAMETER                             | TEST CONDITIONS                                        | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|-----------------|---------------------------------------|--------------------------------------------------------|--------------------|--------------------|--------------------|------|

| VIH             | Input High Voltage                    | At the temperature extremes                            | 0.7*VDD            |                    |                    | V    |

| VIL             | Input Low Voltage                     | At the temperature extremes                            |                    |                    | 0.3*VDD            | V    |

| V <sub>OL</sub> | Output Low Voltage                    | $I_{OUT} = 3 \text{ mA}$ , at the temperature extremes |                    |                    | 0.4                | V    |

|                 | Hysteresis <sup>(4)</sup>             | At the temperature extremes                            | 0.1*VDD            |                    |                    | V    |

| C <sub>IN</sub> | Input Capacitance on all digital pins | At the temperature extremes                            |                    | 0.5                |                    | pF   |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No ensured specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(4) This parameter is specified by design or characterization.

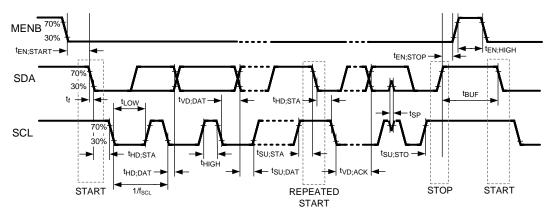

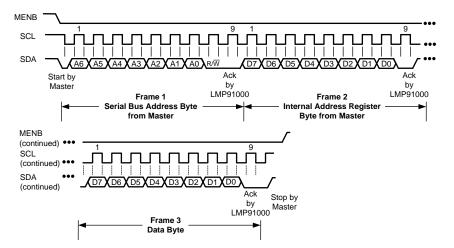

### 6.7 Timing Characteristics

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}$ C,  $V_S = (VDD - AGND)$ ,  $V_S = 3.3$  V and AGND = DGND = 0 V, VREF = 2.5 V, Internal Zero= 20% VREF. All limits apply at the temperature extremes. Refer to timing diagram in Figure 1<sup>(1)</sup>.

| PARAMETER             |                                                                                  | TEST CONDITIONS                                                                   | MIN | TYP | MAX  | UNIT |

|-----------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|------|------|

| f <sub>SCL</sub>      | Clock Frequency                                                                  | At the temperature extremes                                                       | 10  |     | 100  | kHz  |

| t <sub>LOW</sub>      | Clock Low Time                                                                   | At the temperature extremes                                                       | 4.7 |     |      | μs   |

| t <sub>HIGH</sub>     | Clock High Time                                                                  | At the temperature extremes                                                       | 4   |     |      | μs   |

| t <sub>HD;STA</sub>   | Data valid                                                                       | After this period, the first clock pulse is generated at the temperature extremes | 4   |     |      | μs   |

| t <sub>SU;STA</sub>   | Set-up time for a repeated START condition                                       | At the temperature extremes                                                       | 4.7 |     |      | μs   |

| t <sub>HD;DAT</sub>   | Data hold time <sup>(2)</sup>                                                    | At the temperature extremes                                                       | 0   |     |      | ns   |

| t <sub>SU;DAT</sub>   | Data Set-up time                                                                 | At the temperature extremes                                                       | 250 |     |      | ns   |

| t <sub>f</sub>        | SDA fall time <sup>(3)</sup>                                                     | $IL \le 3 \text{ mA}, CL \le 400 \text{ pF},$<br>at the temperature extremes      |     |     | 250  | ns   |

| t <sub>su;sто</sub>   | Set-up time for STOP condition                                                   | At the temperature extremes                                                       | 4   |     |      | μs   |

| t <sub>BUF</sub>      | Bus free time between a STOP and START condition                                 | At the temperature extremes                                                       | 4.7 |     |      | μs   |

| t <sub>VD;DAT</sub>   | Data valid time                                                                  | At the temperature extremes                                                       |     |     | 3.45 | μs   |

| t <sub>VD;ACK</sub>   | Data valid acknowledge time                                                      | At the temperature extremes                                                       |     |     | 3.45 | μs   |

| t <sub>SP</sub>       | Pulse width of spikes that must be suppressed by the input filter <sup>(3)</sup> | At the temperature extremes                                                       |     |     | 50   | ns   |

| t_timeout             | SCL and SDA Timeout                                                              | At the temperature extremes                                                       | 25  |     | 100  | ms   |

| t <sub>EN;START</sub> | I <sup>2</sup> C Interface Enabling                                              | At the temperature extremes                                                       | 600 |     |      | ns   |

| t <sub>EN;STOP</sub>  | I <sup>2</sup> C Interface Disabling                                             | At the temperature extremes                                                       | 600 |     |      | ns   |

| t <sub>EN;HIGH</sub>  | time between consecutive I <sup>2</sup> C interface enabling and disabling       | At the temperature extremes                                                       | 600 |     |      | ns   |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No ensured specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>. Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

(2) LMP91002 provides an internal 300ns minimum hold time to bridge the undefined region of the falling edge of SCL.

(3) This parameter is specified by design or characterization.

Figure 1. I<sup>2</sup>C Interface Timing Diagram

LMP91002

ZHCSAU0B-APRIL 2012-REVISED OCTOBER 2015

NSTRUMENTS

EXAS

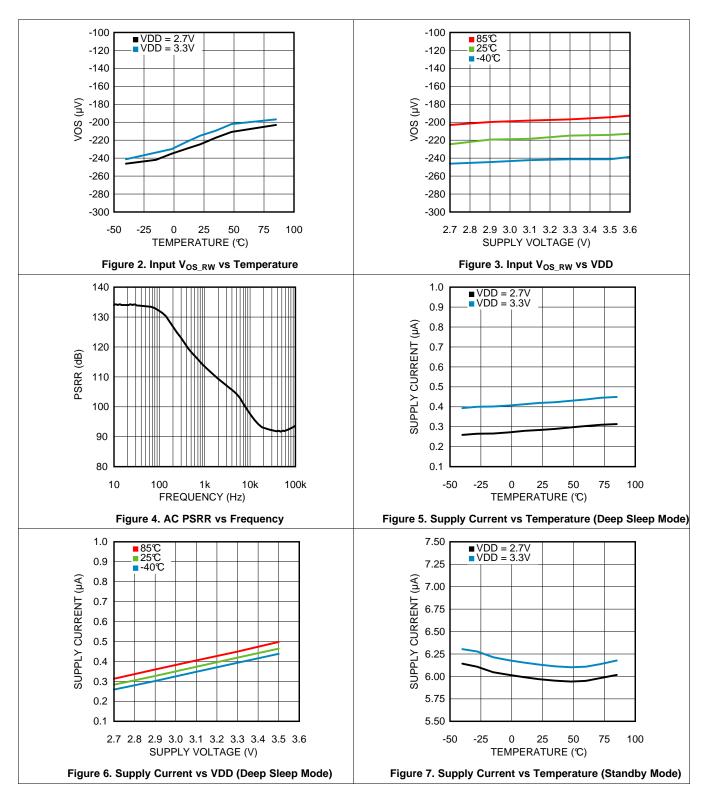

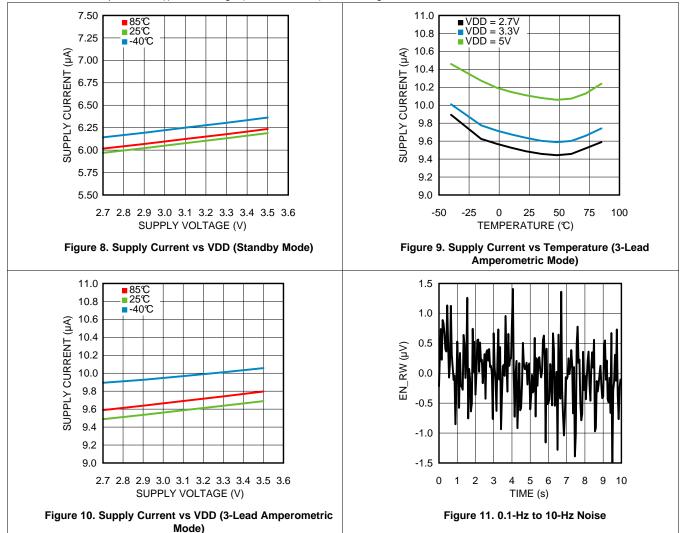

### 6.8 Typical Characteristics

Unless otherwise specified,  $T_A = 25^{\circ}$ C,  $V_S = (VDD - AGND)$ , 2.7 V <V<sub>S</sub>< 3.6 V and AGND = DGND = 0 V, VREF = 2.5 V.

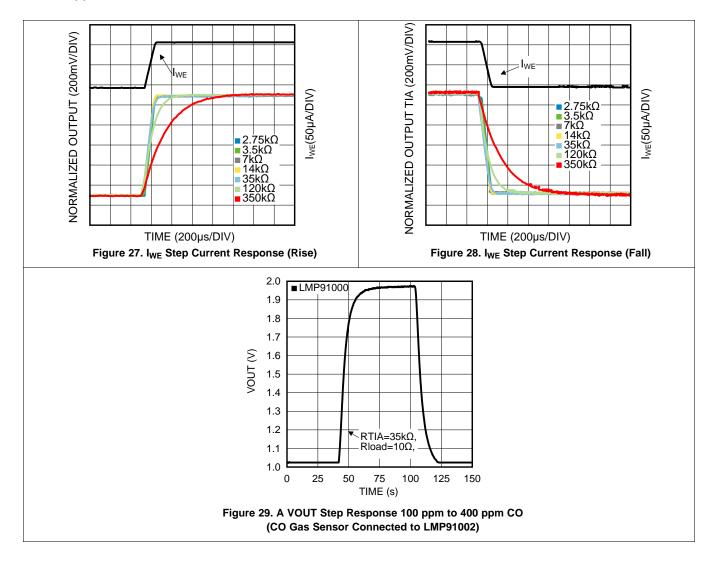

### **Typical Characteristics (continued)**

Unless otherwise specified,  $T_A = 25^{\circ}$ C,  $V_S = (VDD - AGND)$ , 2.7 V <V<sub>S</sub>< 3.6 V and AGND = DGND = 0 V, VREF = 2.5 V.

### 7 Detailed Description

### 7.1 Overview

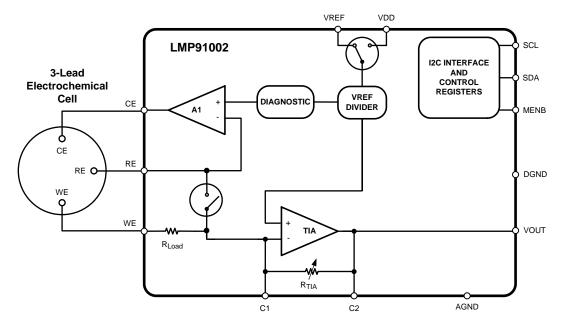

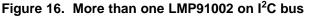

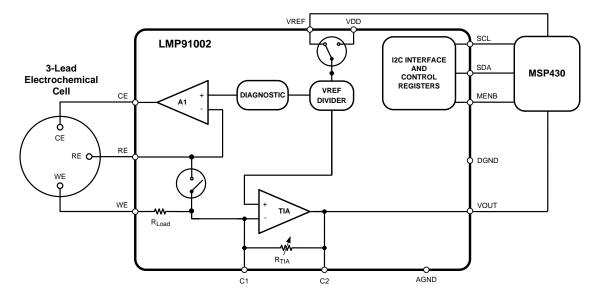

The LMP91002 is a programmable AFE for use in micropower chemical sensing applications. The LMP91002 is designed for 3-lead non-biased gas sensors and for 2 leads galvanic cell. This device provides all of the functionality for detecting changes in gas concentration based on a delta current at the working electrode. The LMP91002 generates an output voltage proportional to the cell current. Transimpedance gain is user programmable through an I<sup>2</sup>C compatible interface from  $2.75k\Omega$  to  $350k\Omega$  making it easy to convert current ranges from  $5\mu$ A to  $750\mu$ A full scale. Optimized for micro-power applications, the LMP91002 AFE works over a voltage range of 2.7V to 3.6 V. The cell voltage is user selectable using the on board programmability. In addition, it is possible to connect an external transimpedance gain resistor. Depending on the configuration, total current consumption for the device can be less than  $10\mu$ A. For power savings, the transimpedance amplifier can be turned off and instead a load impedance equivalent to the TIA's inputs impedance is switched in.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Potentiostat Circuitry

The core of the LMP91002 is a potentiostat circuit. It consists of a differential input amplifier used to compare the potential between the working and reference electrodes to a zero bias potential. The error signal is amplified and applied to the counter electrode (through the **Control Amplifier - A1**). Any changes in the impedance between the working and reference electrodes will cause a change in the voltage applied to the counter electrode, in order to maintain the constant voltage between working and reference electrodes. A **Transimpedance Amplifier** connected to the working electrode, is used to provide an output voltage that is proportional to the cell current. The working electrode is held at virtual ground (**Internal ground**) by the transimpedance amplifier. The potentiostat will compare the reference voltage to the desired bias potential and adjust the voltage at the counter electrode to maintain the proper working-to-reference voltage.

### 7.3.2 Transimpedance Amplifier

The transimpedance amplifier (TIA in *Functional Block Diagram*) has 7 programmable internal gain resistors. This accommodates the full scale ranges of most existing sensors. Moreover an external gain resistor can be connected to the LMP91002 between C1 and C2 pins. The gain is set through the I<sup>2</sup>C interface.

#### Feature Description (continued)

#### 7.3.3 Control Amplifier

The control amplifier (A1 op amp in *Functional Block Diagram*) provides initial charge to the sensor. A1 has the capability to drive up to 10mA into the sensor in order to to provide a fast initial conditioning. A1 is able to sink and source current according to the connected gas sensor (reducing or oxidizing gas sensor). It can be powered down to reduce system power consumption. However powering down A1 is not recommended, as it may take a long time for the sensor to recover from this situation.

### 7.3.4 Internal Zero

The internal Zero is the voltage at the non-inverting pin of the TIA. The internal zero can be programmed to be either 67%, 50% or 20%, of the supply, or the external reference voltage. This provides both sufficient headroom for the counter electrode of the sensor to swing, in case of sudden changes in the gas concentration, and best use of the ADC's full scale input range.

The Internal zero is provided through an internal voltage divider (Vref divider box in *Functional Block Diagram*). The divider is programmed through the I<sup>2</sup>C interface.

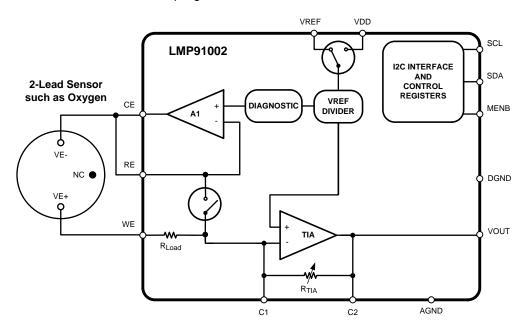

#### 7.3.5 2-Lead Galvanic Cell in Potentiostat Configuration

When the LMP91002 is interfaced to a galvanic cell (for instance to an Oxygen gas sensor) referred to a reference, the Counter and the Reference pin of the LMP91002 are shorted together and connected to negative electrode of the galvanic cell. The positive electrode of the galvanic cell is then connected to the Working pin of the LMP91002.

The LMP91002 is then configured in 3-lead amperometric cell mode (as for amperometric cell). In this configuration the Control Amplifier (A1) is ON and provides the internal zero voltage. The transimpedance amplifier (TIA) is also ON, it converts the current generated by the gas sensor in a voltage, according to the transimpedance gain:

#### Gain= R<sub>TIA</sub>

If different gains are required, an external resistor can be connected between the pins C1 and C2. In this case the internal feedback resistor should be programmed to "external".

Figure 12. Two-Lead Sensor Connections

### 7.4 Device Functional Modes

#### 7.4.1 Timeout Feature

The timeout is a safety feature to avoid bus lockup situation. If SCL is stuck low for a time exceeding t\_timeout, the LMP91002 will automatically reset its I<sup>2</sup>C interface. Also, in the case the LMP91002 hangs the SDA for a time exceeding t\_timeout, the LMP91002's I<sup>2</sup>C interface will be reset so that the SDA line will be released. Since the SDA is an open-drain with an external resistor pull-up, this also avoids high power consumption when LMP91002 is driving the bus and the SCL is stopped.

### 7.5 Programming

### 7.5.1 I<sup>2</sup>C Interface

The I<sup>2</sup>C compatible interface operates in Standard mode (100kHz). Pull-up resistors or current sources are required on the SCL and SDA pins to pull them high when they are not being driven low. A logic zero is transmitted by driving the output low. A logic high is transmitted by releasing the output and allowing it to be pulled-up externally. The appropriate pull-up resistor values will depend upon the total bus capacitance and operating speed. The LMP91002 comes with a 7 bit bus fixed address: 1001 000.

#### 7.5.2 Write and Read Operation

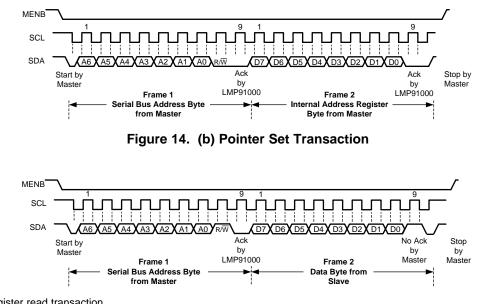

In order to start any read or write operation with the LMP91002, MENB needs to be set low during the whole communication. Then the master generates a start condition by driving SDA from high to low while SCL is high. The start condition is always followed by a 7-bit slave address and a Read/Write bit. After these 8 bits have been transmitted by the master, SDA is released by the master and the LMP91002 either ACKs or NACKs the address. If the slave address matches, the LMP91002 ACKs the master. If the address doesn't match, the LMP91002 NACKs the master. For a write operation, the master follows the ACK by sending the 8-bit register address pointer. Then the LMP91002 ACKs the transfer by driving SDA low. Next, the master sends the 8-bit data to the LMP91002. Then the LMP91002 ACKs the transfer by driving SDA low. At this point the master should generate a stop condition and optionally set the MENB at logic high level (refer to Figure 15).

A read operation requires the LMP91002 address pointer to be set first, also in this case the master needs setting at low logic level the MENB, then the master needs to write to the device and set the address pointer before reading from the desired register. This type of read requires a start, the slave address, a write bit, the address pointer, a Repeated Start (if appropriate), the slave address, and a read bit (refer to Figure 15). Following this sequence, the LMP91002 sends out the 8-bit data of the register.

When just one LMP91002 is present on the I<sup>2</sup>C bus the MENB can be tied to ground (low logic level).

Figure 13. (a) Register Write Transaction

LMP91002 ZHCSAU0B – APRIL 2012 – REVISED OCTOBER 2015

# Programming (continued)

(c) Register read transaction

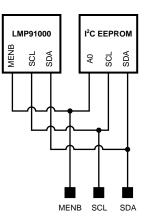

#### 7.5.3 Connection of More Than One LMP91002 to the I<sup>2</sup>C Bus

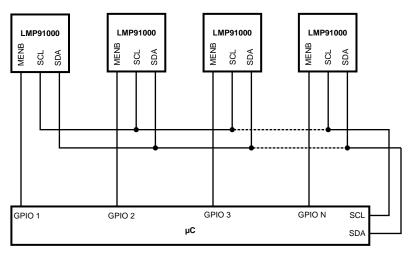

The LMP91002 comes out with a unique and fixed I<sup>2</sup>C slave address. It is still possible to connect more than one LMP91002 to an I<sup>2</sup>C bus and select each device using the MENB pin. The MENB simply enables/disables the I<sup>2</sup>C communication of the LMP91002. When the MENB is at logic level low all the I<sup>2</sup>C communication is enabled, it is disabled when MENB is at high logic level.

In a system based on a  $\mu$ controller and more than one LMP91002 connected to the I<sup>2</sup>C bus, the I<sup>2</sup>C lines (SDA and SCL) are shared, while the MENB of each LMP91002 is connected to a dedicate GPIO port of the  $\mu$ controller.

The  $\mu$ controller starts communication asserting one out of N MENB signals where N is the total number of LMP91002s connected to the I<sup>2</sup>C bus. Only the enabled device will acknowledge the I<sup>2</sup>C commands. After finishing communicating with this particular LMP91002, the microcontroller de-asserts the corresponding MENB and repeats the procedure for other LMP91002s. Figure 16 shows the typical connection when more than one LMP91002 is connected to the I<sup>2</sup>C bus.

LMP91002 ZHCSAU0B – APRIL 2012–REVISED OCTOBER 2015

www.ti.com.cn

### 7.6 Register Maps

The registers are used to configure the LMP91002.

If writing to a reserved bit, user must write only 0. Readback value is unspecified and should be discarded.

|                 |          |                  | • •                   |           |         |

|-----------------|----------|------------------|-----------------------|-----------|---------|

| Offset          | Name     | Power on Default | Access <sup>(1)</sup> | Lockable? | Section |

| 00h             | STATUS   | 0x00             | Read only             | N         | Go      |

| 01h             | LOCK     | 0x01             | R/W                   | N         | Go      |

| 02h through 09h | RESERVED |                  |                       |           |         |

| 10h             | TIACN    | 0x03             | R/W                   | Y         | Go      |

| 11h             | REFCN    | 0x20             | R/W                   | Y         | Go      |

| 12h             | MODECN   | 0x00             | R/W                   | N         | Go      |

| 13h through FFh | RESERVED |                  |                       |           |         |

Table 1. Register Map

(1) LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### 7.6.1 STATUS Register (Offset = 00h)

Status Register. The status bit is an indication of the LMP91002's power-on status. If its readback is "0", the LMP91002 is not ready to accept other I<sup>2</sup>C commands.

### Figure 17. STATUS Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1      | 0 |

|---|----------|---|---|---|---|--------|---|

|   | Reserved |   |   |   |   | STATUS |   |

|   | R        |   |   |   |   |        | R |

### Table 2. STATUS Register Field Descriptions

| Bit | Name     | Function                                                   |

|-----|----------|------------------------------------------------------------|

| 7-1 | RESERVED |                                                            |

| 0   | STATUS   | Status of Device<br>0h = Not Ready (default)<br>1h = Ready |

### 7.6.2 LOCK Register (Offset = 01h)

Protection Register. The lock bit enables and disables the writing of the TIACN and the REFCN registers. To change the content of the TIACN and the REFCN registers, the lock bit must be set to "0".

#### Figure 18. LOCK Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0    |

|---|----------|---|---|---|---|---|------|

|   | Reserved |   |   |   |   |   | LOCK |

|   |          |   |   |   |   |   | R/W  |

### Table 3. LOCK Register Field Descriptions

| Bit | Name Function |                                                                                                                      |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------|

| 7-1 | RESERVED      |                                                                                                                      |

| 0   | LOCK          | Write protection<br>0h = Registers 0x10, 0x11 in write mode<br>1h = Registers 0x10, 0x11 in read only mode (default) |

#### 7.6.3 TIACN Register (Offset = 10h)

TIA Control Register. The parameters in the TIA control register allow the configuration of the transimpedance gain ( $R_{TIA}$ ).

| 7 | 6        | 5 | 4 | 3        | 2 | 1    | 0     |

|---|----------|---|---|----------|---|------|-------|

|   | Reserved |   |   | TIA_GAIN |   | Rese | erved |

### Figure 19. TIACN Register

| Table 4. TIACN Register Field | eld Descriptions |

|-------------------------------|------------------|

|-------------------------------|------------------|

| Bit | Name     | Function                                                                                                                                                                                                                                       |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | RESERVED | RESERVED                                                                                                                                                                                                                                       |

| 4-2 | TIA_GAIN | TIA feedback resistance selection<br>000h = External resistance (default)<br>$001h = 2.75 k\Omega$<br>$010h = 3.5 k\Omega$<br>$011h = 7 k\Omega$<br>$100h = 14 k\Omega$<br>$101h = 35 k\Omega$<br>$110h = 120 k\Omega$<br>$111h = 350 k\Omega$ |

| 1-0 | RESERVED | RESERVED                                                                                                                                                                                                                                       |

#### 7.6.4 REFCN Register (Offset = 11h)

Reference Control Register. The parameters in the Reference control register allow the configuration of the Internal zero, and reference source. When the reference source is external, the reference is provided by a reference voltage connected to the VREF pin. In this condition the internal zero is defined as a percentage of VREF voltage instead of the supply voltage.

#### Figure 20. REFCN Register

| 7          | 6  | 5   | 4        | 3 | 2     | 1     | 0 |

|------------|----|-----|----------|---|-------|-------|---|

| REF_SOURCE | IN | T_Z | Reserved |   | DIAGN | OSTIC |   |

#### Table 5. REFCN Register Field Descriptions

| BIT | NAME       | FUNCTION                                                                                                      |

|-----|------------|---------------------------------------------------------------------------------------------------------------|

| 7   | REF_SOURCE | Reference voltage source selection<br>0h = Internal (default)<br>1h = external                                |

| 6-5 | INT_Z      | Internal zero selection (Percentage of the source reference)<br>00h = 20%<br>01h = 50% (default)<br>10h = 67% |

| 4   | RESERVED   | RESERVED                                                                                                      |

| 3-0 | DIAGNOSTIC | Diagnostic step (Percentage of the source reference)<br>0000h = 0% (default)<br>0001h = 1%                    |

LMP91002

ZHCSAU0B-APRIL 2012-REVISED OCTOBER 2015

Texas Instruments

www.ti.com.cn

### 7.6.5 MODECN Register (Offset = 12h)

Mode Control Register. The parameters in the mode register allow the configuration of the operation mode of the LMP91002.

| Figure 21. | MODECN Register |

|------------|-----------------|

|------------|-----------------|

| 7         | 6 | 5    | 4     | 3 | 2 | 1       | 0 |

|-----------|---|------|-------|---|---|---------|---|

| FET_SHORT |   | Rese | erved |   |   | OP_MODE |   |

### Table 6. MODECN Register Field Descriptions

| BIT | NAME        | FUNCTION                        |

|-----|-------------|---------------------------------|

|     |             | Shorting FET feature            |

| 7   | 7 FET_SHORT | 0h = Disabled (default)         |

|     |             | 1h = Enabled                    |

| 6-3 | RESERVED    | RESERVED                        |

|     |             | Mode of Operation selection     |

| 2-0 | OP MODE     | 000h = Deep Sleep (default)     |

| 2-0 | OF_MODE     | 010h = Standby                  |

|     |             | 011h = 3-lead amperometric cell |

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

#### 8.1.1 Gas Sensor Interface

The LMP91002 supports both 3-lead and 2-lead gas sensors. Most of the toxic gas sensors are amperometric cells with 3 leads (Counter, Worker and Reference). These leads should be connected to the LMP91002 in the potentiostat topology.

#### 8.1.1.1 3-Lead Amperometric Cell In Potentiostat Configuration

Most of the amperometric cell have 3 leads (Counter, Reference and Working electrodes). The interface of the 3lead gas sensor to the LMP91002 is straightforward. The leads of the gas sensor should be connected to the LMP91002 pins which have the matching name

The LMP91002 is then configured in 3-lead amperometric cell mode; in this configuration the Control Amplifier (A1) is ON and provides the internal zero voltage and bias in case of biased gas sensor. The transimpedance amplifier (TIA) is ON, it converts the current generated by the gas sensor in a voltage, according to the transimpedance gain:

#### Gain = $R_{TIA}$

If different gains are required, an external resistor can be connected between the pins C1 and C2. In this case the internal feedback resistor should be programmed to "external". The R<sub>Load</sub> together with the output capacitance of the gas sensor acts as a low pass filter.

Figure 22. 3-Lead Amperometric Cell

TEXAS INSTRUMENTS

www.ti.com.cn

### **Application Information (continued)**

#### 8.1.2 Sensor Test Procedure

The LMP91002 has all the hardware and programmability features to implement some test procedures. The purpose of the test procedure is to:

- a. test proper function of the sensor (status of health)

- b. test proper connection of the sensor to the LMP91002

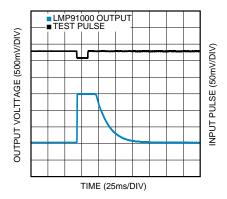

The test procedure is very easy. The diagnostic block is user programmable through the digital interface. A step voltage can be applied by the end user to the positive input of A1. As a consequence a transient current will start flowing into the sensor (to charge its internal capacitance) and it will be detected by the TIA. If the current transient is not detected, either a sensor fault or a connection problem is present. The slope and the aspect of the transient response can also be used to detect sensor aging (for example, a cell that is drying and no longer efficiently conducts the current). After it is verified that the sensor is working properly, the LMP91002 needs to be reset to its original configuration. It is not required to observe the full transient in order to contain the testing time. All the needed information are included in the transient slopes (both edges). Figure 23 shows an example test procedure, a Carbon Monoxide sensor is connected to the LMP91002, a 25-mVpp pulse is applied between Reference and Working pin.

The following procedure shows how to implement the sensor test. Preliminary conditions:

The LMP91002 is unlocked and it is in 3-Lead Amperometric Cell Mode

- 1. Put in the [3:0] bit of the register REFCN (0x11) the 0001b value, leaving the other bit unchanged. This operation will apply a potential (V<sub>RW</sub>) between RE and WE pin (V<sub>RE</sub> > V<sub>WE</sub>), V<sub>RW</sub>= 1% Source reference.

- 2. Put in the [3:0] bit of the register REFCN (0x11) the 0000b value, leaving the other bit unchanged. This operation will remove the potential ( $V_{RW}$ ) between RE and WE pin ( $V_{RE} > V_{WE}$ ),  $V_{RW}$ = 0 V.

The width of the pulse is simply the time between the two writing operation.

Figure 23. Test Procedure Example

### 8.2 Typical Application

Figure 24. AFE Gas Detector

#### 8.2.1 Design Requirements

The primary design requirement is selecting the appropriate TIA gain for the expected range of current over the operating range of the sensor. This gain should set the VOUT range to fall within the limits of the full-scale voltage for the ADC that is sampling the signal. For example, assume the current output range of the sensor is 0 to 100,000 nA, and the full scale ADC input range is 0 to 1 V. Because Gain =  $R_{TIA}$ , the appropriate relationship is:

ISENSOR × Gain =

$$R_{TIA}$$

× 10<sup>-4</sup> A ≤ 1 V

Hence,  $R_{TIA} < 10^4 \Omega$ . In this case, the closest programmed gain value is 7 k $\Omega$  (see Table 4). However, if optimization of the full-scale range is desired, then alternatively,  $R_{TIA}$  can be programmed to 350 k $\Omega$ , and a 10-k $\Omega$  resistor connected between pins C1 and C2. This will give an equivalent resistance of 9.7 k $\Omega$ .

#### 8.2.2 Detailed Design Procedure

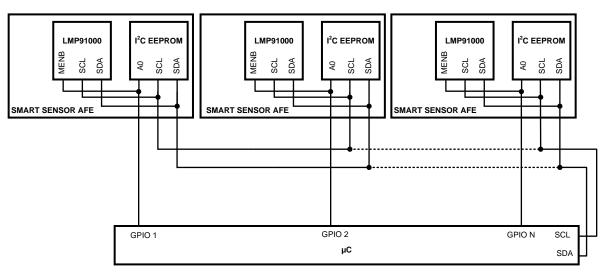

#### 8.2.2.1 Smart Gas Sensor Analog Front End

The LMP91002 together with an external EEPROM represents the core of a SMART GAS SENSOR AFE. In the EEPROM it is possible to store the information related to the GAS sensor type, calibration and LMP91002's configuration (content of registers 10h, 11h, 12h). At startup the microcontroller reads the EEPROM's content and configures the LMP91002. A typical smart gas sensor AFE is shown in Figure 25. The connection of MENB to the hardware address pin A0 of the EEPROM allows the microcontroller to select the LMP91002 and its corresponding EEPROM when more than one smart gas sensor AFE is present on the I<sup>2</sup>C bus.

**NOTE** Only EEPROM I<sup>2</sup>C addresses with A0 = 0 should be used in this configuration. (1)

### **Typical Application (continued)**

Figure 25. Smart Gas Sensor AFE

### 8.2.2.2 Smart Gas Sensor AFES on PC Bus

The connection of Smart gas sensor AFEs on the  $I^2C$  bus is the natural extension of the previous concepts. Also in this case the microcontroller starts communication asserting 1 out of N MENB signals where N is the total number of smart gas sensor AFE connected to the  $I^2C$  bus. Only one of the devices (either LMP91002 or its corresponding EEPROM) in the smart gas sensor AFE enabled will acknowledge the  $I^2C$  commands. When the communication with this particular module ends, the microcontroller de-asserts the corresponding MENB and repeats the procedure for other modules. Figure 26 shows the typical connection when several smart gas sensor AFEs are connected to the  $I^2C$  bus.

Figure 26. Smart Gas Sensor AFEs on I<sup>2</sup>C Bus

### **Typical Application (continued)**

### 8.2.3 Application Curves

### 9 Power Supply Recommendations

### 9.1 Power Consumption

The LMP91002 is intended for use in portable devices, so the power consumption is as low as possible in order to ensure a long battery life. The total power consumption for the LMP91002 is below 10  $\mu$ A at 3.3-V average over time, (this excludes any current drawn from any pin). A typical usage of the LMP91002 is in a portable gas detector and its power consumption is summarized in Table 7. This has the following assumptions:

- Power On only happens a few times over life, so its power consumption can be ignored

- Deep Sleep mode is not used

- The system is used about 8 hours a day, and 16 hours a day it is in Standby mode.

This results in an average power consumption of approximately 7.8  $\mu$ A. This can potentially be further reduced, by using the Standby mode between gas measurements. It may even be possible, depending on the sensor used, to go into deep sleep for some time between measurements, further reducing the average power consumption.

|                                        | DEEP SLEEP | STANDBY | 3-LEAD AMPEROMETRIC<br>CELL | TOTAL |

|----------------------------------------|------------|---------|-----------------------------|-------|

| Current consumption (µA) typical value | 0.6        | 6.5     | 10                          |       |

| Time ON (%)                            | 0          | 60      | 39                          |       |

| Average (µA)                           | 0          | 3.9     | 3.9                         | 7.8   |

| Notes                                  |            |         |                             |       |

| A1                                     | OFF        | ON      | ON                          | -     |

| TIA                                    | OFF        | OFF     | ON                          | -     |

| I <sup>2</sup> C interface             | ON         | ON      | ON                          | -     |

#### Table 7. Power Consumption Scenario

### 10 Layout

### 10.1 Layout Guidelines

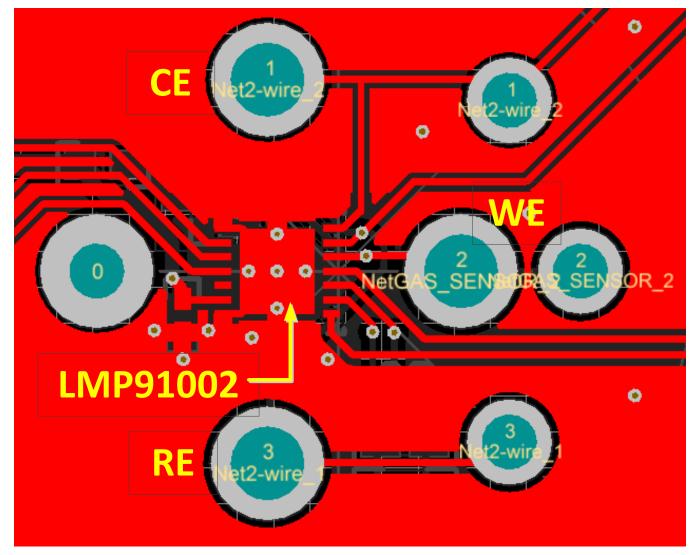

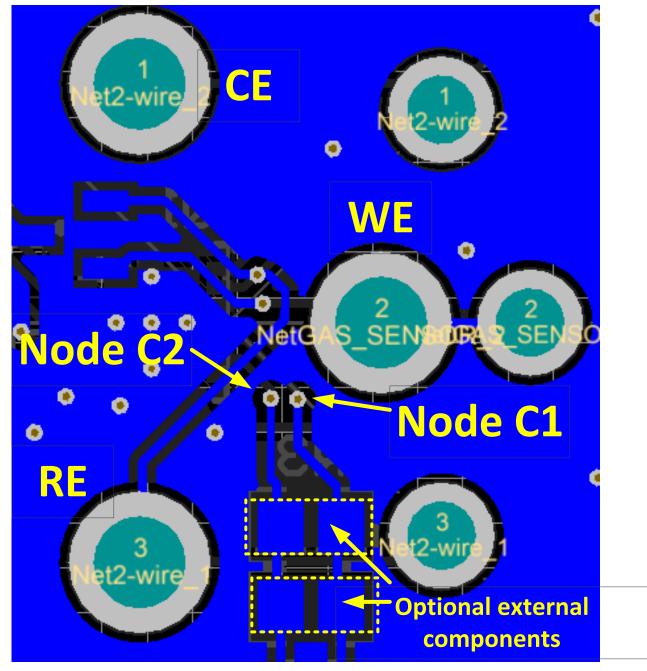

Figure 30 and Figure 31 show an example layout for the LMP91002. Figure 30 shows the top layer, and Figure 31 shows the bottom layer. Figure 30 shows that the sensor electrodes may be arranged around the LMP91002 so that the sensor sets directly over the LMP91002, creating a compact layout. There are very few components needed for the LMP91002: one or more bypass capacitors attached to VDD, and one or two optional external components attached to pins C1 or C2 of the TIA that can provide extra filtering or gain. In the layout shown here, the VDD bypass capacitor is on the top layer, close to the LMP91002, while the optional components for the TIA are placed on the bottom layer. However, these components may also be placed on the top layer.

### 10.2 Layout Example

Figure 30. Layout Example – Top Layer

## Layout Example (continued)

### Figure 31. Layout Example – Bottom Layer

### 11 器件和文档支持

### 11.1 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 11.2 商标

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 11.3 静电放电警告

这些装置包含有限的内置 ESD 保护。存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不 对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

### **PACKAGING INFORMATION**

| Orderable part number | Status   | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|----------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)      | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |          |               |                 |                       |      | (4)           | (5)                 |              |              |

| LMP91002SD/NOPB       | Obsolete | Production    | WSON (NHL)   14 | -                     | -    | Call TI       | Call TI             | -40 to 85    | L91002       |

| LMP91002SDE/NOPB      | Obsolete | Production    | WSON (NHL)   14 | -                     | -    | Call TI       | Call TI             | -40 to 85    | L91002       |

| LMP91002SDX/NOPB      | Active   | Production    | WSON (NHL)   14 | 4500   LARGE T&R      | Yes  | SN            | Level-3-260C-168 HR | -40 to 85    | L91002       |

| LMP91002SDX/NOPB.A    | Active   | Production    | WSON (NHL)   14 | 4500   LARGE T&R      | Yes  | SN            | Level-3-260C-168 HR | -40 to 85    | L91002       |

| LMP91002SDX/NOPB.B    | Active   | Production    | WSON (NHL)   14 | 4500   LARGE T&R      | -    | SN            | Level-3-260C-168 HR | -40 to 85    | L91002       |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

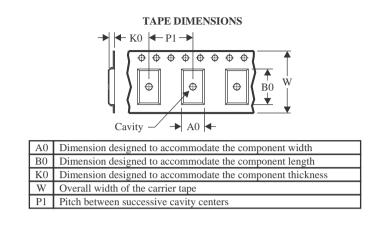

### TAPE AND REEL INFORMATION

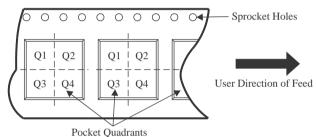

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| All dimensions are nominal |                 |                    |    |      |                          |                          |       |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|-------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | · · / | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LMP91002SDX/NOPB           | WSON            | NHL                | 14 | 4500 | 330.0                    | 12.4                     | 4.3   | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com

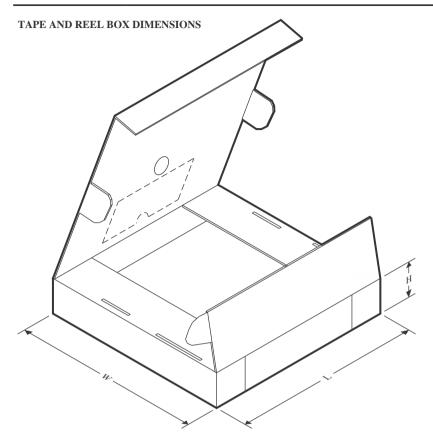

# PACKAGE MATERIALS INFORMATION

13-May-2024

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMP91002SDX/NOPB | WSON         | NHL             | 14   | 4500 | 356.0       | 356.0      | 36.0        |

# **MECHANICAL DATA**

# NHL0014B

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行 复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索 赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司