LMK5B12204

# ZHCSLM0A - MAY 2020 - REVISED JANUARY 2021

# LMK5B12204 具有两个频域的超低抖动网络同步器时钟

# 1 特性

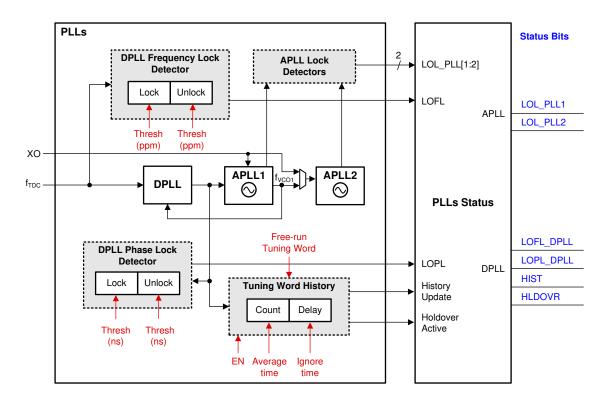

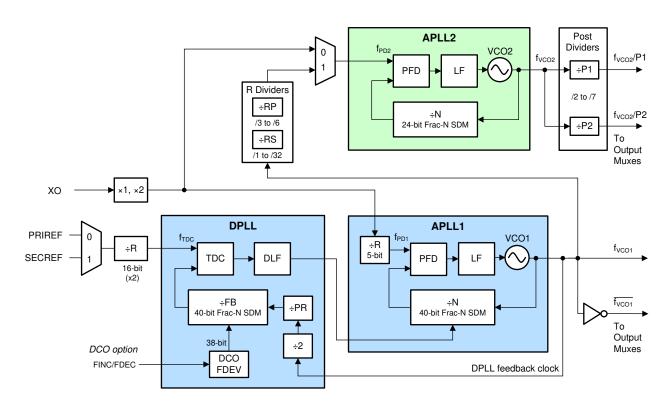

- 一个数字锁相环 (DPLL),具有:

- 无中断切换: ±50ps 相位瞬态

- 具有快速锁定功能的可编程环路带宽

- 使用低成本 TCXO/OCXO 实现符合标准的同步 和保持模式

- 两个具备业界领先性能的模拟锁相环 (APLL):

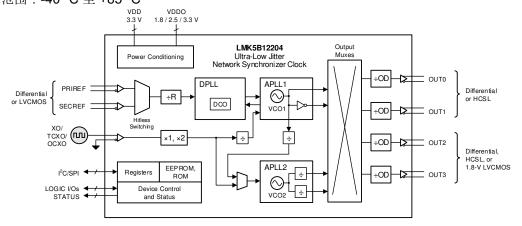

- 312.5MHz 频率下 50fs RMS 抖动 (APLL1)

- 155.52MHz 频率下 125fs RMS 抖动 (APLL2)

- 两个基准时钟输入

- 基于优先级的输入选择

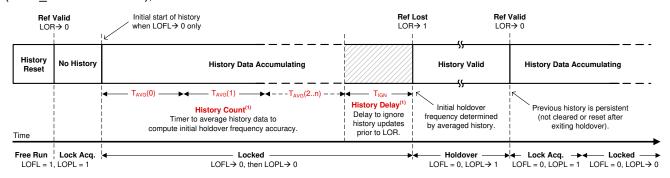

- 在缺失参考时实现数字保持

- 具有可编程驱动器的 四个时钟输出

- 多达四个不同的输出频率

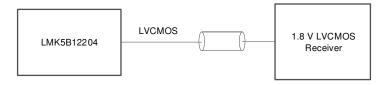

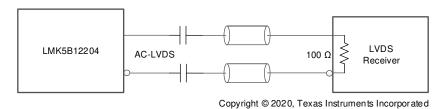

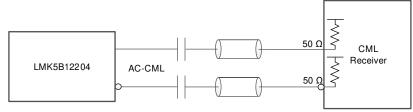

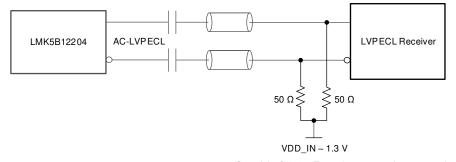

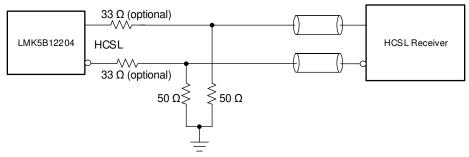

- AC-LVDS、AC-CML、AC-LVPECL、HCSL 和 1.8V LVCMOS 输出格式

- 加电后自定义时钟的 EEPROM/ROM

- 灵活的配置选项

- 输入为 1Hz (1PPS) 至 800MHz

- XO/TCXO/OCXO 输入: 10MHz 至 100MHz

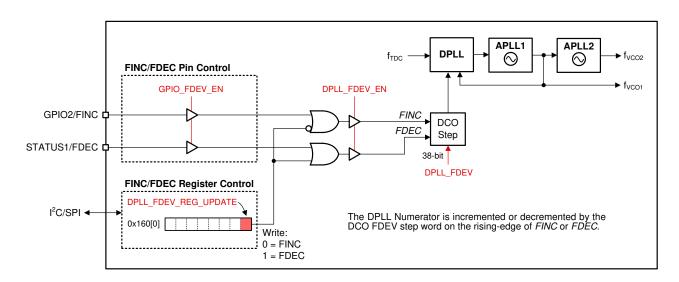

- DCO 模式: < 0.001ppb/阶跃,可进行精确的时 钟控制 (IEEE 1588 PTP 从运行)

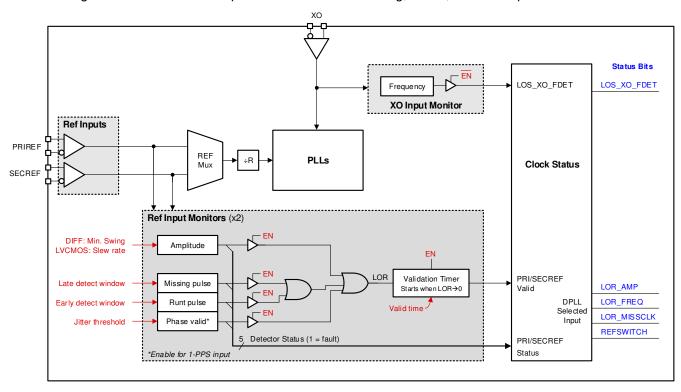

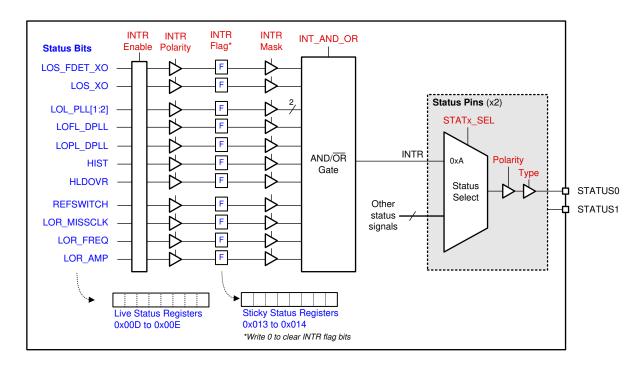

- 先进的时钟监控和状态

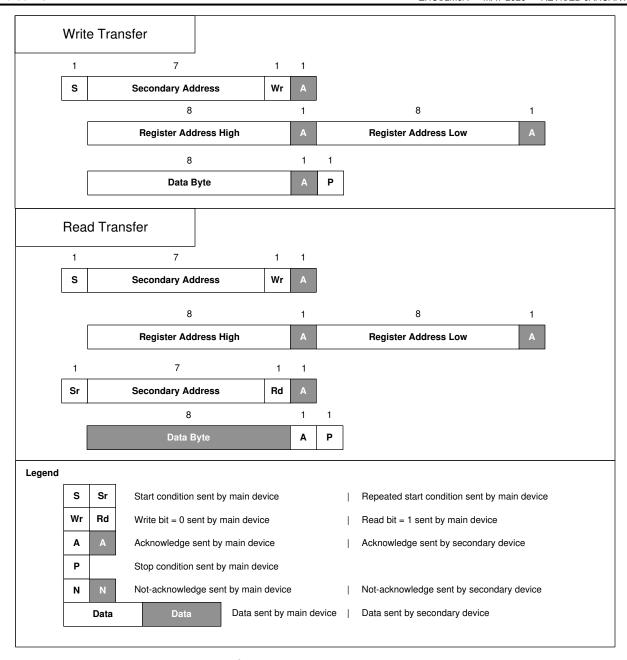

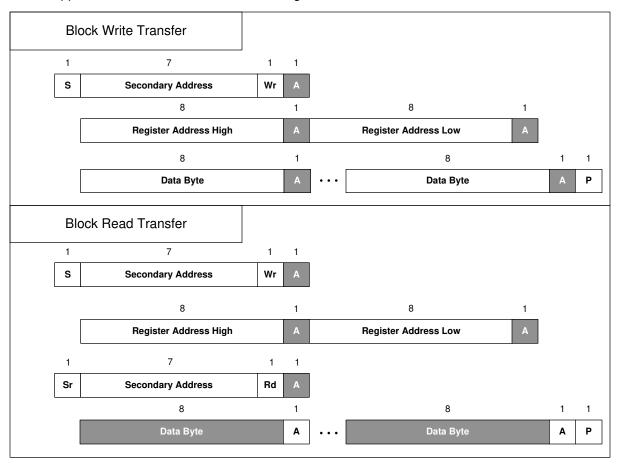

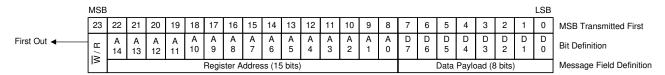

- I<sup>2</sup>C 或 SPI 接口

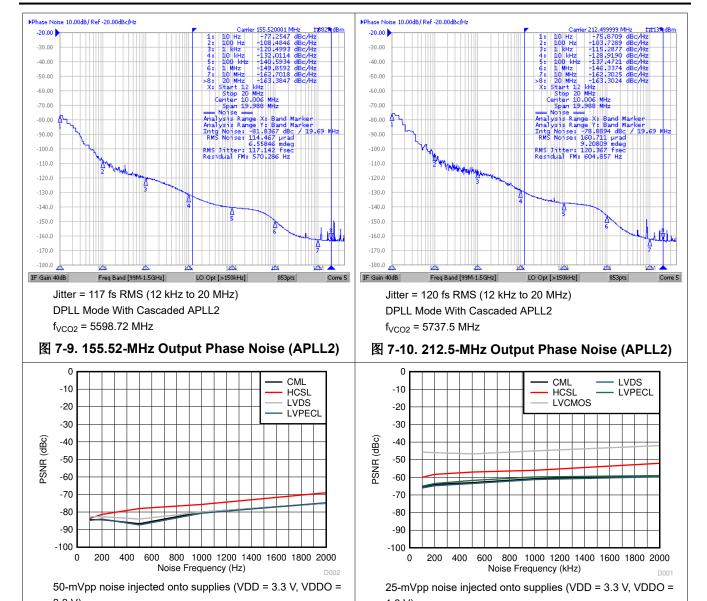

- PSNR: -83dBc(3.3V电源下噪声为 50mVpp)

- 3.3V 电源,提供 1.8V、2.5V 或 3.3V 输出

- 工业温度范围: -40°C至+85°C

# 2 应用

- SyncE (G.8262), SONET/SDH (Stratum 3/3E, G.813、GR-1244、GR-253)、IEEE 1588 PTP 从 时钟,或光传输网络(G.709)

- 用于以太网交换机和路由器的 400G 线卡、网络卡

- 无线基站 (BTS)、无线回程

- 测试与测量、医疗成像

- 56G/112G PAM-4 PHY、ASIC、FPGA、SoC 和处 理器的抖动消除、漂移衰减和基准时钟生成

# 3 说明

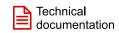

LMK5B12204 是一款高性能网络同步器时钟器件,提 供抖动消除、时钟生成、先进的时钟监控和卓越的无中 断切换性能,可满足通信基础设施和工业应用的严格时 序要求。该器件具有超低抖动和高电源噪声抑制 (PSNR) 性能,可降低高速串行链路中的误码率 (BER)。

该器件可使用 TI 专有的体声波 (BAW) VCO 技术生成 具有 50fs RMS 抖动的输出时钟,而不受 XO 和基准输 入的抖动和频率的影响。

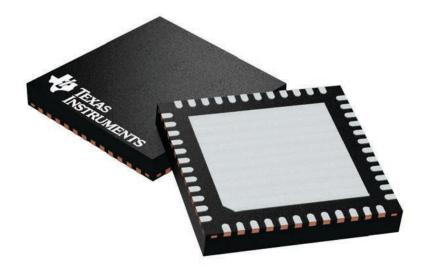

#### 器件信息

|            | PP 1 1 1          |                 |  |

|------------|-------------------|-----------------|--|

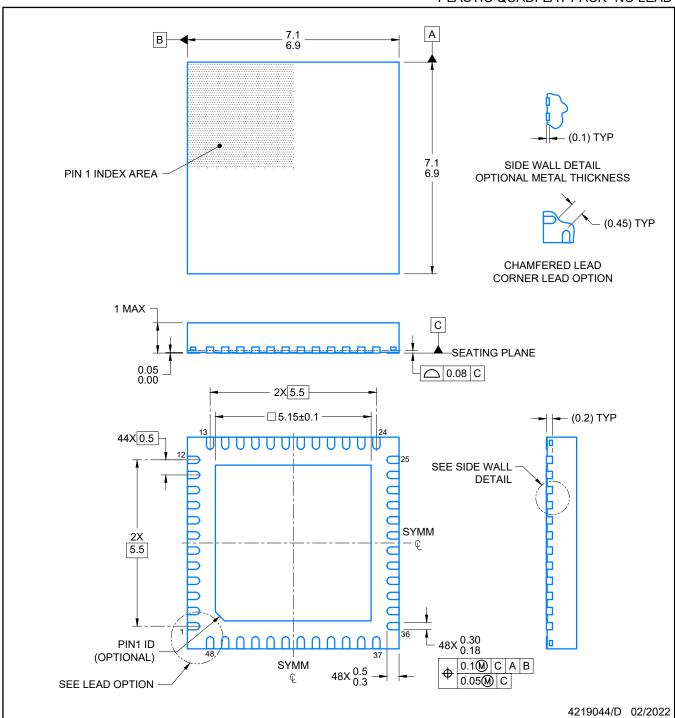

| 器件型号       | 封装 <sup>(1)</sup> | 封装尺寸 ( 标称值 )    |  |

| LMK5B12204 | VQFN (48)         | 7.00mm × 7.00mm |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

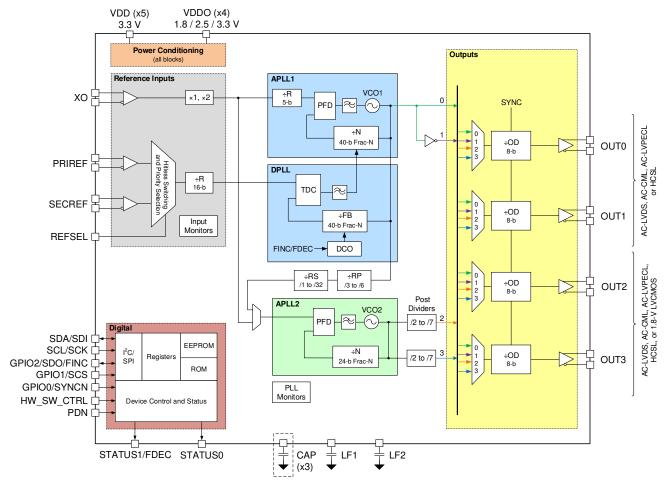

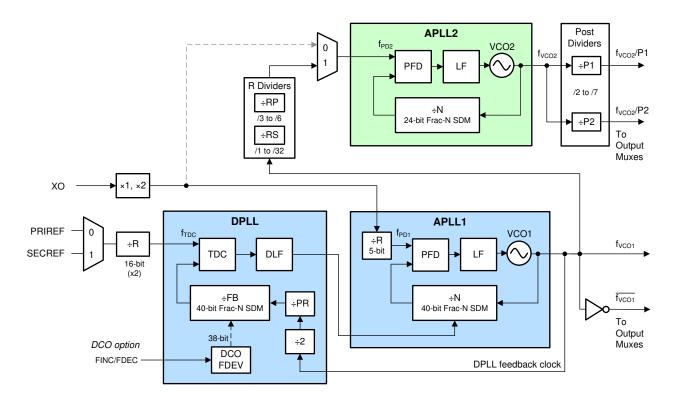

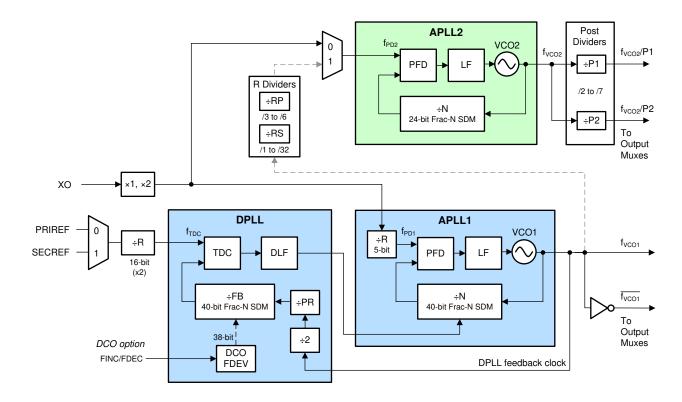

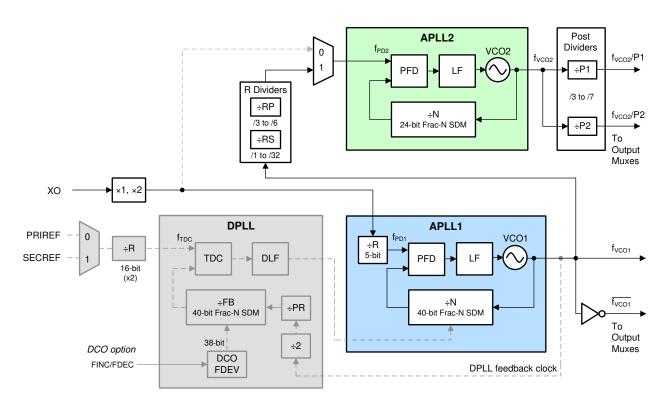

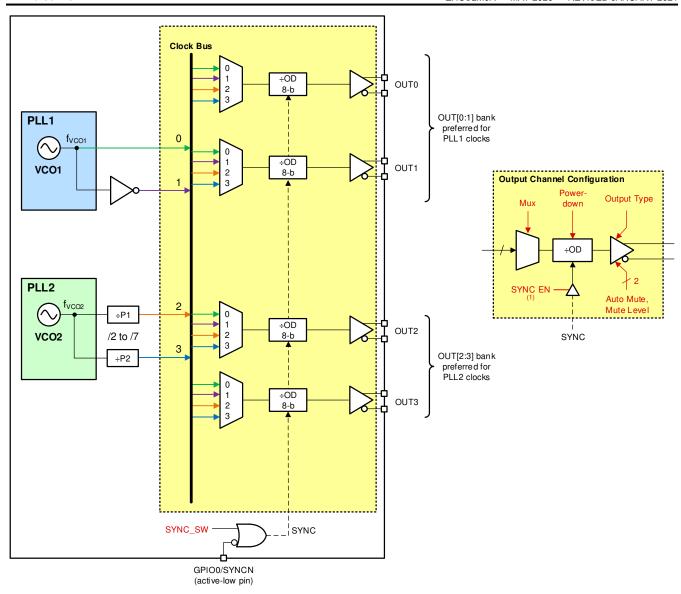

简化版方框图

# **Table of Contents**

| 1 特性                                            | 1  | 9.4 Device Functional Modes               | 5          |

|-------------------------------------------------|----|-------------------------------------------|------------|

| 2 应用                                            |    | 9.5 Programming                           | 59         |

| 3 说明                                            |    | 10 Application and Implementation         | 67         |

| 4 Revision History                              |    | 10.1 Application Information              | 67         |

| 5 说明(续)                                         |    | 10.2 Typical Application                  |            |

| 6 Pin Configuration and Functions               |    | 10.3 Do's and Don'ts                      |            |

| 6.1 Device Start-Up Modes                       |    | 11 Power Supply Recommendations           |            |

| 7 Specifications                                |    | 11.1 Power Supply Bypassing               | 76         |

| 7.1 Absolute Maximum Ratings                    |    | 11.2 Device Current and Power Consumption | 76         |

| 7.2 ESD Ratings                                 |    | 12 Layout                                 | 78         |

| 7.3 Recommended Operating Conditions            |    | 12.1 Layout Guidelines                    |            |

| 7.4 Thermal Information: 4-Layer JEDEC Standard |    | 12.2 Layout Example                       | <b>7</b> 8 |

| PCB                                             | 9  | 12.3 Thermal Reliability                  |            |

| 7.5 Thermal Information: 10-Layer Custom PCB    |    | 13 Device and Documentation Support       |            |

| 7.6 Electrical Characteristics                  |    | 13.1 Device Support                       |            |

| 7.7 Timing Diagrams                             | 16 | 13.2 接收文档更新通知                             | 8          |

| 7.8 Typical Characteristics                     |    | 13.3 支持资源                                 | 80         |

| 8 Parameter Measurement Information             |    | 13.4 Trademarks                           | 80         |

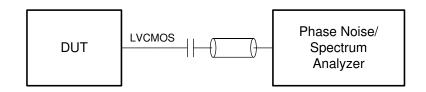

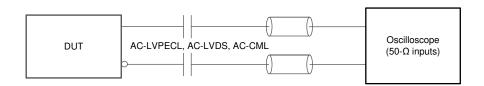

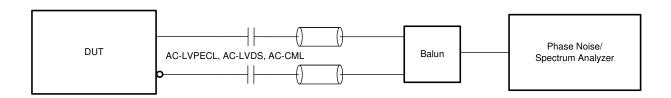

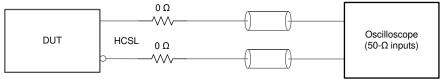

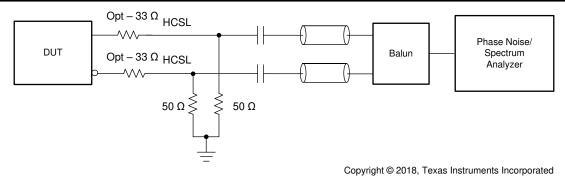

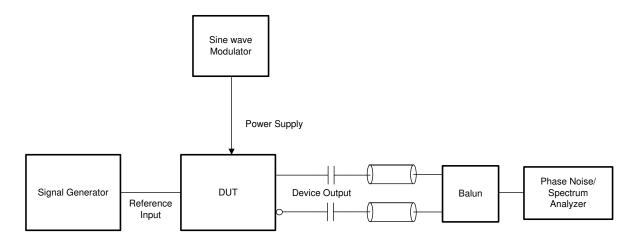

| 8.1 Output Clock Test Configurations            |    | 13.5 静电放电警告                               | 80         |

| 9 Detailed Description                          |    | 13.6 术语表                                  | 8          |

| 9.1 Overview                                    |    | 14 Mechanical, Packaging, and Orderable   |            |

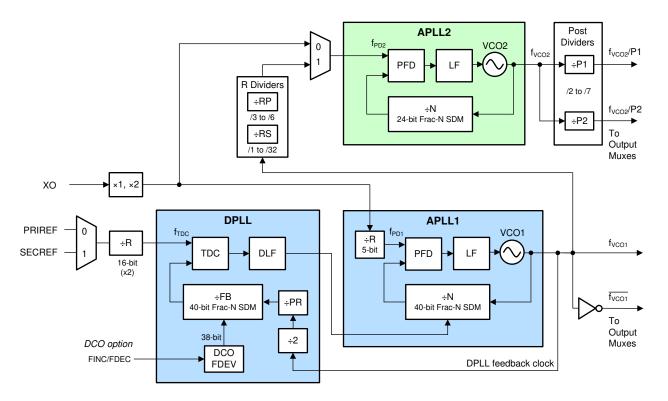

| 9.2 Functional Block Diagram                    | 24 | Information                               | 8          |

| 9.3 Feature Description                         |    | 14.1 Package Option Addendum              | 8          |

|                                                 |    |                                           |            |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision * (May 2020) to Revision A (January 2021)                    | Page |

|---|-----------------------------------------------------------------------------------|------|

| • | 将 155.52MHz 时的典型 RMS 抖动从 130fs 更改为 125fs                                          | 1    |

| • | Changed the maximum APLL1 PFD frequency from 50 MHz to 80 MHz                     | 9    |

| • | Changed the maximum AC-LVDS output frequency from 800 MHz to 1250 MHz             | 9    |

| • | Changed the maximum AC-CML output frequency from 800 MHz to 1250 MHz              | 9    |

| • | Changed the maximum AC-LVPECL output frequency from 800 MHz to 1250 MHz           | 9    |

| • | Changed the output format in RMS jitter test conditions from AC-DIFF to AC-LVPECL | 9    |

| • | Changed the max RMS jitter for 312.5 MHz from 100 fs to 80 fs                     | 9    |

| • | Changed the max RMS jitter for 156.25 MHz from 100 fs to 90 fs                    | 9    |

| • | Changed the max RMS jitter for 153.6 MHz from 250 fs to 200 fs                    | 9    |

| • | Changed the max RMS jitter for 155.52 MHz from 250 fs to 200 fs                   | 9    |

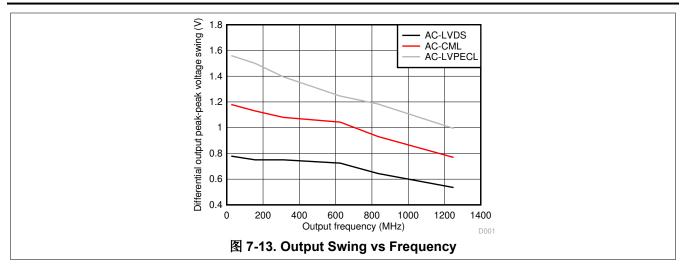

|   | Added typical performance plot for output voltage swing vs. output frequency      |      |

|   | Added descriptions for reference frequency monitoring                             |      |

# 5 说明(续)

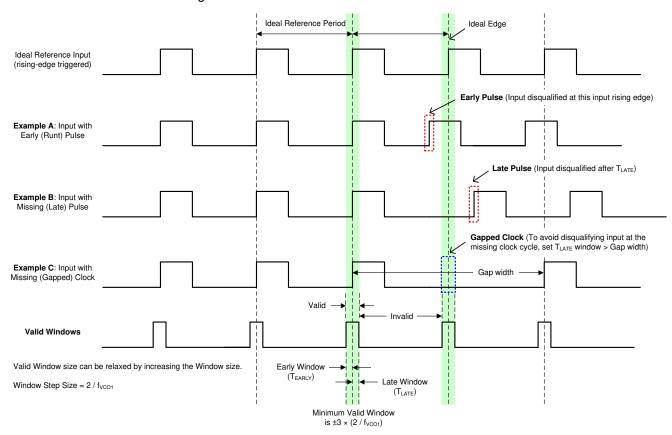

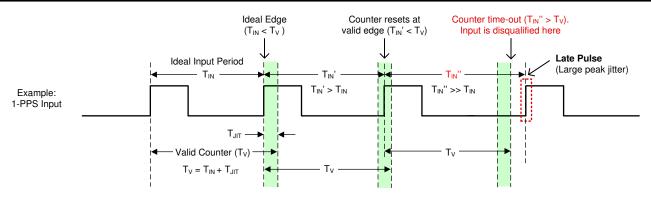

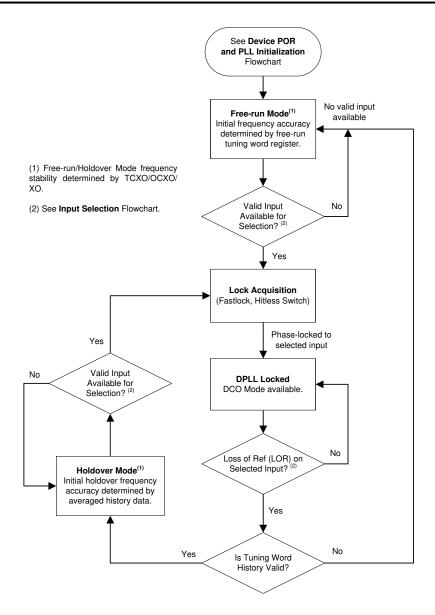

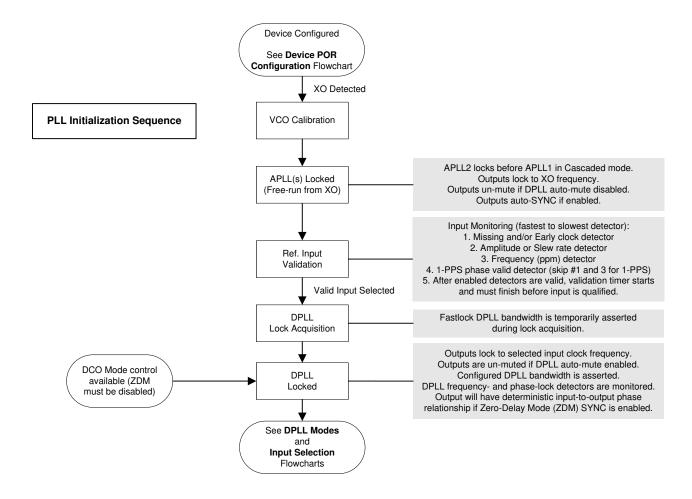

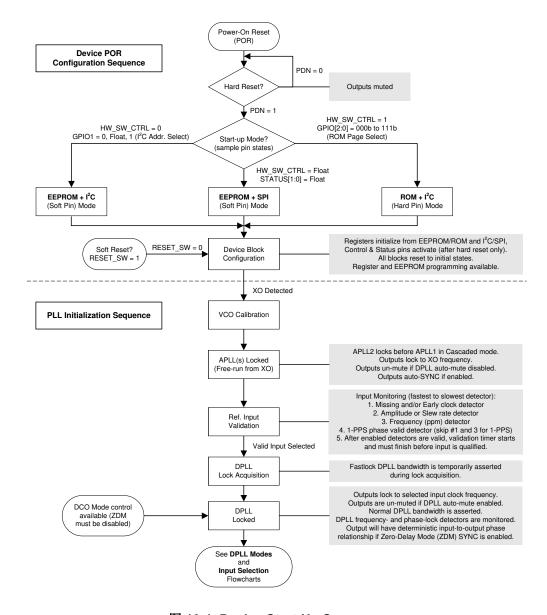

DPLL 支持抖动和漂移衰减的可编程环路带宽,而两个 APLL 支持分频率转换,从而可以实现灵活的时钟生成。DPLL 上支持的同步选项包括采用相位消除的无中断切换、数字保持和频率阶跃小于 0.001ppb(十亿分之一)的 DCO 模式,从而实现精确的时钟控制(IEEE 1588 PTP 从运行)。DPLL 可以锁相到 1 PPS(每秒脉冲数)基准输入,。先进的基准输入监控块可确保稳健的时钟故障检测并在发生基准缺失 (LOR) 时帮助将输出时钟干扰降至最低。

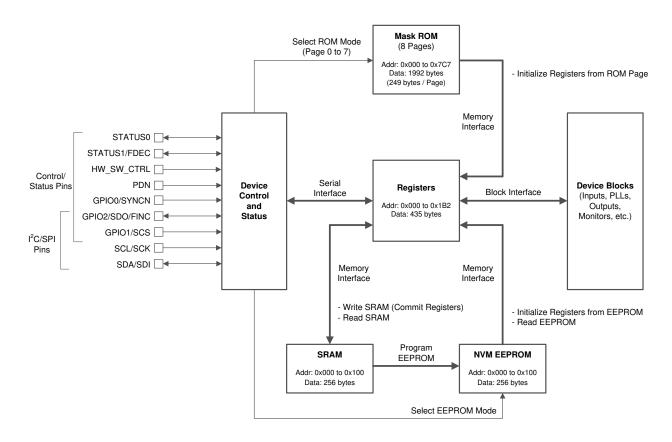

该器件可以使用通用的低频 TCXO 或 OCXO 来根据同步标准设置自由运行型或保持型输出频率稳定性。否则,在自由运行型或保持型频率稳定性和漂移不重要时,该器件可以使用标准 XO。该器件可通过 I<sup>2</sup>C 或 SPI 接口实现完全编程,在通电后支持通过内部 EEPROM 或 ROM 进行自定义频率配置。EEPROM 在出厂时进行了预编程,且可根据需要进行系统内编程。

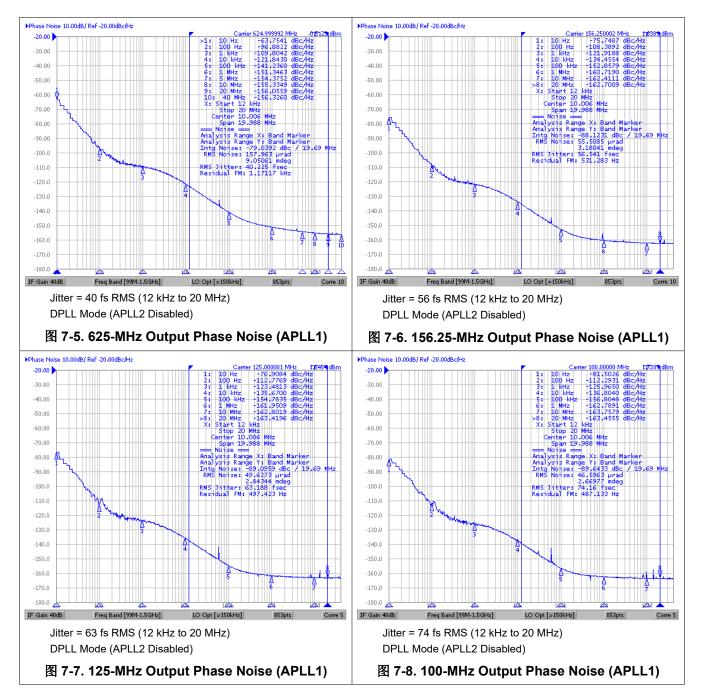

请参阅节 7.8,以了解测试条件。

图 5-1. 312.5MHz 输出相位噪声 (APLL1), < 50fs RMS 抖动

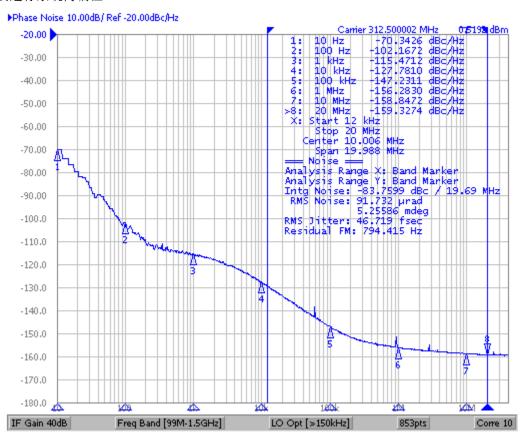

# **6 Pin Configuration and Functions**

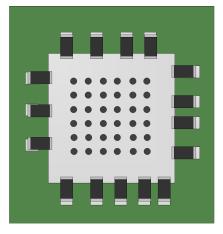

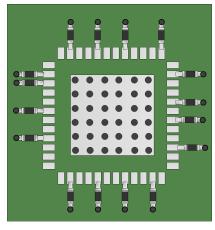

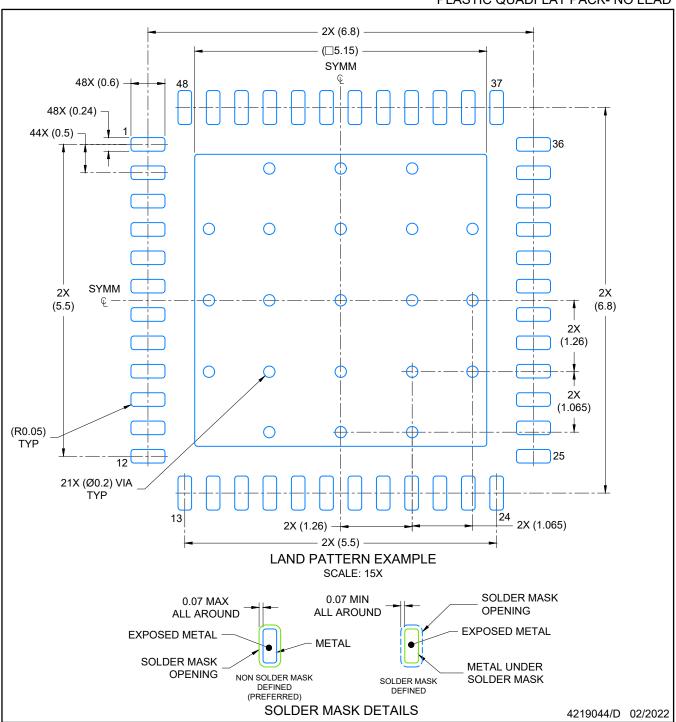

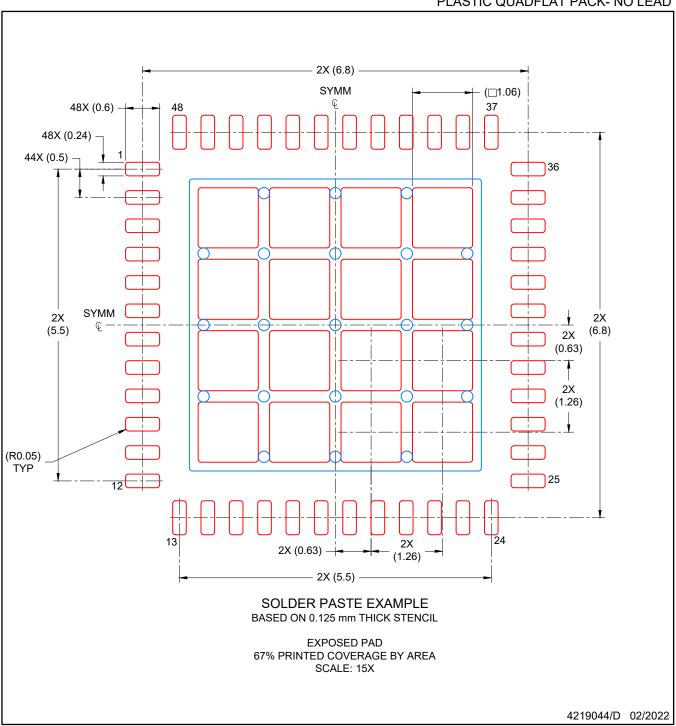

图 6-1. RGZ Package 48-Pin VQFN Top View

表 6-1. Pin Functions

| PIN         |        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.    | IIFE\/              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| POWER       |        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

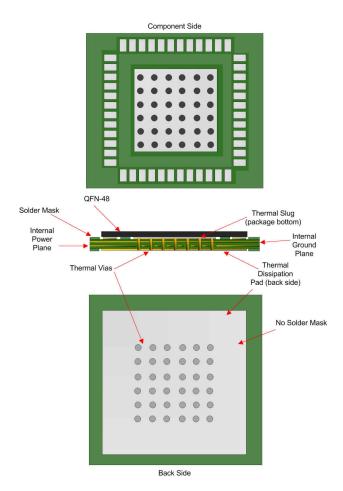

| GND         | PAD    | G                   | Ground / Thermal Pad.  The exposed pad must be connected to PCB ground for proper electrical and thermal performance.  A 5×5 via pattern is recommended to connect the IC ground pad to the PCB ground layers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| VDD_IN      | 5      | Р                   | Core Supply (3.3 V) for Primary and Secondary Reference Inputs. Place a nearby 0.1-µF bypass capacitor on each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| VDD_XO      | 33     | Р                   | Core Supply (3.3 V) for XO Input. Place a nearby 0.1-µF bypass capacitor on each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| VDD_PLL1    | 27     | Р                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| VDD_PLL2    | 36     | Р                   | Core Supply (3.3 V) for PLL1, PLL2, and Digital Blocks.  Place a nearby 0.1-µF bypass capacitor on each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| VDD_DIG     | 4      | Р                   | The second means of the second |  |

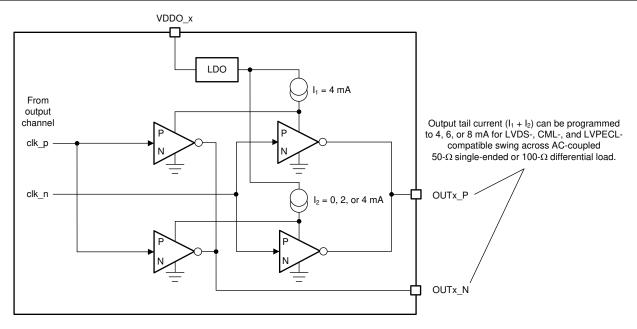

| VDDO_0      | 18     | Р                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| VDDO_1      | 19     | Р                   | Output Supply (1.8, 2.5, or 3.3 V) for Clock Outputs 0 to 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| VDDO_2      | 37, 40 | Р                   | Place a nearby 0.1-μF bypass capacitor on each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| VDDO_3      | 43, 46 | Р                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| CORE BLOCKS | ,      | •                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

# 表 6-1. Pin Functions (continued)

| PIN                                                                                                                                                                                                                                                                                                                                                               |     | (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 0-1.1 III I diletions (continued)                                                                                                                                                                                         |  |                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                              | NO. | TYPE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DESCRIPTION                                                                                                                                                                                                                 |  |                                            |

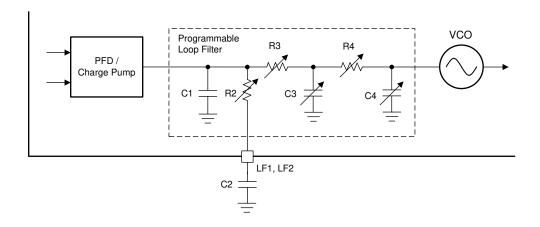

| LF1                                                                                                                                                                                                                                                                                                                                                               | 29  | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External Loop Filter Capacitor for APLL1 and APLL2.                                                                                                                                                                         |  |                                            |

| LF2                                                                                                                                                                                                                                                                                                                                                               | 34  | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Place a nearby capacitor on each pin. For LF1, a 0.47-µF capacitor is suggested for typical APLL1 loop bandwidths around 1.0 kHz. For LF2, a 0.1-µF capacitor is suggested for typical APLL2 loop bandwidth around 500 kHz. |  |                                            |

| CAP_PLL1                                                                                                                                                                                                                                                                                                                                                          | 28  | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                             |  |                                            |

| CAP_PLL2                                                                                                                                                                                                                                                                                                                                                          | 35  | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External Bypass Capacitors for APLL1, APLL2, and Digital Blocks.  Place a nearby 10-uF bypass capacitor on each pin.                                                                                                        |  |                                            |

| CAP_DIG                                                                                                                                                                                                                                                                                                                                                           | 3   | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | That a hearby to an expansion of each pin.                                                                                                                                                                                  |  |                                            |

| INPUT BLOCKS                                                                                                                                                                                                                                                                                                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                             |  |                                            |

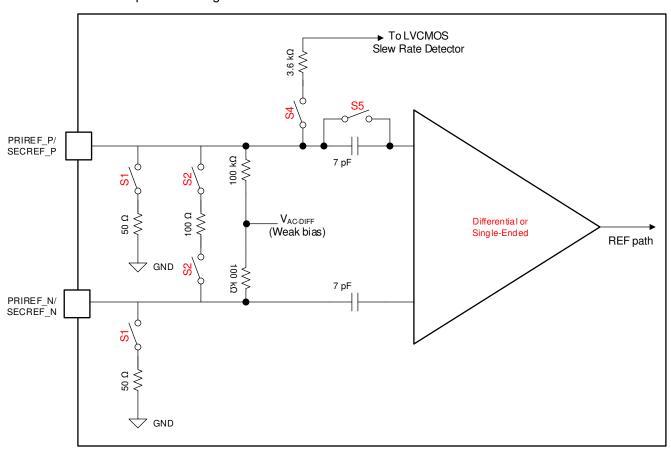

| PRIREF_P                                                                                                                                                                                                                                                                                                                                                          | 6   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DPLL Primary and Secondary Reference Clock Inputs.                                                                                                                                                                          |  |                                            |

| PRIREF_N                                                                                                                                                                                                                                                                                                                                                          | 7   | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Each input pair can accept a differential or single-ended clock as a reference to the DPLL. Each pair has a programmable input type with internal termination to support AC- or DC-coupled clocks. A                        |  |                                            |

| SECREF_P                                                                                                                                                                                                                                                                                                                                                          | 10  | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | single-ended LVCMOS clock can be applied to the P input with the N input pulled down to ground.                                                                                                                             |  |                                            |

|                                                                                                                                                                                                                                                                                                                                                                   | 11  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                             |  | An unused input pair can be left floating. |

| SECREF_N                                                                                                                                                                                                                                                                                                                                                          |     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | For low-frequency input, an internal AC-coupling capacitor can be disabled to improve noise                                                                                                                                 |  |                                            |

|                                                                                                                                                                                                                                                                                                                                                                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | immunity. Differential Input and LVCMOS input can be DC-coupled to the receiver.                                                                                                                                            |  |                                            |

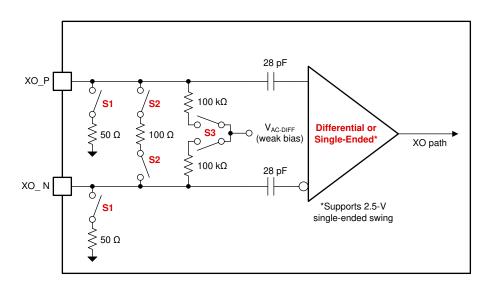

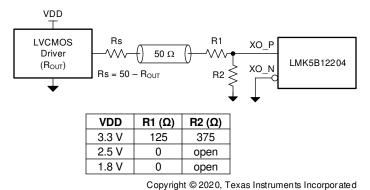

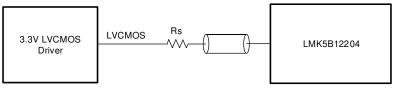

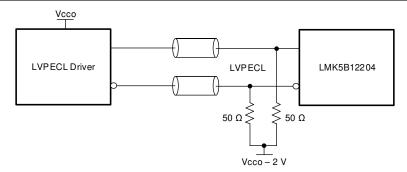

| XO_P                                                                                                                                                                                                                                                                                                                                                              | 31  | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XO/TCXO/OCXO Input.  This input pair can accent a differential or single ended clock signal from a low-litter local oscillator.                                                                                             |  |                                            |

| Support AC- or DC-coupled clocks. A single-ended LVCMOS clock (up the P input with the N input pulled down to ground. A low-frequency TC set the clock output frequency accuracy and stability during free-run ar In DPLL mode, the XO frequency must have a non-integer relationship APLL1 can operate in fractional mode (required for proper DPLL operations). |     | as a reference to the APLLs. This input has a programmable input type with internal termination to support AC- or DC-coupled clocks. A single-ended LVCMOS clock (up to 2.5 V) can be applied to the P input with the N input pulled down to ground. A low-frequency TCXO or OCXO can be used to set the clock output frequency accuracy and stability during free-run and holdover modes. In DPLL mode, the XO frequency must have a non-integer relationship to the VCO1 frequency so APLL1 can operate in fractional mode (required for proper DPLL operation). In APLL-only mode, the XO frequency can have either an integer or non-integer relationship to the VCO1 frequency. |                                                                                                                                                                                                                             |  |                                            |

| OUTPUT BLOCKS                                                                                                                                                                                                                                                                                                                                                     | S   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                             |  |                                            |

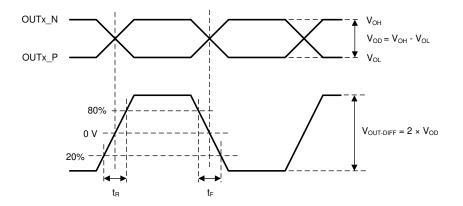

| OUT0_P                                                                                                                                                                                                                                                                                                                                                            | 17  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Clock Outputs 0 and 1 Bank.                                                                                                                                                                                                 |  |                                            |

| OUT0_N                                                                                                                                                                                                                                                                                                                                                            | 16  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Each programmable output driver pair can support AC-LVDS, AC-CML, AC-LVPECL, and HCSL.  Unused differential outputs should be terminated if active or left floating if disabled through                                     |  |                                            |

| OUT1_P                                                                                                                                                                                                                                                                                                                                                            | 20  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | registers.                                                                                                                                                                                                                  |  |                                            |

| OUT1_N                                                                                                                                                                                                                                                                                                                                                            | 21  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The OUT[0:1] bank is preferred for PLL1 clocks to minimize output crosstalk.                                                                                                                                                |  |                                            |

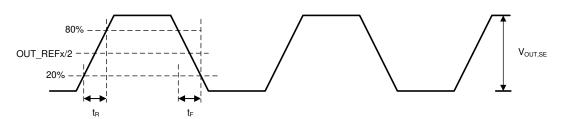

| OUT2_P                                                                                                                                                                                                                                                                                                                                                            | 42  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Clock Outputs 2 and 3 Bank.                                                                                                                                                                                                 |  |                                            |

| OUT2_N                                                                                                                                                                                                                                                                                                                                                            | 41  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Each programmable output driver pair can support AC-LVDS, AC-CML, AC-LVPECL, HCSL, or 1.8-<br>V LVCMOS clocks (one or two per pair). Unused differential outputs should be terminated if active                             |  |                                            |

| OUT3_P                                                                                                                                                                                                                                                                                                                                                            | 45  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | or left floating if disabled through registers.                                                                                                                                                                             |  |                                            |

| OUT3_N                                                                                                                                                                                                                                                                                                                                                            | 44  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The OUT[2:3] bank is preferred for PLL2 clocks to minimize output crosstalk. When PLL2 is not used, the OUT[2:3] bank can be used for PLL1 clocks without risk of cross-coupling from PLL2.                                 |  |                                            |

# 表 6-1. Pin Functions (continued)

| PIN                |         | TVDE(1)             | D.T.O.D.ID.T.O.U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------------------|---------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME               | NO.     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| LOGIC CONTROL      | / STATU | S (2) (3)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

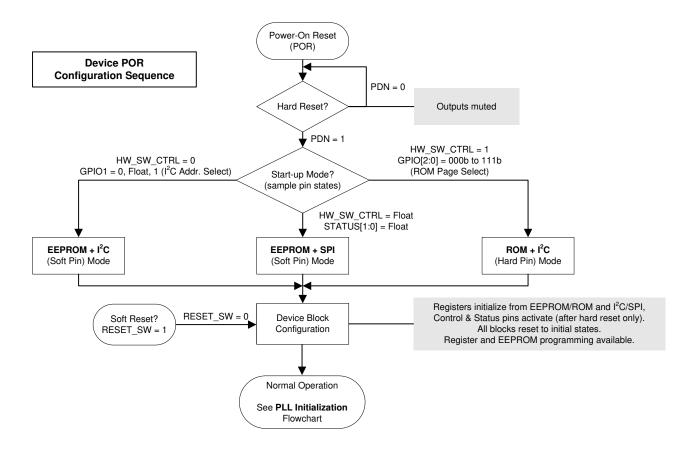

| HW_SW_CTRL         | 9       | I                   | Device Start-Up Mode Select (3-level, 1.8-V compatible). This input selects the device start-up mode that determines the memory page used to initialize the registers, serial interface, and logic pin functions. The input level is sampled only at device power-on reset (POR). See 表 6-2 for start-up mode descriptions and logic pin functions.                                                                                                                                                                                                                                                                                                                                         |  |

| PDN                | 13      | I                   | Device Power-Down (active low).  When PDN is pulled low, the device is in hard-reset and all blocks including the serial interface are powered down. When PDN is pulled high, the device is started according to device mode selected by HW_SW_CTRL and begins normal operation with all internal circuits reset to their initial state.                                                                                                                                                                                                                                                                                                                                                    |  |

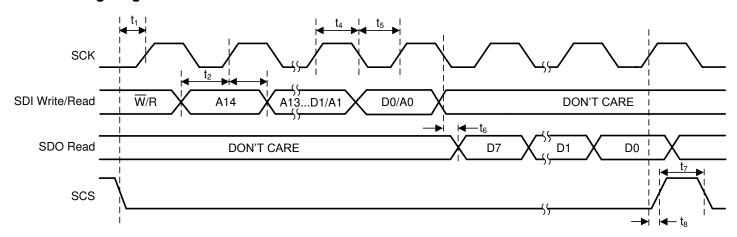

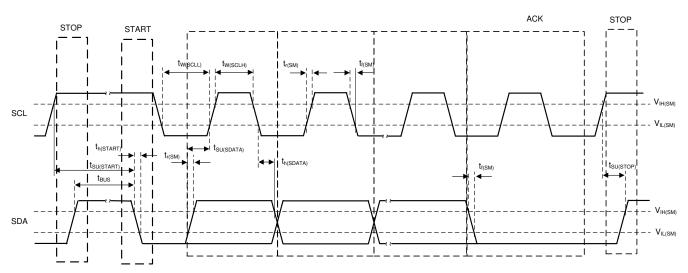

| SDA/SDI            | 25      | I/O                 | I <sup>2</sup> C Serial Data I/O (SDA) or SPI Serial Data Input (SDI). See 表 6-2. When HW_SW_CTRL is 0 or 1, the serial interface is I <sup>2</sup> C. SDA and SCL pins (open-drain) require external I <sup>2</sup> C pullup resistors. The default 7-bit I <sup>2</sup> C address is 11001xxb, where the MSB bits (11001b) are initialized from on-chip EEPROM and the LSB bits (xxb) are determined by the logic input pins. When HW_SW_CTRL is 0, the LSBs are determined by the GPIO1 input state (3-level) during POR. When HW_SW_CTRL is 1, the LSBs are fixed to 00b. When HW_SW_CTRL is Float, the serial interface is SPI (4-wire, Mode 0) using the SDI, SCK, SCS, and SDO pins. |  |

| SCL/SCK            | 26      | I                   | I <sup>2</sup> C Serial Clock Input (SCL) or SPI Serial Clock Input (SCK). See 表 6-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| GPIO0/SYNCN        | 12      | I                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| GPIO1/SCS          | 24      | I                   | Multifunction Inputs or Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| GPIO2/SDO/<br>FINC | 30      | I/O                 | See 表 6-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| STATUS0            | 1       | I/O                 | Status Outputs 0 and 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

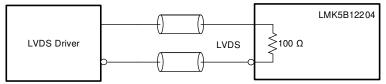

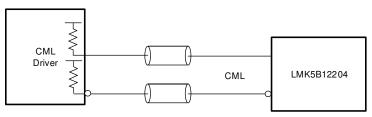

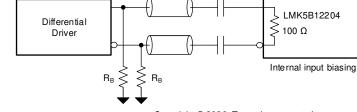

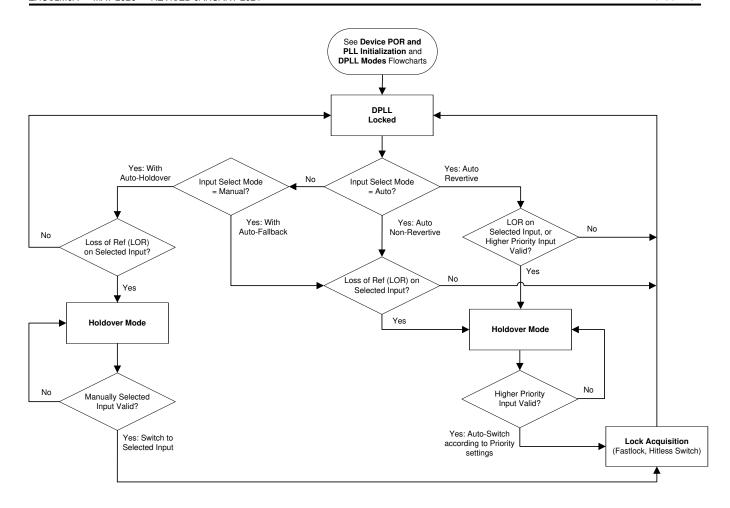

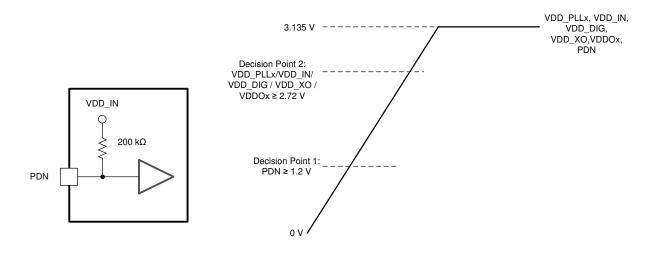

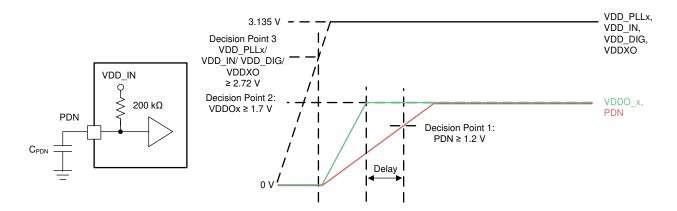

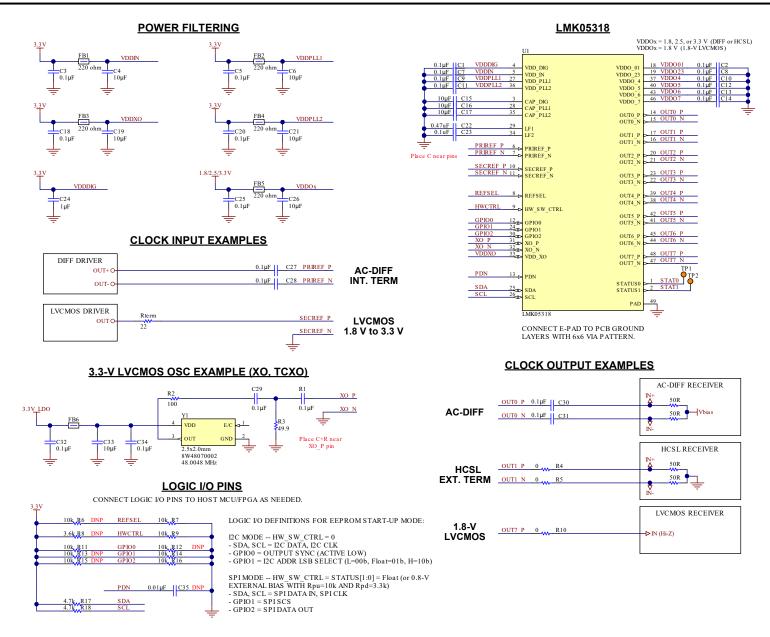

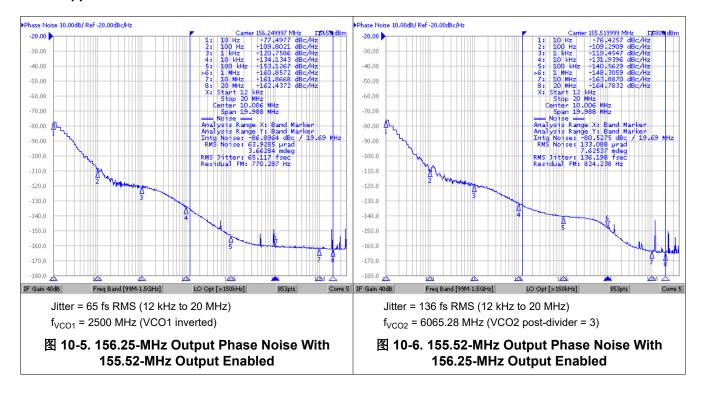

| STATUS1/<br>FDEC   | 2       | I/O                 | Each output has programmable status signal selection, driver type (3.3-V LVCMOS or open-drain), and status polarity. Open-drain requires an external pullup resistor. Leave pin floating if unused. In I <sup>2</sup> C mode, the STATUS1/FDEC pin can function as a DCO mode control input pin. See 表 6-2.                                                                                                                                                                                                                                                                                                                                                                                 |  |