ZHCS747D - JANUARY 2012 - REVISED SEPTEMBER 2021

# LMK01801 双时钟分频缓冲器

# 1 特性

- 引脚控制模式或 MICROWIRE (SPI) •

- 输入和输出频率范围:1 kHz 至 3.1 GHz

- 针对时钟输出组 A 和 B 的单独输入

- 两组(A和B)中的14个差分时钟输出

- 输出组 A

Texas

INSTRUMENTS

- 8个差分、可编程输出 (如同 LVCMOS 多达 8个)

- 分压器值为1至8,偶数和奇数。

- 输出组 B

- 6个差分输出 (或如同 LVCMOS 多达 12 个)

- 将数值1到1045或1到8分频,偶数和奇 数

- 模拟和数字延迟

- 所有分频的所有输出均为 50% 占空比

- A 组和 B 组分别同步。

- 在 800MHz 时的 RMS 附加抖动为 50fs。

- 50fs RMS 附加抖动 (12kHz 至 20MHz )

- 工业温度范围: 40°C 至 85°C

- 3.15V 至 3.45V 工作电压 •

# 2 应用

- 高性能的时钟分配和分频

- 无线基础设施

- 数据通信和电信时钟分配

- 医疗成像

- 测试和测量

- 军用/航天

# 3 说明

LMK01801 是针对时钟系统的一种超低噪音的解决方 案,需要精确时钟的分配和频率分频。

LMK01801 具有超低残余噪声、频率分频、数字和模 拟延迟调整以及十四 (14) 个可编程差分输出: LVPECL、LVDS 和 LVCMOS (每个差分输出有 2 个 输出)。

LMK01801 具有两个独立输入,该输入可采用差分驱 动(LVDS、LVPECL)或以单端模式驱动 (LVCMOS、RF Sinewave)。第一个输入驱动包括 八 (8) 个输出的输出组 A。第二个输入驱动包括六 (6) 个输出的输出组 B。

#### 器件信息(1)

| 器件型号     | 封装        | 封装尺寸            |

|----------|-----------|-----------------|

| LMK01801 | VQFN (48) | 7.00mm × 7.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1) 录。

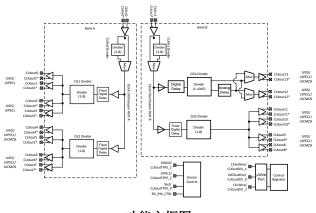

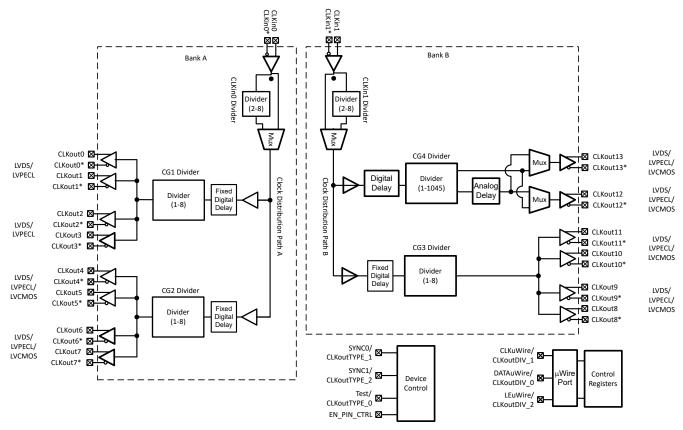

功能方框图

# **Table of Contents**

| 1 | 特性                                               | 1              |

|---|--------------------------------------------------|----------------|

| 2 | 应用                                               | 1              |

|   | 说明                                               |                |

|   | Revision History                                 |                |

| 5 | Device Comparison                                | 4              |

|   | 5.1 Functional Configurations                    |                |

| 6 | Pin Configuration and Functions                  | 5              |

| 7 | Specifications                                   | 7              |

|   | 7.1 Absolute Maximum Ratings                     | 7              |

|   | 7.2 Recommended Operating Conditions             | 7              |

|   | 7.3 Thermal Information                          | 7              |

|   | 7.4 Electrical Characteristics                   | <mark>8</mark> |

|   | 7.5 Serial MICROWIRE Timing Diagram              |                |

|   | 7.6 Typical Characteristics                      | 12             |

| 8 | Parameter Measurement Information                | 13             |

|   | 8.1 Differential Voltage Measurement Terminology | 13             |

| 9 | Detailed Description                             |                |

|   | 9.1 Overview                                     | 14             |

|   | 9.2 Functional Block Diagram                     | 14             |

|   | 9.3 Feature Description                          | 14             |

| 9.4 Device Functional Modes             | 17 |

|-----------------------------------------|----|

| 9.5 Programming                         |    |

| 9.6 Register Map                        |    |

| 10 Application and Implementation       |    |

| 10.1 Typical Application                |    |

| 11 Power Supply Recommendations         |    |

| 11.1 Current Consumption                |    |

| 12 Layout                               | 49 |

| 12.1 Layout Guidelines                  | 49 |

| 12.2 Thermal Management                 |    |

| 13 Device and Documentation Support     |    |

| 13.1 Documentation Support              |    |

| 13.2 接收文档更新通知                           |    |

| 13.3 支持资源                               | 50 |

| 13.4 Trademarks                         |    |

| 13.5 Electrostatic Discharge Caution    |    |

| 13.6 术语表                                |    |

| 14 Mechanical, Packaging, and Orderable |    |

| Information                             |    |

|                                         |    |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision C (October 2019) to Revision D (September 2021)                              | Page  |

|---|---------------------------------------------------------------------------------------------------|-------|

| • | Updated Delay column for Clock Output Configurations table                                        | 4     |

| • | Added Fixed Digital Delay note for Clock Output Configurations table                              |       |

| • | Changed Absolute Maximum Ratings note 1                                                           | 7     |

| • | Added Fixed Digital Delay block for CLKout0 to CLKout11 in Functional Block Diagram               |       |

| • | Changed content and renamed Large Divider (1 to 1045) section to CLKout0 to CLKout11 Digital Dela | iy 15 |

| • | Added CLKoutX_Y_OFFSET_PD description to the <i>Fixed Digital Delay</i> section                   | 17    |

| • | Added CLKoutX_Y_OFFSET_PD description to SYNC Timing section                                      | 19    |

| • | Added CLKoutX_Y_OFFSET_PD to 图 9-1                                                                |       |

| • | Added CLKoutX_Y_OFFSET_PD to 图 9-2                                                                |       |

| • | Added CLKoutX_Y_OFFSET_PD to the <i>Register Map</i> table                                        |       |

| • | Added CLKoutX_Y_OFFSET_PD fields to the Default Device Register Settings table                    |       |

| • | Added CLKoutX_Y_OFFSET_PD section                                                                 |       |

| С | hanges from Revision B (January 2019) to Revision C (October 2019)                                | Page  |

| • | Changed Test/CLKoutTYPE_0 type from: I to: I/O                                                    | 5     |

| • | Added propagation delay parameter in the <i>Electrical Characteristics</i> table                  | 8     |

| • | Added note to Clock Output Synchronization (SYNC) section                                         |       |

| • | Changed Clock Output Synchronization Using the SYNC1 Pin graphic                                  |       |

| • | Changed the Relative Dynamic Digital Delay Programming Example, 2nd Adjust graphic                |       |

| • | Changed divide value for 1 (0x01) in the CLKinX_DIV table from: 2 to: 1 | 32 |

|---|-------------------------------------------------------------------------|----|

| • | Changed CLKoutX Y Div, 2 Bits table title to: CLKoutX Y Div, 3 Bits     | 39 |

|   |                   | —                      |  |

|---|-------------------|------------------------|--|

| • | Added Unused GPIO | (CLKoutTYPE_X) section |  |

# Changes from Revision A (April 2013) to Revision B (January 2019)

Page

| CI | hanges from Revision * (April 2013) to Revision A (April 2013)                 | Page |

|----|--------------------------------------------------------------------------------|------|

| •  | Added Device and Documentation Support section                                 | 50   |

|    | Deleted T <sub>CR</sub> because readback is not supported                      |      |

| •  | Changed CLKinX_DIV condition to "2 to 8" from "1 to 8" for f <sub>CLKinX</sub> | 8    |

| •  | Changed polarity for pins 4,5 and 9,10 to be correct                           | 5    |

| •  | Added SPI note for Pin Control Mode Tables                                     | 4    |

|   |               | \ I                | ,        | · · ·     | , | <u> </u> |

|---|---------------|--------------------|----------|-----------|---|----------|

| • | Changed layou | t of National Data | Sheet to | TI format |   | <br>45   |

# 5 Device Comparison

# **5.1 Functional Configurations**

|  | Bank Input Clock<br>Group |         | Output<br>CLKoutX/CLKoutX* | Output Type | Outputs in<br>Divider Group | Divider Ratios | Delay                    |                                      |  |

|--|---------------------------|---------|----------------------------|-------------|-----------------------------|----------------|--------------------------|--------------------------------------|--|

|  |                           | CLKin0/ | CG1                        | 0 to 3      | LVDS/LVPECL                 | 0 to 3         | 1 to 8                   | Fixed Digital <sup>(2)</sup>         |  |

|  | Δ                         | CLKin0* | CG2                        | 4 to 7      | LVDS/LVPECL/<br>LVCMOS      | 4 to 7         | 1 to 8                   | Fixed Digital <sup>(2)</sup>         |  |

|  | В                         | CLKin1/ | CG3                        | 8 to 11     | LVDS/LVPECL/<br>LVCMOS      | 8 to 11        | 1 to 8                   | Fixed Digital <sup>(2)</sup>         |  |

|  | D CLKin1                  | CLKin1* | CG4                        | 12 and 13   | LVDS/LVPECL/<br>LVCMOS      | 12 and 13      | 1 to 1045 <sup>(1)</sup> | Digital and<br>Analog <sup>(3)</sup> |  |

#### 表 5-1. Clock Output Configurations

(1) Digital Delay will not work if CLKout12\_13\_DIV = 1.

(2) Fixed Digital Delay occurs when CLKoutX\_Y\_OFFSET\_PD = 0. See  $\ddagger$  9.4.5.

(3) See **节** 7.4

| Pin          | Output Groups                   | Pin=Low | Pin=Middle        | Pin=High |

|--------------|---------------------------------|---------|-------------------|----------|

| CLKoutTYPE 0 | CLKout0 to CLKout3              | LVDS    | Powerdown         | LVPECL   |

| CEROUTIFE_0  | CLKout4 to CLKout7              |         | LVCMOS (Norm/Inv) |          |

| CLKoutTYPE_1 | CLKout8 to CLKout11             | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

| CLKoutTYPE_2 | CLKout12 to CLKout13            | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

| CLKoutDIV_0  | CLKout0 to<br>CLKout3 Divider   | ÷ 1     | ÷ 4               | ÷ 2      |

| CLKoutDIV_1  | CLKout4 to<br>CLKout7 Divider   | ÷ 1     | ÷ 4               | ÷ 2      |

| CLKoutDIV 2  | CLKout8 to<br>CLKout11 Divider  | ÷ 1     | ÷ 4               | ÷ 2      |

| CENOUDIV_2   | CLKout12 to<br>CLKout13 Divider | ÷ 8     | ÷ 512             | ÷ 16     |

# 表 5-2. Pin Control Mode for EN\_PIN\_CTRL = Low<sup>(1)</sup>

(1) Floating is SPI. See <sup>††</sup> 9.4.2.

#### 表 5-3. Pin Control Mode for EN\_PIN\_CTRL = High<sup>(1) (2)</sup>

| Pin                          | Output Groups                   | Pin=Low | Pin=Middle        | Pin=High |

|------------------------------|---------------------------------|---------|-------------------|----------|

| CLKoutTYPE 0                 | CLKout0 to CLKout3              | LVDS    | LVPECL            | LVPECL   |

| CEROUTITIE_0                 | CLKout4 to CLKout7              | LVDS    | LVCMOS (Norm/Inv) |          |

| CLKoutTYPE_1<br>CLKoutTYPE_2 | CLKout8 to CLKout11             | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

|                              | CLKout12 to CLKout13            | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

| CLKoutDIV_0                  | CLKout0 to<br>CLKout7 Dividers  | ÷ 1     | ÷ 4               | ÷ 2      |

| CLKoutDIV_1                  | CLKout8 to<br>CLKout11 Divider  | ÷ 1     | ÷ 4               | ÷ 2      |

| CLKoutDIV_2                  | CLKout12 to<br>CLKout13 Divider | ÷ 4     | ÷ 512             | ÷ 16     |

(1) Digital Delay will not work if CLKout12\_13\_DIV = 1.

(2) See <sup>††</sup> 7.4

# **6** Pin Configuration and Functions

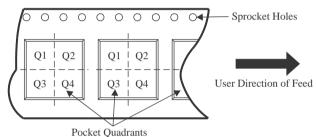

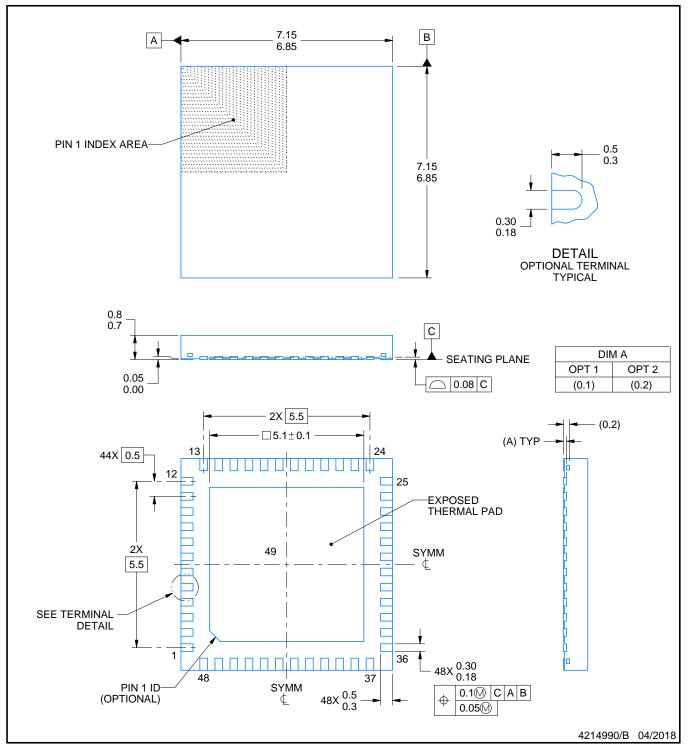

#### 图 6-1. 48-Pin Package

| 表 6- | 1. | Pin | Fund | ction | s <sup>(1)</sup> |

|------|----|-----|------|-------|------------------|

|------|----|-----|------|-------|------------------|

| Pin Number | Name(s)                 | I/O | Туре           | Description                                                         |

|------------|-------------------------|-----|----------------|---------------------------------------------------------------------|

| 1          | LEuWire/<br>CLKoutDIV_2 | I   | CMOS / 3-State | MICROWIRE Latch Enable Input /<br>Pin control mode: clock divider 2 |

| 2, 3       | CLKout0,<br>CLKout0*    | 0   | Programmable   | Clock output 0: LVDS or LVPECL                                      |

| 4, 5       | CLKout1*,<br>CLKout1    | 0   | Programmable   | Clock output 1: LVDS or LVPECL                                      |

| 6          | Vcc1_CLKout<br>0_1_2_3  | I   | PWR            | Power supply for clock outputs 0, 1, 2, and 3                       |

| 7, 8       | CLKout2,<br>CLKout2*    | 0   | Programmable   | Clock output 2: LVDS or LVPECL                                      |

| 9, 10      | CLKout3*,<br>CLKout3    | 0   | Programmable   | Clock output 3: LVDS or LVPECL                                      |

| 11         | Test/<br>CLKoutTYPE_0   | I/O | CMOS / 3-State | Reserved Test Pin /<br>Pin control mode: clock output type select 0 |

| 12         | SYNC0/<br>CLKoutTYPE_1  | I   | CMOS / 3-State | SYNC0 / Pin control mode: clock output type select 1                |

Copyright © 2021 Texas Instruments Incorporated

| 表 6-1. Pin Functions <sup>(1)</sup> (continued) |                           |     |                |                                                                                              |  |  |

|-------------------------------------------------|---------------------------|-----|----------------|----------------------------------------------------------------------------------------------|--|--|

| Pin Number                                      | Name(s)                   | I/O | Туре           | Description                                                                                  |  |  |

| 13, 14                                          | CLKin0,<br>CLKin0*        | I   | ANLG           | Clock input 0. Supports clocking types including but not limited to LVDS, LVPECL, and LVCMOS |  |  |

| 15                                              | Vcc2_CLKin0               | I   | PWR            | Power supply for clock input 0                                                               |  |  |

| 16, 17                                          | CLKout4,<br>CLKout4*      | 0   | Programmable   | Clock output 4: LVDS, LVPECL, or LVCMOS                                                      |  |  |

| 18, 19                                          | CLKout5*,<br>CLKout5      | 0   | Programmable   | Clock output 5: LVDS, LVPECL, or LVCMOS                                                      |  |  |

| 20                                              | Vcc3_CLKout<br>4_5_6_7    | I   | PWR            | Power supply for clock outputs 4, 5, 6, and 7                                                |  |  |

| 21, 22                                          | CLKout6,<br>CLKout6*      | 0   | Programmable   | Clock output 6: LVDS, LVPECL, or LVCMOS                                                      |  |  |

| 23, 24                                          | CLKout7*,<br>CLKout7      | 0   | Programmable   | Clock output 7: LVDS, LVPECL, or LVCMOS                                                      |  |  |

| 25                                              | Vcc4_Bias                 | I   | PWR            | Power supply for Bias                                                                        |  |  |

| 26                                              | Bias                      |     | ANLG           | Bias bypass pin                                                                              |  |  |

| 27                                              | EN_PIN_CTRL               | I   | 3-State        | Select MICROWIRE or pin control mode                                                         |  |  |

| 28, 29                                          | CLKout8,<br>CLKout8*      | 0   | Programmable   | Clock output 8: LVDS, LVPECL, or LVCMOS                                                      |  |  |

| 30, 31                                          | CLKout9*,<br>CLKout9      | 0   | Programmable   | Clock output 9: LVDS, LVPECL, or LVCMOS                                                      |  |  |

| 32                                              | Vcc5_CLKout<br>8_9_10_11  | I   | PWR            | Power supply for clock outputs 8, 9, 10, and 11                                              |  |  |

| 33, 34                                          | CLKout10,<br>CLKout10*    | 0   | Programmable   | Clock output 10: LVDS, LVPECL, or LVCMOS                                                     |  |  |

| 35, 36                                          | CLKout11*,<br>CLKout11    | 0   | Programmable   | Clock output 11: LVDS, LVPECL, or LVCMOS                                                     |  |  |

| 37                                              | Vcc6_CLKin1               | I   | PWR            | Power supply for clock input 1                                                               |  |  |

| 38, 39                                          | CLKin1,<br>CLKin1*        | I   | ANLG           | Clock input 1. Supports clocking types including but not limited to LVDS, LVPECL, and LVCMOS |  |  |

| 40                                              | SYNC1/<br>CLKoutTYPE_2    | I   | CMOS / 3-State | SYNC pin for CLKin1 and bank B.<br>Pin control mode: Clock output type select 2              |  |  |

| 41                                              | Vcc7_CLKout<br>12_13      | I   | PWR            | Power supply for clock outputs 12, and 13                                                    |  |  |

| 42, 43                                          | CLKout12,<br>CLKout12*    | 0   | Programmable   | Clock output 12: LVDS, LVPECL, or LVCMOS                                                     |  |  |

| 44, 45                                          | CLKout13*,<br>CLKout13    | 0   | Programmable   | Clock output 13: LVDS, LVPECL, or LVCMOS                                                     |  |  |

| 46                                              | Vcc8_DIG                  | I   | PWR            | Power supply for digital                                                                     |  |  |

| 47                                              | DATAuWire/<br>CLKoutDIV_0 | I   | CMOS / 3-State | MICROWIRE DATA Pin / Pin control mode: Clock divider<br>0                                    |  |  |

| 48                                              | CLKuWire/<br>CLKoutDIV_1  | I   | CMOS / 3-State | MICROWIRE CLK Pin / Pin control mode: Clock divider                                          |  |  |

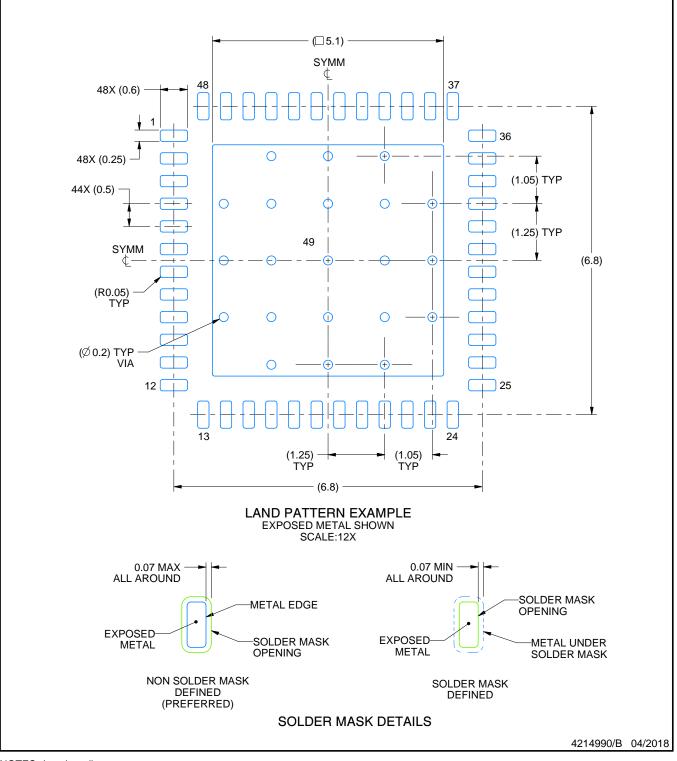

| DAP                                             | DAP                       |     | GND            | DIE ATTACH PAD, connect to GND                                                               |  |  |

(1) See  $\ddagger$  12.1.1 for recommended connections.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

see (1) (2) (3) (5)

|                  |                                        | MIN   | MAX                     | UNIT |

|------------------|----------------------------------------|-------|-------------------------|------|

| V <sub>CC</sub>  | Supply Voltage <sup>(4)</sup>          | - 0.3 | 3.6                     | V    |

| V <sub>IN</sub>  | Input Voltage                          | - 0.3 | (V <sub>CC</sub> + 0.3) | V    |

| TL               | Lead Temperature (solder 4 seconds)    |       | 260                     | °C   |

| I <sub>IN</sub>  | Differential Input Current (CLKinX/X*) |       | ±5                      | mA   |

| MSL              | Moisture Sensitivity Level             |       | 3                       |      |

| T <sub>stg</sub> | Storage Temperature                    | - 65  | 150                     | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) This device is a high performance RF integrated circuit with an ESD rating up to 2.5 kV Human Body Model, up to 250 V Machine Model and up to 1,250 V Charged Device Model and is ESD sensitive. Handling and assembly of this device should only be done at ESD-free workstations.

(3) Stresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These are absolute stress ratings only. Functional operation of the device is only implied at these or any other conditions in excess of those given in the operation sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

(4) Never to exceed 3.6 V.

(5) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

# 7.2 Recommended Operating Conditions

| PARAMETER                           |                                |                         | MIN  | NOM | MAX  | UNIT |

|-------------------------------------|--------------------------------|-------------------------|------|-----|------|------|

| T <sub>A</sub>                      | Ambient Temperature            | V <sub>CC</sub> = 3.3 V | -40  | 25  | 85   | °C   |

| V <sub>CC</sub>                     | V <sub>CC</sub> Supply Voltage |                         | 3.15 | 3.3 | 3.45 | V    |

| T <sub>J</sub> Junction Temperature |                                |                         |      | 125 | °C   |      |

# 7.3 Thermal Information

#### 48-Lead WQFN

|                                                                                                 | VALUE | UNIT |

|-------------------------------------------------------------------------------------------------|-------|------|

| $\theta_{JA}$ Thermal resistance from junction to ambient on 4-layer JEDEC board <sup>(1)</sup> | 26    | °C/W |

| θ <sub>JC</sub> Thermal resistance from junction to case                                        | 3     | °C/W |

(1) Specification assumes 9 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC board. These vias play a key role in improving the thermal performance of the WQFN. It is recommended that the maximum number of vias be used in the board layout.

# 7.4 Electrical Characteristics

$3.15 \text{ V} \leq \text{V}_{CC} \leq 3.45 \text{ V}, -40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C}$ . Typical values represent most likely parametric norms at  $\text{V}_{CC}$  =  $3.3 \text{ V}, \text{T}_{A}$  = 25°C, at the Recommended Operating Conditions at the time of product characterization and are not ensured.

|                                     | PARAMETER                                                        | TEST CONDITIONS                                                                     | MIN           | TYP | MAX             | UNIT |

|-------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------|-----|-----------------|------|

| CURRENT CO                          | ONSUMPTION                                                       |                                                                                     |               |     |                 |      |

| I <sub>CC_PD</sub>                  | Power Down Supply Current                                        |                                                                                     |               | 1   |                 | mA   |

| Icc_clks                            | Supply Current with all clocks enabled <sup>(2)</sup>            | All clock delays disabled,<br>CLKoutX_Y_DIV = 1,<br>CLKoutX_TYPE = 1 (LVDS),        | ),<br>),      |     | 390             | mA   |

| CLKin0/0* AN                        | ID CLKin1/1* INPUT CLOCK SPECIFI                                 | CATIONS                                                                             |               |     | 1               |      |

|                                     |                                                                  | CLKinX_MUX = Bypassed<br>CLKoutX_Y_DIV = 1                                          | 0.001         |     | 3100            | MHz  |

| f <sub>CLKinX</sub>                 | Clock 0 or 1 Input Frequency                                     | CLKinX_MUX = Bypassed<br>CLKoutX_Y_DIV = 2 to 8                                     | 0.001         |     | 1600            | MHz  |

|                                     |                                                                  | CLKin_MUX = Divide<br>CLKinX_DIV = 2 to 8                                           | 0.001         |     | 3100            | MHz  |

| SLEW <sub>CLKin</sub>               | Slew Rate on CLKin <sup>(3)</sup>                                | 20% to 80%                                                                          | 0.15          | 0.5 |                 | V/ns |

| DUTY <sub>CLKin</sub>               | Clock input duty cycle                                           |                                                                                     |               | 50% |                 |      |

| N/                                  | Clock Input,                                                     | AC coupled to CLKinX; CLKinX* AC<br>coupled to Ground<br>(CLKinX_BUF_TYPE = Bipolar | 0.25          |     | 2.4             | Vpp  |

| V <sub>CLKin</sub>                  | Single-ended Input Voltage                                       | AC coupled to CLKinX; CLKinX* AC<br>coupled to Ground<br>(CLKinX_BUF_TYPE = MOS     | 0.25          |     | 2.4             | Vpp  |

| V <sub>ID</sub> CLK <sub>in</sub>   |                                                                  | AC coupled                                                                          | 0.25          |     | 1.55            | V    |

| V <sub>SS</sub> CLK <sub>in</sub>   | Clock Input                                                      | (CLKinX_BUF_TYPE = Bipolar                                                          | 0.5           |     | 3.1             | Vpp  |

| V <sub>ID</sub> CLK <sub>in</sub>   | Differential Input Voltage <sup>(1) (9)</sup>                    | AC coupled                                                                          | 0.25          |     | 1.55            | V    |

| V <sub>SS</sub> CLK <sub>in</sub>   | _                                                                | (CLKinX_BUF_TYPE = MOS                                                              | 0.5           |     | 3.1             | Vpp  |

|                                     | DC offset voltage between CLKinX/                                | Each pin AC coupled                                                                 |               | 0   |                 | mV   |

| V <sub>CLKinX-offset</sub>          | CLKinX*<br>CLKinX* - CLKinX                                      | CLKinX_BUF_TYPE = Bipolar                                                           |               | 0   |                 | mV   |

| V <sub>CLKin-</sub> V <sub>IH</sub> | Maximum input voltage                                            | DC coupled to CLKinX; CLKinX* AC                                                    | 2.0           |     | V <sub>CC</sub> | V    |

| V <sub>CLKin-</sub> V <sub>IL</sub> | Minimum input voltage                                            | coupled to Ground<br>CLKinX_BUF_TYPE = MOS                                          | 0.0           |     | 0.4             | V    |

| V <sub>CLKinX-offset</sub>          | DC offset voltage between CLKinX/<br>CLKinX*<br>CLKinX* - CLKinX | Each pin AC coupled<br>CLKinX_BUF_TYPE = MOS                                        |               | 55  |                 | mV   |

| DIGITAL INPL                        | JTS (CLKuWire, DATAuWire, LEuWire                                | ) for EN_PIN_CTRL = MIDDLE                                                          |               |     |                 |      |

| V <sub>IH</sub>                     | High-Level Input Voltage                                         |                                                                                     | 1.2           |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>                     | Low-Level Input Voltage                                          |                                                                                     |               |     | 0.4             | V    |

| Ін                                  | High-Level Input Current                                         | V <sub>IH</sub> = V <sub>CC</sub>                                                   | -5            |     | 5               | μA   |

| I <sub>IL</sub>                     | Low-Level Input Current                                          | V <sub>IL</sub> = 0                                                                 | -5            |     | 5               | μA   |

| DIGITAL INPU                        | JTS (SYNC0, SYNC1) FOR EN_PIN_                                   | CTRL = MIDDLE                                                                       |               |     | 1               |      |

| V <sub>IH</sub>                     | High-Level Input Voltage                                         |                                                                                     | 1.2           |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>                     | Low-Level Input Voltage                                          |                                                                                     |               |     | 0.4             | V    |

| Ін                                  | High-Level Input Current<br>V <sub>IH</sub> = V <sub>CC</sub>    | V <sub>IH</sub> = V <sub>CC</sub>                                                   | -5            |     | 5               | μA   |

| liL                                 | Low-Level Input Current<br>V <sub>IL</sub> = 0 V                 | V <sub>IL</sub> = 0                                                                 | -40           |     | -5              | μA   |

| DIGITAL INPU                        | JTS (CLKuWire, DATAuWire, LEuWire                                | , SYNC0, SYNC1) FOR EN_PIN_CTRI                                                     | _= LOW OR HIG | GH  |                 |      |

| V <sub>IH</sub>                     | High-Level Input Voltage                                         |                                                                                     | 2.6           |     | V <sub>CC</sub> | V    |

| V <sub>IM</sub>                     | Mid-Level Input Voltage                                          |                                                                                     | 1.3           |     | 1.85            | V    |

# $3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{A} \le 85^{\circ}\text{C}$ . Typical values represent most likely parametric norms at $\text{V}_{CC}$ = $3.3 \text{ V}, \text{T}_{A}$ = $25^{\circ}\text{C}$ , at the Recommended Operating Conditions at the time of product characterization and are not ensured.

|                                    | PARAMETER                                                                                     | TEST CONDITIONS                                                                                                                                                                           | MIN   | ТҮР  | MAX   | UNIT |  |

|------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|--|

| V <sub>IL</sub>                    | Low-Level Input Voltage                                                                       |                                                                                                                                                                                           |       |      | 0.7   | V    |  |

| I <sub>IH</sub>                    | High-Level Input Current                                                                      | V <sub>IH</sub> = V <sub>CC</sub>                                                                                                                                                         |       |      | 100   | μA   |  |

| I <sub>IM</sub>                    | Mid-Level Input Current                                                                       |                                                                                                                                                                                           | -10   |      | 10    | μA   |  |

| I <sub>IL</sub>                    | Low-Level Input Current                                                                       | V <sub>IL</sub> = 0                                                                                                                                                                       | -100  |      |       | μA   |  |

| CLOCK SKEV                         | V AND DELAY                                                                                   |                                                                                                                                                                                           |       |      |       |      |  |

| T <sub>PD</sub>                    | CLKinX to CLKoutY                                                                             | Single-ended CLKinX* input, LVDS output                                                                                                                                                   |       | 2.25 |       | ns   |  |

|                                    | CLKoutX to CLKoutY                                                                            | LVDS-to-LVDS, T = 25°C,<br>$F_{CLK}$ = 800 MHz, $R_L$ = 100 $\Omega$<br>AC coupled, Within same Divider                                                                                   |       | 3    |       |      |  |

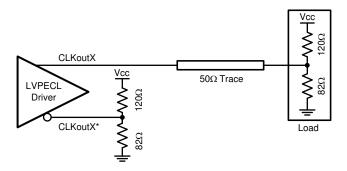

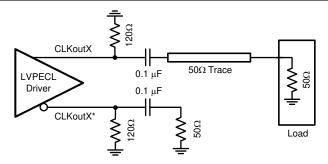

| T <sub>SKEW</sub>                  | (4) (5)                                                                                       | $      LVPECL-to-LVPECL, T = 25^{\circ}C \\ F_{CLK} = 800 \text{ MHz}, R_L = 100 \ \Omega \\ emitter resistors = 240 \ \Omega \text{ to GND} \\ AC \text{ coupled, Within same Divider} $ | 3     |      |       | ps   |  |

|                                    | Skew between any two LVCMOS<br>outputs, same CLKout or different<br>CLKout <sup>(4) (5)</sup> | $R_L$ = 50 $\Omega$ , $C_L$ = 10 pF,<br>T = 25 °C, $F_{CLK}$ = 100 MHz, Within<br>same Divider                                                                                            |       | 50   |       |      |  |

| MixedT <sub>SKEW</sub>             | LVPECL to LVDS skew                                                                           |                                                                                                                                                                                           |       | 32   |       |      |  |

| CLKoutX -                          | LVDS to LVCMOS skew                                                                           | Same device, T = 25°C,<br>250 MHz, Within same Divider                                                                                                                                    | 830   |      | ps    |      |  |

| CLKoutY                            | LVCMOS to LVPECL skew                                                                         |                                                                                                                                                                                           | 800   |      |       |      |  |

| F <sub>ADLY</sub>                  | Maximum Analog<br>Delay Frequency                                                             |                                                                                                                                                                                           | 1536  |      |       | MHz  |  |

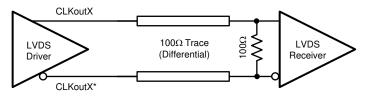

| LVDS CLOCK                         | COUTPUTS (CLKoutX)                                                                            | 1                                                                                                                                                                                         |       |      | I     |      |  |

| f <sub>CLKout</sub>                | Maximum Clock Frequency<br>(5) (6)                                                            | R <sub>L</sub> = 100 Ω                                                                                                                                                                    | 1600  |      |       | MHz  |  |

| V <sub>OD</sub>                    | Differential Output Voltage<br>(1) (9)                                                        |                                                                                                                                                                                           | 225   | 400  | 575   | mV   |  |

| $\Delta V_{OD}$                    | Change in Magnitude of V <sub>OD</sub> for complementary output states                        | T = 25°C, DC measurement<br>AC coupled to receiver input                                                                                                                                  | -50   |      | 50    | mV   |  |

| V <sub>OS</sub>                    | Output Offset Voltage                                                                         | R = 100 $\Omega$ differential termination                                                                                                                                                 | 1.125 | 1.25 | 1.375 | V    |  |

| $\Delta V_{OS}$                    | Change in $V_{OS}$ for complementary output states                                            |                                                                                                                                                                                           |       |      | 35    | mV   |  |

| T <sub>R</sub>                     | Output Rise Time                                                                              | 20% to 80%, $R_L$ = 100 $\Omega$                                                                                                                                                          |       | 200  |       | ps   |  |

| T <sub>F</sub>                     | Output Fall Time                                                                              | 80% to 20%, $R_L$ = 100 $\Omega$                                                                                                                                                          |       | 300  |       | ps   |  |

| I <sub>SA</sub><br>I <sub>SB</sub> | Output short circuit current - single ended                                                   | Single-ended output shorted to GND,<br>T = 25°C                                                                                                                                           | -24   |      | 24    | mA   |  |

| SAB                                | Output short circuit current -<br>differential                                                | Complimentary outputs tied together                                                                                                                                                       | -12   |      | 12    | mA   |  |

$3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{A} \le 85^{\circ}\text{C}$ . Typical values represent most likely parametric norms at  $\text{V}_{CC}$  =  $3.3 \text{ V}, \text{T}_{A}$  =  $25^{\circ}\text{C}$ , at the Recommended Operating Conditions at the time of product characterization and are not ensured.

|                     | PARAMETER                          | TEST CONDITIONS                                                                        | MIN                   | TYP                    | MAX  | UNIT |

|---------------------|------------------------------------|----------------------------------------------------------------------------------------|-----------------------|------------------------|------|------|

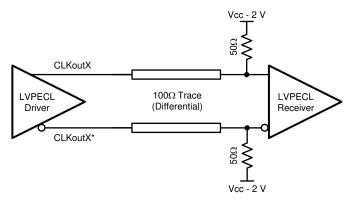

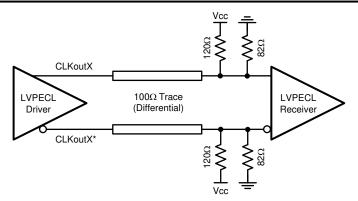

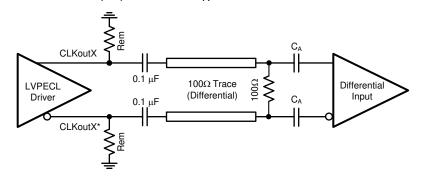

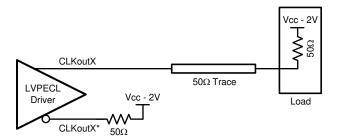

| LVPECL CI           | LOCK OUTPUTS (CLKoutX)             |                                                                                        |                       |                        |      |      |

| T <sub>R</sub>      | Output Rise Time                   | 20% to 80%, R <sub>L</sub> = 100 $\Omega$ ,<br>emitter resistors = 240 $\Omega$ to GND |                       | 200                    |      | ps   |

| T <sub>F</sub>      | Output Fall Time                   | 80% to 20%, R <sub>L</sub> = 100 $\Omega$ ,<br>emitter resistors = 240 $\Omega$ to GND |                       | 200                    |      | ps   |

| LOW COM             | MON-MODE VOLTAGE PECL (LCPE        | CL) <sup>(7)</sup> , <sup>(8)</sup>                                                    |                       |                        |      |      |

| f <sub>CLKout</sub> | Maximum Clock Frequency<br>(5) (6) | $R_L = 100 \Omega$ ,<br>emitter resistors = 240 $\Omega$ to GND                        | 3100                  |                        |      | MHz  |

| V <sub>он</sub>     | Output High Voltage                | T = 25°C, DC Measurement                                                               |                       | 1.6                    |      | V    |

| V <sub>OL</sub>     | Output Low Voltage                 | Termination = 50 $\Omega$ to                                                           |                       | 0.75                   |      | V    |

| V <sub>OD</sub>     | Output Voltage                     | V <sub>CC</sub> - 0.6 V                                                                | 535                   | 840                    | 1145 | mV   |

| 1600-mV L           | VPECL (LVPECL) CLOCK OUTPUTS       | (CLKoutX)                                                                              |                       |                        | I    |      |

| f <sub>CLKout</sub> | Maximum Clock Frequency<br>(5) (6) | $R_L$ = 100 Ω,<br>emitter resistors = 240 Ω to GND                                     | 3100                  |                        |      | MHz  |

| V <sub>OH</sub>     | Output High Voltage                | T = 25°C, DC Measurement                                                               |                       | V <sub>CC</sub> - 0.94 |      | V    |

| V <sub>OL</sub>     | Output Low Voltage                 | Termination = 50 $\Omega$ to                                                           |                       | V <sub>CC</sub> - 1.9  |      | V    |

| V <sub>OD</sub>     | Output Voltage                     | V <sub>CC</sub> - 2.0 V                                                                | 585                   | 925                    | 1240 | mV   |

| 2000-mV L           | VPECL (2VPECL) CLOCK OUTPUTS       | (CLKoutX)                                                                              |                       |                        | I    |      |

| f <sub>CLKout</sub> | Maximum Clock Frequency<br>(5) (6) | $R_L$ = 100 Ω,<br>emitter resistors = 240 Ω to GND                                     | 3100                  |                        |      | MHz  |

| V <sub>он</sub>     | Output High Voltage                | T = 25°C, DC Measurement                                                               |                       | V <sub>CC</sub> - 0.97 |      | V    |

| V <sub>OL</sub>     | Output Low Voltage                 | Termination = 50 $\Omega$ to                                                           |                       | V <sub>CC</sub> - 1.95 |      | V    |

| V <sub>OD</sub>     | Output Voltage                     | V <sub>CC</sub> - 2.3 V                                                                | 705                   | 1150                   | 1585 | mV   |

| LVCMOS C            | CLOCK OUTPUTS (CLKoutX)            |                                                                                        |                       |                        |      |      |

| CLKout              | Maximum Clock Frequency<br>(5) (6) | 5-pF Load                                                                              | 250                   |                        |      | MHz  |

| V <sub>OH</sub>     | Output High Voltage                | 1-mA Load                                                                              | V <sub>CC</sub> - 0.1 |                        |      | V    |

| V <sub>OL</sub>     | Output Low Voltage                 | 1-mA Load                                                                              |                       |                        | 0.1  | V    |

| l <sub>он</sub>     | Output High Current (Source)       | V <sub>CC</sub> = 3.3 V, V <sub>O</sub> = 1.65 V                                       |                       | 28                     |      | mA   |

| OL                  | Output Low Current (Sink)          | V <sub>CC</sub> = 3.3 V, V <sub>O</sub> = 1.65 V                                       |                       | 28                     |      | mA   |

| DUTY <sub>CLK</sub> | Output Duty Cycle (5)              | $V_{CC}/2$ to $V_{CC}/2,F_{CLK}$ = 100 MHz, T = 25 $^{\circ}\text{C}$                  | 45%                   | 50%                    | 55%  |      |

| T <sub>R</sub>      | Output Rise Time                   | 20% to 80%, R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = 5 pF                       |                       | 400                    |      | ps   |

| T <sub>F</sub>      | Output Fall Time                   | 80% to 20%, R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = 5 pF                       |                       | 400                    |      | ps   |

|                     |                                    |                                                                                        |                       |                        |      |      |

3.15 V  $\leq$  V<sub>CC</sub>  $\leq$  3.45 V, - 40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C. Typical values represent most likely parametric norms at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C, at the Recommended Operating Conditions at the time of product characterization and are not ensured.

|                  | PARAMETER                  | TEST CONDITIONS            | MIN | ТҮР | MAX | UNIT |  |

|------------------|----------------------------|----------------------------|-----|-----|-----|------|--|

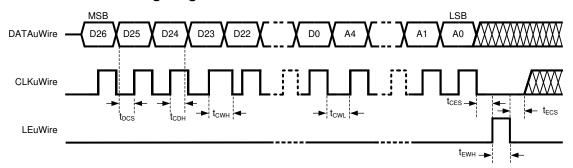

| MICROWI          | MICROWIRE INTERFACE TIMING |                            |     |     |     |      |  |

| T <sub>ECS</sub> | LE to Clock Set Up Time    | See MICROWIRE Input Timing | 25  |     |     | ns   |  |

| T <sub>DCS</sub> | Data to Clock Set Up Time  | See MICROWIRE Input Timing | 25  |     |     | ns   |  |

| T <sub>CDH</sub> | Clock to Data Hold Time    | See MICROWIRE Input Timing | 8   |     |     | ns   |  |

| Т <sub>СWH</sub> | Clock Pulse Width High     | See MICROWIRE Input Timing | 25  |     |     | ns   |  |

| T <sub>CWL</sub> | Clock Pulse Width Low      | See MICROWIRE Input Timing | 25  |     |     | ns   |  |

| T <sub>CES</sub> | Clock to LE Set Up Time    | See MICROWIRE Input Timing | 25  |     |     | ns   |  |

| T <sub>EWH</sub> | LE Pulse Width             | See MICROWIRE Input Timing | 25  |     |     | ns   |  |

(1) See applications section  $\ddagger$  8.1 for definition of  $V_{\text{ID}}$  and  $V_{\text{OD}}$  voltages.

(2) For lcc for specific part configuration, see applications section  $\ddagger$  11.1 for calculating lcc.

(3) The minimum recommended slew rate for all input clocks is 0.5 V/ns. This is especially true for single-ended clocks. Phase noise performance will begin to degrade as the clock input slew rate is reduced. However, the device will function at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) will be less susceptible to degradation in phase noise performance at lower slew rates due to their common mode noise rejection. However, it is also recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device outputs.

- (4) Equal loading and identical clock output configuration on each clock output is required for specification to be valid. Specification not valid for delay mode.

- (5) Ensured by characterization.

- (6) Refer to typical performance charts for output operation performance at higher frequencies than the minimum maximum output frequency.

(7) For LCPECL, the common mode voltage is regulated (VOH=1.6V, VOL=VOH-Vsw, Vcm=(VOH+VOL)/2) and is more stable against with PVT (process, supply, temperature) variations than conventional LVPECL implementations.

- (8) With proper selection of external emitter resistors, LCPECL can also be used for DC-coupling with devices with low common voltage such as 0.5V or 0.8V etc.

- (9) Refer to application note AN-912 Common Data Transmission Parameters and their Definitions (SNLA036) for more information.

#### 7.5 Serial MICROWIRE Timing Diagram

Register programming information on the DATAuWire pin is clocked into a shift register on each rising edge of the CLKuWire signal. On the rising edge of the LEuWire signal, the register is sent from the shift register to the register addressed. A slew rate of at least 30 V/µs is recommended for these signals. After programming is complete the CLKuWire, DATAuWire, and LEuWire signals should be returned to a low state.

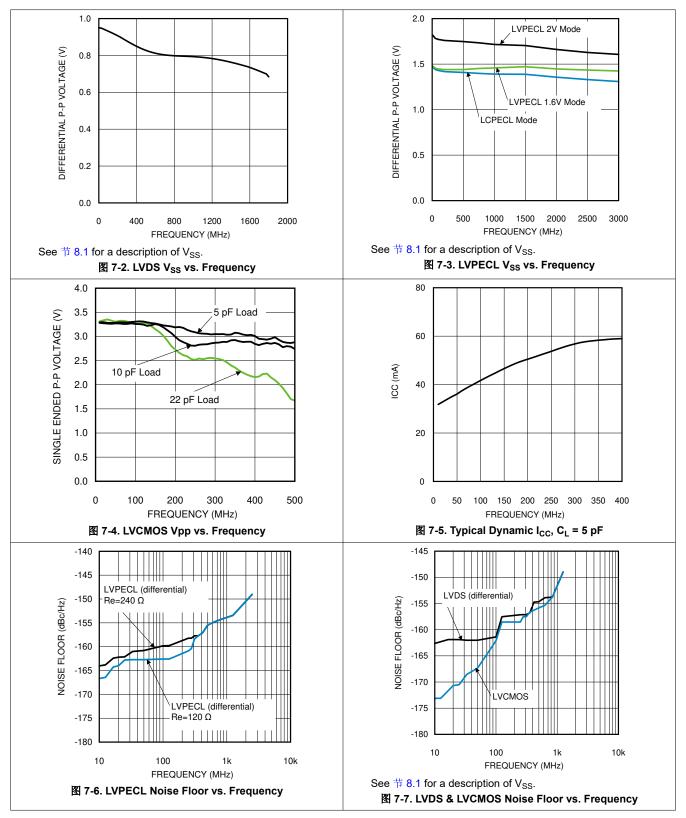

# 7.6 Typical Characteristics

Unless otherwise specified:  $V_{dd}$ =3.3V,  $T_A$ =25 °C

# 8 Parameter Measurement Information

#### 8.1 Differential Voltage Measurement Terminology

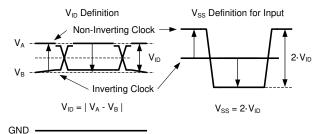

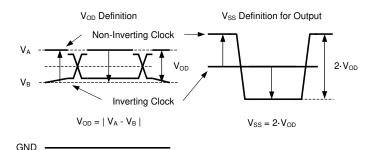

The differential voltage of a differential signal can be described by two different definitions causing confusion when reading data sheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to understand and discern between the two different definitions when used.

The first definition used to describe a differential signal is the absolute value of the voltage potential between the inverting and non-inverting signal. The symbol for this first measurement is typically  $V_{ID}$  or  $V_{OD}$  depending on if an input or output voltage is being described.

The second definition used to describe a differential signal is to measure the potential of the non-inverting signal with respect to the inverting signal. The symbol for this second measurement is  $V_{SS}$  and is a calculated parameter. Nowhere in the IC does this signal exist with respect to ground, it only exists in reference to its differential pair.  $V_{SS}$  can be measured directly by oscilloscopes with floating references, otherwise this value can be calculated as twice the value of  $V_{OD}$  as described in the first section

$\mathbb{E}$  8-1 illustrates the two different definitions side-by-side for inputs and  $\mathbb{E}$  8-2 illustrates the two different definitions side-by-side for outputs. The V<sub>ID</sub> and V<sub>OD</sub> definitions show V<sub>A</sub> and V<sub>B</sub> DC levels that the noninverting and inverting signals toggle between with respect to ground. V<sub>SS</sub> input and output definitions show that if the inverting signal is considered the voltage potential reference, the noninverting signal voltage potential is now increasing and decreasing above and below the noninverting reference. Thus the peak-to-peak voltage of the differential signal can be measured.

$V_{ID}$  and  $V_{OD}$  are often defined in volts (V) and  $V_{SS}$  is often defined as volts peak-to-peak ( $V_{PP}$ ).

图 8-2. Two Different Definitions for Differential Output Signals

# 9 Detailed Description

# 9.1 Overview

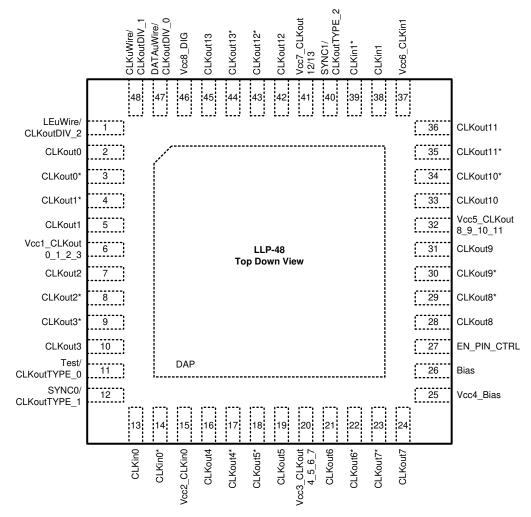

The LMK01801 is a dual clock buffer which allows separate clock domains on the same IC with options to divide and delay signals.

The LMK01801 consists of two separate buffer banks, each with its own input divider, output dividers and programmable control of clock output channels.

- Bank A has two clock output groups, see the  $\ddagger 5.1$  for more details.

- Bank B has two clock output groups, one of which has analog and digital delay. See the

<sup>†</sup> 5.1 for more details.

Each bank has it own common input divider and is then divided into output groups which share an output divider.

The LMK01801 comes in a 48-pin WQFN package.

### 9.2 Functional Block Diagram

# 9.3 Feature Description

# 9.3.1 High-Speed Clock Inputs (CLKin0/CLKin0\* and CLKin1/CLKin1\*)

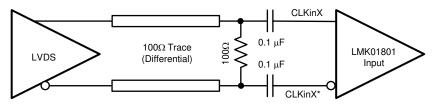

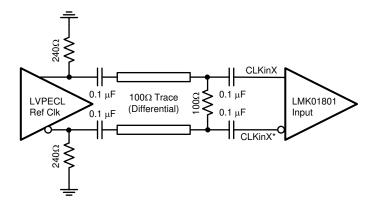

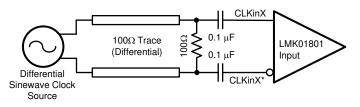

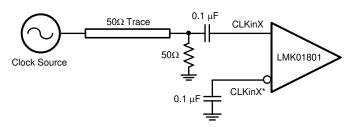

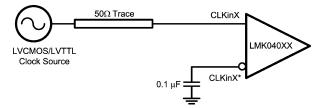

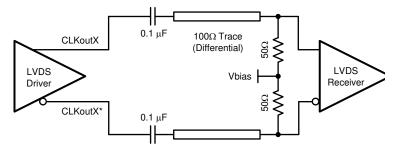

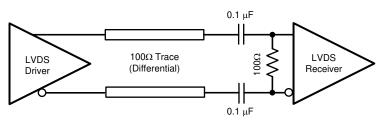

The LMK01801 has two clock inputs, CLKin0 and CLKin1 which can be driven differentially or single-ended. See  $\ddagger$  10.1.1.1 for more information. Each input has a 2 to 8 divider that may be enabled or bypassed.

#### 9.3.2 Clock Distribution

The LMK01801 features a total of 14 differential outputs. CLKout0 through CLKout7 are driven from CLKin0 and CLKout8 through CLKout13 are driven from CLKin1.

#### 9.3.3 Small Divider (1 to 8)

There are three small dividers which drive CLKout0 to CLKout3, CLKout4 to CLKout7, and CLKout8 to CLKout11. These dividers support a divide range of 1 to 8 (even and odd).

#### 9.3.4 Large Divider (1 to 1045)

The divider for CLKout12 and CLKout13 supports a divide range of 1 to 1045 (even and odd). When divides of 26 or greater are used, the divider/delay block uses extended mode.

#### 9.3.5 CLKout Analog Delay

Clock outputs 12 and 13 include a fine (analog) delay for phase adjustment of the clock outputs.

The fine (analog) delay allows a nominal 25 ps step size and range from 0 to 475 ps of total delay. Enabling the analog delay adds a nominal 500 ps of delay in addition to the programmed value.

When adjusting analog delay, glitches may occur on the clock outputs being adjusted.

#### 9.3.6 CLKout0 to CLKout11 Digital Delay

CLKout0 to CLKout11 include a fixed digital delay for phase adjustment of the clock outputs.

The fixed delay allows a group of outputs to be delayed by 5 clock distribution path cycles. The 5-cycle offset takes effect on the clock outputs after a SYNC event. The delay is enabled through the CLKoutX\_Y\_OFFSET\_PD register bit.

See  $\ddagger$  9.4.5 for more information.

#### 9.3.7 CLKout12 and CLKout13 Digital Delay

CLKout12 and CLKout13 includes a coarse (digital) delay for phase adjustment of the clock outputs.

The coarse (digital) delay allows a group of outputs to be delayed by 4.5 to 12 clock distribution path cycles in normal mode, or from 12.5 to 522 clock cycles in extended mode. The delay step can be as small as half the period of the clock distribution path by using the CLKout12\_13\_HS bit. For example, a 2-GHz clock frequency without using CLKin1 input clock divider results in 250-ps coarse tuning steps.

The coarse (digital) delay value takes effect on the clock outputs after a SYNC event.

There are 2 different ways to use the digital (coarse) delay.

- 1. Fixed Digital Delay

- 2. Relative Dynamic Digital Delay

See *Device Functional Modes* for more information.

#### 9.3.8 Programmable Outputs

The outputs of the LMK01801 are programmable in a combination of output types based on  $\frac{1}{8}$  5-1. Programming the outputs is by MICROWIRE or by pin control mode based on the state of EN\_PIN\_CTRL pin.

Any LVPECL output type can be programmed to LCPECL, 1600, or 2000 mVpp amplitude levels. The 2000 mVpp LVPECL output type is a Texas Instruments proprietary configuration that produces a 2000 mVpp differential swing for compatibility with many data converters and is also known as 2VPECL.

#### 9.3.9 Clock Output Synchronization

Using the SYNC input causes all active clock outputs to share a rising edge. See <sup>†</sup> 9.4.6 for more information.

The SYNC event also causes the digital delay value to take effect.

#### 9.3.10 Default Clock Outputs

The power on reset sets the device to operate with all outputs active in bypass mode (no divide) with LVDS output type. In this way the device can be used without programming for fan-out purposes.

#### 9.4 Device Functional Modes

#### 9.4.1 Programmable Mode

When the EN\_PIN\_CTRL pin is floating (default by internal pull-up/pull-down) then programming is via MICROWIRE.

See 表 5-1 for a description of available programming options for the LMK01801 in programmable mode.

#### 9.4.2 Pin Control Mode

The LMK01801 provides for an alternate function of the MICROWIRE (uWire) pins. This pin control mode is set by the logic of the EN\_PIN\_CTRL pin to provide limited control of the outputs and dividers.

When the EN\_PIN\_CTRL pin is set high or low (not open) then the output states can be programmed by pins, eliminating the need for an external FPGA or CPU.

If EN\_PIN\_CTRL is LOW then  $\frac{1}{5}$  5-2 in  $\frac{1}{5}$  5.1 defines how the outputs and dividers are configured.

If EN\_PIN\_CTRL is HIGH then  $\frac{1}{5}$  5-3 in  $\frac{1}{5}$  5.1 defines how the outputs and dividers are configured.

#### 9.4.3 Inputs / Outputs

#### 9.4.3.1 CLKin0 and CLKin1

There are two clock inputs CLKin0 and CLKin1. CLKin0 provides the input for output Bank A and CLKin1 provides the input for the output Bank B. Each input has it's own divider (2 to 8) that may be bypassed.

#### 9.4.4 Input and Output Dividers

This section discusses the recommended usage of input and output dividers.

Clock inputs 0 and 1 each have an associated divider (2 to 8) that may be enabled or bypassed.

Clock groups 1, 2 and 3 have small output dividers (1 to 8). Clock group 4 (CLKout12 and CLKout13) has a large output divider (1 to 1045).

While the input and output clock dividers may be used in any combination the recommended operating frequency ranges are shown in the table below to minimize the phase noise floor:

| Input Divider   | Output Divider  | Max Frequency |

|-----------------|-----------------|---------------|

| Bypassed        | Divide = 1      | 3.1 GHz       |

| Bypassed        | Divide > 1      | 1.6 GHz       |

| Divide = 2 to 8 | Divide = 1 to 8 | 3.1 GHz       |

#### 表 9-1. Input and Output Divider Input Frequency Ranges

#### 9.4.5 Fixed Digital Delay

This section discusses Fixed Digital Delay and associated registers.

Clock outputs 0 to 11 may be delayed after synchronization by a fixed offset of 5 clock distribution path cycles. The CLKoutX\_Y\_OFFSET\_PD register bit inserts the delay for each respective clock group. By default, the fixed offset is enabled for CLKout8\_11 and disabled for CLKout0\_3 and CLKout4\_7. CLKoutX\_Y\_OFFSET\_PD aligns the specified clock group with CLKout12\_13 after a SYNC event upon meeting the following conditions:

- 1. The input clock frequency of the specified clock group(s) is the same as CLKout12\_13 (CLKin1).

- 2. CLKout12\_13 does not have any digital or analog delays enabled.

See SYNC Timing for further synchronization details on CLKoutX\_Y\_OFFSET\_PD.

Clock outputs 12 and 13 may be delayed relative to CLKout8 to CLKout11 by up to 517.5 clock distribution path periods if divide is 1 and 518.5 clock distribution path periods if divide is greater than 1. By programming a digital delay value from 4.5 to 522 clock distribution path periods, a relative clock output delay from 0 to 517.5 periods is achieved. The CLKout12\_13\_DDLY register sets the digital delay as shown in the table  $\frac{1}{2}$  9-2.

#### 表 9-2. Possible Digital Delay Values

| CLKout12_13_DDLY | CLKout12_13_HS | DIGITAL DELAY |

|------------------|----------------|---------------|

| 5                | 1              | 4.5           |

| 5                | 0              | 5             |

| 6                | 1              | 5.5           |

| 6                | 0              | 6             |

| 7                | 1              | 6.5           |

| 7                | 0              | 7             |

|                  |                |               |

| 520              | 0              | 520           |

| 521              | 1              | 520.5         |

| 521              | 0              | 521           |

| 522              | 1              | 521.5         |

| 522              | 0              | 522           |

The CLKout12\_13\_DDLY value only takes effect during a SYNC event and if the NO\_SYNC\_CLKout12\_13 bit is cleared for this clock group. See  $\ddagger$  9.4.6 for more information.

The resolution of digital delay is related to the frequency at the input to the Clock Group 4 (CG4) clock distribution path.

Digital Delay Resolution = 1 / (2 \* Clock Frequency)

The digital delay between clock outputs can be dynamically adjusted with minimum or no disruption of the output clocks. See 节 9.4.6.1 for more information.

#### 9.4.5.1 Fixed Digital Delay - Example

Given a CLKin1 clock frequency of 983.04 MHz as input to CG4, by using digital delay the outputs can be adjusted in 1 / (2 \* 983.04 MHz) = ~509 ps steps (Assumes CLKin1\_MUX = bypass).

To achieve a quadrature (90 degree) phase shift on 122.88 MHz outputs between CLKout12 and CLKout11 from a clock frequency of 983.04 MHz program:

- Clock output divider to 8. CLKout8\_11 = 8 and CLKout12\_13\_DIV = 8

- Set clock digital delay value. CLKout12\_13\_DDLY = 5, CLKout12\_13\_HS = 0.

The frequency of 122.88 MHz has a period of ~8.14 ns. To delay 90 degrees of a 122.88 MHz clock period requires a ~2.03 ns delay. Given a digital delay step of ~509 ps, this requires a digital delay value of 4 steps (2.03 ns / 509 ps = 4). Since the 4 steps are half period steps, CLKout12\_13\_DDLY is programmed 2 full periods beyond 5 for a total of 7.

$\frac{1}{8}$  9-3 shows some of the possible phase delays in degrees achievable in the above example.

| CLKout12 and CLKout13 to CLKout8 to CLKout11 |                |                        |                       |  |  |  |

|----------------------------------------------|----------------|------------------------|-----------------------|--|--|--|

| CLKout12_13_DDLY                             | CLKout12_13_HS | Relative Digital Delay | Degrees of 122.88 MHz |  |  |  |

| 5                                            | 1              | -0.5                   | -23°                  |  |  |  |

| 5                                            | 0              | 0.0                    | 0°                    |  |  |  |

| 6                                            | 1              | 0.5                    | 23°                   |  |  |  |

| 6                                            | 0              | 1.0                    | 45°                   |  |  |  |

| 7                                            | 1              | 1.5                    | 68°                   |  |  |  |

| 7                                            | 0              | 2.0                    | 90°                   |  |  |  |

| 8                                            | 1              | 2.5                    | 113°                  |  |  |  |

| 8                                            | 0              | 3.0                    | 135°                  |  |  |  |

#### 表 9-3. Relative Phase Shift From LKout12 and CLKout13 to CLKout8 to CLKout11

| (continued)         CLKout12_13_DDLY       CLKout12_13_HS       Relative Digital Delay       Degrees of 122.88 MHz |   |     |      |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|---|-----|------|--|--|--|--|--|--|--|--|

| 9                                                                                                                  | 1 | 3.5 | 158° |  |  |  |  |  |  |  |  |

| 9                                                                                                                  | 0 | 4.0 | 180° |  |  |  |  |  |  |  |  |

| 10                                                                                                                 | 1 | 4.5 | 203° |  |  |  |  |  |  |  |  |

| 10                                                                                                                 | 0 | 5.0 | 225° |  |  |  |  |  |  |  |  |

| 11                                                                                                                 | 1 | 5.5 | 248° |  |  |  |  |  |  |  |  |

| 11                                                                                                                 | 0 | 6.0 | 270° |  |  |  |  |  |  |  |  |

| 12                                                                                                                 | 1 | 6.5 | 293° |  |  |  |  |  |  |  |  |

| 12                                                                                                                 | 0 | 7.0 | 315° |  |  |  |  |  |  |  |  |

| 13                                                                                                                 | 1 | 7.5 | 338° |  |  |  |  |  |  |  |  |

| 13                                                                                                                 | 0 | 8.0 | 360° |  |  |  |  |  |  |  |  |

|                                                                                                                    |   |     |      |  |  |  |  |  |  |  |  |

#### 表 9-3. Relative Phase Shift From CLKout12 and CLKout13 to CLKout8 to CLKout11 (continued)

8 9-2 illustrates clock outputs programmed with different digital delay values during a SYNC event.

Refer to  $\ddagger$  9.4.6.1 for more information on dynamically adjusting digital delay.

#### 9.4.6 Clock Output Synchronization (SYNC)

The purpose of the SYNC function is to synchronize the clock outputs with a fixed and known phase relationship between each clock output selected for SYNC. SYNC can also be used to hold the outputs in a low or 0 state. The NO\_SYNC\_CLKoutX\_Y bits can be set to disable synchronization for a clock group.

The digital delay value set by CLKout12\_13\_DDLY takes effect only upon a SYNC event. The digital delay due to CLKout12\_13\_HS takes effect immediately upon programming. See  $\ddagger$  9.4.6.1 for more information on dynamically changing digital delay.

It is necessary to ensure that the CLKin1 signal is stable before a sync event occurs when CLKout12\_13\_DIV is greater than 1.

#### Effect of SYNC

When SYNC is asserted, the outputs to be synchronized are held in a logic low state. When SYNC is unasserted, the clock outputs to be synchronized are activated and will transition to a high state simultaneously with one another except where digital delay values have been programmed.

Refer to  $\ddagger$  9.4.6.1 for SYNC functionality when SYNC\_QUAL = 1.

#### 表 9-4. Steady-State Clock Output Condition Given Specified Inputs

| SYNC_POL<br>_INV | SYNC PIN | CLOCK STEADY STATE |

|------------------|----------|--------------------|

| 0                | 0        | Active             |

| 0                | 1        | Low                |

| 1                | 0        | Low                |

| 1                | 1        | Active             |

### Methods of Generating SYNC

There are three methods to generate a SYNC event:

- Manual:

- Asserting the SYNC pin according to the polarity set by SYNC\_POL\_INV.

- Toggling the SYNC\_POL\_INV bit though MICROWIRE will cause a SYNC to be asserted.

- Automatic:

- Programming Register R4 when SYNC\_EN\_AUTO = 1 will generate a SYNC event for Bank B.

- Programming Register R5 when SYNC\_EN\_AUTO = 1 will generate a SYNC event for both Bank A and Bank B.

Due to the high speed of the clock distribution path (as fast as ~322 ps period) and the slow slew rate of the SYNC, the exact clock cycle at which the SYNC is asserted or unasserted by the SYNC is undefined. The timing diagrams show a sharp transition of the SYNC to clarify functionality.

#### Avoiding clock output interruption due to SYNC

#### Note

When Automatic SYNC is enabled, after a write to registers 4 of 5, there is an 170-ns delay after LE falling edge before the SYNC event is registered.

If a clock output has the NO\_SYNC\_CLKoutX\_Y bits set they will be unaffected by the SYNC event. It is possible to perform a SYNC operation with the NO\_SYNC\_CLKoutX\_Y bit cleared, set the NO\_SYNC\_CLKoutX\_Y bits so that the selected clocks will not be affected by a future SYNC. Future SYNC events will not effect these clocks but will still cause the newly synchronized clocks to be resynchronized using the currently programmed digital delay values. When this happens, the phase relationship between the first group of synchronized clocks and the second group of synchronized clocks will be undefined. Except for CLKout12 and CLKout13 when synced using qualification mode. See † 9.4.6.1.

#### SYNC Timing

When discussing the timing of the SYNC function, one cycle refers to one period of the clock distribution path.

Case 2: CLKout0\_3\_OFFSET\_PD, CLKout4\_7\_OFFSET\_PD, & CLKout8\_11\_OFFSET\_PD = 1

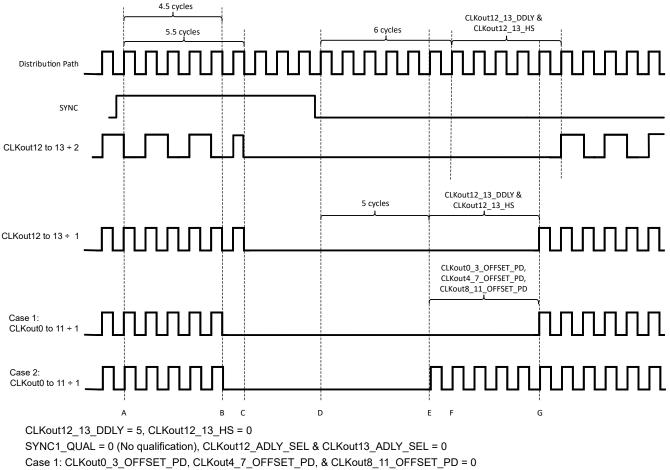

# 图 9-1. Clock Output Synchronization Using the SYNC1 Pin (SYNC1 is Active High, SYNC1\_POL\_INV = 0)

Refer to [3] 9-1 during this discussion on the timing of SYNC. SYNC must be asserted for greater than one clock cycle of the clock distribution path to register the SYNC event. After SYNC is asserted the SYNC event will begin on the following rising edge of the distribution path clock, at time A. After this event has been registered, the outputs will not reflect the low state for 4.5 cycles for CLKout0 to CLKout11 at time B or 5.5 cycles for CLKout12 and CLKout13 if divide = 1 or 6.5 cycles for CLKout12 and CLKout13 if divide > 1, at time C. Due to the asynchronous nature of SYNC with respect to the output clocks, it is possible that a runt pulse could be created when the clock output goes low from the SYNC event. This is shown by CLKout12 and CLKout13. See  $\ddagger$  9.4.6.1.2 for more information on synchronizing relative to an output clock to eliminate or minimize this runt pulse for CLKout13.

After SYNC becomes unasserted the event will be registered on the following rising edge of the distribution path clock, time D. CLKout0 to CLKout11 will rise at time E, if Case 2, coincident with a rising distribution clock edge that occurs after 5 cycles for CLKout0 to CLKout11 and for CLKout12 to CLKout13, if CLKout12\_13\_DIV = 1. If CLKoutX\_Y\_OFFSET\_PD = 0, CLKout0 to CLKout11 will rise at time G after an additional 5 cycles. If CLKout12\_13\_DIV > 1 then the rising edge of CLKout12 and CLKout13 will occur after 6 cycles of the distribution path at time F plus as many more cycles as programmed by the digital delay for that clock output path. CLKout12 and CLKout13 will rise at time G, which is the Digital Delay value plus 5 cycles when CLKout12\_13\_DIV > 1.

See 8 9-2 for further SYNC timing detail using different digital delays.

SYNC1\_QUAL = 0 (No qualification), CLKout12\_ADLY\_SEL & CLKout13\_ADLY\_SEL = 0

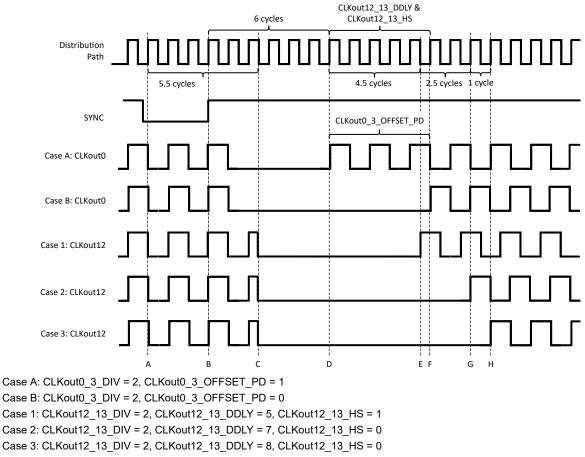

# 图 9-2. Clock Output Synchronization Using the SYNC Pin (SYNC is Active Low, SYNC\_POL\_INV = 1)

图 9-2 illustrates the timing with various digital delays programmed.

- Time A) SYNC assertion event is registered.

- Time B) SYNC unassertion registered.

- Time C) CLKout12 outputs toggle and remain low. A runt pulse can occur at this time as shown.

- Time D) After 5 cycles, in Case A, CLKout0 rises.

- Time E) After 6 + 4.5 = 10.5 cycles, in Case 1, CLKout12 rises.

- Time F) After 5 + 5 = 10 cycles, in Case B, CLKout0 rises.

- Time G) After 6 + 7 = 13 cycles, in Case 2, CLKout12 rises.

- Time H) After 6 + 8 = 14 cycles, in Case 3, CLKout12 rises.

- Note: CLKout 12 and CLKout 13 are driven by the same divider and delay circuit, therefore, their timing is always the same except when analog delay is used.

#### 9.4.6.1 Dynamically Programming Digital Delay

To use dynamic digital delay **synchronization qualification** set SYNC1\_QUAL = 3. This causes the SYNC pulse to be qualified by a clock output so that the SYNC event occurs after a specified time from a clock output transition. This allows the relative adjustment of clock output phase in real-time with no or minimum interruption of clock outputs. Hence the term dynamic digital delay.

Note that changing the phase of a clock output requires momentarily altering in the rate of change of the clock output phase and therefore by definition results in a frequency distortion of the signal.

Without qualifying the SYNC with an output clock, the newly synchronized clocks would have a random and unknown digital delay (or phase) with respect to clock outputs not currently being synchronized. Only CLKout12 can be used as a qualifying clock.

#### **Relative Dynamic Digital Delay**

When the qualifying clock digital delay is being adjusted, because the qualifying clock and the adjusted clock are the same, then a **relative dynamic digital delay** adjust is performed. Clocks with NO\_SYNC\_CLKoutX\_Y = 1 are defined as clocks not being adjusted. These clocks operate without interruption.

#### SYNC and Minimum Step Size

The minimum step size adjustment for digital delay is half a clock distribution path cycle. This is achieved by using the CLKout12\_13\_HS bit. The CLKout12\_13\_HS bit change effect is immediate without the need for SYNC. To shift digital delay using CLKout12\_13\_DDLY, a SYNC signal must be generated for the change to take effect.

#### **Programming Overview**

To dynamically adjust the digital delay with respect to an existing clock output the device should be programmed as follows:

- Set SYNC1\_QUAL = 3 for clock output qualification.

- Set NO\_SYNC\_CLKout12\_13 = 0 to enable synchronization on CLKout12 and CLKout13.

- Set CLKout12\_ADLY\_SEL = 0.

- Set NO\_SYNC\_CLKoutX\_Y = 1 for the output clocks, except CLKout12 and CLKout13, that will continue to operate during the SYNC event. There is no interruption of output on these clocks.

- The SYNC\_EN\_AUTO bit may be set to cause a SYNC event to begin when register R4 is programmed. The auto SYNC feature is a convenience since it does not require the application to manually assert SYNC by toggling the SYNC\_POL\_INV bit or the SYNC pin when changing digital delay.

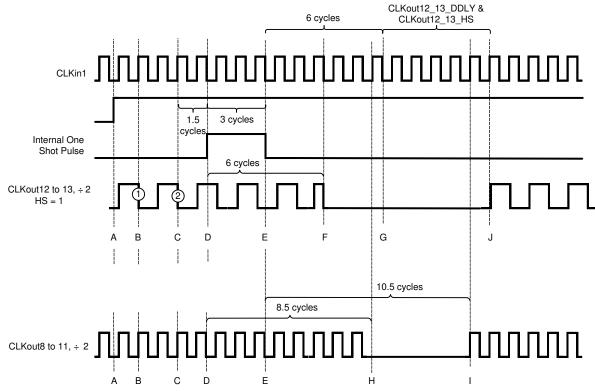

#### Internal Dynamic Digital Delay Timing

Once SYNC is qualified by an output clock, 1.5 cycles later an internal one shot pulse will occur. The width of the one shot pulse is 3 cycles. This internal one shot pulse will cause the outputs to turn off and then back on with a fixed delay with respect to the falling edge of the qualification clock. This allows for dynamic adjustments of digital delay with respect to an output clock.

The qualified SYNC timing is shown in 89-3 for relative dynamic digital delay.

#### **Dynamic Digital Delay Conditions**

To perform a dynamic digital delay adjustment, the analog delay must be bypassed by setting CLKout12\_ADLY\_SEL to 0. If the analog delay is not bypassed the output synchronization may be inaccurate due to unknown analog delay settings.

When adjusting digital delay dynamically, the falling edge of the qualifying clock must coincide with the falling edge of the clock distribution path. For this requirement to be met, program the CLKout12\_13\_HS value of the qualifying clock group according to  $\frac{1}{5}$  9-5.

| CLKout12_13_DIV VALUE | CLKout12_13_HS              |  |  |  |  |  |  |  |  |

|-----------------------|-----------------------------|--|--|--|--|--|--|--|--|

| Odd                   | Must = 1 during SYNC event. |  |  |  |  |  |  |  |  |

| Even                  | Must = 0 during SYNC event. |  |  |  |  |  |  |  |  |

#### 表 9-5. Half-Step Programming Requirement of Qualifying Clock During SYNC Event

#### 9.4.6.1.1 Relative Dynamic Digital Delay

Relative dynamic digital delay can be used to program a clock output to a specific phase offset from another clock output.

Pros:

- Direct phase adjustment with respect to same clock output.

- Possible glitch pulses from clock output will always be the same during digital delay adjustment transient.

Cons:

- For some clock divide values there may be a glitch pulse due to SYNC assertion.