### LMH6642Q-Q1, LMH6643Q-Q1

ZHCSCS5C - JANUARY 2012-REVISED SEPTEMBER 2014

# LMH6642Q/LMH6643Q 低功耗 130MHz 75mA 轨到轨输出放大器

# 特性

- $(V_S = \pm 5V, T_A = 25^{\circ}C, R_I = 2k\Omega, A_V = +1.$ 无特殊说明则采用典型值)。

- $-3dB BW (A_V = +1) 130MHz$

- 电源电压范围在 2.7V 至 10V 之间

- 转换率,(A<sub>V</sub> = −1) 130V/µs<sup>(1)</sup>

- 电源电流(无负载)2.7 mA/amp

- 输出短路电流 +115mA/-145mA

- 线性输出电流 ±75mA

- 输入共模电压下限为 V⁻以下 0.5V, 上限为 V⁺以

- 输出电压距电源轨摆幅 40mV

- 输入电压噪声 (100kHz) 17nV/√Hz

- 输入电流噪声 (100kHz) 0.9pA/√Hz

- THD (5MHz,  $R_L = 2k\Omega$ ,  $V_O = 2V_{PP}$ ,  $A_V = +2$ ) -62dBc

- 稳定时间 68ns

- 在 3V、5V 和 ±5V 电压下体现完整特性

- 过驱恢复时间 100ns

- 输出短路保护(2)

- 超出 CMVR 时不发生输出反相

- LMH6643QMM 和 LMH6642QMF 符合 AEC-Q100 3 级要求并且按汽车应用级流程制造

- (1) 转换率是上升转换率和下降转换率的平均值

- $^{(2)}$  在室温及温度低于室温时, $V_S < 6V$  的输出短路持续时间无限。  $V_S > 6V$  时,允许的短路持续时间为 1.5ms。

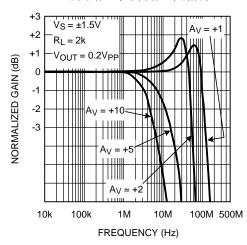

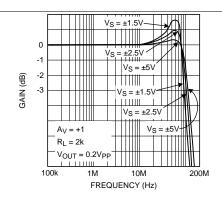

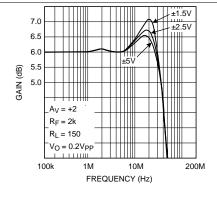

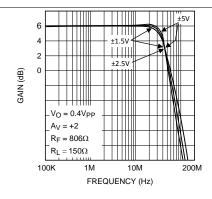

#### 闭环增益与 不同增益下的频率

## 2 应用

- 有源滤波器

- CD/DVD ROM

- ADC 缓冲放大器

- 便携式视频设备

- 电流感测缓冲器

- 汽车

## 3 说明

LMH664X 系列是真正的单电源电压反馈放大器,可提 供高速 (130MHz) 低失真 (-62dBc) 特性和超高输出电 流(约 **75mA**),与性能类似的现有器件相比,该产品 的成本和功耗更低。

输入共模电压范围扩展至下限 V⁻以下 0.5V, 上限 V⁺ 以上 1V。 各电源轨输出电压范围扩展至 40mV 以 内,允许较宽的动态范围,尤其适用于低压应用。输 出级能够输出约 75mA 的电流以驱动较大负载。 高速 输出转换率 (130V/us) 可确保较大的峰峰值输出摆幅即 使在更高的速度条件下也能保持不变, 从而在 3V 电源 下输出优异的 40MHz 满功率带宽。 器件的上述特性 及低成本优势是多种工业和商业应用的理想特性。

#### 器件信息(1)

| 部件号        | 封装         | 封装尺寸 (标称值)      |

|------------|------------|-----------------|

| LMH6642-Q1 | SOT-23 (5) | 2.90mm x 1.60mm |

| LMH6643-Q1 | VSSOP (8)  | 3.00mm × 3.00mm |

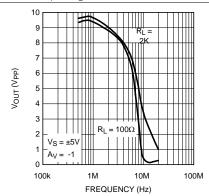

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。 大信号频率响应

Recommended Operating Conditions......4

7.4 Thermal Information ...... 4

7.5 3V Electrical Characteristics ...... 5

| 目園                                            | ž. |                                                              |    |

|-----------------------------------------------|----|--------------------------------------------------------------|----|

| 特性 1                                          |    | 7.7 ±5V Electrical Characteristics                           |    |

| 应用                                            |    | 7.8 Typical Performance Characteristics                      |    |

| 说明 1                                          | 8  |                                                              |    |

| 修订历史记录 2                                      |    | 8.1 Circuit Description                                      | 20 |

| Description (continued)3                      |    | 8.2 Single Supply, Low Power Photodiode Amplifier            |    |

| Pin Configuration and Functions3              |    | 8.3 Printed Circuit Board Layout and Component Value Section |    |

| Specifications4                               | 9  |                                                              |    |

| 7.1 Absolute Maximum Ratings <sup>(1)</sup> 4 | •  | 9.1 文档支持                                                     |    |

| 7.2 Handling Ratings 4                        |    | 9.2 相关链接                                                     |    |

商标.......25

# 4 修订历史记录

7.3

5

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision B (March 2013) to Revision C **Page** 已更改数据表结构和组织结构。添加、更新或重新命名了以下部分:器件信息表,引脚配置和功能,应用和实施,器 件和文档支持,机械、封装和订购信息.......1 Changed "Junction Temperature Range" to "Operating Temperature Range" in Recommended Operating Conditions...... 4 Deleted T<sub>J</sub> = 25°C in Electrical Characteristics tables. Changes from Revision A (March 2013) to Revision B Page

# 5 Description (continued)

Careful attention has been paid to ensure device stability under all operating voltages and modes. The result is a very well behaved frequency response characteristic (0.1dB gain flatness up the 12MHz under 150 $\Omega$  load and A<sub>V</sub> = +2) with minimal peaking (typically 2dB maximum) for any gain setting and under both heavy and light loads. This along with fast settling time (68ns) and low distortion allows the device to operate well in ADC buffer, and high frequency filter applications as well as other applications.

This device family offers professional quality video performance with low DG (0.01%) and DP (0.01°) characteristics. Differential Gain and Differential Phase characteristics are also well maintained under heavy loads ( $150\Omega$ ) and throughout the output voltage range. The LMH664X family is offered in single (LMH6642) and dual (LMH6643).

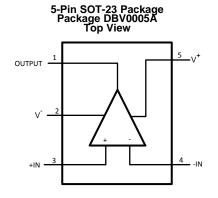

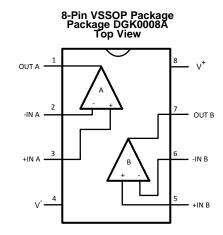

# 6 Pin Configuration and Functions

## **Pin Functions**

|                | PIN      |          |     |                         |

|----------------|----------|----------|-----|-------------------------|

| NAME           | NUN      | MBER     | 1/0 | DESCRIPTION             |

| NAME           | LMH6642Q | LMH6643Q |     |                         |

| -IN            | 4        |          | I   | Inverting Input         |

| +IN            | 3        |          | 1   | Non-inverting Input     |

| -IN A          |          | 2        | I   | ChA Inverting Input     |

| +IN A          |          | 3        | I   | ChA Non-inverting Input |

| -IN B          |          | 6        | I   | ChB Inverting Input     |

| +IN B          |          | 5        | I   | ChB Non-inverting Input |

| OUT A          |          | 1        | 0   | ChA Output              |

| OUT B          |          | 7        | 0   | ChB Output              |

| OUTPUT         | 1        |          | 0   | Output                  |

| V-             | 2        | 4        | I   | Negative Supply         |

| V <sup>+</sup> | 5        | 8        | I   | Positive Supply         |

# 7 Specifications

# 7.1 Absolute Maximum Ratings (1)(2)(1)

over operating free-air temperature range (unless otherwise noted)

|                                                   | MIN | MAX                                        | UNIT |

|---------------------------------------------------|-----|--------------------------------------------|------|

| V <sub>IN</sub> Differential                      |     | ±2.5                                       | V    |

| Output Short Circuit Duration                     |     | See (3) and (4)                            |      |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) |     | 13.5                                       | V    |

| Voltage at Input/Output pins                      |     | V <sup>+</sup> +0.8<br>V <sup>-</sup> -0.8 | V    |

| Input Current                                     |     | ±10                                        | mA   |

| Junction Temperature <sup>(5)</sup>               |     | +150                                       | °C   |

| Soldering Information                             |     |                                            |      |

| Infrared or Convection Reflow (20 sec)            |     | 235                                        | °C   |

| Wave Soldering Lead Temp.(10 sec)                 |     | 260                                        | °C   |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

- (4) Output short circuit duration is infinite for V<sub>S</sub> < 6 V at room temperature and below. For V<sub>S</sub> > 6 V, allowable short circuit duration is 1.5ms.

- (5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PC board.

# 7.2 Handling Ratings

|                    |                           |                                                         | MIN | MAX  | UNIT |

|--------------------|---------------------------|---------------------------------------------------------|-----|------|------|

| T <sub>stg</sub>   | Storage temperature range |                                                         | -65 | +150 | °C   |

|                    |                           | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |     | 2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Machine Model (MM) <sup>(2)</sup>                       |     | 200  | V    |

|                    |                           | Charged Device Model (CDM), per AEC Q100-011            |     | 1000 |      |

AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification,1.5kΩ in series with 100pF.

# 7.3 Recommended Operating Conditions<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                   | MIN | MAX | UNIT |

|---------------------------------------------------|-----|-----|------|

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) | 2.7 | 10  | V    |

| Operating Temperature Range <sup>(2)</sup>        | -40 | +85 | °C   |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

#### 7.4 Thermal Information

|                 | THERMAL METRIC <sup>(1)</sup>                         | DBV05A  | DGK08A   | UNIT |

|-----------------|-------------------------------------------------------|---------|----------|------|

|                 | I TERMAL METRIC"                                      | 5 PINS  | S 8 PINS | UNII |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance <sup>(2)</sup> | 265°C/W | 235°C/W  | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Machine Model,  $0\Omega$  in series with 200pF.

<sup>(2)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta,JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/R_{\theta,JA}$ . All numbers apply for packages soldered directly onto a PC board.

The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PC board.

## 7.5 3V Electrical Characteristics

Unless otherwise specified, all limits ensured for  $V^+=3V$ ,  $V^-=0V$ ,  $V_{CM}=V_O=V^+/2$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L=2k\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

|                     | PARAMETER                        | TEST CONDITIONS                                                                               | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup>    | UNIT               |

|---------------------|----------------------------------|-----------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|--------------------|

| BW                  | -3dB BW                          | $A_V = +1$ , $V_{OUT} = 200$ m $V_{PP}$                                                       | 80                 | 115                |                       | MIL                |

|                     |                                  | $A_V = +2, -1, V_{OUT} = 200 \text{mV}_{PP}$                                                  |                    | 46                 |                       | MHz                |

| BW <sub>0.1dB</sub> | 0.1dB Gain Flatness              | $A_V = +2$ , $R_L = 150\Omega$ to V+/2,<br>$R_L = 402\Omega$ , $V_{OUT} = 200 \text{mV}_{PP}$ |                    | 19                 |                       | MHz                |

| PBW                 | Full Power Bandwidth             | $A_V = +1$ , $-1dB$ , $V_{OUT} = 1V_{PP}$                                                     |                    | 40                 |                       | MHz                |

| en                  | Input-Referred Voltage Noise     | f = 100kHz                                                                                    |                    | 17                 |                       | nV/√ <del>Hz</del> |

|                     |                                  | f = 1kHz                                                                                      |                    | 48                 |                       | 110/ 1112          |

| i <sub>n</sub>      | Input-Referred Current Noise     | f = 100kHz                                                                                    |                    | 0.90               |                       | pA/√ <del>Hz</del> |

|                     |                                  | f = 1kHz                                                                                      |                    | 3.3                |                       | ρΑ/ 1112           |

| THD                 | Total Harmonic Distortion        | $f = 5MHz$ , $V_O = 2V_{PP}$ , $A_V = -1$ , $R_L = 100Ω$ to $V^+/2$                           |                    | -48                |                       | dBc                |

| DG                  | Differential Gain                | $V_{CM} = 1V$ , NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to $V^+/2$                              |                    | 0.17%              |                       |                    |

|                     |                                  | $R_L = 1k\Omega$ to $V^+/2$                                                                   |                    | 0.03%              |                       |                    |

| DP                  | Differential Phase               | $V_{CM} = 1V$ , NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to $V^+/2$                              |                    | 0.05               |                       | deg                |

|                     |                                  | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                                         |                    | 0.03               |                       | Ü                  |

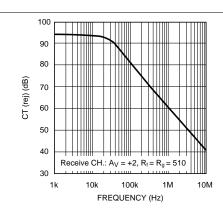

| CT Rej.             | Cross-Talk Rejection             | f = 5MHz, Receiver:<br>$R_f = R_g = 510\Omega$ , $A_V = +2$                                   |                    | 47                 |                       | dB                 |

| T <sub>S</sub>      | Settling Time                    | $V_{O} = 2V_{PP}, \pm 0.1\%, 8pF Load, V_{S} = 5V$                                            |                    | 68                 |                       | ns                 |

| SR                  | Slew Rate <sup>(3)</sup>         | $A_V = -1$ , $V_I = 2V_{PP}$                                                                  | 90                 | 120                |                       | V/µs               |

| V <sub>OS</sub>     | Input Offset Voltage             | For LMH6642                                                                                   |                    | ±1                 | ±5<br><b>±7</b>       | \/                 |

|                     |                                  | For LMH6643                                                                                   |                    | ±1                 | ±3.4<br><b>±7</b>     | mV                 |

| TC V <sub>OS</sub>  | Input Offset Average Drift       | (4)                                                                                           |                    | ±5                 |                       | μV/°C              |

| I <sub>B</sub>      | Input Bias Current               | (5)                                                                                           |                    | -1.50              | -2.60<br><b>-3.25</b> | μΑ                 |

| I <sub>OS</sub>     | Input Offset Current             |                                                                                               |                    | 20                 | 800<br><b>1000</b>    | nA                 |

| R <sub>IN</sub>     | Common Mode Input Resistance     |                                                                                               |                    | 3                  |                       | ΜΩ                 |

| C <sub>IN</sub>     | Common Mode Input<br>Capacitance |                                                                                               |                    | 2                  |                       | pF                 |

| CMVR                | Input Common-Mode Voltage Range  | CMRR ≥ 50dB                                                                                   |                    | -0.5               | -0.2<br><b>-0.1</b>   | V                  |

|                     |                                  |                                                                                               | 1.8<br><b>1.6</b>  | 2.0                |                       | V                  |

| CMRR                | Common Mode Rejection Ratio      | V <sub>CM</sub> Stepped from 0V to 1.5V                                                       | 72                 | 95                 |                       | dB                 |

| A <sub>VOL</sub>    | Large Signal Voltage Gain        | $V_O = 0.5V$ to 2.5V<br>$R_L = 2k\Omega$ to V <sup>+</sup> /2                                 | 80<br><b>75</b>    | 96                 |                       | dB                 |

|                     |                                  | $V_{O} = 0.5V \text{ to } 2.5V$<br>$R_{L} = 150\Omega \text{ to } V^{+}/2$                    | 74<br><b>70</b>    | 82                 |                       |                    |

| Vo                  | Output Swing                     | $R_L = 2k\Omega \text{ to V}^+/2, V_{ID} = 200\text{mV}$                                      | 2.90               | 2.98               |                       |                    |

|                     | High                             | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = 200$ mV                                     | 2.80               | 2.93               |                       | V                  |

|                     | Output Swing                     | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200$ mV                                     |                    | 25                 | 75                    |                    |

|                     | Low                              | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200$ mV                                    |                    | 75                 | 150                   | mV                 |

<sup>(1)</sup> All limits are ensured by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm.

<sup>(3)</sup> Slew rate is the average of the rising and falling slew rates.

<sup>(4)</sup> Offset voltage average drift determined by dividing the change in V<sub>OS</sub> at temperature extremes by the total temperature change.

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

# **3V Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for  $V^+=3V$ ,  $V^-=0V$ ,  $V_{CM}=V_O=V^+/2$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L=2k\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

|                  | PARAMETER                             | TEST CONDITIONS                                                         | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup>  | UNIT |

|------------------|---------------------------------------|-------------------------------------------------------------------------|--------------------|--------------------|---------------------|------|

| I <sub>SC</sub>  | Output Short Circuit Current          | Sourcing to V <sup>+</sup> /2<br>V <sub>ID</sub> = 200mV <sup>(6)</sup> | 50<br><b>35</b>    | 95                 |                     | A    |

|                  |                                       | Sinking to V <sup>+</sup> /2<br>$V_{ID} = -200 \text{mV}^{(6)}$         | 55<br><b>40</b>    | 110                |                     | mA   |

| I <sub>OUT</sub> | Output Current                        | V <sub>OUT</sub> = 0.5V from either supply                              |                    | ±65                |                     | mA   |

| +PSRR            | Positive Power Supply Rejection Ratio | $V^{+} = 3.0V$ to 3.5V, $V_{CM} = 1.5V$                                 | 75                 | 85                 |                     | dB   |

| I <sub>S</sub>   | Supply Current (per channel)          | No Load                                                                 |                    | 2.70               | 4.00<br><b>4.50</b> | mA   |

<sup>(6)</sup> Short circuit test is a momentary test. Output short circuit duration is infinite for V<sub>S</sub> < 6V at room temperature and below. For V<sub>S</sub> > 6V, allowable short circuit duration is 1.5ms.

## 7.6 5V Electrical Characteristics

Unless otherwise specified, all limits ensured for  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L = 2k\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

|                     | PARAMETER                          | TEST CONDITIONS                                                                               | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup>    | UNIT               |

|---------------------|------------------------------------|-----------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|--------------------|

| BW                  | -3dB BW                            | $A_V = +1$ , $V_{OUT} = 200$ m $V_{PP}$                                                       | 90                 | 120                |                       |                    |

|                     |                                    | A <sub>V</sub> = +2, −1, V <sub>OUT</sub> = 200mV <sub>PP</sub>                               |                    | 46                 |                       | MHz                |

| BW <sub>0.1dB</sub> | 0.1dB Gain Flatness                | $A_V = +2$ , $R_L = 150\Omega$ to V+/2,<br>$R_f = 402\Omega$ , $V_{OUT} = 200 \text{mV}_{PP}$ |                    | 15                 |                       | MHz                |

| PBW                 | Full Power Bandwidth               | $A_V = +1, -1dB, V_{OUT} = 2V_{PP}$                                                           |                    | 22                 |                       | MHz                |

| e <sub>n</sub>      | Input-Referred Voltage Noise       | f = 100kHz                                                                                    |                    | 17                 |                       | nV/√ <del>Hz</del> |

|                     |                                    | f = 1kHz                                                                                      |                    | 48                 |                       | IIV/ VIIZ          |

| i <sub>n</sub>      | Input-Referred Current Noise       | f = 100kHz                                                                                    |                    | 0.90               |                       | pA/√ <del>Hz</del> |

|                     |                                    | f = 1kHz                                                                                      |                    | 3.3                |                       | pA/ vnz            |

| THD                 | Total Harmonic Distortion          | $f = 5MHz, V_O = 2V_{PP}, A_V = +2$                                                           |                    | -60                |                       | dBc                |

| DG                  | Differential Gain                  | NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to $V^+/2$                                              |                    | 0.16%              |                       |                    |

|                     |                                    | $R_L = 1k\Omega$ to $V^+/2$                                                                   |                    | 0.05%              |                       |                    |

| DP                  | Differential Phase                 | NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to $V^+/2$                                              |                    | 0.05               |                       | deg                |

|                     |                                    | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                                         |                    | 0.01               |                       | Ü                  |

| CT Rej.             | Cross-Talk Rejection               | f = 5MHz, Receiver:<br>$R_f = R_g = 510\Omega$ , $A_V = +2$                                   |                    | 47                 |                       | dB                 |

| T <sub>S</sub>      | Settling Time                      | $V_O = 2V_{PP}$ , ±0.1%, 8pF Load                                                             |                    | 68                 |                       | ns                 |

| SR                  | Slew Rate (3)                      | $A_V = -1$ , $V_I = 2V_{PP}$                                                                  | 95                 | 125                |                       | V/µs               |

| V <sub>OS</sub>     | Input Offset Voltage               | For LMH6642                                                                                   |                    | ±1                 | ±5<br><b>±7</b>       |                    |

|                     |                                    | For LMH6643                                                                                   |                    | ±1                 | ±3.4<br>±7            | mV                 |

| TC V <sub>OS</sub>  | Input Offset Average Drift         | (4)                                                                                           |                    | ±5                 |                       | μV/°C              |

| I <sub>B</sub>      | Input Bias Current                 | (5)                                                                                           |                    | -1.70              | -2.60<br><b>-3.25</b> | μΑ                 |

| I <sub>OS</sub>     | Input Offset Current               |                                                                                               |                    | 20                 | 800<br><b>1000</b>    | nA                 |

| R <sub>IN</sub>     | Common Mode Input Resistance       |                                                                                               |                    | 3                  |                       | ΜΩ                 |

| C <sub>IN</sub>     | Common Mode Input Capacitance      |                                                                                               |                    | 2                  |                       | pF                 |

| CMVR                | Input Common-Mode Voltage<br>Range | CMRR ≥ 50dB                                                                                   |                    | -0.5               | -0.2<br><b>-0.1</b>   | V                  |

|                     |                                    |                                                                                               | 3.8<br><b>3.6</b>  | 4.0                |                       | V                  |

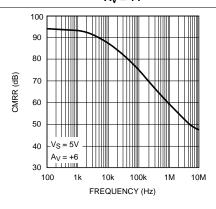

| CMRR                | Common Mode Rejection Ratio        | V <sub>CM</sub> Stepped from 0V to 3.5V                                                       | 72                 | 95                 |                       | dB                 |

| A <sub>VOL</sub>    | Large Signal Voltage Gain          | $V_{O} = 0.5V \text{ to } 4.50V$<br>$R_{L} = 2k\Omega \text{ to } V^{+}/2$                    | 86<br><b>82</b>    | 98                 |                       | dB                 |

|                     |                                    | $V_{O} = 0.5V \text{ to } 4.25V$<br>$R_{L} = 150\Omega \text{ to } V^{+}/2$                   | 76<br><b>72</b>    | 82                 |                       |                    |

| Vo                  | Output Swing                       | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = 200$ mV                                      | 4.90               | 4.98               |                       | V                  |

|                     | High                               | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = 200$ mV                                     | 4.65               | 4.90               |                       |                    |

|                     | Output Swing                       | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200$ mV                                     |                    | 25                 | 100                   | mV                 |

|                     | Low                                | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200$ mV                                    |                    | 100                | 150                   |                    |

All limits are ensured by testing or statistical analysis.

Typical values represent the most likely parametric norm. Slew rate is the average of the rising and falling slew rates.

Offset voltage average drift determined by dividing the change in VOS at temperature extremes by the total temperature change.

Positive current corresponds to current flowing into the device.

# **5V Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L = 2k\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

|                  | PARAMETER                             | TEST CONDITIONS                                       | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup>  | UNIT |

|------------------|---------------------------------------|-------------------------------------------------------|--------------------|--------------------|---------------------|------|

| I <sub>SC</sub>  | Output Short Circuit Current          | Sourcing to $V^+/2$<br>$V_{ID} = 200 \text{mV}^{(6)}$ | 55<br><b>40</b>    | 115                |                     | mA   |

|                  |                                       | Sinking to $V^+/2$<br>$V_{ID} = -200 \text{mV}^{(6)}$ | 70<br><b>55</b>    | 140                |                     | IIIA |

| I <sub>OUT</sub> | Output Current                        | V <sub>O</sub> = 0.5V from either supply              |                    | ±70                |                     | mA   |

| +PSRR            | Positive Power Supply Rejection Ratio | V <sup>+</sup> = 4.0V to 6V                           | 79                 | 90                 |                     | dB   |

| Is               | Supply Current (per channel)          | No Load                                               |                    | 2.70               | 4.25<br><b>5.00</b> | mA   |

<sup>(6)</sup> Short circuit test is a momentary test. Output short circuit duration is infinite for V<sub>S</sub> < 6V at room temperature and below. For V<sub>S</sub> > 6V, allowable short circuit duration is 1.5ms.

## 7.7 ±5V Electrical Characteristics

Unless otherwise specified, all limits ensured for  $V^+ = 5V$ ,  $V^- = -5V$ ,  $V_{CM} = V_O = 0V$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L = 2k\Omega$  to ground. **Boldface** limits apply at the temperature extremes.

|                     | PARAMETER                        | TEST CONDITIONS                                                                               | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup>    | UNIT               |

|---------------------|----------------------------------|-----------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|--------------------|

| BW                  | -3dB BW                          | $A_V = +1$ , $V_{OUT} = 200 \text{mV}_{PP}$                                                   | 95                 | 130                |                       | N 41 1-            |

|                     |                                  | A <sub>V</sub> = +2, −1, V <sub>OUT</sub> = 200mV <sub>PP</sub>                               |                    | 46                 |                       | MHz                |

| BW <sub>0.1dB</sub> | 0.1dB Gain Flatness              | $A_V = +2$ , $R_L = 150\Omega$ to V+/2,<br>$R_f = 806\Omega$ , $V_{OUT} = 200 \text{mV}_{PP}$ |                    | 12                 |                       | MHz                |

| PBW                 | Full Power Bandwidth             | $A_V = +1$ , $-1dB$ , $V_{OUT} = 2V_{PP}$                                                     |                    | 24                 |                       | MHz                |

| e <sub>n</sub>      | Input-Referred Voltage Noise     | f = 100kHz                                                                                    |                    | 17                 |                       | nV/√ <del>Hz</del> |

|                     |                                  | f = 1kHz                                                                                      |                    | 48                 |                       | 117/ 1112          |

| in                  | Input-Referred Current Noise     | f = 100kHz                                                                                    |                    | 0.90               |                       | pA/√ <del>Hz</del> |

|                     |                                  | f = 1kHz                                                                                      |                    | 3.3                |                       | pA/ VHZ            |

| THD                 | Total Harmonic Distortion        | $f = 5MHz, V_O = 2V_{PP}, A_V = +2$                                                           |                    | -62                |                       | dBc                |

| DG                  | Differential Gain                | NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to $V^+/2$                                              |                    | 0.15%              |                       |                    |

|                     |                                  | $R_L = 1k\Omega$ to $V^+/2$                                                                   |                    | 0.01%              |                       |                    |

| DP                  | Differential Phase               | NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to V <sup>+</sup> /2                                    |                    | 0.04               |                       | deg                |

|                     |                                  | $R_L = 1k\Omega$ to $V^+/2$                                                                   |                    | 0.01               |                       | Ü                  |

| CT Rej.             | Cross-Talk Rejection             | f = 5MHz, Receiver:<br>$R_f = R_g = 510\Omega$ , $A_V = +2$                                   |                    | 47                 |                       | dB                 |

| T <sub>S</sub>      | Settling Time                    | $V_{O} = 2V_{PP}$ , ±0.1%, 8pF Load, $V_{S} = 5V$                                             |                    | 68                 |                       | ns                 |

| SR                  | Slew Rate (3)                    | $A_V = -1$ , $V_I = 2V_{PP}$                                                                  | 100                | 135                |                       | V/µs               |

| V <sub>OS</sub>     | Input Offset Voltage             | For LMH6642                                                                                   |                    | ±1                 | ±5<br><b>±7</b>       | \/                 |

|                     |                                  | For LMH6643                                                                                   |                    | ±1                 | ±3.4<br><b>±7</b>     | mV                 |

| TC Vos              | Input Offset Average Drift       | (4)                                                                                           |                    | ±5                 |                       | μV/°C              |

| I <sub>B</sub>      | Input Bias Current               | (5)                                                                                           |                    | -1.60              | -2.60<br><b>-3.25</b> | μΑ                 |

| I <sub>OS</sub>     | Input Offset Current             |                                                                                               |                    | 20                 | 800<br><b>1000</b>    | nA                 |

| R <sub>IN</sub>     | Common Mode Input Resistance     |                                                                                               |                    | 3                  |                       | ΜΩ                 |

| C <sub>IN</sub>     | Common Mode Input<br>Capacitance |                                                                                               |                    | 2                  |                       | pF                 |

| CMVR                | Input Common-Mode Voltage Range  | CMRR ≥ 50dB                                                                                   |                    | <b>-</b> 5.5       | -5.2<br><b>-5.1</b>   | W                  |

|                     |                                  |                                                                                               | 3.8<br><b>3.6</b>  | 4.0                |                       | V                  |

| CMRR                | Common Mode Rejection Ratio      | V <sub>CM</sub> Stepped from -5V to 3.5V                                                      | 74                 | 95                 |                       | dB                 |

| A <sub>VOL</sub>    | Large Signal Voltage Gain        | $V_O = -4.5V$ to 4.5V,<br>$R_L = 2k\Omega$                                                    | 88<br><b>84</b>    | 96                 |                       | ٩D                 |

|                     |                                  | $V_{O} = -4.0V \text{ to } 4.0V,$ $R_{L} = 150\Omega$                                         | 78<br><b>74</b>    | 82                 |                       | dB                 |

| Vo                  | Output Swing                     | $R_L = 2k\Omega$ , $V_{ID} = 200mV$                                                           | 4.90               | 4.96               |                       |                    |

|                     | High                             | $R_L = 150\Omega, V_{ID} = 200 \text{mV}$                                                     | 4.65               | 4.80               |                       | V                  |

|                     | Output Swing                     | $R_L = 2k\Omega$ , $V_{ID} = -200$ mV                                                         |                    | -4.96              | -4.90                 |                    |

|                     | Low                              | $R_L = 150\Omega, V_{ID} = -200mV$                                                            |                    | -4.80              | -4.65                 | V                  |

<sup>1)</sup> All limits are ensured by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm.

<sup>(3)</sup> Slew rate is the average of the rising and falling slew rates.

<sup>(4)</sup> Offset voltage average drift determined by dividing the change in V<sub>OS</sub> at temperature extremes by the total temperature change.

<sup>5)</sup> Positive current corresponds to current flowing into the device.

# ±5V Electrical Characteristics (continued)

Unless otherwise specified, all limits ensured for  $V^+ = 5V$ ,  $V^- = -5V$ ,  $V_{CM} = V_O = 0V$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L = 2k\Omega$  to ground. **Boldface** limits apply at the temperature extremes.

|                  | PARAMETER                    | TEST CONDITIONS                                              | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup>  | UNIT |

|------------------|------------------------------|--------------------------------------------------------------|--------------------|--------------------|---------------------|------|

| I <sub>SC</sub>  | Output Short Circuit Current | Sourcing to Ground V <sub>ID</sub> = 200mV <sup>(6)</sup>    | 60<br><b>35</b>    | 115                |                     | mA   |

|                  |                              | Sinking to Ground<br>V <sub>ID</sub> = −200mV <sup>(6)</sup> | 85<br><b>65</b>    | 145                |                     | IIIA |

| I <sub>OUT</sub> | Output Current               | V <sub>O</sub> = 0.5V from either supply                     | ±75                |                    |                     | mA   |

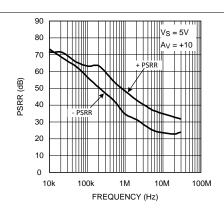

| PSRR             | Power Supply Rejection Ratio | $(V^+, V^-) = (4.5V, -4.5V)$ to $(5.5V, -5.5V)$              | 78                 | 90                 |                     | dB   |

| I <sub>S</sub>   | Supply Current (per channel) | No Load                                                      |                    | 2.70               | 4.50<br><b>5.50</b> | mA   |

<sup>(6)</sup> Short circuit test is a momentary test. Output short circuit duration is infinite for V<sub>S</sub> < 6V at room temperature and below. For V<sub>S</sub> > 6V, allowable short circuit duration is 1.5ms.

# 7.8 Typical Performance Characteristics

Figure 1. Closed Loop Frequency Response for Various Supplies

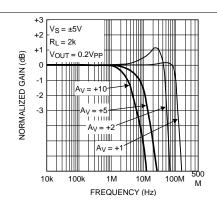

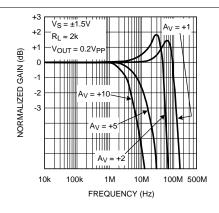

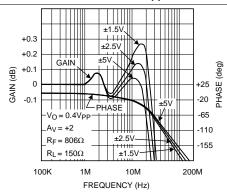

Figure 3. Closed Loop Gain vs. Frequency for Various Gain

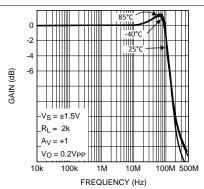

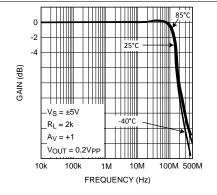

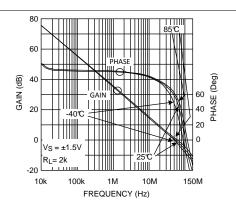

Figure 4. Closed Loop Frequency Response for Various Temperature

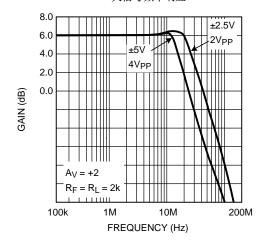

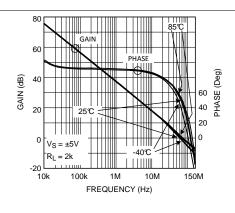

Figure 5. Closed Loop Gain vs. Frequency for Various Supplies

Figure 6. Closed Loop Frequency Response for Various Temperature

# TEXAS INSTRUMENTS

# **Typical Performance Characteristics (continued)**

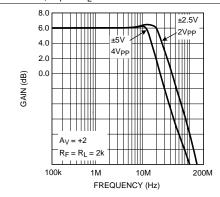

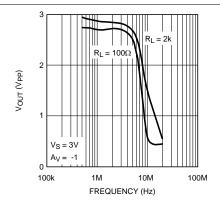

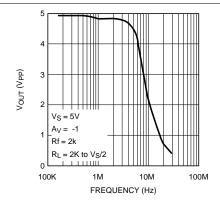

Figure 7. Large Signal Frequency Response

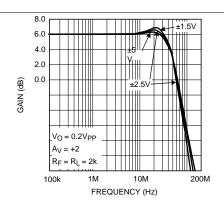

Figure 8. Closed Loop Small Signal Frequency Response for Various Supplies

Figure 9. Closed Loop Frequency Response for Various Supplies

Figure 10. ±0.1dB Gain Flatness for Various Supplies

Figure 11.  $V_{OUT}$  ( $V_{PP}$ ) for THD < 0.5%

Figure 12.  $V_{OUT}$  ( $V_{PP}$ ) for THD < 0.5%

# **Typical Performance Characteristics (continued)**

Figure 13.  $V_{OUT}$  ( $V_{PP}$ ) for THD < 0.5%

Figure 14. Open Loop Gain/Phase for Various Temperature

Figure 15. Open Loop Gain/Phase for Various Temperature

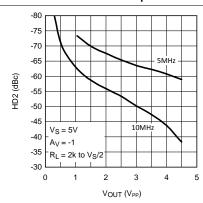

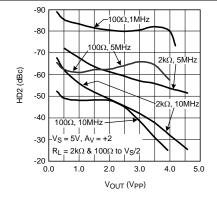

Figure 16. HD2 (dBc) vs. Output Swing

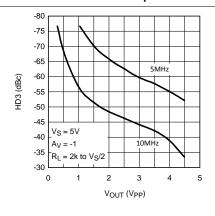

Figure 17. HD3 (dBc) vs. Output Swing

Figure 18. HD2 vs. Output Swing

# TEXAS INSTRUMENTS

# **Typical Performance Characteristics (continued)**

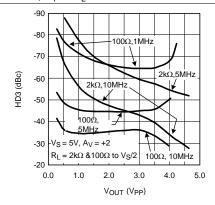

Figure 19. HD3 vs. Output Swing

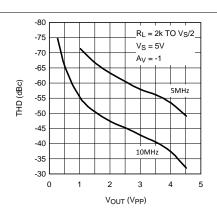

Figure 20. THD (dBc) vs. Output Swing

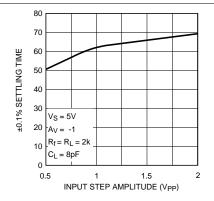

Figure 21. Settling Time vs. Input Step Amplitude (Output Slew and Settle Time)

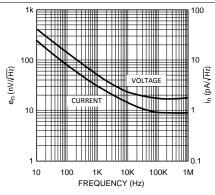

Figure 22. Input Noise vs. Frequency

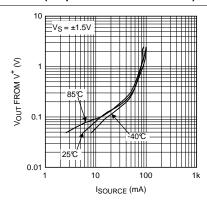

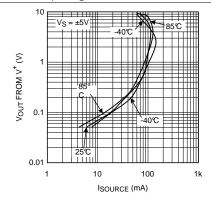

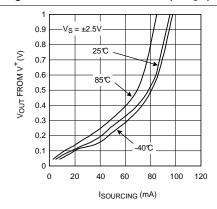

Figure 23.  $V_{OUT}$  from V<sup>+</sup> vs.  $I_{SOURCE}$

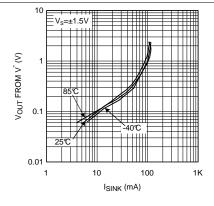

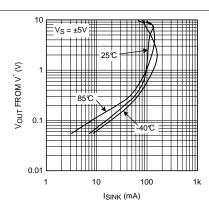

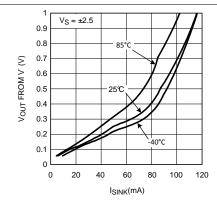

Figure 24.  $V_{OUT}$  from  $V^-$  vs.  $I_{SINK}$

# **Typical Performance Characteristics (continued)**

Figure 25. V<sub>OUT</sub> from V<sup>+</sup> vs. I<sub>SOURCE</sub>

Figure 26. V<sub>OUT</sub> from V<sup>-</sup> vs. I<sub>SINK</sub>

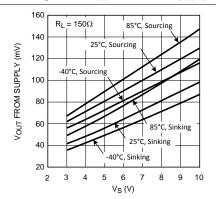

Figure 27. Swing vs. V<sub>S</sub>

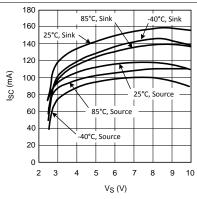

Figure 28. Short Circuit Current (to V<sub>S</sub>/2) vs. V<sub>S</sub>

Figure 29. Output Sinking Saturation Voltage vs.  $I_{OUT}$

Figure 30. Output Sourcing Saturation Voltage vs. I<sub>OUT</sub>

# TEXAS INSTRUMENTS

# **Typical Performance Characteristics (continued)**

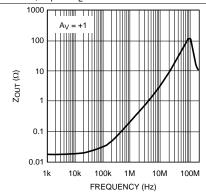

Figure 31. Closed Loop Output Impedance vs. Frequency,  $A_V = +1$

Figure 33. CMRR vs. Frequency

Figure 34. Crosstalk Rejection vs. Frequency (Output to Output)

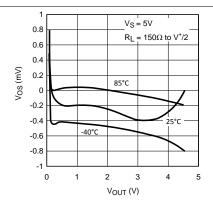

Figure 35. V<sub>OS</sub> vs. V<sub>OUT</sub> (Typical Unit)

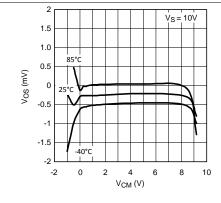

Figure 36. V<sub>OS</sub> vs. V<sub>CM</sub> (Typical Unit)

# **Typical Performance Characteristics (continued)**

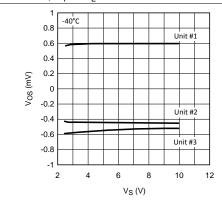

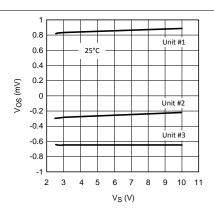

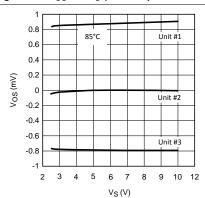

Figure 37. V<sub>OS</sub> vs. V<sub>S</sub> (for 3 Representative Units)

Figure 38. V<sub>OS</sub> vs. V<sub>S</sub> (for 3 Representative Units)

Figure 39. V<sub>OS</sub> vs. V<sub>S</sub> (for 3 Representative Units)

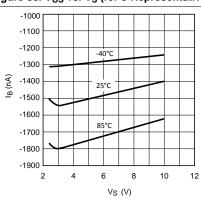

Figure 40.  $I_B$  vs.  $V_S$

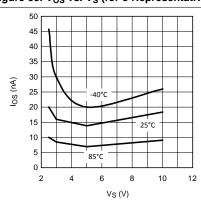

Figure 41. I<sub>OS</sub> vs. V<sub>S</sub>

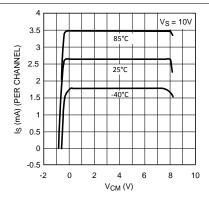

Figure 42.  $I_{\rm S}$  vs.  $V_{\rm CM}$

# TEXAS INSTRUMENTS

# **Typical Performance Characteristics (continued)**

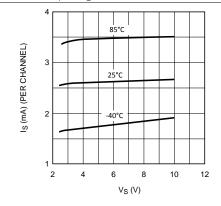

Figure 43. I<sub>S</sub> vs. V<sub>S</sub>

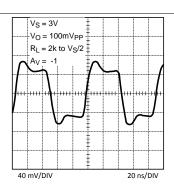

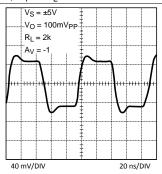

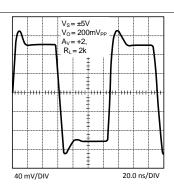

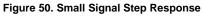

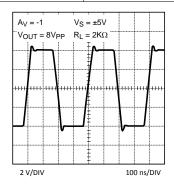

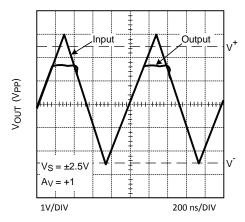

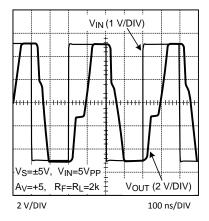

Figure 44. Small Signal Step Response

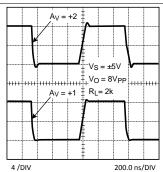

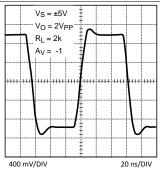

Figure 45. Large Signal Step Response

Figure 46. Large Signal Step Response

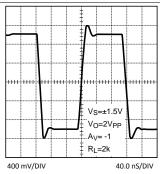

Figure 47. Small Signal Step Response

Figure 48. Small Signal Step Response

# **Typical Performance Characteristics (continued)**

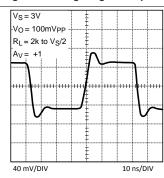

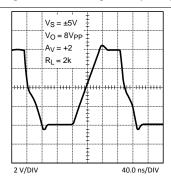

Figure 49. Small Signal Step Response

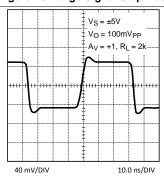

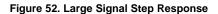

Figure 51. Large Signal Step Response

Figure 53. Large Signal Step Response

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Circuit Description

The LMH664X family is based on Texas Instruments' proprietary VIP10 dielectrically isolated bipolar process.

This device family architecture features the following:

- Complimentary bipolar devices with exceptionally high f<sub>t</sub> (~8 GHz) even under low supply voltage (2.7 V) and low bias current.

- A class A-B "turn-around" stage with improved noise, offset, and reduced power dissipation compared to similar speed devices (patent pending).

- Common Emitter push-push output stage capable of 75mA output current (at 0.5V from the supply rails) while consuming only 2.7 mA of total supply current per channel. This architecture allows output to reach within milli-volts of either supply rail.

- Consistent performance over the entire operating supply voltage range with little variation for the most important specifications (for example, BW, SR, I<sub>OUT</sub>, and so forth).

- Significant power saving (~40%) compared to competitive devices on the market with similar performance.

### 8.1.1 Application Hints

This Op Amp family is a drop-in replacement for the AD805X family of high speed Op Amps in most applications. In addition, the LMH664X will typically save about 40% on power dissipation, due to lower supply current, when compared to competition. All AD805X family's ensured parameters are included in the list of LMH664X ensured specifications in order to ensure equal or better level of performance. However, as in most high performance parts, due to subtleties of applications, it is strongly recommended that the performance of the part to be evaluated is tested under actual operating conditions to ensure full compliance to all specifications.

With 3V supplies and a common mode input voltage range that extends 0.5V below  $V^-$ , the LMH664X find applications in low voltage/low power applications. Even with 3V supplies, the -3dB BW (@  $A_V = +1$ ) is typically 115MHz with a tested limit of 80MHz. Production testing ensures that process variations with not compromise speed. High frequency response is exceptionally stable confining the typical -3dB BW over the industrial temperature range to  $\pm 2.5\%$ .

As can be seen from the *Typical Performance Characteristics*, the LMH664X output current capability (~75mA) is enhanced compared to AD805X. This enhancement, increases the output load range, adding to the LMH664X's versatility.

Because of the LMH664X's high output current capability attention should be given to device junction temperature in order not to exceed the Absolute Maximum Rating.

## **Circuit Description (continued)**

This device family was designed to avoid output phase reversal. With input overdrive, the output is kept near supply rail (or as closed to it as mandated by the closed loop gain setting and the input voltage). See Figure 54:

Figure 54. Input and Output Shown with CMVR Exceeded

However, if the input voltage range of -0.5V to 1V from  $V^+$  is exceeded by more than a diode drop, the internal ESD protection diodes will start to conduct. The current in the diodes should be kept at or below 10mA.

Output overdrive recovery time is less than 100ns as can be seen from Figure 55 plot:

Figure 55. Overload Recovery Waveform

## **Circuit Description (continued)**

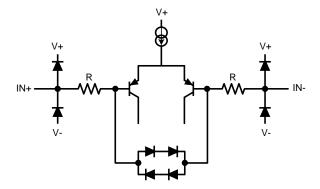

### 8.1.2 Input and Output Topology

All input / output pins are protected against excessive voltages by ESD diodes connected to V $^+$  and V $^-$  rails (see Figure 56). These diodes start conducting when the input / output pin voltage approaches  $1V_{be}$  beyond V $^+$  or V $^-$  to protect against over voltage. These diodes are normally reverse biased. Further protection of the inputs is provided by the two resistors (R in Figure 56), in conjunction with the string of anti-parallel diodes connected between both bases of the input stage. The combination of these resistors and diodes reduces excessive differential input voltages approaching  $2V_{be}$ . The most common situation when this occurs is when the device is used as a comparator (or with little or no feedback) and the device inputs no longer follow each other. In such a case, the diodes may conduct. As a consequence, input current increases and the differential input voltage is clamped. It is important to make sure that the subsequent current flow through the device input pins does not violate the Absolute Maximum Ratings of the device. To limit the current through this protection circuit, extra series resistors can be placed. Together with the built-in series resistors of several hundred ohms, these external resistors can limit the input current to a safe number (i.e. < 10mA). Be aware that these input series resistors may impact the switching speed of the device and could slow down the device.

Figure 56. Input Equivalent Circuit

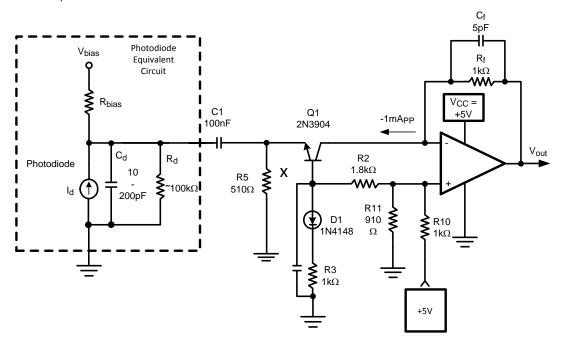

# 8.2 Single Supply, Low Power Photodiode Amplifier

The circuit shown in Figure 57 is used to amplify the current from a photo-diode into a voltage output. In this circuit, the emphasis is on achieving high bandwidth and the transimpedance gain setting is kept relatively low. Because of its high slew rate limit and high speed, the LMH664X family lends itself well to such an application.

This circuit achieves approximately 1V/mA of transimpedance gain and capable of handling up to  $1mA_{pp}$  from the photodiode. Q1, in a common base configuration, isolates the high capacitance of the photodiode ( $C_d$ ) from the Op Amp input in order to maximize speed. Input is AC coupled through C1 to ease biasing and allow single supply operation. With 5V single supply, the device input/output is shifted to near half supply using a voltage divider from  $V_{CC}$ . Note that Q1 collector does not have any voltage swing and the Miller effect is minimized. D1, tied to Q1 base, is for temperature compensation of Q1's bias point. Q1 collector current was set to be large enough to handle the peak-to-peak photodiode excitation and not too large to shift the U1 output too far from mid-supply.

No matter how low an  $R_f$  is selected, there is a need for  $C_f$  in order to stabilize the circuit. The reason for this is that the Op Amp input capacitance and Q1 equivalent collector capacitance together ( $C_{IN}$ ) will cause additional phase shift to the signal fed back to the inverting node.  $C_f$  will function as a zero in the feedback path counteracting the effect of the  $C_{IN}$  and acting to stabilized the circuit. By proper selection of  $C_f$  such that the Op Amp open loop gain is equal to the inverse of the feedback factor at that frequency, the response is optimized with a theoretical  $45^{\circ}$  phase margin.

$$C_F = \sim SQRT \left[ (C_{IN})/(2\pi \cdot GBWP \cdot R_F) \right]$$

Optimized as such, the I-V converter will have a theoretical pole, fp, at:

$$f_P = SQRT \left[ GBWP/(2\pi R_F \cdot C_{IN}) \right]$$

(2)

With Op Amp input capacitance of 3pF and an estimate for Q1 output capacitance of about 3pF as well,  $C_{IN}$  = 6pF. From *Typical Performance Characteristics*, LMH6642/6643 family GBWP is approximately 57 MHz. Therefore, with  $R_f$  = 1k, from Equation 1 and Equation 2 above.

$$C_f = \sim 4.1 \text{ pF}$$

, and  $f_p = 39 \text{ MHz}$

Figure 57. Single Supply Photodiode I-V Converter

(1)

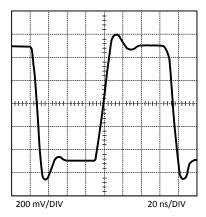

# Single Supply, Low Power Photodiode Amplifier (continued)

For this example, optimum  $C_f$  was empirically determined to be around 5pF. This time domain response is shown in Figure 58 below showing about 9 ns rise/fall times, corresponding to about 39 MHz for  $f_p$ . The overall supply current from the +5 V supply is around 5 mA with no load.

Figure 58. Converter Step Response (1V<sub>PP</sub>, 20 ns/DIV)

## 8.3 Printed Circuit Board Layout and Component Values Section

Generally, a good high frequency layout will keep power supply and ground traces away from the inverting input and output pins. Parasitic capacitances on these nodes to ground will cause frequency response peaking and possible circuit oscillations (see Application Note OA-15 (SNOA367) for more information). Texas Instruments suggests the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization:

| DEVICE     | PACKAGE      | EVALUATION BOARD PN |  |  |  |

|------------|--------------|---------------------|--|--|--|

| LMH6642QMF | 5-Pin SOT-23 | LMH730216           |  |  |  |

| LMH6643QMM | 8-Pin VSSOP  | LMH730123           |  |  |  |

Another important parameter in working with high speed/high performance amplifiers, is the component values selection. Choosing external resistors that are large in value will effect the closed loop behavior of the stage because of the interaction of these resistors with parasitic capacitances. These capacitors could be inherent to the device or a by-product of the board layout and component placement. Either way, keeping the resistor values lower, will diminish this interaction to a large extent. On the other hand, choosing very low value resistors could load down nodes and will contribute to higher overall power dissipation.

## 9 器件和文档支持

# 9.1 文档支持

## 9.1.1 相关文档

# 9.2 相关链接

以下表格列出了快速访问链接。 范围包括技术文档、支持与社区资源、工具和软件,并且可以快速访问样片或购买链接。

表 1. 相关链接

| 部件          | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|-------------|-------|-------|-------|-------|-------|

| LMH6642Q-Q1 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| LMH6643Q-Q1 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

## 9.3 商标

All trademarks are the property of their respective owners.

## 9.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

## 9.5 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

# 10 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                |              |              |

| LMH6642QMF/NOPB       | Active | Production    | SOT-23 (DBV)   5 | 1000   SMALL T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | A64Q         |

| LMH6642QMF/NOPB.A     | Active | Production    | SOT-23 (DBV)   5 | 1000   SMALL T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | A64Q         |

| LMH6642QMFX/NOPB      | Active | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | A64Q         |

| LMH6642QMFX/NOPB.A    | Active | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | A64Q         |

| LMH6643QMM/NOPB       | Active | Production    | VSSOP (DGK)   8  | 1000   SMALL T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | 643Q         |

| LMH6643QMM/NOPB.A     | Active | Production    | VSSOP (DGK)   8  | 1000   SMALL T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | 643Q         |

| LMH6643QMMX/NOPB      | Active | Production    | VSSOP (DGK)   8  | 3500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | 643Q         |

| LMH6643QMMX/NOPB.A    | Active | Production    | VSSOP (DGK)   8  | 3500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 85    | 643Q         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 23-May-2025

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-Aug-2025

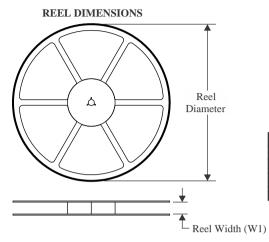

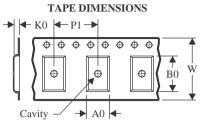

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

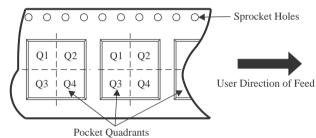

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMH6642QMF/NOPB  | SOT-23          | DBV                | 5 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMH6642QMFX/NOPB | SOT-23          | DBV                | 5 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMH6643QMM/NOPB  | VSSOP           | DGK                | 8 | 1000 | 177.8                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMH6643QMMX/NOPB | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 1-Aug-2025

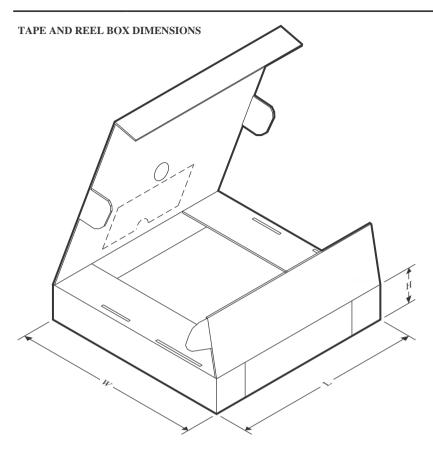

#### \*All dimensions are nominal

| 7 111 41111011010110 41 0 11011111141 |              |                 |      |      |             |            |             |

|---------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                                | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LMH6642QMF/NOPB                       | SOT-23       | DBV             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMH6642QMFX/NOPB                      | SOT-23       | DBV             | 5    | 3000 | 208.0       | 191.0      | 35.0        |

| LMH6643QMM/NOPB                       | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LMH6643QMMX/NOPB                      | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

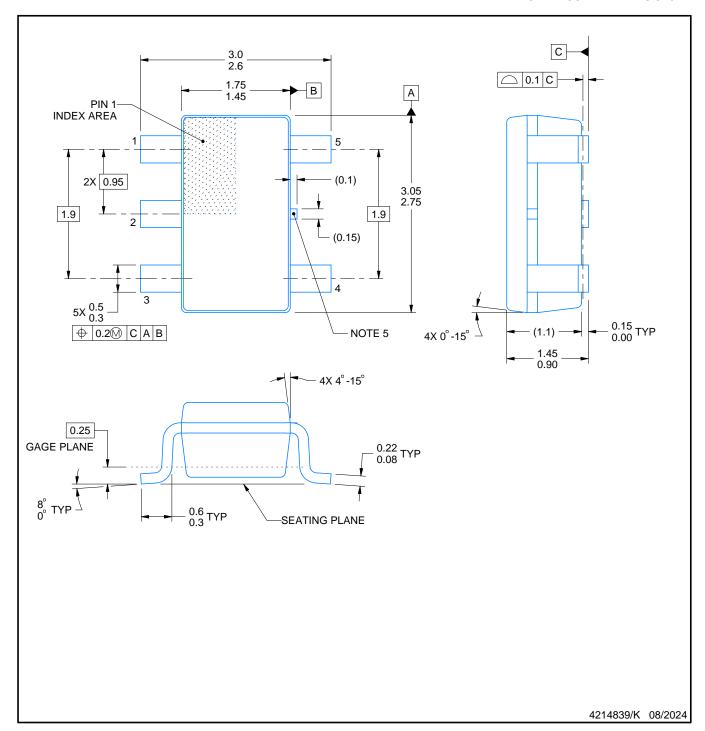

SMALL OUTLINE TRANSISTOR

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

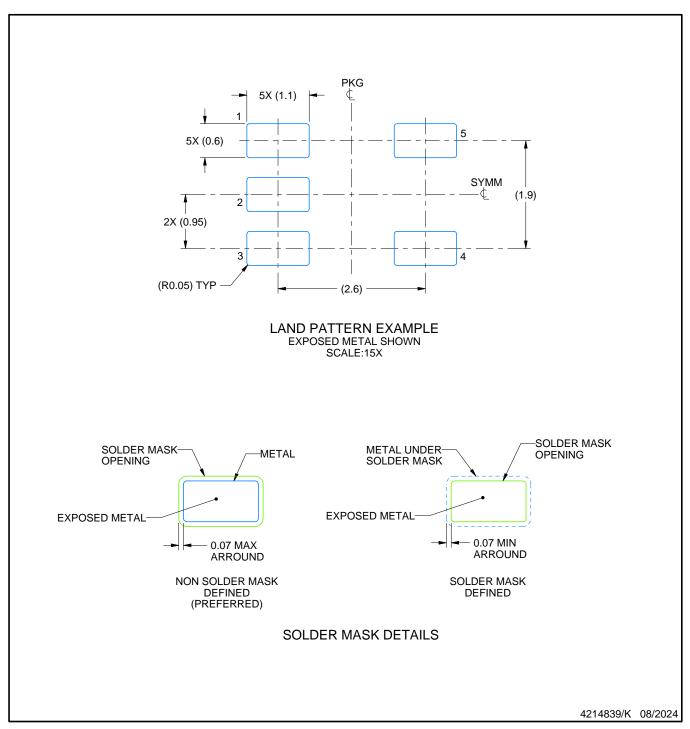

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

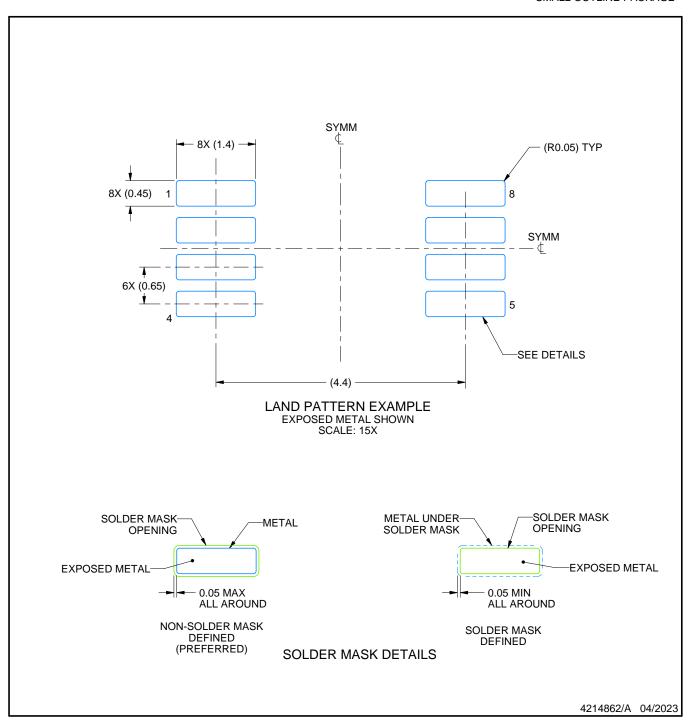

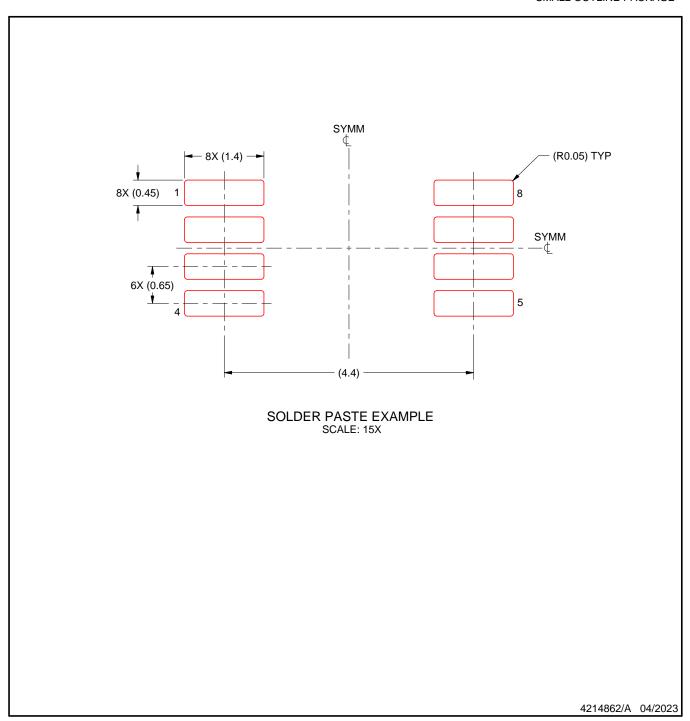

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

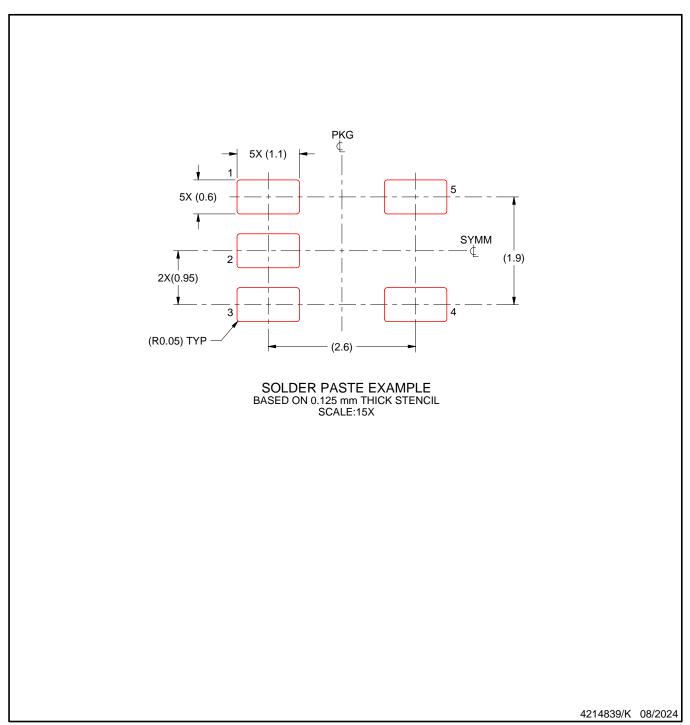

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

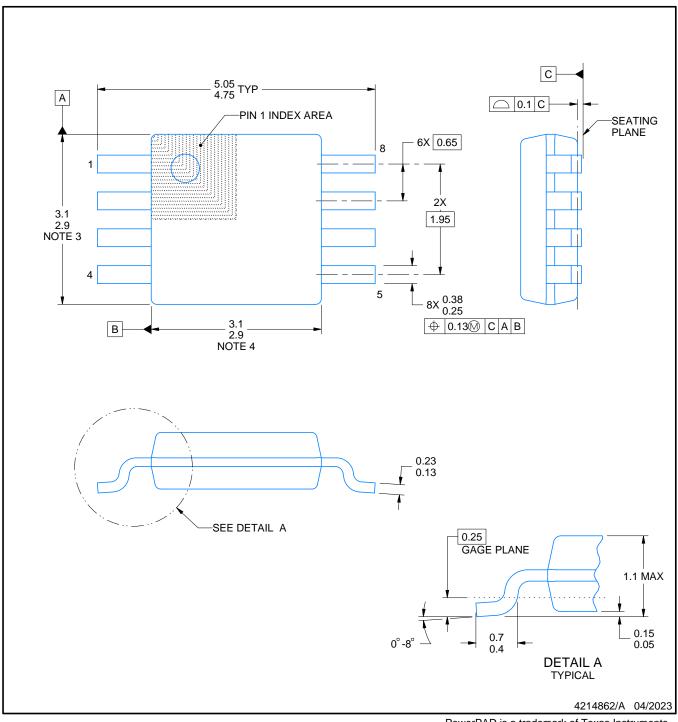

SMALL OUTLINE PACKAGE

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司