LMH1228

ZHCSKF4C -MARCH 2017-REVISED OCTOBER 2019

# 带集成时钟恢复器的 LMH1228 12G UHD-SDI 双路输出电缆驱动器

# 1 特性

- 支持 ST-2082-1 (12G)、ST-2081-1 (6G)、ST-424 (3G)、ST-292 (HD) 和 ST-259 (SD)

- 兼容 DVB-ASI 和 AES10 (MADI)

- 集成时钟恢复器锁定为 11.88Gbps、5.94Gbps、2.97Gbps、1.485Gbps 或 1.001 分频子速率和270Mbps 的 SMPTE 速率

- 集成眼图张开度监视器 (EOM)

- 双路差分输出电缆驱动器

- 片上 75Ω 终端和回损补偿网络

- 自适应 PCB 输入均衡器

- 时钟恢复型 100Ω 环回输出

- 75Ω 输出端的自动压摆率控制

- 75Ω 输出端的自动预加重和输出振幅

- 100Ω 输出端的可编程去加重功能和输出振幅

- 75Ω 和 100Ω 输出端的极性反转

- 没有输入信号时自动进入省电工作模式

- 功耗: 25mW (典型值)

- 通过使能引脚进行断电控制

- 2.5V 单电源

- 功耗: 305mW (典型值)

- 可通过引脚、SPI 或 SMBus 接口进行编程

- 工作温度范围: -40°C 至 +85°C

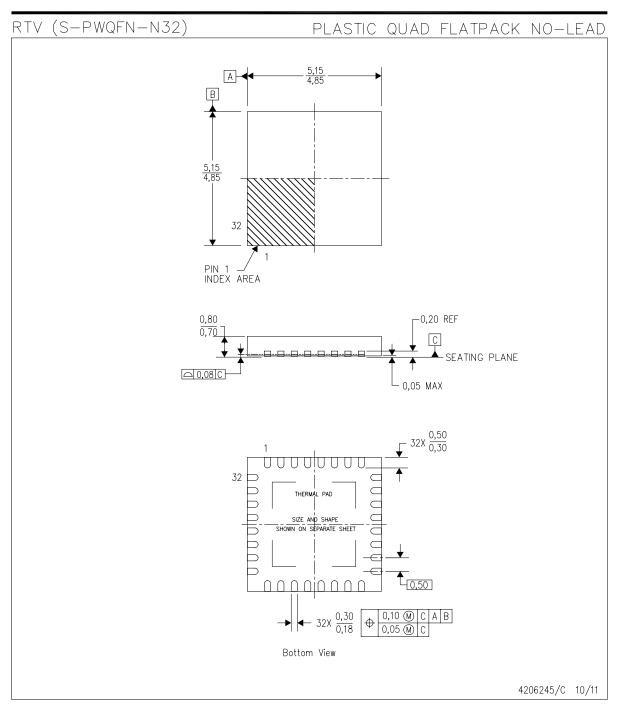

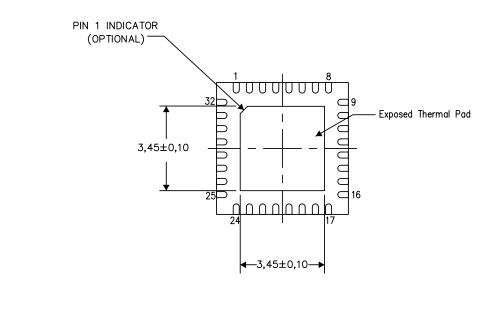

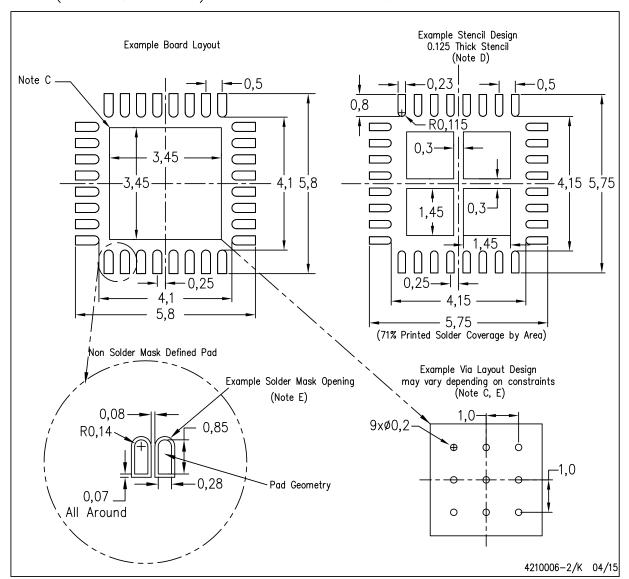

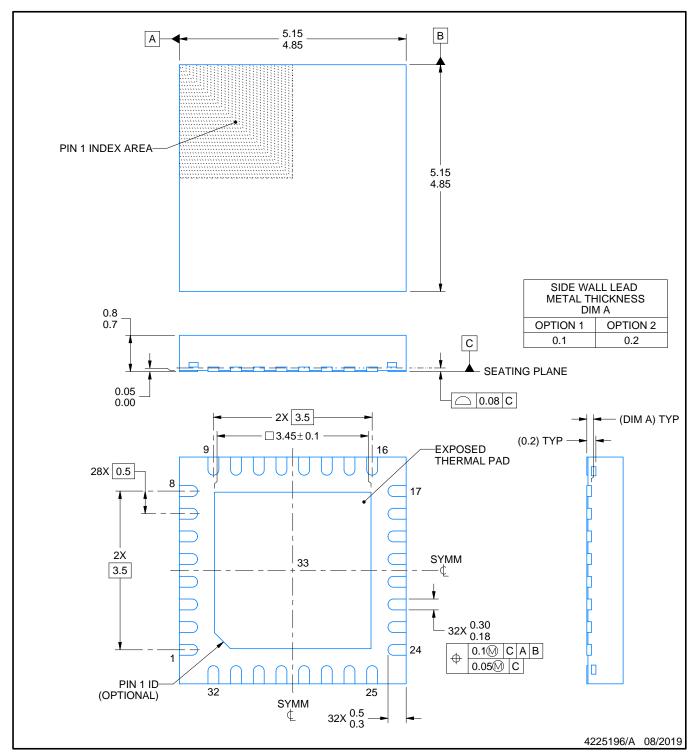

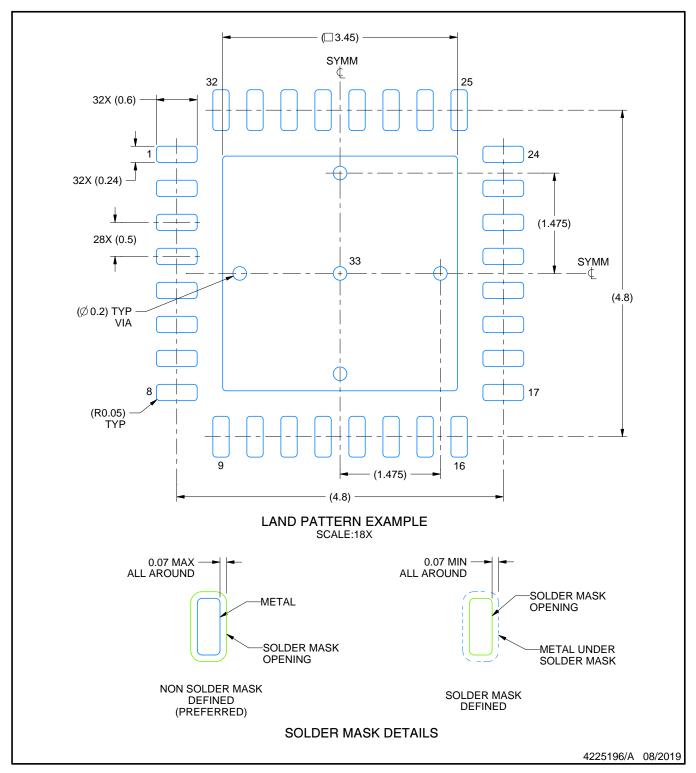

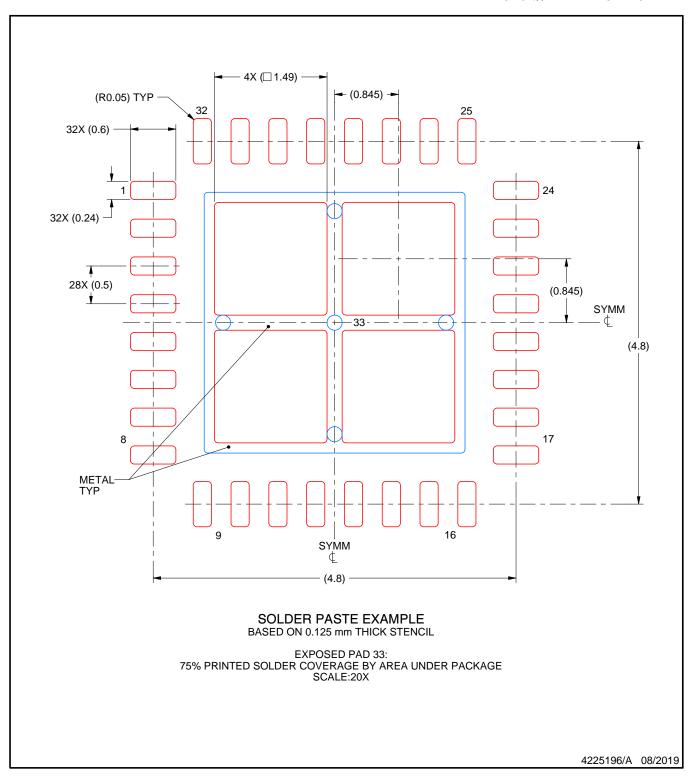

- 5mm x 5mm 32 引脚 WQFN 封装

#### 2 应用

- SMPTE 兼容串行数字接口

- UHDTV/4K/8K/HDTV/SDTV 视频

- 广播视频路由器、交换机、分配放大器和监视器

- 数字视频处理和编辑

# 3 说明

LMH1228 器件是一款带有时钟恢复器的 12G UHD-SDI 低功耗双路输出电缆驱动器。它支持高达 11.88Gbps 的 SMPTE 视频速率,因此可为 4K/8K 应用实现超高清视频的高度集成和高性能解决方案。时钟和数据恢复 (CDR) 电路多种多样,因此片上时钟恢复器可自动检测并锁定到高达 11.88Gbps 的各种 SMPTE 视频速率。主机端上的其他时钟恢复型 100Ω 驱动器输出可用于监控或信号分配用途。

片上时钟恢复器可减弱高频抖动并使用纯净的低抖动时钟完全重新生成数据。此时钟恢复器具有内置环路滤波器,且不需要任何输入参考时钟。LMH1228 还具有内部眼图张开度监视器和可编程引脚,可实现 CDR 锁定指示、输入信号检测或硬件干扰,从而为系统诊断和板启动提供支持。

LMH1228 由 2.5V 单电源供电运行。它采用小尺寸 5mm x 5mm 32 引脚 WQFN 封装。LMH1228 与 LMH1208(12G 双路电缆驱动器)引脚兼容。

### 器件信息(1)

| 器件型号 |         | 封装        | 封装尺寸 (标称值)      |

|------|---------|-----------|-----------------|

|      | LMH1228 | WQFN (32) | 5.00mm × 5.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

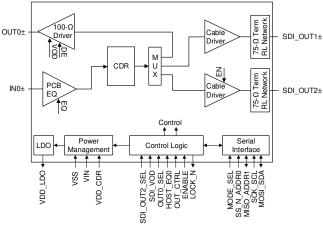

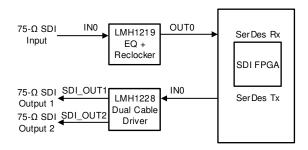

# 简化方框图

Copyright © 2016, Texas Instruments Incorporated

| 4 | k± kH                                      | 4  | 7.4 Device Functional Modes       |

|---|--------------------------------------------|----|-----------------------------------|

| 1 | 特性                                         |    | 7.4 Device i unctional wodes      |

| 2 | 应用                                         |    |                                   |

| 3 | 说明                                         |    |                                   |

| 4 | 修订历史记录                                     | 2  | 8.1 Application Information       |

| 5 | Pin Configuration and Functions            |    | 8.2 Typical Applications          |

| 6 | Specifications                             | 5  | 9 Power Supply Recommendations 34 |

|   | 6.1 Absolute Maximum Ratings               | 5  | 10 Layout 34                      |

|   | 6.2 ESD Ratings                            |    | 10.1 Layout Guidelines34          |

|   | 6.3 Recommended Operating Conditions       | 5  | 10.2 Layout Example               |

|   | 6.4 Thermal Information                    |    | <b>11</b> 器件和文档支持 37              |

|   | 6.5 Electrical Characteristics             | 6  | 11.1 文档支持 37                      |

|   | 6.6 Recommended SMBus Interface Timing     |    | 11.2 接收文档更新通知37                   |

|   | Specifications                             | 11 | 11.3 支持资源 37                      |

|   | 6.7 Serial Parallel Interface (SPI) Timing |    | 11.4 商标37                         |

|   | Specifications                             |    | 11.5 静电放电警告                       |

|   | 6.8 Typical Characteristics                | 14 | 11.6 出口管制提示37                     |

| 7 | Detailed Description                       | 15 | 11.7 Glossary37                   |

|   | 7.1 Overview                               | 15 | <b>12</b> 机械、封装和可订购信息37           |

|   | 7.2 Functional Block Diagram               | 15 | 12.1 Package Option Addendum      |

|   | 7.3 Feature Description                    | 16 |                                   |

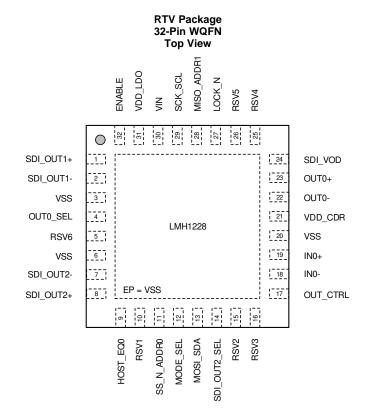

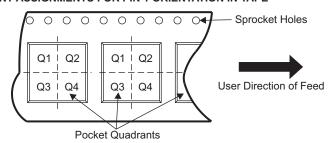

# 5 Pin Configuration and Functions

Copyright © 2016, Texas Instruments Incorporated

# **Pin Functions**

| PIN NAME NO.            |          | I/O <sup>(1)</sup>                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-------------------------|----------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                         |          | 1/0 ( /                                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| HIGH-SPEED DIFF         | ERENTIAL | I/OS                                                                                                      |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

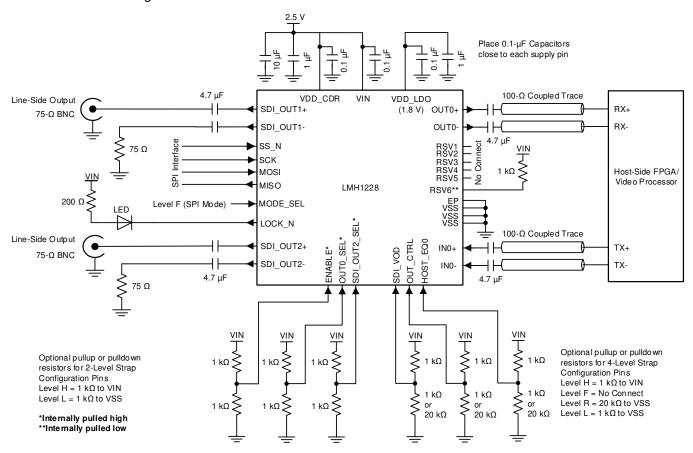

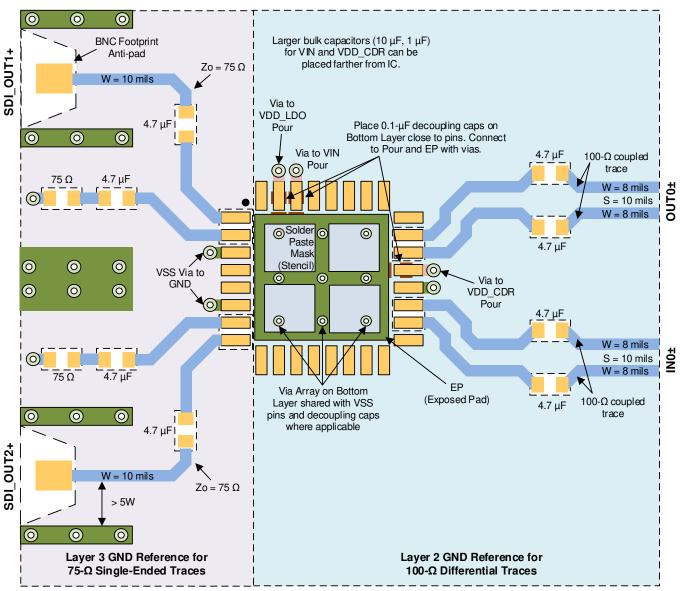

| SDI_OUT1+ 1 I/O, Analog |          | I/O, Analog                                                                                               | Single-ended complementary outputs with on-chip 75-Ω termination at SDI_OUT1+ and SDI_OUT1                                                                                                                                                                                                                                                        |  |  |  |  |

| SDI_OUT1-               | 2        | I/O, Analog                                                                                               | SDI_OUT1± include integrated return loss networks designed to meet the SMPTE output return loss requirements. Connect SDI_OUT1+ to a BNC through a 4.7-μF, AC-coupling capacitor. SDI_OUT1- should be similarly AC-coupled and terminated with an external 4.7-μF capacitor and 75-Ω resistor to GND.                                             |  |  |  |  |

| SDI_OUT2+               | 8        | O, Analog                                                                                                 | Single-ended complementary outputs with on-chip 75-Ω termination at SDI_OUT2+ and SDI_OUT2                                                                                                                                                                                                                                                        |  |  |  |  |

| SDI_OUT2- 7             |          | O, Analog                                                                                                 | SDI_OUT2± include integrated return loss networks designed to meet the SMPTE output return loss requirements. SDI_OUT2± is used as a second cable driver. Connect SDI_OUT2+ to a BNC through a 4.7-μF, AC-coupling capacitor. SDI_OUT2- should be similarly AC-coupled and terminated with an external 4.7-μF capacitor and 75-Ω resistor to GND. |  |  |  |  |

| IN0+                    | 19       | I, Analog Differential inputs from host video processor. On-chip 100-Ω differential termination. Requires |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| INO-                    | 18       | I, Analog                                                                                                 | 4.7-μF, AC-coupling capacitors for SMPTE applications.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| OUT0+                   | 23       | O, Analog                                                                                                 | Differential outputs to host video processor. On-chip 100-Ω differential termination. Requires external 4.7-                                                                                                                                                                                                                                      |  |  |  |  |

| OUT0-                   | 22       | O, Analog                                                                                                 | μF, AC-coupling capacitors for SMPTE applications.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CONTROL PINS            |          |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| OUT0_SEL                | 4        | I, LVCMOS                                                                                                 | OUT0_SEL enables the use of the 100-Ω host-side output driver at OUT0±. See Table 2 for details.  OUT0_SEL is internally pulled high by default (OUT0 disabled).                                                                                                                                                                                  |  |  |  |  |

| HOST_EQ0                | 9        | I, 4-LEVEL                                                                                                | HOST_EQ0 selects the equalizer setting for IN0±. See Table 4 for details.                                                                                                                                                                                                                                                                         |  |  |  |  |

| MODE_SEL                | 12       | I, 4-LEVEL                                                                                                | MODE_SEL enables the SPI or SMBus serial control interface.<br>See Table 9 for details.                                                                                                                                                                                                                                                           |  |  |  |  |

| SDI_OUT2_SEL            | 14       | I, LVCMOS                                                                                                 | SDI_OUT2_SEL enables the use of the 75-Ω output driver at SDI_OUT2±. See Table 2 for details. SDI_OUT2_SEL is internally pulled high by default (SDI_OUT2 disabled).                                                                                                                                                                              |  |  |  |  |

(1) I = Input, O = Output, I/O = Input or Output, OD = Open Drain, LVCMOS = 2-State Logic, 4-LEVEL = 4-State Logic

# Pin Functions (continued)

| PIN                                  |                            | (1)                |                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|--------------------------------------|----------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                 | NO.                        | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OUT_CTRL                             | 17                         | I, 4-LEVEL         | OUT_CTRL selects the signal being routed to the output. It is used to enable or bypass the reclocker. See Table 6 for details.                                                                                                                                                                                                                                         |  |  |

| SDI_VOD                              | 24                         | I, 4-LEVEL         | SDI_VOD selects one of four output amplitudes for the cable drivers at SDI_OUT1± and SDI_OUT2±. See Table 7 for details.                                                                                                                                                                                                                                               |  |  |

| LOCK_N                               | 27                         | O, LVCMOS,<br>OD   | LOCK_N is the reclocker lock indicator. LOCK_N is pulled low when the reclocker has acquired lock condition. LOCK_N is a 3.3-V tolerant, open-drain output. It requires an external resistor to a logic supply. LOCK_N can be reconfigured to indicate Signal Detector (SD_N) or Interrupt (INT_N) through register programming. See Status Indicators and Interrupts. |  |  |

| ENABLE                               | 32                         | I, LVCMOS          | A logic-high at ENABLE enables normal operation for the LMH1228. A logic-low at ENABLE places the LMH1228 in Power-Down Mode. ENABLE is internally pulled high by default.                                                                                                                                                                                             |  |  |

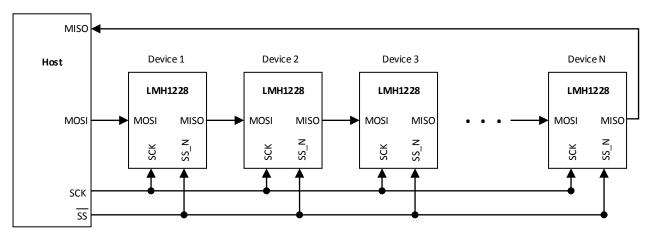

| SPI SERIAL CON                       | TROL INTER                 | FACE, MODE_SEL     | = F (FLOAT)                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SS_N                                 | 11                         | I, LVCMOS          | SS_N is the Slave Select. When SS_N is at logic Low, it enables SPI access to the LMH1228 slave device. SS_N is a 2.5-V LVCMOS input and is internally pulled high by default.                                                                                                                                                                                         |  |  |

| MOSI                                 | 13                         | I, LVCMOS          | MOSI is the SPI serial control data input to the LMH1228 slave device when the SPI bus is enabled.  MOSI is a 2.5-V LVCMOS input.  An external pullup resistor is recommended.                                                                                                                                                                                         |  |  |

| MISO                                 | 28                         | O, LVCMOS          | MISO is the SPI serial control data output from the LMH1228 slave device. MISO is a 2.5-V LVCMOS output.                                                                                                                                                                                                                                                               |  |  |

| SCK                                  | 29                         | I, LVCMOS          | SCK is the SPI serial input clock to the LMH1228 slave device when the SPI interface is enabled. SCK is a 2.5-V LVCMOS input.  An external pullup resistor is recommended.                                                                                                                                                                                             |  |  |

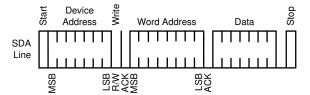

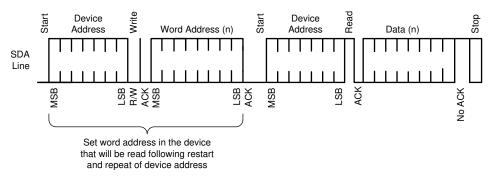

| SMBUS SERIAL                         | CONTROL IN                 | TERFACE, MODE_S    | SEL = L (1 K $\Omega$ TO VSS)                                                                                                                                                                                                                                                                                                                                          |  |  |

| ADDR0                                | 11                         | Strap, 4-LEVEL     | ADDR[1:0] are 4-level straps, read into the device at power up. They are used to select one of the 16 supported SMBus addresses when SMBus is enabled. See Table 10 for details.                                                                                                                                                                                       |  |  |

| SDA                                  | 13                         | I/O, LVCMOS,<br>OD | SDA is the SMBus bidirectional data line to or from the LMH1228 slave device when SMBus is enabled. SDA is an open-drain I/O and requires an external pullup resistor to the SMBus termination voltage. SDA is 3.3-V tolerant.                                                                                                                                         |  |  |

| ADDR1                                | 28                         | Strap, 4-LEVEL     | ADDR[1:0] are 4-level straps, read into the device at power up. They are used to select one of the 16 supported SMBus addresses when SMBus is enabled. See Table 10 for details.                                                                                                                                                                                       |  |  |

| SCL                                  | 29                         | I/O, LVCMOS,<br>OD | SCL is the SMBus input clock to the LMH1228 slave device when SMBus is enabled. It is driven by a LVCMOS open-drain driver from the SMBus master. SCL requires an external pullup resistor to the SMBus termination voltage. SCL is 3.3-V tolerant.                                                                                                                    |  |  |

| RESERVED                             |                            |                    |                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| RSV1<br>RSV2<br>RSV3<br>RSV4<br>RSV5 | 10<br>15<br>16<br>25<br>26 | _                  | Reserved pins. Do not connect.                                                                                                                                                                                                                                                                                                                                         |  |  |

| RSV6                                 | 5                          | I, LVCMOS          | Reserved pin. This input must be tied high with 1-k $\Omega$ resistor to VIN. Alternatively, this pin setting can be overridden by register control. Refer to the <i>LMH1228 and LMH1208 Programming Guide</i> (SNAU206) for more details.                                                                                                                             |  |  |

| POWER                                | *                          |                    | •                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| VSS                                  | 3, 6, 20                   | I, Ground          | Ground reference.                                                                                                                                                                                                                                                                                                                                                      |  |  |

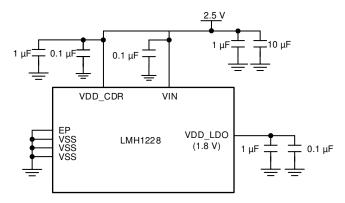

| VDD_CDR                              | 21                         | I, Power           | VDD_CDR powers the reclocker circuitry. It is connected to the same 2.5-V ± 5% supply as VIN.                                                                                                                                                                                                                                                                          |  |  |

| VIN                                  | 30                         | I, Power           | VIN is connected to an external 2.5-V ± 5% power supply.                                                                                                                                                                                                                                                                                                               |  |  |

| VDD_LDO                              | 31                         | O, Power           | VDD_LDO is the output of the internal 1.8-V LDO regulator. VDD_LDO output requires an external 1-μF and 0.1-μF bypass capacitor to VSS. The internal LDO is designed to power internal circuitry only.                                                                                                                                                                 |  |  |

| EP                                   | _                          | I, Ground          | EP is the exposed pad at the bottom of the RTV package. The exposed pad should be connected to the VSS plane through a $3 \times 3$ via array.                                                                                                                                                                                                                         |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                     | MIN  | MAX  | UNIT |

|---------------------------------------------------------------------|------|------|------|

| Supply voltage (VIN, VDD_CDR)                                       | -0.5 | 2.75 | V    |

| Input voltage for 4-level pins                                      | -0.5 | 2.75 | V    |

| Input/output voltage for 2-level control pins                       | -0.5 | 2.75 | V    |

| SMBus input/output voltage (SDA, SCL)                               | -0.5 | 4    | V    |

| SPI input/output voltage (SS_N, MISO, MOSI, and SCK)                | -0.5 | 2.75 | V    |

| High-speed input/output voltage (IN0±, SDI_OUT1±, OUT0±, SDI_OUT2±) | -0.5 | 2.75 | V    |

| Input current (IN0±)                                                | -30  | 30   | mA   |

| Operating junction temperature                                      |      | 125  | °C   |

| Storage temperature, T <sub>stg</sub>                               | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |           |                                                           | All pins except 13 and 29 | ±6000 |   |

|--------------------|-----------|-----------------------------------------------------------|---------------------------|-------|---|

| V <sub>(ESD)</sub> | discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)    | Pins 13 and 29            | ±5500 | V |

| · (L3D)            |           | Charged-device model (CDM), per JEDEC specification JESD2 | ±1500                     |       |   |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

### 6.3 Recommended Operating Conditions

|                         |                                      |                                    | MIN   | NOM  | MAX   | UNIT  |

|-------------------------|--------------------------------------|------------------------------------|-------|------|-------|-------|

|                         | Supply voltage                       | VIN, VDD_CDR to VSS                | 2.375 | 2.5  | 2.625 | V     |

| VDD <sub>SMBUS</sub>    | SMBus: SDA, SCL open-drain to        | ermination voltage                 | 2.375 |      | 3.6   | V     |

| V                       | Source differential launch amplitude | Before 5-inch board trace to IN0±  | 300   |      | 850   | mVp-p |

| V <sub>IN0_LAUNCH</sub> |                                      | Before 20-inch board trace to IN0± | 650   |      | 1000  |       |

| T <sub>JUNCTION</sub>   | Operating junction temperature       |                                    |       |      | 110   | °C    |

| T <sub>AMBIENT</sub>    | Ambient temperature                  |                                    | -40   | 25   | 85    | °C    |

| NIT                     | Maximum supply noise <sup>(1)</sup>  | 50 Hz to 1 MHz, sinusoidal         |       | < 20 |       | mVp-p |

| NTps <sub>max</sub>     |                                      | 1.1 MHz to 50 MHz, sinusoidal      |       | < 10 |       |       |

<sup>(1)</sup> The sum of the DC supply voltage and AC supply noise should not exceed the recommended supply voltage range.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 6.4 Thermal Information

|                        |                                              | LMH1228    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RTV (WQFN) | UNIT |

|                        |                                              | 32 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 32.5       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 15.0       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.5        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.5        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

|                     | PARAMETER                                                                                                         | TEST CONDITIONS                                           | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| POWER               |                                                                                                                   |                                                           |     |     |     |      |

|                     |                                                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± disabled |     | 305 |     | mW   |

| PD                  | Power dissipation,<br>Measured with PRBS10,                                                                       | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± enabled  |     | 350 |     | mW   |

| PD                  | CDR Locked to 11.88 Gbps,<br>VOD = default,<br>HEO/VEO lock monitor disabled                                      | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± disabled  |     | 442 |     | mW   |

|                     |                                                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± enabled   |     | 485 |     | mW   |

| $PD_Z$              | Power dissipation, Power Save Mode                                                                                | Power Save Mode,<br>ENABLE = H, no signal applied at IN0± |     | 25  |     | mW   |

|                     | Current consumption, Measured with PRBS10, CDR Locked to 11.88 Gbps, VOD = default, HEO/VEO lock monitor disabled | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± disabled |     | 122 | 146 | mA   |

| DD                  |                                                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± enabled  |     | 140 | 166 | mA   |

| טט                  |                                                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± disabled  |     | 177 | 211 | mA   |

|                     |                                                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± enabled   |     | 194 | 230 | mA   |

| IDD <sub>Z</sub>    | Current consumption, Power Save Mode                                                                              | Power Save Mode,<br>ENABLE = H, no signal applied at IN0± |     | 10  |     | mA   |

| IDD <sub>Z_PD</sub> | Current consumption, Power-Down Mode                                                                              | Power-Down Mode,<br>ENABLE = L, no signal applied at IN0± |     | 10  | 30  | mA   |

|                      | PARAMETER                                               | TEST CONDITIONS                                                                 | MIN           | TYP MAX                                                               | UNIT |

|----------------------|---------------------------------------------------------|---------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------|------|

|                      |                                                         | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± disabled                       |               | 200                                                                   | mA   |

| IDD                  | Current consumption, CDR acquiring lock to 11.88        | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± enabled                        |               | 225                                                                   | mA   |

| IDD <sub>TRANS</sub> | Gbps,<br>VOD = default,<br>HEO/VEO lock monitor enabled | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± disabled                        |               | 271                                                                   | mA   |

|                      |                                                         | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± enabled                         |               | 290                                                                   | mA   |

| LVCMOS DC            | SPECIFICATIONS                                          |                                                                                 |               |                                                                       |      |

| V <sub>a</sub> .     | Logic high input voltage                                | 2-level input (SS_N, SCK, MOSI, SDI_OUT2_SEL, OUT0_SEL, ENABLE)                 | 0.72 ×<br>VIN | VIN +<br>0.3                                                          | ٧    |

| V <sub>IH</sub>      | Logic high input voltage                                | 2-level input (SCL, SDA)                                                        | 0.7 ×<br>VIN  | 3.6                                                                   | V    |

| V <sub>IL</sub>      | Logic low input voltage                                 | 2-level input (SS_N, SCK, MOSI,<br>SDI_OUT2_SEL, OUT0_SEL, ENABLE,<br>SCL, SDA) | 0             | 0.3 ×<br>VIN                                                          | V    |

| V <sub>OH</sub>      | Logic high output voltage                               | IOH = -2 mA, (MISO)                                                             | 0.8 ×<br>VIN  | VIN                                                                   | V    |

| V <sub>OL</sub>      | Logic low output voltage                                | IOL = 2 mA, (MISO)                                                              | 0             | 0.2 ×<br>VIN                                                          | ٧    |

|                      |                                                         | IOL = 3 mA, (LOCK_N, SDA)                                                       |               | 0.4                                                                   | ٧    |

|                      |                                                         | LVCMOS (SDI_OUT2_SEL, ENABLE)                                                   |               | 271 290  VIN + 0.3 3.6  0.3 × VIN  VIN  0.2 × VIN  0.4 15 65 10 15 10 | μΑ   |

|                      | Input high lookage current                              | LVCMOS (OUT0_SEL)                                                               |               | 65                                                                    | μΑ   |

| I <sub>IH</sub>      | Input high leakage current (Vinput = VIN)               | LVCMOS (LOCK_N)                                                                 |               | 10                                                                    | μΑ   |

|                      | ,                                                       | SPI mode: LVCMOS (SS_N, SCK, MOSI)                                              |               | 15                                                                    | μA   |

|                      |                                                         | SMBus mode: LVCMOS (SCL, SDA)                                                   |               | 10                                                                    | μA   |

|                      |                                                         | LVCMOS (SDI_OUT2_SEL, ENABLE)                                                   | -50           |                                                                       | μA   |

|                      |                                                         | LVCMOS (OUT0_SEL)                                                               | -15           |                                                                       | μΑ   |

| I <sub>IL</sub>      | Input low leakage current                               | LVCMOS (LOCK_N)                                                                 | -10           |                                                                       | μΑ   |

| IL                   | (Vinput = GND)                                          | SPI mode: LVCMOS (SCK, MOSI)                                                    | -15           |                                                                       | μΑ   |

|                      |                                                         | SPI mode: LVCMOS (SS_N)                                                         | -50           |                                                                       | μΑ   |

|                      |                                                         | SMBus mode: LVCMOS (SCL, SDA)                                                   | -10           |                                                                       | μΑ   |

|                         | PARAMETER                                                     | TEST CONDITIONS                                                                                                                         | MIN  | TYP          | MAX | UNIT  |

|-------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-----|-------|

| 4-LEVEL LOGI            | IC DC SPECIFICATIONS (APPLY T                                 | O ALL 4-LEVEL INPUT CONTROL PINS)                                                                                                       |      |              |     |       |

| V <sub>LVL_H</sub>      | LEVEL-H input voltage                                         | Measured voltage at 4-level pin with external 1 kΩ to VIN                                                                               |      | VIN          |     | ٧     |

| $V_{LVL_{F}}$           | LEVEL-F default voltage                                       | Measured voltage 4-level pin at default                                                                                                 |      | 2/3 ×<br>VIN |     | V     |

| V <sub>LVL_R</sub>      | LEVEL-R input voltage                                         | Measured voltage at 4-level pin with external 20 kΩ to VSS                                                                              |      | 1/3 ×<br>VIN |     | V     |

| V <sub>LVL_L</sub>      | LEVEL-L input voltage                                         | Measured voltage at 4-level pin with external 1 kΩ to VSS                                                                               |      | 0            |     | V     |

| I <sub>IH</sub>         | Input high leakage current                                    | 4-levels (HOST_EQ0, MODE_SEL,<br>OUT_CTRL, SDI_VOD)                                                                                     | 20   | 45           | 80  | μA    |

| -111                    | (Vinput = VIN)                                                | SMBus mode: 4-levels (ADDR0, ADDR1)                                                                                                     | 20   | 45           | 80  | μA    |

| I <sub>IL</sub>         | Input low leakage current                                     | 4-levels (HOST_EQ0, MODE_SEL,<br>OUT_CTRL, SDI_VOD)                                                                                     | -160 | -93          | -40 | μΑ    |

|                         | (Vinput = GND)                                                | SMBus mode: 4-levels (ADDR0, ADDR1)                                                                                                     | -160 | -93          | -40 | μΑ    |

| RECEIVER SP             | ECIFICATIONS (IN0±)                                           |                                                                                                                                         |      |              |     |       |

| R <sub>IN0_TERM</sub>   | DC input differential termination                             | Measured across IN0+ to IN0-                                                                                                            | 80   | 100          | 120 | Ω     |

|                         |                                                               | SDD11, 10 MHz – 2.8 GHz                                                                                                                 |      | -22          |     | dB    |

| RL <sub>IN0_SDD11</sub> | Input differential return loss (1)                            | SDD11, 2.8 GHz – 6 GHz                                                                                                                  |      | -16          |     | dB    |

|                         |                                                               | SDD11, 6 GHz – 11.1 GHz                                                                                                                 |      | -10          |     | dB    |

| RL <sub>IN0_SCD11</sub> | Differential to common-mode input conversion <sup>(1)</sup>   | SCD11, 10 MHz to 11.1 GHz                                                                                                               |      | -21          |     | dB    |

| V <sub>IN0_CM</sub>     | DC common-mode voltage                                        | Input common-mode voltage at IN0+ or IN0- to GND                                                                                        |      | 2.06         |     | V     |

| CD <sub>ON_IN0</sub>    | Signal detect (default) Assert ON threshold level for IN0±    | 11.88 Gbps, EQ and PLL pathological pattern                                                                                             |      | 20           |     | mVp-p |

| CD <sub>OFF_IN0</sub>   | Signal detect (default) Deassert OFF threshold level for IN0± | 11.88 Gbps, EQ and PLL pathological pattern                                                                                             |      | 18           |     | mVp-p |

| DRIVER OUTP             | PUT (SDI_OUT1+ AND SDI_OUT2+)                                 |                                                                                                                                         |      |              |     |       |

| R <sub>OUT_TERM</sub>   | DC output single-ended termination                            | SDI_OUT1+ and SDI_OUT1-,<br>SDI_OUT2+ and SDI_OUT2- to VIN                                                                              | 63   | 75           | 87  | Ω     |

| VOD                     | Output single-ended output                                    | Measure AC signal at SDI_OUT1+ and SDI_OUT2+, with SDI_OUT1- and SDI_OUT2- AC terminated with 75 $\Omega$ SDI_VOD = H                   |      | 840          |     | mVp-p |

| VOD <sub>CD_OUTP</sub>  | voltage                                                       | SDI_VOD = F                                                                                                                             | 720  | 800          | 880 | mVp-p |

|                         |                                                               | SDI_VOD = R                                                                                                                             |      | 880          |     | mVp-p |

|                         |                                                               | SDI_VOD = L                                                                                                                             |      | 760          |     | mVp-p |

| VOD                     | Output single-ended output                                    | Measure AC signal at SDI_OUT1- and SDI_OUT2-, with SDI_OUT1+ and SDI_OUT2+ AC terminated with 75 $\Omega$ SDI_VOD = H                   |      | 840          |     | mVp-p |

| VOD <sub>CD_OUTN</sub>  | voltage                                                       | SDI_VOD = F                                                                                                                             | 720  | 800          | 880 | mVp-p |

|                         |                                                               | SDI_VOD = R                                                                                                                             |      | 880          |     | mVp-p |

|                         |                                                               | SDI_VOD = L                                                                                                                             |      | 760          |     | mVp-p |

| PRE <sub>CD_OUTP</sub>  | Output pre-emphasis                                           | Output pre-emphasis boost amplitude at SDI_OUT1+ and SDI_OUT2+, programmed to maximum setting through register, measured at SDI_VOD = F |      | 2            |     | dB    |

<sup>(1)</sup> This parameter is measured with the LMH1297EVM (Evaluation board for LMH1228).

|                        | PARAMETER                                              | TEST CONDITIONS                                                                                                                         | MIN | TYP  | MAX                                           | UNIT |

|------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----------------------------------------------|------|

| PRE <sub>CD_OUTN</sub> | Output pre-emphasis                                    | Output pre-emphasis boost amplitude at SDI_OUT1- and SDI_OUT2-, programmed to maximum setting through register, measured at SDI_VOD = F |     | 2    |                                               | dB   |

|                        |                                                        | Measured with PRBS10 pattern, default VOD at 20% – 80% amplitude, default preemphasis enabled 11.88 Gbps                                |     | 34   | 42                                            | ps   |

| t <sub>R_F_SDI</sub>   | Output rise and fall time <sup>(1)</sup>               | 5.94 Gbps                                                                                                                               |     | 36   | 43                                            | ps   |

|                        |                                                        | 2.97 Gbps                                                                                                                               |     | 59   | 67                                            | ps   |

|                        |                                                        | 1.485 Gbps                                                                                                                              |     | 60   | 73                                            | ps   |

|                        |                                                        | 270 Mbps                                                                                                                                | 400 | 550  | 700                                           | ps   |

|                        |                                                        | Measured with PRBS10 pattern, default<br>VOD at 20% – 80% amplitude, default pre-<br>emphasis enabled<br>11.88 Gbps                     |     | 3    | 18                                            | ps   |

| t <sub>R_F_DELTA</sub> | Output rise and fall time mismatch (1)                 | 5.94 Gbps                                                                                                                               |     | 2.7  | 12                                            | ps   |

|                        | monacon                                                | 2.97 Gbps                                                                                                                               |     | 0.8  | 11                                            | ps   |

|                        |                                                        | 1.485 Gbps                                                                                                                              |     | 0.8  | 12                                            | ps   |

|                        |                                                        | 270 Mbps                                                                                                                                |     | 72   | 150                                           | ps   |

| V <sub>OVERSHOOT</sub> | Output overshoot or undershoot                         | Measured with PRBS10 pattern, default VOD, default pre-emphasis enabled (2) 12G/6G/3G/HD/SD                                             |     | 5%   |                                               |      |

| $V_{DC\_OFFSET}$       | DC offset                                              | 12G/6G/3G/HD/SD                                                                                                                         |     | ±0.2 |                                               | V    |

| V <sub>DC_WANDER</sub> | DC wander                                              | 12G/6G/3G/HD/SD with EQ pathological pattern                                                                                            |     | 20   |                                               | mV   |

|                        |                                                        | S22, 5 MHz to 1.485 GHz                                                                                                                 |     | -25  |                                               | dB   |

| DI                     | Output return loss at                                  | S22, 1.485 GHz to 3 GHz                                                                                                                 |     | -22  |                                               | dB   |

| RL <sub>CD_S22</sub>   | SDI_OUT1+ and SDI_OUT2+ reference to 75 $\Omega^{(1)}$ | S22, 3 GHz to 6 GHz                                                                                                                     |     | -12  |                                               | dB   |

| ı                      |                                                        | S22, 6 GHz to 12 GHz                                                                                                                    |     | -8   | 43<br>67<br>73<br>700<br>18<br>12<br>11<br>12 | dB   |

|                        |                                                        |                                                                                                                                         |     |      |                                               |      |

<sup>(2)</sup> V<sub>OVERSHOOT</sub> overshoot/undershoot maximum measurements are largely affected by the PCB layout and input test pattern. The maximum value specified in *Electrical Characteristics* for V<sub>OVERSHOOT</sub> is based on bench evaluation across temperature and supply voltages with the LMH1297EVM.

|                                | PARAMETER                                      | TEST CONDITIONS                                                                                 | MIN          | TYP    | MAX  | UNIT     |

|--------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------|--------|------|----------|

| DRIVER OUTP                    | UT (OUT0±)                                     |                                                                                                 |              |        |      |          |

| R <sub>OUT0_TERM</sub>         | DC output differential termination             | Measured across OUT0+ and OUT0-                                                                 | 80           | 100    | 120  | Ω        |

|                                |                                                | Measured with 8T pattern<br>HOST_EQ0 = H                                                        |              | 410    |      | mVp-p    |

| VOD <sub>OUT0</sub>            | Output differential voltage at OUT0±           | HOST_EQ0 = F                                                                                    | 485          | 560    | 620  | mVp-p    |

|                                | 0010±                                          | HOST_EQ0 = R                                                                                    |              | 635    |      | mVp-p    |

|                                |                                                | HOST_EQ0 = L                                                                                    |              | 810    |      | mVp-p    |

|                                |                                                | Measured with 8T pattern<br>HOST_EQ0 = H                                                        |              | 410    |      | mVp-p    |

| VOD <sub>OUT0_DE</sub>         | De-emphasized output                           | HOST_EQ0 = F                                                                                    |              | 550    |      | mVp-p    |

| 0010_52                        | differential voltage at OUT0±                  | HOST_EQ0 = R                                                                                    |              | 545    |      | mVp-p    |

|                                |                                                | HOST_EQ0 = L                                                                                    |              | 532    |      | mVp-p    |

| t <sub>R</sub> /t <sub>F</sub> | Output rise and fall time                      | Measured with 8T Pattern, 20% – 80% amplitude                                                   |              | 45     |      | ps       |

| RL <sub>OUT0-SDD22</sub>       | Output differential return loss <sup>(1)</sup> | Measured with the device powered up and outputs a 10-MHz clock signal SDD22, 10 MHz – 2.8 GHz   |              | -24    |      | dB       |

| N=0010-SDD22                   |                                                | SDD22, 2.8 GHz – 6 GHz                                                                          |              | -16    |      | dB       |

|                                |                                                | SDD22, 6 GHz – 11.1 GHz                                                                         |              | -15    |      | dB       |

| RL <sub>OUT0-SCC22</sub>       | Output common-mode return loss <sup>(1)</sup>  | Measured with the device powered up and outputs a 10-MHz clock signal. SCC22, 10 MHz – 4.75 GHz |              | -12    |      | dB       |

|                                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,        | SCC22, 4.75 GHz – 11.1 GHz                                                                      |              | -9     |      | dB       |

| V <sub>OUT0_CM</sub>           | AC common-mode voltage on OUT0± <sup>(1)</sup> | Default setting, PRBS31, 11.88 Gbps                                                             |              | 8      |      | mV (rms) |

| RECLOCKER C                    | OUTPUT JITTER                                  |                                                                                                 |              |        |      |          |

| AJ <sub>CD</sub>               | Alignment jitter <sup>(1)</sup>                | Measured at SDI_OUT1+ and SDI_OUT2+,<br>OUT0± disabled<br>PRBS10, 3G/HD/SD12G/6G/3G/HD/SD       |              | 0.1    | 0.14 | UI       |

| TMJ <sub>CD</sub>              | Timing jitter <sup>(1)</sup>                   | Measured at SDI_OUT1+ and SDI_OUT2+,<br>OUT0± disabled<br>PRBS10, 12G/6G/3G/HD/SD               |              | 0.45   |      | UI       |

| RECLOCKER S                    | SPECIFICATIONS                                 |                                                                                                 |              |        |      |          |

|                                |                                                | SMPTE 12G, /1                                                                                   |              | 11.88  |      | Gbps     |

|                                |                                                | SMPTE 12G, /1.001                                                                               |              | 11.868 |      | Gbps     |

|                                |                                                | SMPTE 6G, /1                                                                                    | <del> </del> | 5.94   |      | Gbps     |

|                                |                                                | SMPTE 6G, /1.001                                                                                |              | 5.934  |      | Gbps     |

| LOCK <sub>RATE</sub>           | Reclocker lock data rates                      | SMPTE 3G, /1                                                                                    |              | 2.97   |      | Gbps     |

|                                |                                                | SMPTE 3G, /1.001                                                                                |              | 2.967  |      | Gbps     |

|                                |                                                | SMPTE HD, /1                                                                                    |              | 1.485  |      | Gbps     |

|                                |                                                | SMPTE HD, /1.001                                                                                | <del> </del> | 1.4835 |      | Gbps     |

|                                |                                                | SMPTE SD, /1                                                                                    |              | 270    |      | Mbps     |

| BYPASS <sub>RATE</sub>         | Reclocker automatically goes to bypass         | MADI                                                                                            |              | 125    |      | Mbps     |

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                  | TEST CONDITIONS                                                                                                         | MIN | TYP            | MAX | UNIT |

|----------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|----------------|-----|------|

|                      |                            | Applied 0.2 UI input sinusoidal jitter,<br>measure –3-dB bandwidth on input-to-<br>output jitter transfer<br>11.88 Gbps |     | 13             |     | MHz  |

| $BW_{PLL}$           | PLL bandwidth              | 5.94 Gbps                                                                                                               |     | 7              |     | MHz  |

|                      |                            | 2.97 Gbps                                                                                                               |     | 5              |     | MHz  |

|                      |                            | 1.485 Gbps                                                                                                              |     | 3              |     | MHz  |

|                      |                            | 270 Mbps                                                                                                                |     | 1              |     | MHz  |

| J <sub>PEAKING</sub> | PLL jitter peaking         | 11.88 Gbps, 5.94 Gbps, 2.97 Gbps, 1.485 Gbps, 270 Mbps                                                                  |     | <0.3           |     | dB   |

| T <sub>LOCK</sub>    | Lock time                  | SMPTE supported data rates, disable HEO/VEO monitor, CTLE in AM0 Manual Mode                                            |     | 5              |     | ms   |

| TEMP <sub>LOCK</sub> | VCO temperature lock range | Measured with temperature ramp of 5°C per min, ramp up and down, –40°C to 85°C operating range at 11.88 Gbps            |     | 125            |     | °C   |

| TLAT                 | Declarica lateral          | Measured from IN0± to SDI_OUT1+, 11.88 Gbps                                                                             | 1   | .5 UI +<br>175 |     | ps   |

|                      | Reclocker latency          | Measured from IN0± to SDI_OUT2+, 11.88 Gbps                                                                             | 1   | .6 UI +<br>130 |     | ps   |

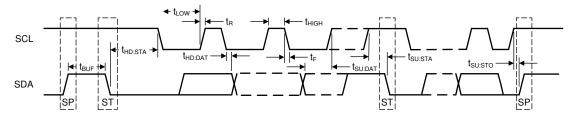

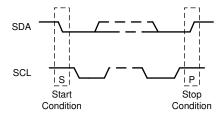

# 6.6 Recommended SMBus Interface Timing Specifications

over recommended operating supply and temperature ranges unless otherwise specified<sup>(1)</sup>

|                     | PARAMETER                                      | TEST CONDITIONS                                             | MIN | NOM M | AΧ | UNIT |

|---------------------|------------------------------------------------|-------------------------------------------------------------|-----|-------|----|------|

| F <sub>SCL</sub>    | SMBUS SCL frequency                            |                                                             | 10  | 4     | 00 | kHz  |

| T <sub>BUF</sub>    | Bus free time between stop and start condition | See Figure 1.                                               | 1.3 |       |    | μs   |

| T <sub>HD:STA</sub> | Hold time after (repeated) start condition.    | After this period, the first clock is generated.            | 0.6 |       |    | μs   |

| T <sub>SU:STA</sub> | Repeated start condition setup time            | See Figure 1.                                               | 0.6 |       |    | μs   |

| T <sub>SU:STO</sub> | Stop condition setup time                      | See Figure 1.                                               | 0.6 |       |    | μs   |

| T <sub>HD:DAT</sub> | Data hold time                                 | See Figure 1.                                               | 0   |       |    | ns   |

| T <sub>SU:DAT</sub> | Data setup time                                | See Figure 1.                                               | 100 |       |    | ns   |

| T <sub>LOW</sub>    | Clock low period                               | See Figure 1.                                               | 1.3 |       |    | μs   |

| T <sub>HIGH</sub>   | Clock high period                              | See Figure 1.                                               | 0.6 |       |    | μs   |

| T <sub>R</sub>      | Clock and data rise time                       | See Figure 1.                                               |     | 3     | 00 | ns   |

| T <sub>F</sub>      | Clock and data fall time                       | See Figure 1.                                               |     | 3     | 00 | ns   |

| T <sub>POR</sub>    | SMBus ready time after POR                     | Time from minimum VDDIO to SMBus valid write or read access |     |       | 50 | ms   |

<sup>(1)</sup> These parameters support SMBus 2.0 specifications.

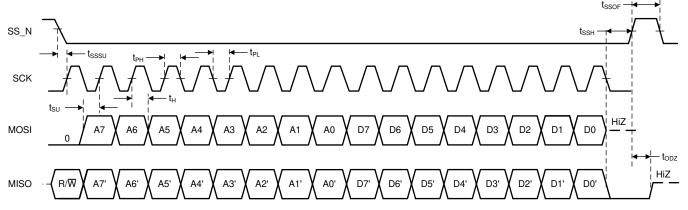

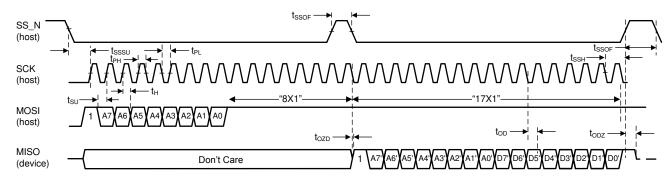

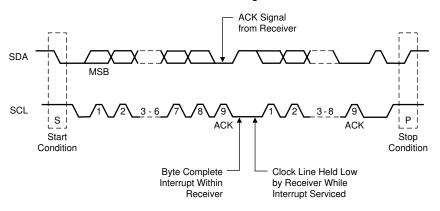

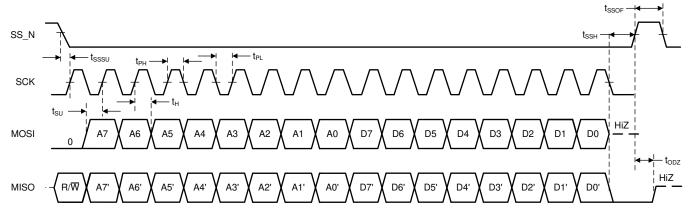

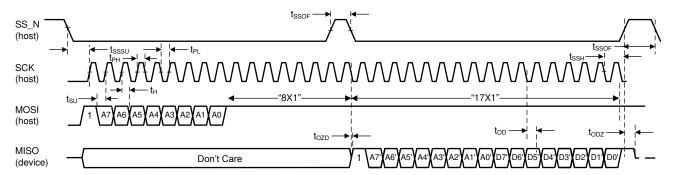

# 6.7 Serial Parallel Interface (SPI) Timing Specifications

over recommended operating supply and temperature ranges unless otherwise specified (1)

|                   | PARAMETER                    | TEST CONDITIONS             | MIN | NOM | MAX | UNIT            |

|-------------------|------------------------------|-----------------------------|-----|-----|-----|-----------------|

| F <sub>SCK</sub>  | SPI SCK frequency            |                             |     |     | 20  | MHz             |

| T <sub>PH</sub>   | SCK pulse width high         | See Figure 17 and Figure 18 | 40  |     |     | % SCK<br>period |

| T <sub>PL</sub>   | SCK pulse width low          | See Figure 17 and Figure 16 | 40  |     |     | % SCK<br>period |

| T <sub>SU</sub>   | MOSI setup time              | Con Figure 47 and Figure 40 | 4   |     |     | ns              |

| T <sub>H</sub>    | MOSI hold time               | See Figure 17 and Figure 18 | 4   |     |     | ns              |

| T <sub>SSSU</sub> | SS setup time                |                             | 14  |     |     | ns              |

| T <sub>SSH</sub>  | SS hold time                 | See Figure 17 and Figure 18 | 4   |     |     | ns              |

| T <sub>SSOF</sub> | SS off time                  |                             | 1   |     |     | μs              |

| T <sub>ODZ</sub>  | MISO driven-to-tristate time |                             |     | 20  |     | ns              |

| T <sub>OZD</sub>  | MISO tristate-to-driven time | See Figure 17 and Figure 18 |     | 10  |     | ns              |

| T <sub>OD</sub>   | MISO output delay time       |                             |     | 15  |     | ns              |

# (1) Typical SPI load capacitance is 2 pF.

Figure 1. SMBus Timing Parameters

Figure 2. SPI Timing Parameters (Write Operation)

Figure 3. SPI Timing Parameters (Read Operation)

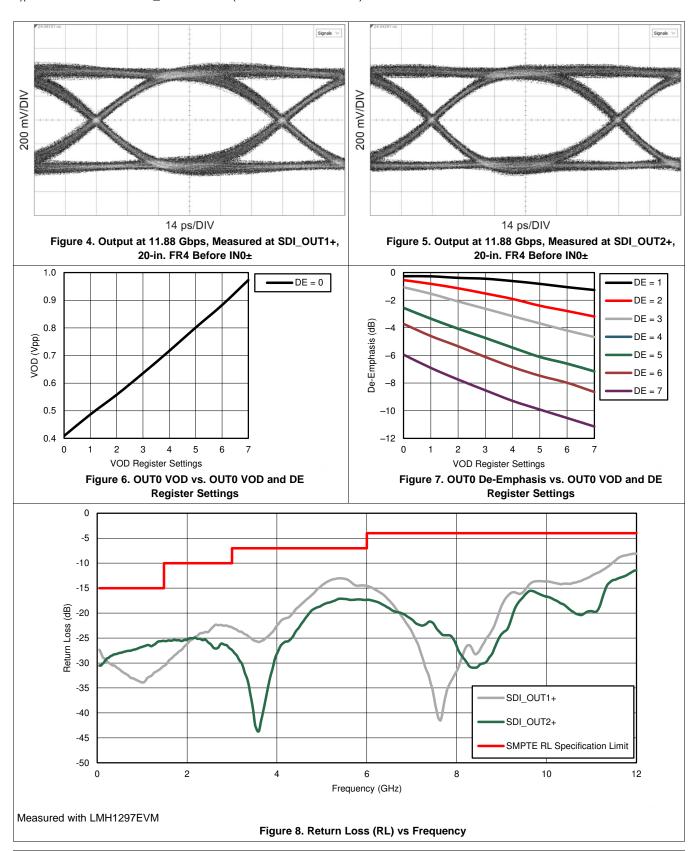

# 6.8 Typical Characteristics

$T_A = 25$ °C and VIN = VDD\_CDR = 2.5 V (unless otherwise noted)

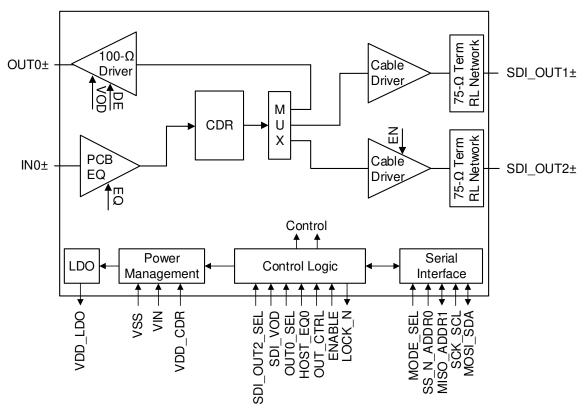

# 7 Detailed Description

#### 7.1 Overview

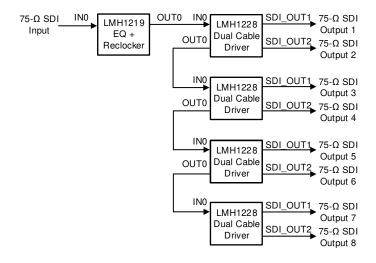

The LMH1228 is a 12G UHD-SDI dual output cable driver with integrated reclocker. From the host-side input at IN0 $\pm$ , the signal is equalized, reclocked, and routed to 75- $\Omega$  cable driver outputs at SDI\_OUT1 $\pm$  and SDI\_OUT2 $\pm$ . The 100- $\Omega$  driver at OUT0 $\pm$  can be used as a host-side loop-back output for monitoring purposes.

# 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 9. LMH1228 Block Diagram Overview

## 7.3 Feature Description

The LMH1228 data path consists of several key blocks as shown in the functional block diagram. These key blocks are:

- 4-Level Input Pins and Thresholds

- OUT0\_SEL and SDI\_OUT2\_SEL Control

- Input Signal Detect

- Continuous Time Linear Equalizer (CTLE)

- Clock and Data (CDR) Recovery

- Internal Eye Opening Monitor (EOM)

- Output Function Control

- Output Driver Control

- Status Indicators and Interrupts

# 7.3.1 4-Level Input Pins and Thresholds

The 4-level input configuration pins use a resistor divider to provide four logic states for each control pin. There is an internal  $30\text{-k}\Omega$  pullup and a  $60\text{-k}\Omega$  pulldown connected to the control pin that sets the default voltage at  $2/3 \times VIN$ . These resistors, together with the external resistor, combine to achieve the desired voltage level. By using the  $1\text{-k}\Omega$  pulldown,  $20\text{-k}\Omega$  pulldown, no connect, and  $1\text{-k}\Omega$  pullup, the optimal voltage levels for each of the four input states are achieved as shown in Table 1.

**Table 1. 4-Level Control Pin Settings**

| LEVEL | SETTING                | NOMINAL PIN VOLTAGE |

|-------|------------------------|---------------------|

| Н     | Tie 1 kΩ to VIN        | VIN                 |

| F     | Float (leave pin open) | 2/3 × VIN           |

| R     | Tie 20 kΩ to VSS       | 1/3 × VIN           |

| L     | Tie 1 kΩ to VSS        | 0                   |

Typical 4-Level Input Thresholds:

- Internal Threshold between L and R = 0.2 x VIN

- Internal Threshold between R and F = 0.5 x VIN

- Internal Threshold between F and H = 0.8 x VIN

#### 7.3.2 OUT0 SEL and SDI OUT2 SEL Control

The OUT0\_SEL and SDI\_OUT2\_SEL pins select the LMH1228 data-path routes. Table 2 shows all possible signal path combinations and typical use cases for each configuration.

Table 2. LMH1228 Signal Path Combinations

| OUT0_SEL | SDI_OUT2_SEL | INPUT | MAIN<br>OUTPUT | LINE SIDE<br>SECONDARY<br>OUTPUT | HOST SIDE<br>LOOP-BACK<br>OUTPUT | TYPICAL APPLICATION                                  |

|----------|--------------|-------|----------------|----------------------------------|----------------------------------|------------------------------------------------------|

| Н        | Н            | IN0±  | SDI_OUT1±      |                                  |                                  | Single cable driver                                  |

| Н        | L            | IN0±  | SDI_OUT1±      | SDI_OUT2±                        |                                  | Dual cable drivers                                   |

| L        | Н            | IN0±  | SDI_OUT1±      |                                  | OUT0±                            | Single cable driver with host-side loop-back enabled |

| L        | L            | IN0±  | SDI_OUT1±      | SDI_OUT2±                        | OUT0±                            | Dual cable drivers with host-side loop-back enabled  |

# 7.3.3 Input Signal Detect

INO has a signal detect circuit to monitor the presence or absence of an input signal. When the input signal amplitude for the selected input exceeds the signal detect assert threshold, the LMH1228 operates in normal operation mode.

In the absence of an input signal, the LMH1228 automatically goes into Power Save Mode to conserve power dissipation. When a valid signal is detected, the LMH1228 automatically exits Power Save Mode and returns to the normal operation mode. If the ENABLE pin is pulled low, the LMH1228 is forced into Power-Down Mode. In Power Save Mode, both the signal detect circuit and the serial interface remain active. In Power-Down Mode, only the serial interface remains active.

Users can monitor the status of the signal detect through register programming. This can be done either by configuring the LOCK\_N pin to output the SD\_N status or by monitoring the signal detect status register.

| ENABLE | SIGNAL INPUT               | OPERATING MODE                                                         |

|--------|----------------------------|------------------------------------------------------------------------|

| н      | 100-Ω signal input at IN0± | Normal operation Signal Detector at IN0± Serial interface active       |

| н      | No signal at IN0±          | Power Save Mode Signal Detector at IN0± Serial interface active        |

| L      | Input signal ignored       | Power-Down Mode<br>Forced device power down<br>Serial interface active |

**Table 3. Input Signal Detect Modes of Operation**

### 7.3.4 Continuous Time Linear Equalizer (CTLE)

The LMH1228 has a continuous time linear equalizer (CTLE) block for INO. The CTLE compensates for frequency-dependent loss due to the transmission media prior to the device input. The CTLE accomplishes this by applying variable gain to the input signal, thereby boosting higher frequencies more than lower frequencies. The CTLE block extends the signal bandwidth, restores the signal amplitude, and reduces ISI caused by the transmission medium.

IN0 has an on-chip  $100-\Omega$  termination and is designed for AC coupling, requiring a  $4.7-\mu F$ , AC-coupling capacitor for minimizing base-line wander. The PCB equalizer can compensate up to 20 inches of board trace at data rates up to 11.88 Gbps. There are two adapt modes for IN0: AM0 manual mode and AM1 adaptive mode. In AM0 manual mode, fixed EQ boost settings are applied through user-programmable control. In AM1 adaptive mode, state machines automatically find the optimal EQ boost from a set of 16 predetermined settings defined in Registers 0x40-0x4F.

The HOST\_EQ0 pin determines the IN0 adapt mode and EQ boost level. For normal operation, HOST\_EQ0 = F is recommended. HOST\_EQ0 pin logic settings are shown in Table 4. These HOST\_EQ0 pin settings can be overridden by register control. For more information, refer to the LMH1228 and LMH1208 Programming Guide (SNAU206).

| HOST_EQ0 <sup>(1)</sup> | IN0± EQ BOOST                                                                                         | RECOMMENDED BOARD<br>TRACE IN0± <sup>(2)</sup> |

|-------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Н                       | All Rates: AM0 Manual Mode, EQ=0x00                                                                   | < 1 inch                                       |

| F                       | Normal Operation<br>12G to 3G Rates: AM1 Adaptive Mode<br>1.5G, 270M Rates: AM0 Manual Mode, EQ= 0x00 | 0-20 inches                                    |

| R                       | All Rates: AM0 Manual Mode, EQ=0x80                                                                   | 10-15 inches                                   |

| L                       | All Rates: AM0 Manual Mode, EQ=0x90                                                                   | 20 inches                                      |

Table 4. HOST\_EQ0 Pin EQ Settings

- (1) The HOST\_EQ0 pin is also used to set OUT0 VOD and de-emphasis values. See Host-Side 100-Ω Output Driver (OUT0±) for more information.

- (2) Recommended board trace at 11.88 Gbps.

### 7.3.5 Clock and Data (CDR) Recovery

After the input signal passes through the CTLE, the equalized data is fed into the clock and data recovery (CDR) block. Using an internal PLL, the CDR locks to the incoming equalized data and recovers a clean internal clock to re-sample the equalized data. The LMH1228 CDR is able to tolerate high input jitter, tracking low-frequency input jitter below the PLL bandwidth while reducing high-frequency input jitter above the PLL bandwidth. The supported data rates are listed in Table 5.

#### Table 5. Supported Data Rates

| INPUT | DATA RATE                                                             | RECLOCKER |

|-------|-----------------------------------------------------------------------|-----------|

| IN0±  | 11.88 Gbps, 5.94 Gbps, 2.97 Gbps, 1.485 Gbps, 270 Mbps <sup>(1)</sup> | Enable    |

|       | 125 Mbps                                                              | Bypass    |

The LMH1228 supports divide-by-1.001 lock rates for 11.88 Gbps, 5.94 Gbps, 2.97 Gbps, and 1.485 Gbps.

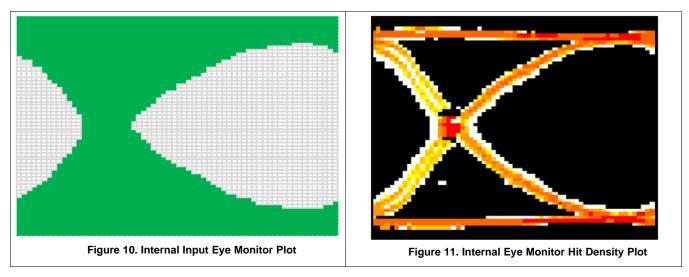

### 7.3.6 Internal Eye Opening Monitor (EOM)

The LMH1228 has an on-chip eye opening monitor (EOM) that can be used to analyze, monitor, and diagnose the post-equalized waveform, just prior to the CDR reclocker. The EOM is operational for 2.97 Gbps and higher data rates.

The EOM monitors the post-equalized waveform in a time window that spans one unit interval and a configurable voltage range that spans up to  $\pm 400$  mV. The time window and voltage range are divided into 64 steps, so the result of the eye capture is a 64 × 64 matrix of hits, where each point represents a specific voltage and phase offset relative to the main data sampler. The number of hits registered at each point needs to be taken in context with the total number of bits observed at that voltage and phase offset to determine the corresponding probability for that point.