# LM3630A 高效双灯串白光发光二级管 (LED) 驱动器

查询样品: LM3630A

### 特性

- 驱动多达 2 灯串 LED (每个灯串有 10 个串联的 LED)

- 效率高达 87%

- 8 位 I<sup>2</sup>C 兼容可编程指数或线性亮度控制

- 针对内容自适应亮度控制 (CABC) 操作的脉宽调制 (PWM) 亮度控制

- 每个灯串的单独电流控制

- 针对 LED 的真正关断隔离

- 内部软启动限制了浪涌电流

- 2.3V 至 5.5V 的宽输入电压范围

- 自适应净空

- 可编程 16V/24V/32V/40V 过压保护

- 具有可选额外偏移的 500kHz 或 1MHz 的可选升压

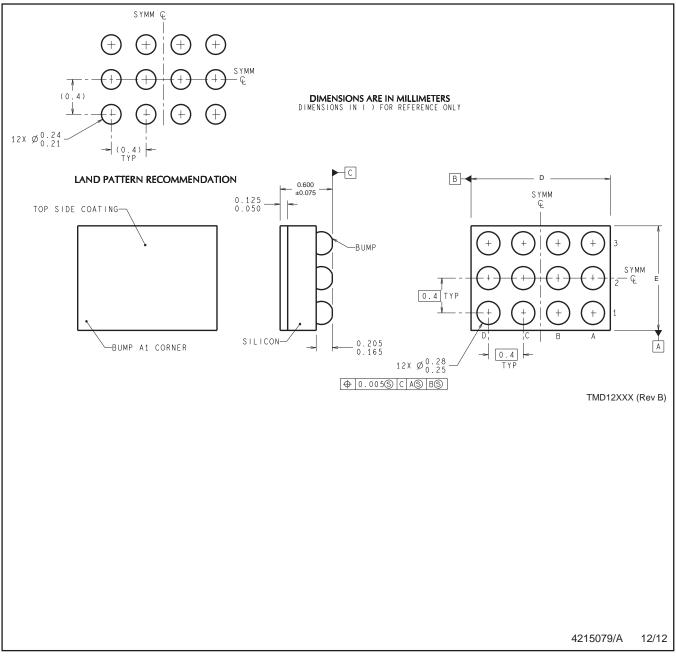

- 半高 12 焊锡凸点芯片级球栅阵列 (DSBGA) 封装

- 解决方案尺寸 32mm²

## 应用范围

- 智能手机 LCD 背光

- LCD + 键盘照明

## 说明

LM3630A 是一款电流模式升压转换器,此转换器为每 串具有 10 个 LED 的两个灯串供电并控制其中的电 流。 可通过一个 I2C 兼容接口完成设定。 最大 LED 电流可在 5mA 至 28.5mA 的范围内调节。 在任一指 定的最大 LED 电流情况下,可使用 256 个指数或线性 调光步长来进一步调节 LED 亮度。 此外,可启用脉宽 调制 ("PWM") 亮度控制,以实现通过一个逻辑电平 PWM 信号来调整 LED 电流。

可在 500kHz 时设定升压开关频率以实现低开关损耗性 能,或者在 1MHz 时使用微型半高电感器。可将这些 频率的偏移设定为 10%。 在 16V, 24V, 32V 或 40V 时可设定过压保护以适应多种 LED 配置以及肖特基二 极管/输出电容器组合的需要。

此器件在 2.3V 至 5.5V 的运行电压范围和 -40°C 至 +85°C 的温度范围内运转。 LM3630A 采用超小型 12 焊锡凸点 DSBGA 封装。

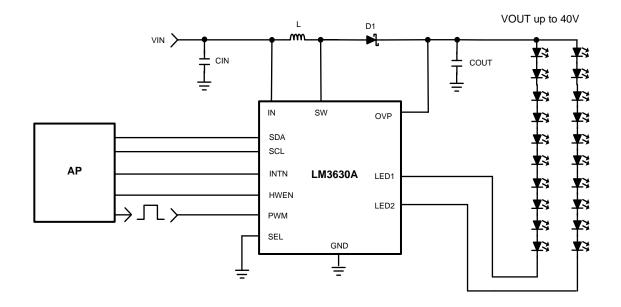

## TYPICAL APPLICATION CIRCUIT

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

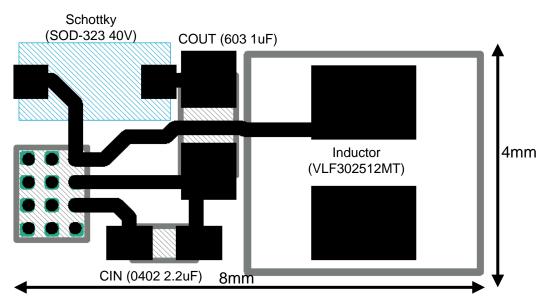

#### **TYPICAL PCB LAYOUT**

Figure 1. Typical PCB Layout (2 x 10 LED Application)

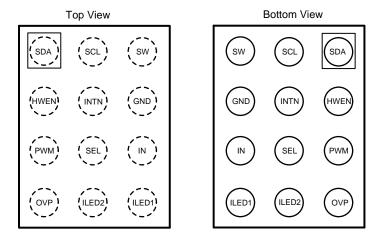

## **CONNECTION DIAGRAM**

Figure 2. Package Number YFQ12HNA

## **AVAILABLE OPTIONS**

| PART NUMBER | PACKAGE MARKING (1) | PACKAGE   | SUPPLIED AS             |

|-------------|---------------------|-----------|-------------------------|

| LM3630ATME  | YM                  | VEOTOLINA | 250 Units, Tape & Reel  |

| LM3630ATMX  | D6                  | YFQ12HNA  | 3000 Units, Tape & Reel |

<sup>(1)</sup> YM = Date Code.

#### **PIN DESCRIPTIONS**

| Ball | Name  | Description                                                                                                                                                                                                    |  |  |  |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1   | SDA   | Serial Data Connection for I <sup>2</sup> C-Compatible Interface                                                                                                                                               |  |  |  |

| A2   | SCL   | Serial Clock Connection for I <sup>2</sup> C-Compatible Interface                                                                                                                                              |  |  |  |

| А3   | SW    | Inductor Connection, Diode Anode Connection, and Drain Connection for Internal NFET.  Connect the inductor and diode as close as possible to SW to reduce inductance and capacitive coupling to nearby traces. |  |  |  |

| B1   | HWEN  | Logic High Hardware Enable                                                                                                                                                                                     |  |  |  |

| B2   | INTN  | Interrupt output for fault status change. Open drain active low signal.                                                                                                                                        |  |  |  |

| В3   | GND   | Ground                                                                                                                                                                                                         |  |  |  |

| C1   | PWM   | External PWM Brightness Control Input                                                                                                                                                                          |  |  |  |

| C2   | SEL   | Selects I <sup>2</sup> C-compatible address. Ground selects 7-bit address 36h. VIN selects address 38h.                                                                                                        |  |  |  |

| С3   | IN    | Input Voltage Connection. Connect a 2.3V to 5.5V supply to IN and bypass to GND with a 2.2 $\mu$ F or greater ceramic capacitor.                                                                               |  |  |  |

| D1   | OVP   | Output Voltage Sense Connection for Over Voltage Sensing. Connect OVP to the positive terminal of the output capacitor.                                                                                        |  |  |  |

| D2   | ILED2 | Input Terminal to Internal Current Sink #2.                                                                                                                                                                    |  |  |  |

| D3   | ILED1 | Input Terminal to Internal Current Sink #1.                                                                                                                                                                    |  |  |  |

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## ABSOLUTE MAXIMUM RATINGS (1) (2)

|                                           |                                                                      | VALUE              | UNIT |  |

|-------------------------------------------|----------------------------------------------------------------------|--------------------|------|--|

| IN, HWEN, PWM, SCL, SDA, INTN, SEL to GND |                                                                      | -0.3 to 6.0        | V    |  |

| SW, OVP, ILED1, ILED2 to GND              |                                                                      | -0.3 to 45         |      |  |

|                                           | Continuous Power Dissipation (3)                                     | Internally Limited |      |  |

|                                           | Maximum Junction Temperature                                         | 150                |      |  |

|                                           | Storage Temperature Range                                            | -45 to +150        |      |  |

| $T_{(J-MAX)}$                             | Maximum Lead Temperature (Soldering) (4) Vapor Phase (60 sec.)       | 215                | °C   |  |

|                                           | Maximum Lead Temperature (Soldering) (4) Infrared (15 sec.)          | 220                |      |  |

| FOD Davies (5)                            | Human Body Model                                                     | 2                  | kV   |  |

| ESD Rating <sup>(5)</sup>                 | Charged Device Mod                                                   | 500                | V    |  |

| Operating Ratings (1) (2)                 |                                                                      | 1                  |      |  |

| V <sub>IN</sub>                           | Input Voltage Range                                                  | 2.3 to 5.5         | V    |  |

| T <sub>A</sub>                            | Operating Ambient Temperature Range (6)                              | -40 to +85         | °C   |  |

| Thermal Properties                        |                                                                      | 1                  |      |  |

| $\theta_{JA}$                             | Junction-to-Ambient Thermal Resistance, YFQ12 package <sup>(7)</sup> | 78.1               | °C/W |  |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages are with respect to the potential at the GND pin.

- (3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 140°C (typ.) and disengages at T<sub>J</sub> = 125°C (typ.).

- (4) For detailed soldering specifications and information, please refer to Texas Instruments Application Note 1112: DSBGA Wafer Level Chip Scale Package (AN-1112)

- (5) The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. (MIL-STD-883 3015.7) .

- (6) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

- (7) Junction-to-ambient thermal resistance is highly dependent on application and board layout. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design. For more information, please refer to Texas Instruments Application Note 1112: DSBGA Wafer Level Chip Scale Package.

## **ELECTRICAL CHARACTERISTICS (1)**

Limits in standard typeface are for  $T_A = 25^{\circ}C$ , and limits **in boldface** type apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_A \le +85^{\circ}C$ ). Unless otherwise specified,  $V_{IN} = 3.6V$ .

| Symbol                         | Parameter                                               | Condition                                                                                                                                                                                             |                                          | Min  | Тур  | Max             | Units |

|--------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|------|-----------------|-------|

| ILED1, ILED2                   | Output Current Regulation                               | 2.5V ≤ V <sub>IN</sub> ≤ 5.5V, Full Sca                                                                                                                                                               | ale Current = 20 mA                      | 19   | 20   | 21              | mA    |

|                                | ILED1 to ILED2 Current                                  | $2.5V \le V_{IN} \le 5.5V$ , ILED = 10 mA, TA = +25°C                                                                                                                                                 | ILED1 on A                               | -1   | 0.5  | 1               | %     |

| матсн                          | Matching <sup>(2)</sup>                                 | $2.5V \le V_{IN} \le 5.5V$ , ILED = 10 mA, 0°C $\le T_A \le +70$ °C                                                                                                                                   | ILED2 on B                               | -2.5 | 0.5  | 2.5             |       |

| V <sub>REG_CS</sub>            | Regulated Current Sink<br>Headroom Voltage              | ILED = 5 mA                                                                                                                                                                                           |                                          |      | 250  |                 | mV    |

| $V_{HR}$                       | Current Sink Minimum<br>Headroom Voltage                | ILED = 95% of nominal, IL                                                                                                                                                                             | ED = 20 mA                               |      | 160  | 240             | IIIV  |

| R <sub>DSON</sub>              | NMOS Switch On<br>Resistance                            | I <sub>SW</sub> = 100 mA                                                                                                                                                                              |                                          |      | 0.25 |                 | Ω     |

|                                |                                                         |                                                                                                                                                                                                       |                                          | 480  | 600  | 720             |       |

| •                              | NMOS Switch Current                                     | 2.5\/////////                                                                                                                                                                                         |                                          | 640  | 800  | 960             |       |

| CL                             | Limit                                                   | $2.5V \le V_{\text{IN}} \le 5.5V$                                                                                                                                                                     |                                          | 800  | 1000 | 1200            | mA    |

|                                |                                                         |                                                                                                                                                                                                       |                                          | 960  | 1200 | 1440            |       |

|                                |                                                         | ON Threshold, 2.3V ≤ V <sub>IN</sub> :                                                                                                                                                                | ≤ 5.5V, 24V option                       | 23   | 24   | 25              |       |

| Output Over-Voltage Protection | ON Threshold, 2.3V ≤ V <sub>IN</sub> ≤ 5.5V, 40V option |                                                                                                                                                                                                       | 39                                       | 41   | 44   | V               |       |

| Totodion                       |                                                         | Hysteresis                                                                                                                                                                                            |                                          | 1    |      |                 |       |

| f <sub>SW</sub> Switching Fi   |                                                         |                                                                                                                                                                                                       | 560 kHz shift = 1                        | 538  | 560  | 582             | kHz   |

|                                | Outliebie e Francisco                                   | 0.5)/ 4.1/ 4.5.5)/                                                                                                                                                                                    | 500 kHz shift = 0                        | 481  | 500  | 518             |       |

|                                | Switching Frequency                                     | $2.5V \le V_{IN} \le 5.5V$                                                                                                                                                                            | 1.12 MHz shift = 1                       | 1077 | 1120 | 1163            |       |

|                                |                                                         |                                                                                                                                                                                                       | 1MHz shift = 0                           | 962  | 1000 | 1038            |       |

| D <sub>MAX</sub>               | Maximum Duty Cycle                                      |                                                                                                                                                                                                       |                                          |      | 94   |                 | %     |

| Q                              | Quiescent Current into Device, Not Switching.           | V <sub>IN</sub> = 3.6V                                                                                                                                                                                | ILED1 = ILED2 = 20mA, Feedback disabled. |      | 350  |                 | μA    |

| SHDN                           | Shutdown Current                                        | 2.3V ≤ V <sub>IN</sub> ≤ 5.5V                                                                                                                                                                         | HWEN = VIN, I <sup>2</sup> C<br>Shutdown |      | 1    | 4               |       |

|                                |                                                         |                                                                                                                                                                                                       | HWEN = GND                               |      | 1    | 4               | μΑ    |

| LED_MIN                        | Minimum LED Current in ILED1 or ILED2                   | Full Scale Current = 20 mA<br>Exponential Mapping Mode                                                                                                                                                |                                          |      | 13   |                 |       |

| -                              | Thermal Shutdown                                        |                                                                                                                                                                                                       |                                          |      | +140 |                 | •c    |

| Γ <sub>SD</sub>                | Hysteresis                                              |                                                                                                                                                                                                       |                                          |      | 15   |                 |       |

| WAIT                           | Initialization Timing                                   | Time period to wait from the assertion of HWEN or after Software Reset, before an I <sup>2</sup> C transaction will be ACK'ed. During this time period an I <sup>2</sup> C transaction will be NAK'ed |                                          | 1    |      |                 | ms    |

| Logic Inputs (F                | PWM, HWEN, SEL, SCL, SC                                 | PA)                                                                                                                                                                                                   |                                          |      |      |                 |       |

| V <sub>IL</sub>                | Input Logic Low                                         |                                                                                                                                                                                                       |                                          | 0    |      | 0.4             | 1/    |

| V <sub>IH</sub>                | Input Logic High                                        |                                                                                                                                                                                                       |                                          | 1.2  |      | V <sub>IN</sub> | V     |

| V <sub>OL</sub>                | Output Logic Low (SDA, INTN)                            | 2.3V ≤ V <sub>IN</sub> ≤ 5.5V                                                                                                                                                                         |                                          |      |      | 400             | mV    |

| :<br>PWM                       | PWM Input Frequency                                     |                                                                                                                                                                                                       |                                          | 10   |      | 80              | kHz   |

|                                | Innut Conscitator                                       | SDA                                                                                                                                                                                                   | Ą                                        |      | 4.5  |                 |       |

| C <sub>IN</sub>                | Input Capacitance                                       | SCI                                                                                                                                                                                                   | _                                        |      | 5.0  |                 | pF    |

Min and Max limits are specified by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most

likely norm. Unless otherwise specified, conditions for typical specifications are:  $V_{IN} = 3.6V$  and  $T_A = +25^{\circ}C$ . LED current sink matching between LED1 and LED2 is given by taking the difference between  $I_{LED1}$  and  $I_{LED2}$  and dividing by the average. This simplifies to  $(I_{LED1} - I_{LED2})/(I_{LED1} + I_{LED2}) \times 2$  at  $I_{LED} = 10$  mA.  $I_{LED1}$  is driven by Bank A and  $I_{LED2}$  is driven by Bank B.

# **ELECTRICAL CHARACTERISTICS** (1) (continued)

Limits in standard typeface are for  $T_A = 25^{\circ}C$ , and limits **in boldface** type apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_A \le +85^{\circ}C$ ). Unless otherwise specified,  $V_{IN} = 3.6V$ .

| Symbol                     | Parameter                                | Condition    | Min | Тур | Max | Units |

|----------------------------|------------------------------------------|--------------|-----|-----|-----|-------|

| I <sup>2</sup> C-Compatibl | e Timing Specifications (S               | CL, SDA) (3) |     |     |     |       |

| t <sub>1</sub>             | SCL (Clock Period)                       |              | 2.5 |     |     | μs    |

| t <sub>2</sub>             | Data in Setup Time to SCL High           |              | 100 |     |     |       |

| t <sub>3</sub>             | Data in Setup Time to SCL Low            |              | 0   |     |     |       |

| t <sub>4</sub>             | SDA Low Setup Time to<br>SCL Low (Start) |              | 100 |     |     | ns    |

| t <sub>5</sub>             | SDA High Hold Time to<br>SCL High (Stop) |              | 100 |     |     |       |

(3) SCL and SDA must be glitch-free in order for proper brightness to be realized.

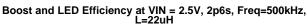

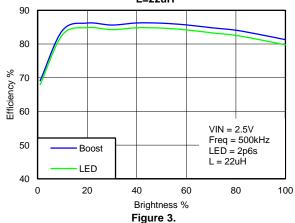

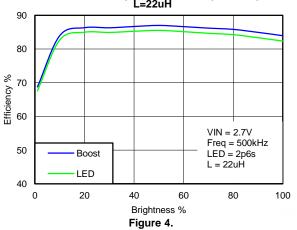

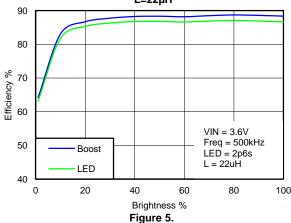

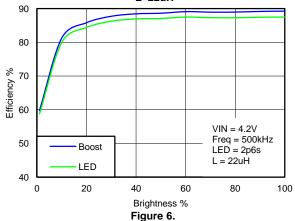

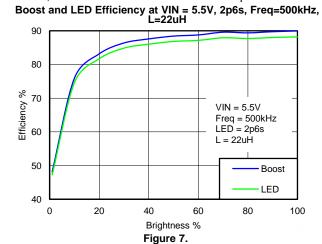

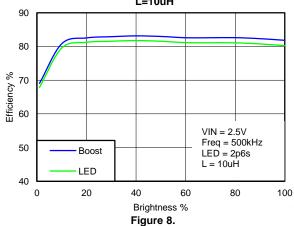

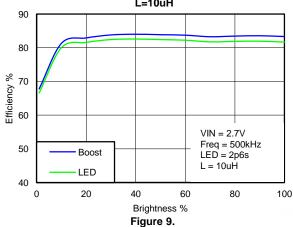

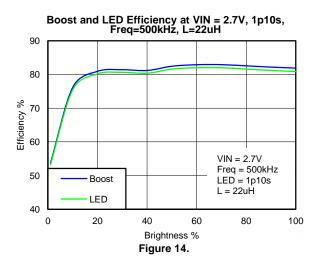

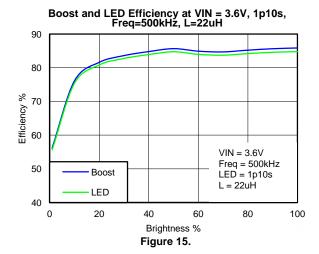

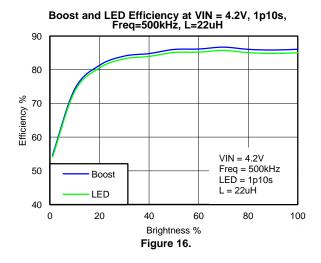

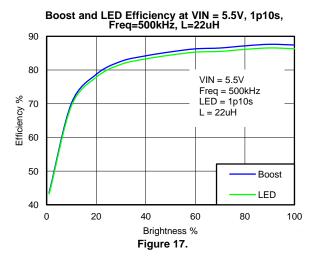

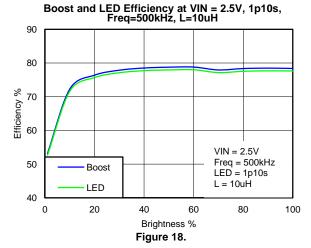

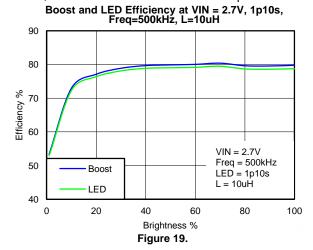

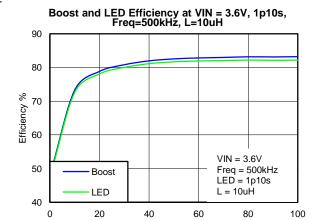

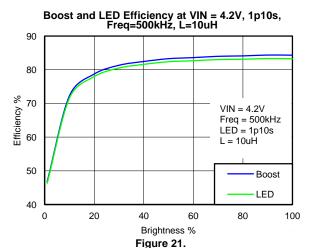

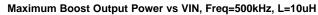

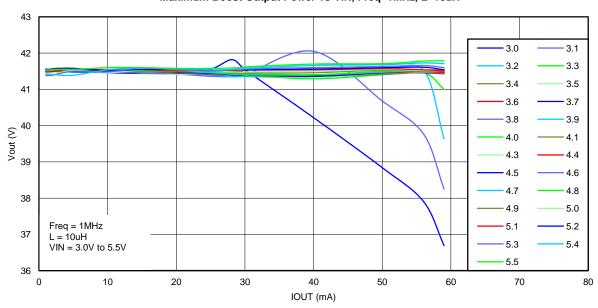

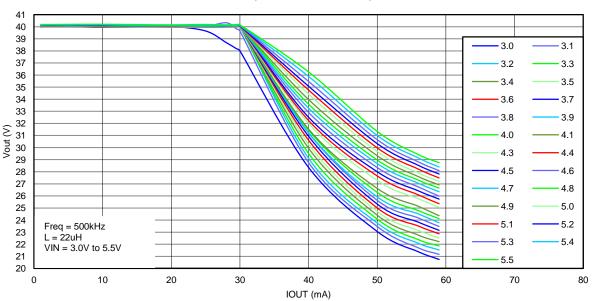

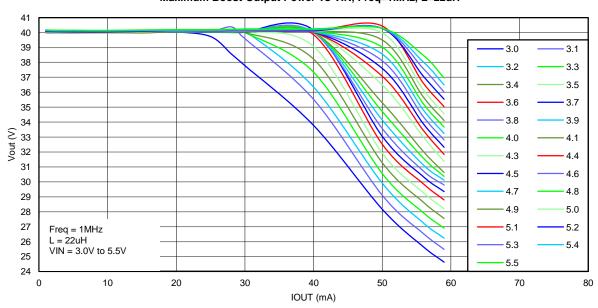

#### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = +25$ °C, ILED Full Scale = 20.0mA unless specified otherwise.

# Boost and LED Efficiency at VIN = 2.7V, 2p6s, Freq=500kHz, L=22uH

# Boost and LED Efficiency at VIN = 3.6V, 2p6s, Freq=500kHz, L=22 $\mu$ H

Boost and LED Efficiency at VIN = 4.2V, 2p6s, Freq=500kHz, L=22uH

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

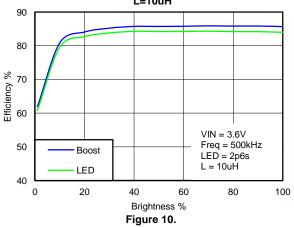

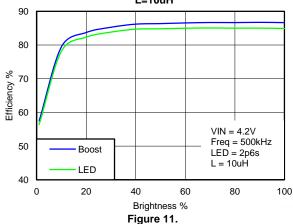

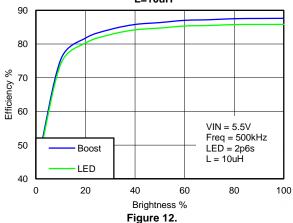

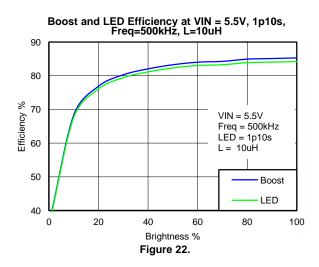

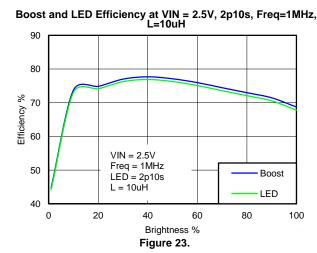

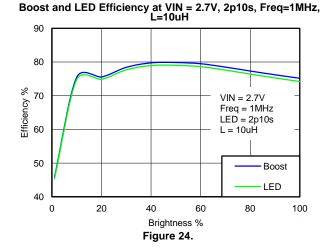

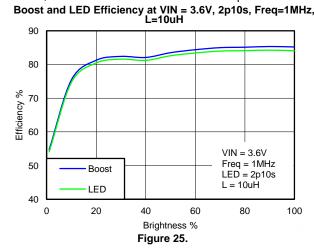

$T_A = +25$ °C, ILED Full Scale = 20.0mA unless specified otherwise.

Boost and LED Efficiency at VIN = 2.5V, 2p6s, Freq=500kHz, L=10uH

Boost and LED Efficiency at VIN = 2.7V, 2p6s, Freq=500kHz, L=10uH

Boost and LED Efficiency at VIN = 3.6V, 2p6s, Freq=500kHz, L=10uH

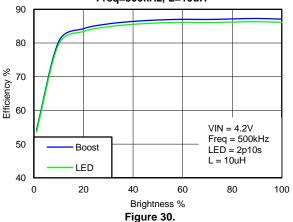

Boost and LED Efficiency at VIN = 4.2V, 2p6s, Freq=500kHz, L=10uH

Boost and LED Efficiency at VIN = 5.5V, 2p6s, Freq=500kHz, L=10uH

# TEXAS INSTRUMENTS

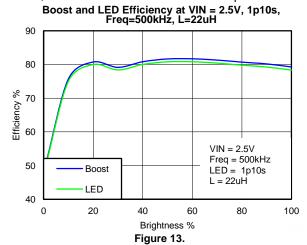

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A$  = +25°C, ILED Full Scale = 20.0mA unless specified otherwise.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A$  = +25°C, ILED Full Scale = 20.0mA unless specified otherwise.

Brightness %

Figure 20.

# TEXAS INSTRUMENTS

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

T<sub>A</sub> = +25°C, ILED Full Scale = 20.0mA unless specified otherwise.

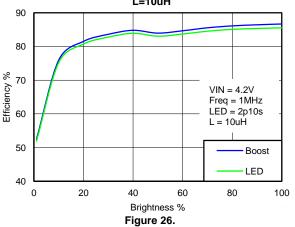

Boost and LED Efficiency at VIN = 4.2V, 2p10s, Freq=1MHz, L=10uH

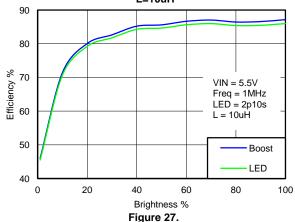

Boost and LED Efficiency at VIN = 5.5V, 2p10s, Freq=1MHz, L=10uH

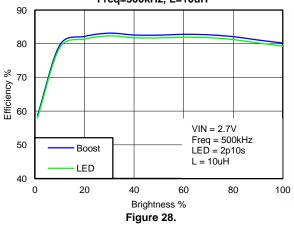

Boost and LED Efficiency at VIN = 2.7V, 2p10s, Freq=500kHz, L=10uH

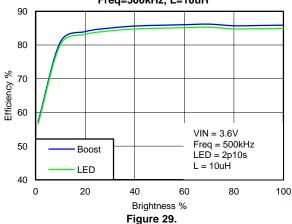

Boost and LED Efficiency at VIN = 3.6V, 2p10s, Freq=500kHz, L=10uH

Boost and LED Efficiency at VIN = 4.2V, 2p10s, Freq=500kHz, L=10uH

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

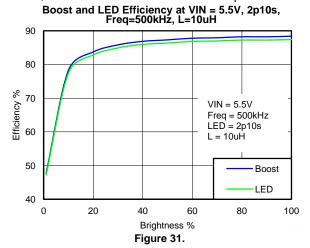

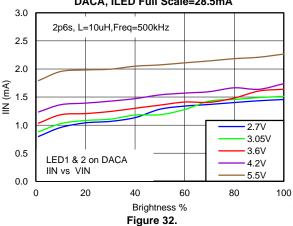

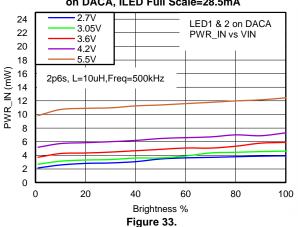

$T_A$  = +25°C, ILED Full Scale = 20.0mA unless specified otherwise.

IIN across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

PWR\_IN across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

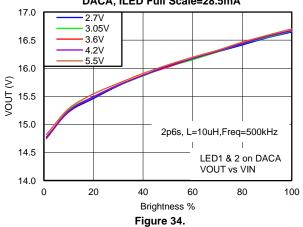

VOUT across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

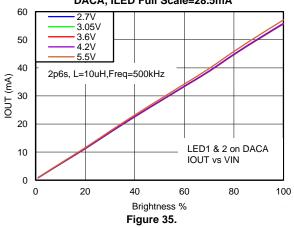

IOUT across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

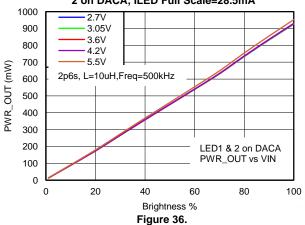

PWR\_OUT across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

T<sub>A</sub> = +25°C, ILED Full Scale = 20.0mA unless specified otherwise.

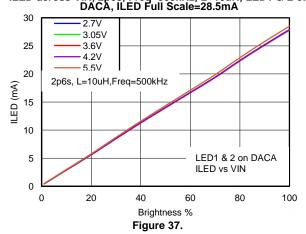

ILED across VIN, 2p6s, Freg=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

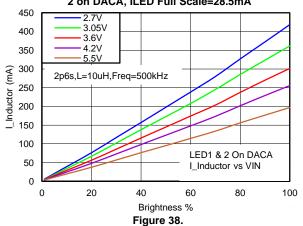

I\_Inductor across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

INSTRUMENTS

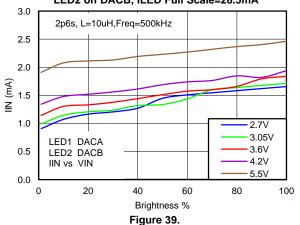

IIN across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

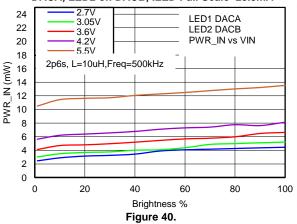

PWR\_IN across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

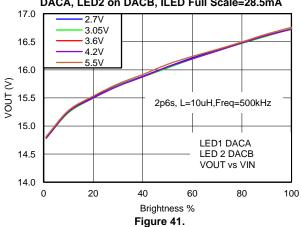

VOUT across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

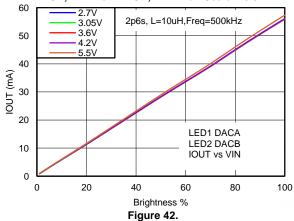

IOUT across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

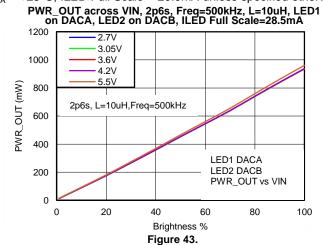

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

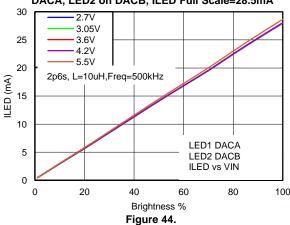

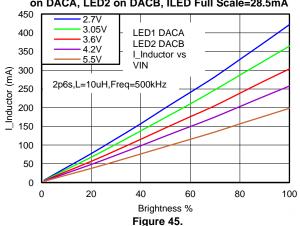

$T_A = +25^{\circ}C$ , ILED Full Scale = 20.0mA unless specified otherwise.

ILED across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

I\_Inductor across VIN, 2p6s, Freq=500kHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

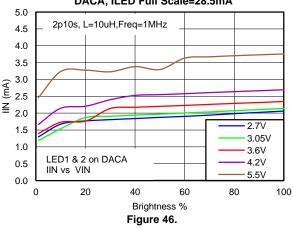

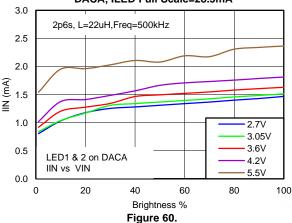

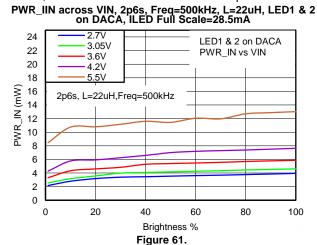

IIN across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

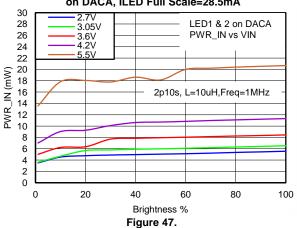

PWR\_IN across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

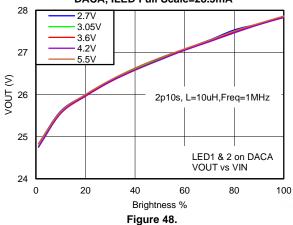

VOUT across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

**NSTRUMENTS**

ZHCSBI3 – APRIL 2013 www.ti.com.cn

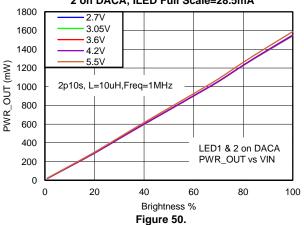

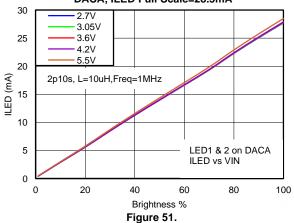

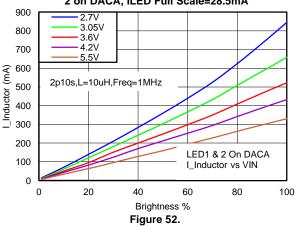

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

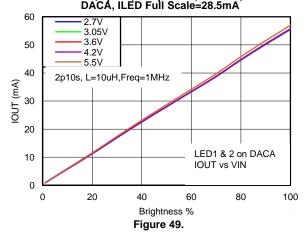

$T_A = +25^{\circ}\text{C}$ , ILED Full Scale = 20.0mA unless specified otherwise. IOUT across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

PWR\_OUT across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

ILED across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

I\_Inductor across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

IIN across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

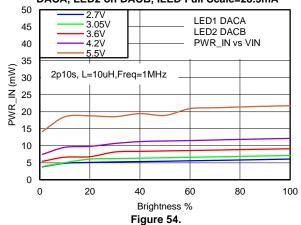

PWR\_IN across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

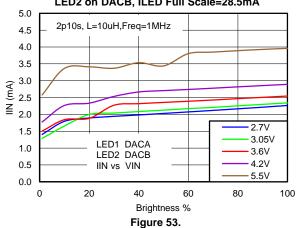

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

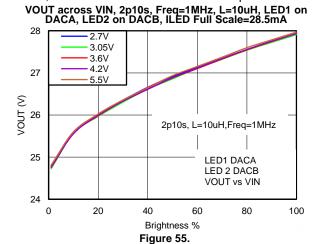

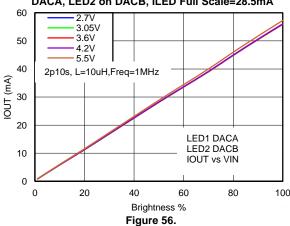

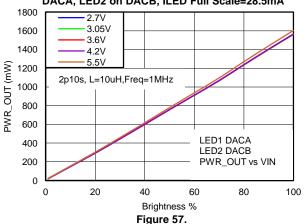

$T_A = +25$ °C, ILED Full Scale = 20.0mA unless specified otherwise.

IOUT across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

PWR\_OUT across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

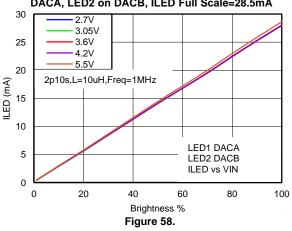

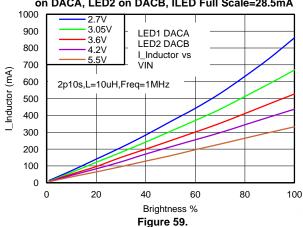

ILED across VIN, 2p10s, Freq=1MHz, L=10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

I\_Inductor across VIN, 2p10s, Freq=1MHz, L = 10uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

IIN across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A$  = +25°C, ILED Full Scale = 20.0mA unless specified otherwise.

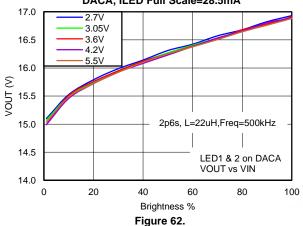

VOUT across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

INSTRUMENTS

PWR\_IOUT across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

ILED across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

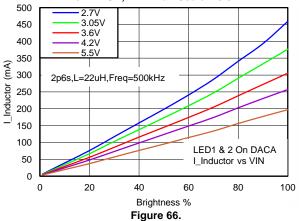

I\_Inductor across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 & 2 on DACA, ILED Full Scale=28.5mA

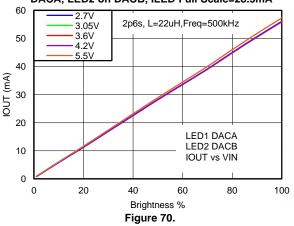

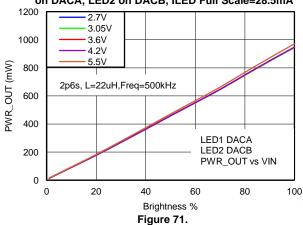

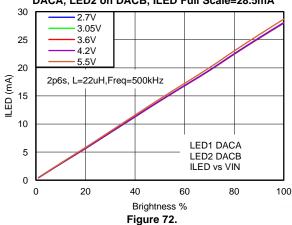

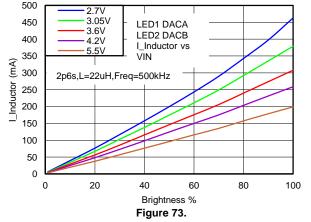

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

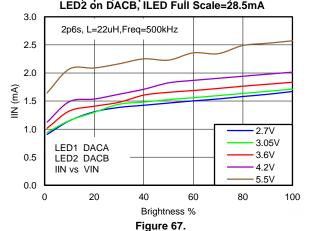

$\rm T_A=+25^{\circ}C,\ ILED\ Full\ Scale=20.0mA$  unless specified otherwise. IIN across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

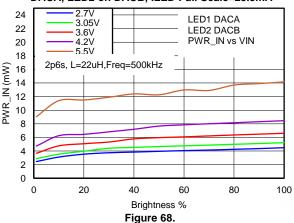

PWR\_IIN across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

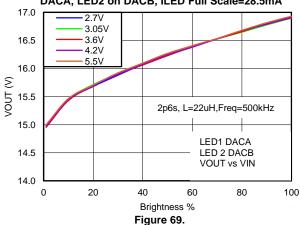

VOUT across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

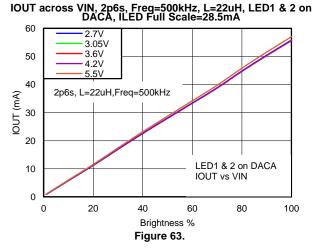

IOUT across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

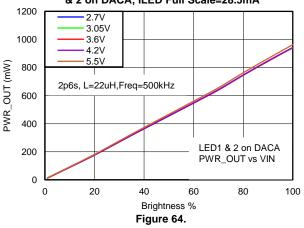

PWR\_OUT across VIN, 2p6s, Freg=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

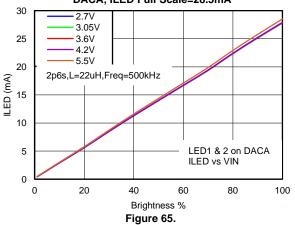

ILED across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

NSTRUMENTS

ZHCSBI3 – APRIL 2013 www.ti.com.cn

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25$ °C, ILED Full Scale = 20.0mA unless specified otherwise.

I\_Inductor across VIN, 2p6s, Freq=500kHz, L=22uH, LED1 on DACA, LED2 on DACB, ILED Full Scale=28.5mA

#### **FUNCTIONAL DESCRIPTION**

## Operation

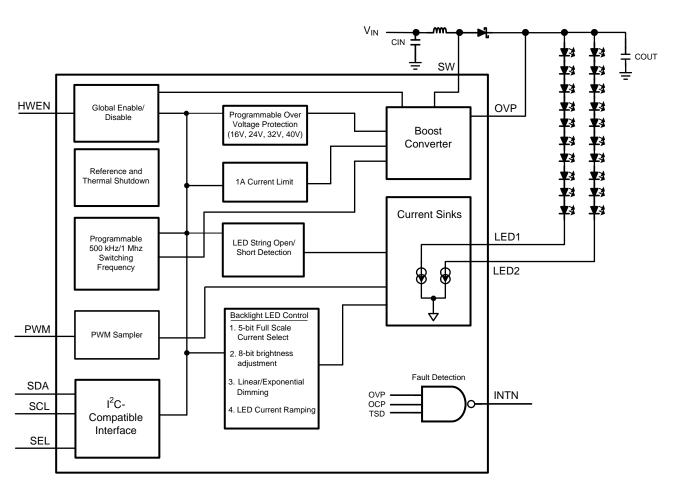

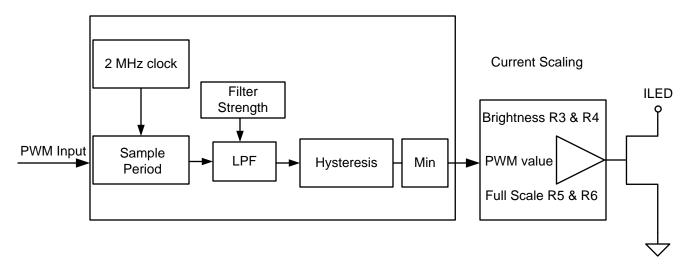

The LM3630A provides the power for two high-voltage LED strings (up to 40V at 28.5 mA each). The two high-voltage LED strings are powered from an integrated asynchronous boost converter. The device is programmable over an I<sup>2</sup>C-compatible interface. Additional features include a PWM input for content adjustable brightness control, programmable switching frequency, and programmable over voltage protection (OVP).

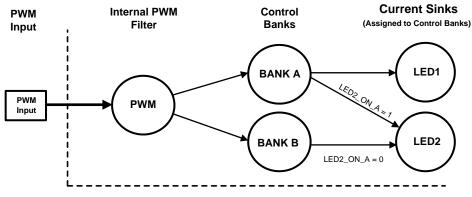

## **Control Bank Mapping**

Control of the LM3630A's current sinks is not done directly, but through the programming of Control Banks. The current sinks are then assigned to the programmed Control Bank (see Figure 74). Both current sinks can be assigned to Control Bank A or LED1 can use Control Bank A while LED2 uses Control Bank B. Assigning LED1 to Control Bank A and LED2 to Control Bank B allows for better LED current matching. Assigning each current sink to different control banks allows for each current sink to be programmed with a different current or have the PWM input control a specific current sink.

Figure 74. Control Diagram

**Table 1. Bank Configuration Examples-Register Values**

| Registers to<br>Program | ILED1 on A, ILED2 on B with PWM Dimming <sup>(1)</sup> | ILED1 and ILED2 on A with PWM Dimming | ILED1 on A with PWM<br>ILED2 on B no PWM     |

|-------------------------|--------------------------------------------------------|---------------------------------------|----------------------------------------------|

| Control                 | 1EH linear or 06h exp                                  | 15h linear or 05h exp                 | 1EH linear or 06h exp                        |

| Configuration           | 1Bh                                                    | 09h                                   | 19h                                          |

| Brightness A            | used for A                                             | used for both                         | used for A                                   |

| Brightness B            | used for B                                             | not used                              | used for B (A and B do not have to be equal) |

<sup>(1)</sup> LED current matching is specified using this configuration.

#### **PWM Input Polaritiy**

The PWM Input can be set for active high (default) or active low polarity. With active low polarity the LED current is a function of the negative duty cycle at PWM.

#### **HWEN Input**

HWEN is the global hardware enable to the LM3630A. HWEN must be pulled high to enable the device. HWEN is a high-impedance input so it cannot be left floating. When HWEN is pulled low the LM3630A is placed in shutdown and all the registers are reset to their default state.

#### **SEL Input**

SEL is the select pin for the serial bus device address. When this pin is connected to ground, the seven-bit device address is 36H. When this pin is tied to the VIN power rail, the device address is 38H.

#### **INTN Output**

The INTN pin is an open drain active low output signal which will indicate detected faults. The signal will assert low when either OCP, OVP, or TSD is detected by the LED driver. The Interrupt Enable register must be set to connect these faults to the INTN pin.

#### **Boost Converter**

The high-voltage boost converter provides power for the two current sinks (ILED1 and ILED2). The boost circuit operates using a 10  $\mu$ H to 22  $\mu$ H inductor and a 1 $\mu$ F output capacitor. The selectable 500 kHz or 1MHz switching frequency allows for the use of small external components and provides for high boost converter efficiency. Both LED1 and LED2 feature an adaptive voltage regulation scheme where the feedback point (LED1 or LED2) is regulated to a minimum of 300 mV. When there are different voltage requirements in both high-voltage LED strings, because of different programmed voltages or string mismatch, the LM3630A will regulate the feedback point of the highest voltage string to 300 mV and drop the excess voltage of the lower voltage string across the lower strings current sink.

#### **Boost Switching Frequency Select**

The LM3630A's boost converter can have a 1MHz or 500 kHz switching frequency. For a 500 kHz switching frequency the inductor must be between 10  $\mu$ H and 22  $\mu$ H. For the 1MHz switching frequency the inductor can be between 10  $\mu$ H and 22  $\mu$ H. Additionally there is a Frequency Shift bit which will offset the frequency approximately 10%. For the 500 kHz setting, Shift = 0. The boost frequency is shifted to 560 kHz when Shift = 1. For the 1MHz setting, Shift = 0. The boost frequency is shifted to 1120 kHz when Shift = 1.

#### **Adaptive Headroom**

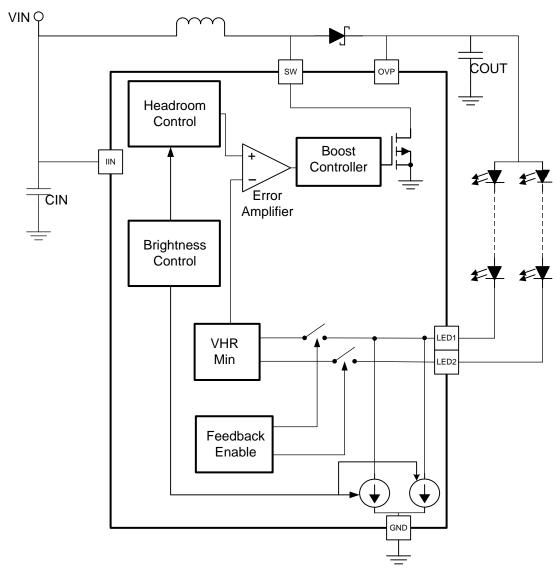

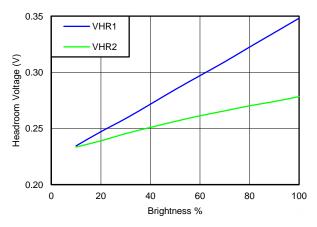

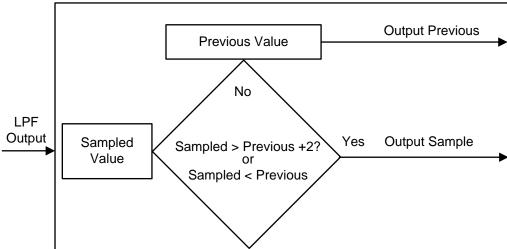

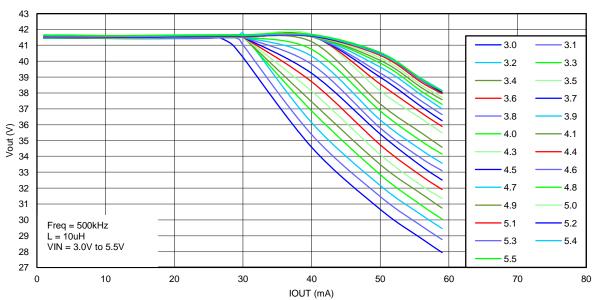

Reference Figure 75 and Figure 76 for the following description.

The adaptive headroom circuit controls the Boost output voltage to provide the minimal headroom voltage necessary for the current sinks to provide the specified ILED current. The headroom voltage is fed back to the Error Amplifier to dynamically adjust the Boost output voltage. The Error Amplifier's reference voltage is adjusted as the brightness level is changed, since the currents sinks require less headroom at lower ILED currents than at higher ILED currents. Note that the VHR Min block dynamically selects the LED string that requires the higher Boost voltage to maintain the ILED current, this string will have the lower headroom voltage. In Figure 76 this is LED string 2. The headroom voltage on LED string 1 is higher, but this is due to LED string 2 have an overall higher forward voltage than LED string 1. LED strings that have closely matched forward voltages will have closely matched headroom voltages and better overall efficiency.

In a single string LED configuration the Feedback enable must be enabled for only that string (LED1 or LED2). The adaptive headroom circuit is control by that single string. In a two string LED configuration the Feedback enable must be enabled for both strings (LED1 and LED2). The VHR Min block then dynamically selects the LED string to control the adaptive headroom circuit.

Figure 75. Adaptive Headroom Block Diagram

Figure 76. Typical Headroom Voltage Curves

#### **Current Sinks**

LED1 and LED2 control the current up to a 40V LED string voltage. Each current sink has 5-bit full-scale current programmability and 8-bit brightness control. Either current sink has its current set through a dedicated brightness register and can additionally be controlled via the PWM input.

#### **Current String Biasing**

Each current string can be powered from the LM3630A's boost or from an external source. When powered from an external source the feedback input for either current sink can be disabled in the Configuration register so it no longer controls the boost output voltage.

#### **Full-Scale LED Current**

The LM3630A's full-scale current is programmable with 32 different full scale levels. The full-scale current is the LED current in the control bank when the brightness code is at max code (0xFF). The 5 bit full-scale current vs code is given by the following equation:

ILED FULLSCALE =

$$5 \text{ mA} + \text{Code x } 0.75 \text{ mA}$$

(1)

With a maximum full-scale current of 28.5 mA.

#### **Brightness Register**

Each control bank has its own 8-bit brightness register. The brightness register code and the full-scale current setting determine the LED current depending on the programmed mapping mode.

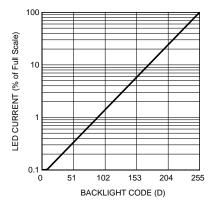

#### **Exponential Mapping**

In exponential mapping mode the brightness code to backlight current transfer function is given by the equation:

$$I_{LED} = I_{LED\_FULLSCALE} \times 0.85^{\left[44 - \frac{\left(\frac{\text{Code} + 1}{5.81818}\right)}{5.81818}\right]} \times D_{PWM}$$

(2)

Where I<sub>LED\_FULLSCALE</sub> is the full-scale LED current setting, Code is the backlight code in the brightness register, and DPWM is the PWM input duty cycle. Figure 77 and Figure 78 show the approximate backlight code to LED current response using exponential mapping mode. Figure 77 shows the response with a linear Y axis, and Figure 78 shows the response with a logarithmic Y axis. In exponential mapping mode the current ramp (either up or down) appears to the human eye as a more uniform transition then the linear ramp. This is due to the logarithmic response of the eye.

Figure 77. Exponential Mapping Mode (Linear Scale)

Figure 78. Exponential Mapping Mode (Log Scale)

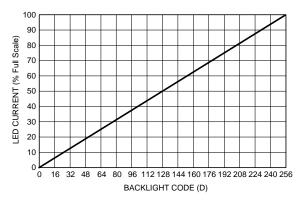

#### **Linear Mapping**

In linear mapping mode the brightness code to backlight current has a linear relationship and follows the equation:

$$I_{LED} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times \text{Code } \times D_{PWM}$$

(3)

Where I<sub>LED\_FULLSCALE</sub> is the full scale LED current setting, Code is the backlight code in the brightness register, and DPWM is the PWM input duty cycle. Figure 79 shows the backlight code to LED current response using linear mapping mode. The Configuration register must be set to enable linear mapping.

Figure 79. Linear Mapping Mode

## **LED Current Ramping**

## Startup/Shutdown Ramp

The LED current turn on time from 0 to the initial LED current set-point is programmable. Similarly, the LED current shutdown time to 0 is programmable. Both the startup and shutdown times are independently programmable with 8 different levels. The Startup times are independently programmable from the Shutdown times, but not independently programmable for each Control bank. For example, programming a Start-up or Shutdown time, programs the same ramp time for each Control Bank. The Startup time is used when the device is first enabled to a non-zero brightness value. The Shutdown time is used when the brightness value is programmed to zero. If HWEN is used to disable the device, the action is immediate and the Shutdown time is not used. The zero code does take a small amount of time which is approximately 0.5 ms.

Table 2. Startup/Shutdown Times

| Code | Startup Time | Shutdown Time |  |

|------|--------------|---------------|--|

| 000  | 4 ms         | 0             |  |

Table 2. Startup/Shutdown Times (continued)

| Code | Startup Time  | Shutdown Time |

|------|---------------|---------------|

| 001  | 261 ms        | 261 ms        |

| 010  | 522 ms 522 ms |               |

| 011  | 1.045s        | 1.045s        |

| 100  | 2.091s        | 2.091s        |

| 101  | 4.182s        | 4.182s        |

| 110  | 8.364s        | 8.364s        |

| 111  | 16.73s        | 16.73s        |

#### **Run-Time Ramp**

Current ramping from one brightness level to the next is programmable. There are 8 different ramp up times and 8 different ramp down times. The ramp up time is independently programmable from the ramp down time, but not independently programmable for each Control Bank. For example, programming a ramp up time or a ramp down time will program the same ramp time for each control bank. The run time ramps are used whenever the device is enabled with a non-zero brightness value and a new non-zero brightness value is written.

**Table 3. LED Current Run Ramp Times**

| Code | Ramp-Up Time | Ramp-Down Time |

|------|--------------|----------------|

| 000  | 0            | 0              |

| 001  | 261 ms       | 261 ms         |

| 010  | 522 ms       | 522 ms         |

| 011  | 1.045s       | 1.045s         |

| 100  | 2.091s       | 2.091s         |

| 101  | 4.182s       | 4.182s         |

| 110  | 8.364s       | 8.364s         |

| 111  | 16.73s       | 16.73s         |

#### **Test Features**

The LM3630A contains an LED open, an LED short, and Over Voltage manufacturing fault detection. This fault detection is designed to be used during the manufacturing process only and not normal operation. These faults do not set the INTN pin.

#### Open LED String (LED1 and LED2)

An open LED string is detected when the voltage at the input to either LED1 or LED2 has fallen below 200 mV and the boost output voltage has hit the OVP threshold. This test assumes that the LED string that is being detected for an open is being powered from the boost output (Feedback Enabled). For an LED string not connected to the boost output, and connected to another voltage source, the boost output would not trigger the OVP flag. In this case an open LED string would not be detected.

#### **Shorted LED String**

The LM3630A features an LED short fault flag indicating if either of the LED strings have experienced a short. There are two methods that can trigger a short in the LED strings

- An LED current sink with feedback enabled and the difference between OVP input and the LED current sink input voltage goes below 1V.

- 2. An LED current sink is configured with feedback disabled (not powered from the boost output) and the difference between VIN and the LED current sink input voltage goes below 1V.

#### Over-Voltage Protection (Manufacturing Fault Detection and Shutdown)

The LM3630A provides an Over-Voltage Protection (OVP) mechanism specifically for manufacturing test where a display may not be connected to the device. The over voltage protection threshold (OVP) on the LM3630A has 4 different programmable options (16V, 24V, 32V, and 40V). The manufacturing protection is enabled in the Fault Status register bit 0. When enabled, this feature will cause the boost converter to shutdown anytime the selected OVP threshold is exceeded. The OVP\_fault bit in the Fault Status register will be set to one. The boost converter will not resume operation until the LM3630A is reset with either a write to the Software Reset bit in the Software Reset register or a cycling of the HWEN pin. The reset will clear the fault.

## **Fault Flags/Protection Features**

The Interrupt Status register contains the status of the protection circuits of the LM3630A. The corresponding bits will be set to one if an OVP, OCP, or TSD event occurs. These faults do set the INTN pin when the corresponding bit is set in the Interrupt Enable register.

#### Over-Voltage Protection (Inductive Boost Operation)

The over-voltage protection threshold (OVP) on the LM3630A has 4 different programmable options (16V, 24V, 32V, and 40V). Over voltage protection protects the device and associated circuitry from high voltages in the event the feedback enabled LED string becomes open. During normal operation, the LM3630A's inductive boost converter will boost the output up so as to maintain at least 300 mV at the active current sink inputs. When a high-voltage LED string becomes open the feedback mechanism is broken, and the boost converter will inadvertently over boost the output. When the output voltage reaches the over voltage protection (OVP) threshold the boost converter will stop switching, thus allowing the output node to discharge. When the output discharges to VOVP – 1V the boost converter will begin switching again. The OVP sense is at the OVP pin, so this pin must be connected directly to the inductive boost output capacitor's positive terminal.

For current sinks that have feedback disabled the over voltage sense mechanism is not in place to protect from potential over-voltage conditions. In this situation the application must ensure that the voltage at LED1 or LED2 doesn't exceed 40V.

The default setting for OVP is set at 24V. For applications that require higher than 24V at the boost output the OVP threshold will have to be programmed to a higher level at power up.

#### **Current Limit**

The switch current limit for the LM3630A's inductive boost is set at 1A. When the current through the NFET switch hits this over current protection threshold (OCP) the device turns the NFET off and the inductor's energy is discharged into the output capacitor. Switching is then resumed at the next cycle. The current limit protection circuitry can operate continuously each switch cycle. The result is that during high output power conditions the device can continuously run in current limit. Under these conditions the LM3630A's inductive boost converter stops regulating the headroom voltage across the high voltage current sinks. This results in a drop in the LED current.

#### **Thermal Shutdown**

The LM3630A contains thermal shutdown protection. In the event the die temperature reaches +140°C, the boost power supply and current sinks will shut down until the die temperature drops to typically +125°C.

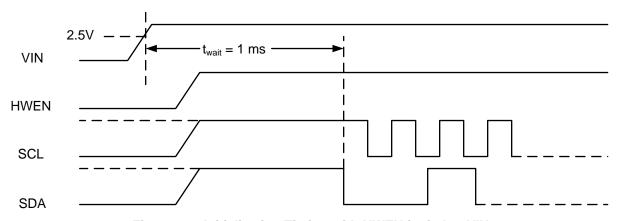

## **Initialization Timing**

#### Initialization Timing with HWEN tied to VIN

If the HWEN input is tied to VIN, then the  $t_{WAIT}$  time starts when VIN crosses 2.5V as shown below. The initial I<sup>2</sup>C transaction can occur after the  $t_{WAIT}$  time expires. Any I<sup>2</sup>C transaction during the  $t_{WAIT}$  period will be NAK'ed.

Figure 80. Initialization Timing with HWEN is tied to VIN

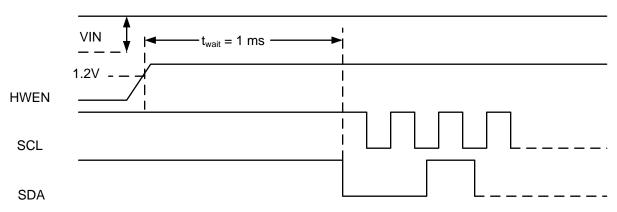

## Initialization Timing with HWEN driven by GPIO

If the HWEN input is driven by a GPIO then the  $t_{WAIT}$  time starts when HWEW crosses 1.2V as shown below. The initial  $I^2C$  transaction can occur after the  $t_{WAIT}$  time expires. Any  $I^2C$  transaction during the  $t_{WAIT}$  period will be NAK'ed

Figure 81. Initialization Timing with HWEN driven by a GPIO

#### **Initialization after Software Reset**

The time between the  $I^2C$  transaction that issues the software reset, and the subsequent  $I^2C$  transaction (ie to configure the LM3630A) must be at greater or equal to the  $t_{WAIT}$  period of 1ms. Any  $I^2C$  transaction during the  $t_{WAIT}$  period will be NAK'ed

#### I<sup>2</sup>C-COMPATIBLE INTERFACE

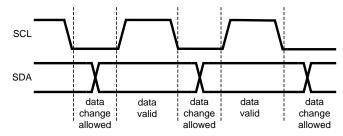

## **Data Validity**

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

Figure 82. Data Validity Diagram

A pull-up resistor between the controller's VIO line, and SDA must be greater than [(VIO- $V_{OL}$ ) / 3mA] to meet the  $V_{OL}$  requirement on SDA. Using a larger pull-up resistor results in lower switching current with slower edges, while using a smaller pull-up results in higher switching currents with faster edges.

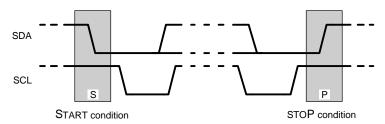

#### **Start And Stop Conditions**

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 83. Start and Stop Conditions

### **Transfering Data**

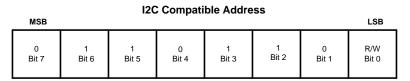

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LM3630A pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The LM3630A generates an acknowledge after each byte is received.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3630A address is 36h. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Figure 84.  $I^2$ C-Compatible Chip Address (0x36), SEL = 0

####

Figure 85.  $I^2$ C-Compatible Chip Address (0x38), SEL = 1

## LM3630A I<sup>2</sup>C Register Map

This table summarizes LM3630A I<sup>2</sup>C-compatible register usage and shows default register bit values after reset, as programmed by the factory. The following sub-sections provide additional details on the use of individual registers. Register bits which are blank in the following tables are considered undefined. Undefined bits should be ignored on reads and written as zero.

| Slav             | Slave Address [0x36h for SEL = 0, 0x38h for SEL = 1] |      |                      |  |  |  |

|------------------|------------------------------------------------------|------|----------------------|--|--|--|

|                  | Base Registers                                       |      |                      |  |  |  |

| Register Name    | Address                                              | Туре | Default Reset Values |  |  |  |

| Control          | 0x00                                                 | R/W  | 0xC0                 |  |  |  |

| Configuration    | 0x01                                                 | R/W  | 0x18                 |  |  |  |

| Boost Control    | 0x02                                                 | R/W  | 0x38                 |  |  |  |

| Brightness A     | 0x03                                                 | R/W  | 0x00                 |  |  |  |

| Brightness B     | 0x04                                                 | R/W  | 0x00                 |  |  |  |

| Current A        | 0x05                                                 | R/W  | 0x1F                 |  |  |  |

| Current B        | 0x06                                                 | R/W  | 0x1F                 |  |  |  |

| On/Off Ramp      | 0x07                                                 | R/W  | 0x00                 |  |  |  |

| Run Ramp         | 0x08                                                 | R/W  | 0x00                 |  |  |  |

| Interrupt Status | 0x09                                                 | R/W  | 0x00                 |  |  |  |

| Interrupt Enable | 0x0A                                                 | R/W  | 0x00                 |  |  |  |

| Fault Status     | 0x0B                                                 | R/W  | 0x00                 |  |  |  |

| Software Reset   | 0x0F                                                 | R/W  | 0x00                 |  |  |  |

| PWM Out Low      | 0x12                                                 | Read | 0x00                 |  |  |  |

| PWM Out High     | 0x13                                                 | Read | 0x00                 |  |  |  |

| Revision         | 0x1F                                                 | Read | 0x02                 |  |  |  |

| Filter Strength  | 0x50                                                 | R/W  | 0x00                 |  |  |  |

## **Register Descriptions**

## Control (Offset = 0x00, Default = 0xC0)

|              |                             |      | Register                                                                                      | Bits              |                     |                    |           |

|--------------|-----------------------------|------|-----------------------------------------------------------------------------------------------|-------------------|---------------------|--------------------|-----------|

| 7            | 6                           | 5    | 4                                                                                             | 3                 | 2                   | 1                  | 0         |

| SLEEP_CMD    | SLEEP_<br>STATUS            |      | LINEAR_A                                                                                      | LINEAR_B          | LED_A_EN            | LED_B_EN           | LED2_ON_A |

| Name         | Name Bit Access Description |      |                                                                                               |                   |                     |                    |           |

| SLEEP_CMD    | 7                           | R/W  | The device is put into sleep mode when set to '1'                                             |                   |                     |                    |           |

| SLEEP_STATUS | 6                           | Read | Reflects the sleep                                                                            | mode status. A    | '1' indicates the p | art is in sleep mo | de.       |

|              |                             |      | Used to determine when part has entered or exited sleep mode after writing the SLEEP_CMD bit. |                   |                     |                    |           |

|              | 5                           | Read |                                                                                               |                   |                     |                    |           |

| LINEAR_A     | 4                           | R/W  | Enables the linear                                                                            | r output mode for | Bank A when se      | t to '1'.          |           |

| LINEAR_B     | 3                           | R/W  | Enables the linear                                                                            | r output mode for | Bank B when se      | t to '1'.          |           |

| LED_EN_A     | 2                           | R/W  | Enables the LED A output                                                                      |                   |                     |                    |           |

| LED_EN_B     | 1                           | R/W  | Enables the LED B output                                                                      |                   |                     |                    |           |

| LED2_ON_A    | 0                           | R/W  | Connect the LED                                                                               | 2 output to Bank  | A Control           |                    | •         |

## Configuration (Offset = 0x01, Default = 0x18)

| Register Bits |     |        |                            |                            |         |          |          |  |

|---------------|-----|--------|----------------------------|----------------------------|---------|----------|----------|--|

| 7             | 6   | 5      | 4                          | 3                          | 2       | 1        | 0        |  |

|               |     |        | FB_EN_B                    | FB_EN_A                    | PWM_LOW | PWM_EN-B | PWM_EN_A |  |

| Name          | Bit | Access | Description                |                            |         |          |          |  |

|               | 7   | Read   |                            |                            |         |          |          |  |

|               | 6   | Read   |                            |                            |         |          |          |  |

|               | 5   | Read   |                            |                            |         |          |          |  |

| FB_EN_B       | 4   | R/W    | Enable Feedback            | on Bank B                  |         |          |          |  |

| FB_EN_A       | 3   | R/W    | Enable Feedback            | on Bank A                  |         |          |          |  |

| PWM_LOW       | 2   | R/W    | Sets the PWM to a          | Sets the PWM to active low |         |          |          |  |

| PWM_EN_B      | 1   | R/W    | Enables the PWM for Bank B |                            |         |          |          |  |

| PWM_EN_A      | 0   | R/W    | Enables the PWM            | for Bank A                 |         |          |          |  |

## Boost Control (Offset = 0x02, Default = 0x38)

|            |              |              | Registe                                                                                                                                                      | r Bits                |                  |       |       |  |

|------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|-------|-------|--|

| 7          | 6            | 5            | 4                                                                                                                                                            | 3                     | 2                | 1     | 0     |  |

|            | BOOST_OVP[1] | BOOST_OVP[0] | BOOST_OCP[1]                                                                                                                                                 | BOOST_OCP[0]          | SLOW_STAR<br>T   | SHIFT | FMODE |  |

| Name       | Bit          | Access       | Description                                                                                                                                                  |                       |                  |       |       |  |

|            | 7            | Read         |                                                                                                                                                              |                       |                  |       |       |  |

| BOOST_OVP  | 6:5          | R/W          | Selects the voltage limit for over-voltage protection:  00 = 16V  01 = 24V  10 = 32V  11 = 40V                                                               |                       |                  |       |       |  |

| BOOST_OCP  | 4:3          | R/W          | Selects the curre<br>00 = 600 mA<br>01 = 800 mA<br>10 = 1.0A<br>11 = 1.2A                                                                                    | nt limit for over-cur | rent protection: |       |       |  |

| SLOW_START | 2            | R/W          | Slows the boost of                                                                                                                                           | output transition     |                  |       |       |  |

| SHIFT      | 1            | R/W          | Enables the alternate oscillator frequencies: For FMODE = 0: SHIFT = 0F = 500 kHz; SHIFT 1F = 560 kHz For FMODE = 1: SHIFT = 0F = 1 MHz; SHIFT 1F = 1120 MHz |                       |                  |       |       |  |

| FMODE      | 0            | R/W          | Selects the boost 0 = 500 kHz, 1 =                                                                                                                           |                       |                  |       |       |  |

# Brightness A (Offset = 0x03, Default = 0x00)<sup>(1)</sup>

|      | Register Bits |        |                                                                                                          |      |      |      |      |  |  |  |  |

|------|---------------|--------|----------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| 7    | 6             | 5      | 4                                                                                                        | 3    | 2    | 1    | 0    |  |  |  |  |

| A[7] | A[6]          | A[5]   | A[4]                                                                                                     | A[3] | A[2] | A[1] | A[0] |  |  |  |  |

| Name | Bit           | Access | Description                                                                                              |      |      |      |      |  |  |  |  |

| Α    | [7:0]         | R/W    | Sets the 8-bit brightness value for outputs connected to Bank A. Minimum brightness setting is code 04h. |      |      |      |      |  |  |  |  |

<sup>(1)</sup> These registers will not update if the device is in Sleep Mode (Control: SLEEP\_STATUS = 1).

# Brightness B (Offset = 0x04, Default = 0x00)<sup>(1)</sup>

|      | Register Bits |        |                                                                                                          |      |      |      |      |  |  |  |  |

|------|---------------|--------|----------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| 7    | 6             | 5      | 4                                                                                                        | 3    | 2    | 1    | 0    |  |  |  |  |

| B[7] | B[6]          | B[5]   | B[4]                                                                                                     | B[3] | B[2] | B[1] | B[0] |  |  |  |  |

| Name | Bit           | Access | Description                                                                                              |      |      |      |      |  |  |  |  |

| В    | [7:0]         | R/W    | Sets the 8-bit brightness value for outputs connected to Bank B. Minimum brightness setting is code 04h. |      |      |      |      |  |  |  |  |

<sup>(1)</sup> These registers will not update if the device is in Sleep Mode (Control: SLEEP\_STATUS = 1).

# Current A (Offset = 0x05, Default 0x1F)

|             | Register Bits |        |                                                                                                                                                                                                                                                                                                                                                 |                    |                   |            |      |  |  |  |  |  |

|-------------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------|------|--|--|--|--|--|

| 7           | 6             | 5      | 4                                                                                                                                                                                                                                                                                                                                               | 3                  | 2                 | 1          | 0    |  |  |  |  |  |

| Hysteresis  | Lower Bound   |        | A[4]                                                                                                                                                                                                                                                                                                                                            | A[3]               | A[2]              | A[1]       | A[0] |  |  |  |  |  |

| Name        | Bit           | Access | Description                                                                                                                                                                                                                                                                                                                                     |                    |                   |            |      |  |  |  |  |  |

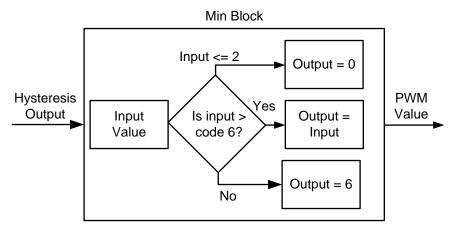

| Hysteresis  | 7             | R/W    | Determines the hysteresis of the PWM Sampler. Clearing this bit, the PWM sampler changes its output upon detecting at least 3 equivalent code changes on the PWM input. Setting this bit, the PWM sampler changes its output upon detecting 2 equivalent code changes on the PWM input.                                                         |                    |                   |            |      |  |  |  |  |  |

| Lower Bound | 6             | R/W    | Determines the lower bound of the PWM Sampler. Clearing this bit, the PWM sampler outputs code 6 when it detects equivalent codes 2 thru 6; and code 0 when it detects equivalent codes 0 thru 1. Setting this bit, the PWM sampler can output codes below 6, based upon the Hysteresis setting and equivalent code sampled from the input PWM. |                    |                   |            |      |  |  |  |  |  |

|             | 5             | Read   |                                                                                                                                                                                                                                                                                                                                                 |                    |                   |            |      |  |  |  |  |  |

| Α           | [4:0]         | R/W    | Sets the 5-bit full-se                                                                                                                                                                                                                                                                                                                          | cale current for o | outputs connected | to Bank A. |      |  |  |  |  |  |

# Current B (Offset = 0x06, Default = 0x1F)

|      | Register Bits |        |                        |                                                                   |      |      |      |  |  |  |  |

|------|---------------|--------|------------------------|-------------------------------------------------------------------|------|------|------|--|--|--|--|

| 7    | 6             | 5      | 4                      | 3                                                                 | 2    | 1    | 0    |  |  |  |  |

|      |               |        | B[4]                   | B[3]                                                              | B[2] | B[1] | B[0] |  |  |  |  |

| Name | Bit           | Access | Description            |                                                                   |      |      |      |  |  |  |  |

| В    | [4:0]         | R/W    | Sets the 5-bit full-se | Sets the 5-bit full-scale current for outputs connected to Bank B |      |      |      |  |  |  |  |

## On/Off Ramp (Offset = 0x07, Default 0x00)

|         | Register Bits |            |                               |               |           |           |           |  |  |  |  |

|---------|---------------|------------|-------------------------------|---------------|-----------|-----------|-----------|--|--|--|--|

| 7       | 6             | 5          | 4                             | 3             | 2         | 1         | 0         |  |  |  |  |

|         |               | T_START[2] | T_START[1]                    | T_START[0]    | T_SHUT[2] | T_SHUT[1] | T_SHUT[0] |  |  |  |  |

| Name    | Bit           | Access     | Description                   |               |           |           |           |  |  |  |  |

|         | 7             | Read       |                               |               |           |           |           |  |  |  |  |

|         | 6             | Read       |                               |               |           |           |           |  |  |  |  |

| T_START | [5:3]         | R/W        | Ramp time for startup events. |               |           |           |           |  |  |  |  |

| T_SHUT  | [2:0]         | R/W        | Ramp time for shu             | tdown events. | ·         | ·         |           |  |  |  |  |

| Code | Start-Up Time | Shutdown Time |

|------|---------------|---------------|

| 000  | 4 ms          | 0*            |

| 001  | 261 ms        | 261 ms        |

| 010  | 522 ms        | 522 ms        |

| 011  | 1.045s        | 1.045s        |

| 100  | 2.091s        | 2.091s        |

| 101  | 4.182s        | 4.182s        |

| 110  | 8.364s        | 8.364s        |

| 111  | 16.73s        | 16.73s        |

<sup>\*</sup>Code 0 results in approximately 0.5 ms ramp time.

# Run Ramp (Offset = 0x08, Default = 0x00)

|        | Register Bits |         |                         |          |           |           |           |  |  |  |  |

|--------|---------------|---------|-------------------------|----------|-----------|-----------|-----------|--|--|--|--|

| 7      | 6             | 5       | 4                       | 3        | 2         | 1         | 0         |  |  |  |  |

|        |               | T_UP[2] | T_UP[1]                 | T_UP[0]  | T_DOWN[2] | T_DOWN[1] | T_DOWN[0] |  |  |  |  |

| Name   | Bit           | Access  | Description             |          |           |           |           |  |  |  |  |

|        | 7             | Read    |                         |          |           |           |           |  |  |  |  |

|        | 6             | Read    |                         |          |           |           |           |  |  |  |  |

| T_UP   | [5:3]         | R/W     | Time for ramp-up events |          |           |           |           |  |  |  |  |

| T_DOWN | [2:0]         | R/W     | Time for ramp-dow       | n events |           |           |           |  |  |  |  |

| Code | Ramp-Up Time | Ramp-down Time |

|------|--------------|----------------|

| 000  | 0*           | 0*             |

| 001  | 261 ms       | 261 ms         |

| 010  | 522 ms       | 522 ms         |

| 011  | 1.045s       | 1.045s         |

| 100  | 2.091s       | 2.091s         |

| 101  | 4.182s       | 4.182s         |

| 110  | 8.364s       | 8.364s         |

| 111  | 16.73s       | 16.73s         |

<sup>\*</sup>Code 0 results in approximately 0.5 ms ramp time.

#### Interrupt Status (Offset = 0x09, Default = 0x00)

|      | Register Bits |        |                    |                    |     |     |     |  |  |  |  |

|------|---------------|--------|--------------------|--------------------|-----|-----|-----|--|--|--|--|

| 7    | 6             | 5      | 4                  | 3                  | 2   | 1   | 0   |  |  |  |  |

|      |               |        |                    |                    | OCP | OVP | TSD |  |  |  |  |

| Name | Bit           | Access | Description        |                    |     |     |     |  |  |  |  |

|      | 7             | Read   |                    |                    |     |     |     |  |  |  |  |

|      | 6             | Read   |                    |                    |     |     |     |  |  |  |  |

|      | 5             | Read   |                    |                    |     |     |     |  |  |  |  |

|      | 4             | Read   |                    |                    |     |     |     |  |  |  |  |

|      | 3             | Read   |                    |                    |     |     |     |  |  |  |  |

| OCP  | 2             | R/W    | An over-current co | ondition occurred. |     |     |     |  |  |  |  |

| OVP  | 1             | R/W    | An over-voltage co | ondition occurred  |     |     |     |  |  |  |  |

| TSD  | 0             | R/W    | A thermal shutdov  | vn event occurred  | i.  |     |     |  |  |  |  |

The interrupt status register is cleared upon a read of the register. If the condition that caused the interrupt is still present, then the bit will be set to one again and another interrupt is signaled on the INTN output pin. The interrupt status register is not cleared if the device is in sleep mode (Control: SLEEP\_STATUS = 1). To disconnect the interrupt condition from the INTN pin during sleep mode, disable the fault connection in the Interrupt Enable register. An interrupt condition will set the status bit and cause an event on the INTN pin only if the corresponding bit in the Interrupt Enable register is one and the Global Enable bit is also one.

## Interrupt Enable (Offset = 0x0A, Default = 0x00)

|        | Register Bits |        |                      |                      |                    |     |     |  |  |  |  |

|--------|---------------|--------|----------------------|----------------------|--------------------|-----|-----|--|--|--|--|

| 7      | 6             | 5      | 4                    | 3                    | 2                  | 1   | 0   |  |  |  |  |

|        |               |        |                      |                      | OCP                | OVP | TSD |  |  |  |  |

| Name   | Bit           | Access | Description          |                      |                    |     |     |  |  |  |  |

| GLOBAL | 7             | R/W    | Set to '1' to enable | e interrupts to driv | e the INTN pin.    |     |     |  |  |  |  |

|        | 6             | Read   |                      |                      |                    |     |     |  |  |  |  |

|        | 5             | Read   |                      |                      |                    |     |     |  |  |  |  |

|        | 4             | Read   |                      |                      |                    |     |     |  |  |  |  |

|        | 3             | Read   |                      |                      |                    |     |     |  |  |  |  |

| OCP    | 2             | R/W    | Set to '1' to enable | the over-current     | condition interrup | ot. |     |  |  |  |  |

| OVP    | 1             | R/W    | Set to '1' to enable | the over-voltage     | condition interrup | ot. |     |  |  |  |  |

| TSD    | 0             | R/W    | Set to '1' to enable | the thermal shu      | tdown interrupt.   |     |     |  |  |  |  |

## Fault Status (Offset = 0x0B, Default = 0x00)

|            |     |        | Registe                                | er Bits           |                  |           |          |  |

|------------|-----|--------|----------------------------------------|-------------------|------------------|-----------|----------|--|

| 7          | 6   | 5      | 4                                      | 3                 | 2                | 1         | 0        |  |

|            |     | OPEN   | LED2_SHORT                             | LED1_SHORT        | SHORT_EN         | OVP_FAULT | OVP_F_EN |  |

| Name       | Bit | Access | Description                            |                   |                  |           |          |  |

|            | 7   | Read   |                                        |                   |                  |           |          |  |

|            | 6   | Read   |                                        |                   |                  |           |          |  |