LM2623-Q1

ZHCSGW9-OCTOBER 2017

# 基于门控振荡器的 LM2623-Q1 汽车类直流/直流升压转换器

# 1 特性

- 符合 AEC-Q100 标准的汽车 应用应用的 32 通道 AFE:

- 器件温度等级 1:环境工作温度范围为 -40°C 至 125°C

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C4A

- 在非常宽的负载范围内具有较高的效率

- 非常低的输出电压纹波

- 高达 2MHz 的开关频率

- 0.9V 至 14V 工作电压范围

- 1.1V 启动电压

- 1.24V 至 14V 可调节输出电压

- 0.17Ω 内部 MOSFET

- 稳压器效率高达 90%

- 典型的工作电流为 80μA (输入到电源的 V<sub>DD</sub> 引 脚)

- 低关断电流 (I<sub>Q</sub> < 2.5μA)</li>

- 4mm x 4mm 热增强型 WSON 封装选项

# 2 应用

- 汽车摄像机

- 汽车雷达

- 汽车 GPS

- 闪存存储器编程

- 白光 LED 驱动器

# 3 说明

LM2623-Q1 是一款用于汽车系统的高效通用型升压直流/直流开关稳压器。此器件支持 0.9V 至 14V 之间的输入电压,并可将其转换为 1.24V 至 14V 的稳压输出电压。

为了适应多种 应用,LM2623-Q1 允许设计人员编程设定输出电压、工作频率(300kHz 至 2MHz)和占空比(17% 至 90%)以优化性能。所选值可以是固定的,也可以随输入电压或输入/输出电压比而变化。

LM2623-Q1 采用非常简单的开/关调节模式在较宽的工作范围内实现良好效率和稳定运行。此器件通常情况下通过跳脉冲(脉冲频率调制 (PFM))方式来调压。

请参阅Non-Linear Effect 和Choosing the Correct C3 Capacitor 以便在电路板设计完成之前解决所有设计难题。

# 器件信息(1)

| 器件型号      | 封装        | 封装尺寸(标称值)       |

|-----------|-----------|-----------------|

| LM2623-Q1 | WSON (14) | 4.00mm x 4.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

Copyright © 2017, Texas Instruments Incorporated

# 目录

| 1 | 特性 1                                 | 8  | Applications and Implementation | 11 |

|---|--------------------------------------|----|---------------------------------|----|

| 2 | 应用 1                                 |    | 8.1 Application Information     | 11 |

| 3 | 说明 1                                 |    | 8.2 Typical Application         | 11 |

| 4 | 修订历史记录 2                             | 9  | Power Supply Recommendations    | 13 |

| 5 | Pin Configuration and Functions3     | 10 | Layout                          | 14 |

| 6 | Specifications4                      |    | 10.1 Layout Guidelines          | 14 |

| • | 6.1 Absolute Maximum Ratings 4       |    | 10.2 Layout Example             | 15 |

|   | 6.2 ESD Ratings                      |    | 10.3 WSON Package Devices       | 15 |

|   | 6.3 Recommended Operating Conditions | 11 | 器件和文档支持                         | 16 |

|   | 6.4 Thermal Information              |    | 11.1 器件支持                       | 16 |

|   | 6.5 Electrical Characteristics       |    | 11.2 文档支持                       | 16 |

|   | 6.6 Typical Characteristics          |    | 11.3 接收文档更新通知                   | 16 |

| 7 | Detailed Description 8               |    | 11.4 社区资源                       |    |

|   | 7.1 Overview 8                       |    | 11.5 商标                         |    |

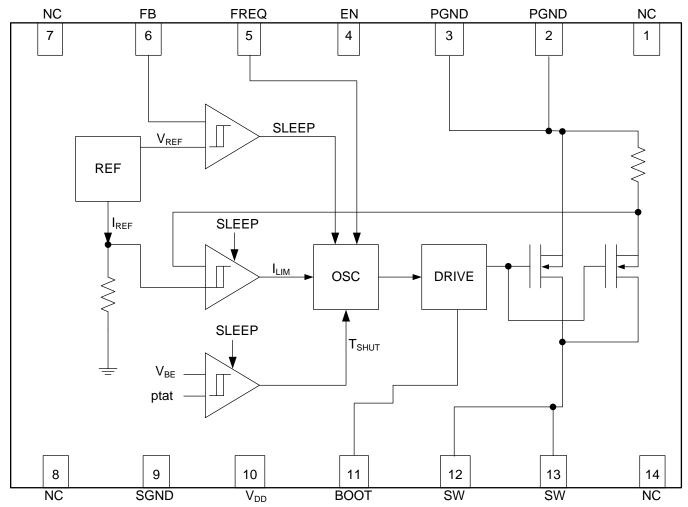

|   | 7.2 Functional Block Diagram 8       |    | 11.6 静电放电警告                     |    |

|   | 7.3 Feature Description 9            |    | 11.7 Glossary                   | 16 |

|   | 7.4 Device Functional Modes          | 12 | 机械、封装和可订购信息                     | 16 |

|   |                                      |    |                                 |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期          | 修订版本 | 说明    |

|-------------|------|-------|

| 2017 年 10 月 | *    | 初始发行版 |

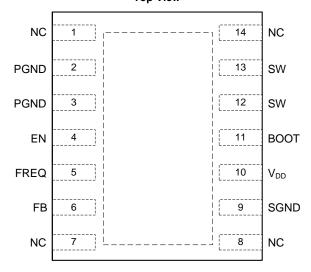

# **5 Pin Configuration and Functions**

# NHL Package 14-Pin WSON Top View

# **Pin Functions**

|        | PIN             | TVDE    | DESCRIPTION                                                                                                                         |

|--------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME            | TYPE    | DESCRIPTION                                                                                                                         |

| 1      | NC              | _       | No connect                                                                                                                          |

| 2, 3   | PGND            | GND     | Power ground (pins 2 and 3 must be shorted together)                                                                                |

| 4      | EN              | Digital | Active-low shutdown input                                                                                                           |

| 5      | FREQ            | Analog  | Frequency adjust; connect an external resistor between this pin and a voltage source sets the switching frequency of the LM2623-Q1. |

| 6      | FB              | Analog  | Output voltage feedback                                                                                                             |

| 7      | NC              | _       | No connect                                                                                                                          |

| 8      | NC              | _       | No connect                                                                                                                          |

| 9      | SGND            | GND     | Signal ground                                                                                                                       |

| 10     | V <sub>DD</sub> | Power   | Power supply for internal circuitry                                                                                                 |

| 11     | BOOT            | Analog  | Bootstrap supply for the gate drive of internal MOSFET power switch                                                                 |

| 12, 13 | SW              | Analog  | Drain of the internal MOSFET power switch (pins 12 and 13 <i>must</i> be shorted together)                                          |

| 14     | NC              | _       | No connect                                                                                                                          |

| DAP    | DAP             | Thermal | Solder to board for enhanced thermal dissipation; must be electrically isolated/floating.                                           |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                        |                                           | MIN  | MAX  | UNIT |

|------------------------|-------------------------------------------|------|------|------|

| Input pins             | SW pin voltage                            | -0.5 | 14.5 | V    |

|                        | BOOT, VDD, EN, and FB pins                | -0.5 | 10   | V    |

|                        | FREQ pin                                  |      | 100  | μΑ   |

| Power dissipation      | on (T <sub>A</sub> = 25°C) <sup>(3)</sup> |      | 500  | mW   |

| T <sub>J_MAX</sub> (3) |                                           |      | 150  | °C   |

| Storage temper         | ature, T <sub>stg</sub>                   | -55  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                         |                           | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|---------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins except 12 and 13 | ±2000 |      |

|                    |                         |                                                         | Pins 12 and 13            | ±1000 | V    |

|                    |                         | Charged device model (CDM), per A                       | ±500                      |       |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|              |                                           | MIN | NOM MAX  | UNIT |

|--------------|-------------------------------------------|-----|----------|------|

| Input pins   | V <sub>DD</sub> pin                       | 3   | 5        | ٧    |

|              | FB and EN pins                            | 0   | $V_{DD}$ | V    |

|              | BOOT pin                                  | 0   | 10       | ٧    |

| Operating ju | unction temperature range, T <sub>J</sub> | -40 | 125      | °C   |

# 6.4 Thermal Information

|                      |                                              | LM2623-Q1  |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | NHL (WSON) | UNIT |

|                      |                                              | 14 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 37.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 26.9       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 15.0       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 4.7        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office / Distributors for availability and specifications.

<sup>(3)</sup> The maximum power dissipation must be derated at elevated temparters and is dictated by T<sub>J-MAX</sub> (maximum junction temperature), R<sub>ΘJA</sub> (junction to ambient thermal resistance), and T<sub>A</sub> (ambient temperature). The maximum allowable power dissipation at any temperature is P<sub>D-MAX</sub> = (T<sub>J-MAX</sub> - T<sub>A</sub>)/R<sub>ΘJA</sub> or the number given in the Absolute Maximum Rating, whichever is lower.

# 6.5 Electrical Characteristics

Limits apply for  $T_J = 25^{\circ}C$  and  $V_{DD} = V_{OUT} = 3.3 \text{ V}$ , unless otherwise specified.

|                                                                                       | PARAMETER                                       | TEST CONDITIONS                                                              | MIN                 | TYP  | MAX                  | UNIT |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------|---------------------|------|----------------------|------|--|--|--|

| GENERAL $V_{DD\_ST}$ Start-up supply voltage 25°C $I_{LOAD} = 0 \text{ mA}^{(1)}$ 1.1 |                                                 |                                                                              |                     |      |                      |      |  |  |  |

| V <sub>DD_ST</sub>                                                                    | Start-up supply voltage 25°C                    | $I_{LOAD} = 0 \text{ mA}^{(1)}$                                              |                     |      | 1.1                  | V    |  |  |  |

| V <sub>IN_OP</sub>                                                                    | Minimum operating supply voltage (once started) | I <sub>LOAD</sub> = 0 mA                                                     |                     | 0.65 | 0.9                  | V    |  |  |  |

|                                                                                       |                                                 |                                                                              |                     | 1.24 |                      |      |  |  |  |

| $V_{FB}$                                                                              | FB pin voltage                                  | -40°C to 85°C                                                                | 1.2028              |      | 1.2772               | V    |  |  |  |

|                                                                                       |                                                 | -40°C to 125°C                                                               | 1.2028              |      | 1.2772               |      |  |  |  |

| V <sub>OUT_MA</sub>                                                                   | Maximum output voltage                          |                                                                              |                     | 14   |                      | ٧    |  |  |  |

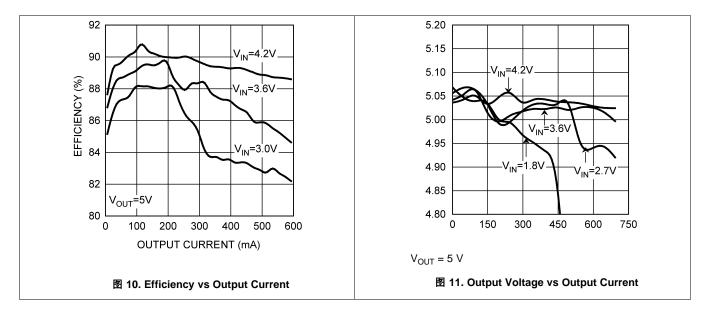

|                                                                                       |                                                 | V <sub>IN</sub> = 3.6 V; V <sub>OUT</sub> = 5 V, I <sub>LOAD</sub> = 500 mA  |                     | 87%  |                      |      |  |  |  |

| η                                                                                     | Efficiency                                      | $V_{IN} = 2.5 \text{ V}; V_{OUT} = 3.3 \text{ V}, I_{LOAD} = 200 \text{ mA}$ |                     | 87%  |                      |      |  |  |  |

| D                                                                                     | Switch duty cycle                               |                                                                              |                     | 17%  |                      |      |  |  |  |

|                                                                                       | Operating quiescent current <sup>(2)</sup>      | FB pin > 1.3 V, EN pin at V <sub>DD</sub>                                    |                     | 80   |                      |      |  |  |  |

| I <sub>DD</sub>                                                                       |                                                 | FB pin > 1.3 V, EN pin at $V_{DD}$ , $-40^{\circ}C$ to 85°C                  |                     |      | 110                  | μΑ   |  |  |  |

|                                                                                       |                                                 | FB pin > 1.3 V, EN pin at V <sub>DD</sub> , –40°C to 125°C                   |                     |      | 110                  |      |  |  |  |

|                                                                                       | Shutdown quiescent current <sup>(3)</sup>       | V <sub>DD</sub> , BOOT, and SW pins at 5 V, EN pin < 200 mV                  |                     | 0.01 |                      |      |  |  |  |

| I <sub>SD</sub>                                                                       |                                                 | V <sub>DD</sub> , BOOT, and SW pins at 5 V, EN pin < 200 mV, –40°C to 85°C   |                     |      | 2.5                  | μΑ   |  |  |  |

|                                                                                       |                                                 | V <sub>DD</sub> , BOOT, and SW pins at 5 V, EN pin < 200 mV, -40°C to 125°C  |                     |      | 2.5                  |      |  |  |  |

| I <sub>CL</sub>                                                                       | Switch peak current limit                       |                                                                              | 2.2                 | 2.85 |                      | Α    |  |  |  |

|                                                                                       |                                                 |                                                                              |                     | 0.17 |                      |      |  |  |  |

| R <sub>DSON</sub>                                                                     | MOSFET switch on resistance                     | -40°C to 85°C                                                                |                     |      | 0.26                 | Ω    |  |  |  |

|                                                                                       |                                                 | -40°C to 125°                                                                |                     |      | 0.26                 |      |  |  |  |

| ENABLE                                                                                | SECTION                                         |                                                                              |                     |      |                      |      |  |  |  |

| V <sub>EN LO</sub>                                                                    | EN pin voltage low <sup>(4)</sup>               | -40°C to 85°C                                                                |                     |      | 0.15 V <sub>DD</sub> | V    |  |  |  |

| VEN_LO                                                                                | Liv pili voltage low                            | -40°C to 125°C                                                               |                     |      | 0.15 V <sub>DD</sub> | v    |  |  |  |

| V                                                                                     | EN pin voltage high <sup>(4)</sup>              | -40°C to 85°C                                                                | 0.7 V <sub>DD</sub> |      |                      | V    |  |  |  |

| V <sub>EN_HI</sub>                                                                    | Liv pin voitage night                           | -40°C to 125°C                                                               | $0.7~V_{DD}$        |      |                      |      |  |  |  |

V<sub>DD</sub> tied to BOOT and EN pins. Frequency pin tied to V<sub>DD</sub> through 121-KΩ resistor. V<sub>DD\_ST</sub> = V<sub>DD</sub> when start-up occurs. V<sub>IN</sub> is V<sub>DD</sub> + D1 voltage (usually 10 mV to 50 mV at start-up).

This is the current into the V<sub>DD</sub> pin.

This is the total current into pins V<sub>DD</sub>, BOOT, SW, and FREQ.

When the EN pin is below V<sub>EN\_LO</sub>, the regulator is shut down; when it is above V<sub>EN\_HI</sub>, the regulator is operating.

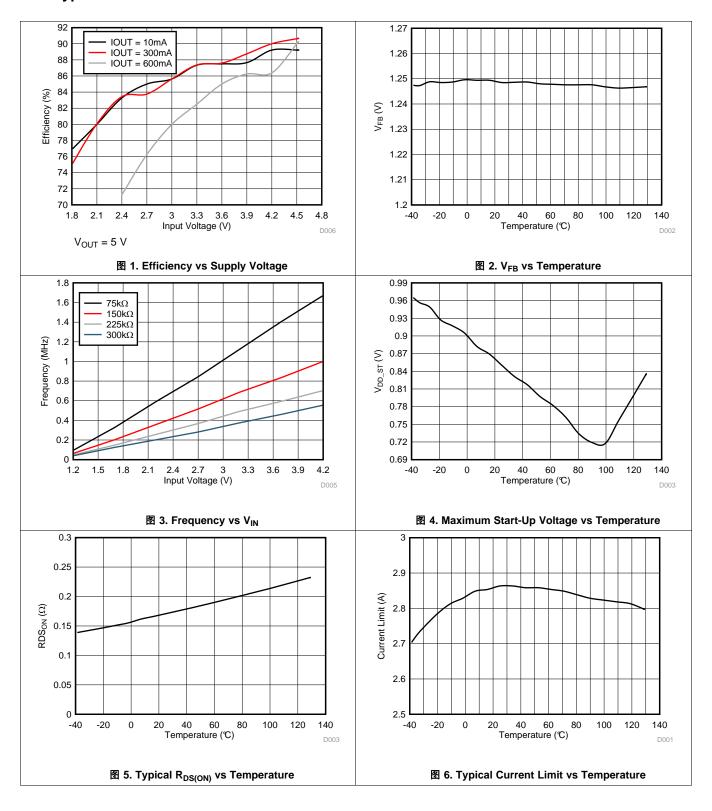

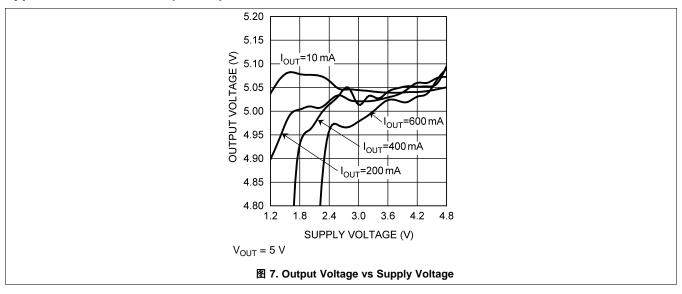

# 6.6 Typical Characteristics

# Typical Characteristics (接下页)

# 7 Detailed Description

# 7.1 Overview

The LM2623-Q1 device is designed to provide step-up DC-DC voltage regulation in battery-powered and low-input voltage systems. The device combines a step-up switching regulator, N-channel power MOSFET, built-in current limit, thermal limit, and voltage reference in a single 14-pin WSON package (see *Functional Block Diagram*). The switching DC-DC regulator boosts an input voltage between 0.9 V and 14 V to a regulated output voltage between 1.24 V and 14 V. The LM2623-Q1 starts from a low 1.1-V input and remains operational down to below 0.9 V. A high-efficiency gated-oscillator topology offers an output of up to 2 A at low step-up ratios.

# 7.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

# 7.3 Feature Description

#### 7.3.1 Gated Oscillator Control Scheme

The on/off regulation mode of the LM2623-Q1, along with its ultra-low quiescent current, results in good efficiency over a very wide load range. The internal oscillator frequency can be programmed using an external resistor to be constant or vary with the battery voltage. Adding a capacitor to program the frequency allows the designer to adjust the duty cycle and optimize it for the application. Adding a resistor in addition to the capacitor allows the duty cycle to dynamically compensate for changes to the input/output voltage ratio. This is called a ratio-adaptive gated-oscillator circuit. See the Typical Application for a sample application circuit. Using the correct RC components to adjust the oscillator allows the device to run with low ripple and high efficiency over a wide range of loads and input/output voltages.

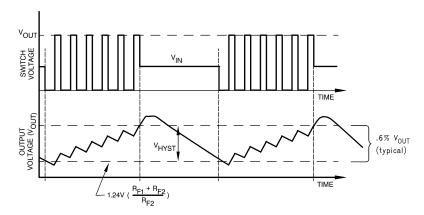

图 8. Typical Step-Up Regulator Waveforms

#### 7.3.2 Cycle-To-Cycle PFM

When the load does not vary over a wide range, ratio adaptive circuit techniques can be used to achieve cycle to cycle PFM regulation and lower ripple (or smaller output capacitors). The key to success is matching the duty cycle of the circuit closely to what is required by the input-to-output voltage ratio. This ratio then must be dynamically adjusted for input voltage changes (usually caused by batteries running down). The chosen ratio must allow most of the energy in each switching cycle to be delivered to the load and only a small amount to be stored. When the regulation limit is reached, the overshoot is small, and the system settles at an equilibrium point where it adjusts the off time in each switching cycle to meet the current requirements of the load. The off-time adjustment is done by exceeding the regulation limit during each switching cycle and waiting until the voltage drops below the limit again to start the next switching cycle. The current in the coil never goes to zero like it frequently does in the hysteretic operating mode of circuits with wide load variations or duty cycles that are not matched to the input/output voltage ratio. Optimizing the duty cycle for a given set of input/output voltages conditions can be done by referencing the circuit values in AN-1221 LM2623 General Purpose, Boost Converter Circuit.

#### 7.3.3 Shutdown

The LM2623-Q1 features a shutdown mode that reduces the quiescent current to less than an ensured 2.5  $\mu$ A over temperature. This extends the life of the battery in battery-powered applications. During shutdown, all feedback and control circuitry is turned off. The output voltage of the regulator drops to one diode drop below the input voltage. Entry into the shutdown mode is controlled by the active-low logic input pin EN (pin 4). When the logic input to this pin is pulled below 0.15  $V_{DD}$ , the device goes into shutdown mode. The logic input to this pin must be above 0.7  $V_{DD}$  for the device to work in normal step-up mode. If EN is pulled above 0.7  $V_{DD}$  the SW pin switches continuously for experimentally tested 5  $\mu$ s period, regardless of the output voltage. Once this time period is expired the feedback and gated oscillator scheme take over to regulate the output voltage.

# Feature Description (接下页)

#### 7.3.4 Internal Current Limit and Thermal Protection

An internal cycle-by-cycle current limit serves as a protection feature. This is set high enough (2.85 A typical, approximately 4 A maximum) so it does not come into effect during normal operating conditions. An internal thermal protection circuit disables the MOSFET power switch when the junction temperature (T<sub>J</sub>) exceeds about 160°C. The switch is re-enabled when T<sub>I</sub> drops below approximately 135°C.

# 7.4 Device Functional Modes

#### 7.4.1 Pulse Frequency Modulation (PFM)

Pulse frequency modulation is typically accomplished by switching continuously until the voltage limit is reached and skipping cycles after that to just maintain it. This results in a somewhat hysteretic mode of operation. The coil stores more energy each cycle as the current ramps up to high levels. When the voltage limit is reached, the system usually overshoots to a higher voltage than required, due to the stored energy in the coil (see 🛭 8). The system also undershoots somewhat when it starts switching again because it has depleted all the stored energy in the coil and must store more energy to reach equilibrium with the load. Larger output capacitors and smaller inductors reduce the ripple in these situations. The frequency being filtered, however, is not the basic switching frequency. It is a lower frequency determined by the load, the input/output voltage and the circuit parameters. This mode of operation is useful in situations where the load variation is significant. Power-managed computer systems, for instance, may vary from zero to full load while the system is on, and this is usually the preferred regulation mode for such systems.

# 7.4.2 Low Voltage Start-Up

The LM2623-Q1 can start up from voltages as low as 1.1 V. On start-up, the control circuitry switches the N-channel MOSFET continuously until the output reaches 3 V. After this output voltage is reached, the normal step-up regulator feedback and gated oscillator control scheme take over. Once the device is in regulation, it can operate down to 0.9 V input, because the internal power for the device can be boot-strapped from the output using the  $V_{DD}$  pin.

ZHCSGW9-OCTOBER 2017 www.ti.com.cn

# Applications and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The LM2623-Q1 is suitable for automotive applications, and supports shutdown mode for low quiescent current when EN input is low. Output voltage level can be adjusted by changing feedback resistor divider values from 1.24-V to 14-V range. The maximum switching frequency is 2MHz.

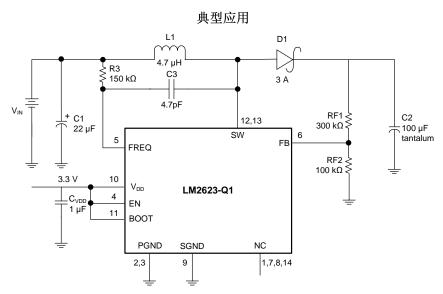

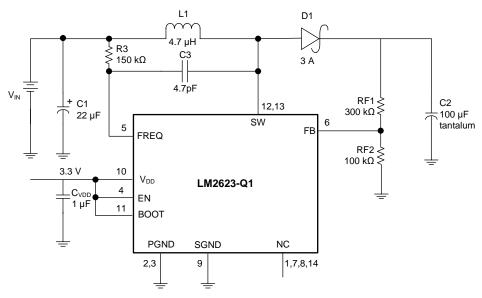

# 8.2 Typical Application

Copyright © 2017, Texas Instruments Incorporated

图 9. LM2623-Q1 Typical Application

# 8.2.1 Design Requirements

The LM2623-Q1 allows the designer to vary output voltage, operating frequency and duty cycle to optimize device performance (see Detailed Design Procedure for details).

For typical boost-converter applications, use the parameters listed in 表 1.

# 表 1. Design Parameters

| DESIGN PARAMETER | EXAMPLE VALUE               |

|------------------|-----------------------------|

| Input voltage    | 0.9 V to 14 V               |

| Output voltage   | 1.24 V to 14 V (adjustable) |

| Output current   | 2 A (maximum)               |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Non-Linear Effect

The LM2623-Q1 takes advantage of a non-linear effect, allowing for the duty cycle to be programmable. C3 in S 9 allows for the duty cycle to be programable.

#### 8.2.2.2 Choosing the Correct C3 Capacitor

The duty cycle of the internal oscillator is programmable with the C3 capacitor. Choosing the correct C3 capacitor to obtain the appropriate duty cycle for a particular application circuit is a trial-and-error process. The non-linear effect that C3 produces is dependent on the input voltage and output voltage values. The correct C3 capacitor for specific input and output voltage values cannot be calculated. Choosing the correct C3 capacitance is best done by trial and error, in conjunction with the checking of the inductor peak current to make sure it is not too close to the current limit of the device. As the C3 capacitor value increases, so does the duty cycle; conversely, as the C3 capacitor value decreases, the duty cycle decreases. An incorrect choice of the C3 capacitor can result in the device prematurely tripping the current limit and/or double pulsing, which could lead to the output voltage not being stable. Optimizing the duty cycle for a given set of input/output voltages conditions can be done by referencing the component values in *AN-1221 LM2623 General Purpose*, *Boost Converter Circuit*.

#### 8.2.2.3 Setting the Output Voltage

The output voltage of the step-up regulator can be set by connecting a feedback resistive divider made of  $R_{F1}$  and  $R_{F2}$ . The resistor values are selected as follows:

$$R_{F1} = R_{F2} \times [(V_{OUT} / 1.24) - 1] \tag{1}$$

A value of 50 kΩ to 100 kΩ is suggested for  $R_{F2}$ .  $R_{F1}$  can be selected using  $\Delta \pm 1$ .

# 8.2.2.4 V<sub>DD</sub> Supply

The  $V_{DD}$  supply must be between 3 V to 5 V for the LM2623-Q1 device. This voltage can be bootstrapped from a much lower input voltage by simply connecting the  $V_{DD}$  pin to  $V_{OUT}$ . In the event that the  $V_{DD}$  supply voltage is not a low-ripple voltage source (less than 200 mV), it may be advisable to use an RC filter to clean it up. Excessive ripple on  $V_{DD}$  may reduce the efficiency.

# 8.2.2.5 Setting the Switching Frequency

The switching frequency of the oscillator is selected by choosing an external resistor (R3) connected between  $V_{IN}$  and the FREQ pin. See  $\ 3$  in the *Typical Characteristics* for choosing the R3 value to achieve the desired switching frequency. A high switching frequency allows the use of very small surface mount inductors and capacitors and results in a very small solution size. TI recommends a switching frequency between 300 kHz and 2 MHz.

### 8.2.2.6 Output Diode Selection

Use a Schottky diode for the output diode. The forward current rating of the diode must be higher than the peak input current, and the reverse voltage rating must be higher than the output voltage. Do not use ordinary rectifier diodes, because slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer.

# 8.2.3 Application Curves

# 9 Power Supply Recommendations

The LM2623-Q1 can start up from voltages as low as 1.1 V. On start-up, the control circuitry switches the N-channel MOSFET continuously until the output reaches 3 V. After this output voltage is reached, the normal step-up regulator feedback and gated oscillator control scheme take over. Once the device is in regulation, it can operate down to below 0.9 V input, because the internal power for the device can be boot-strapped from the output using the  $V_{DD}$  pin.

# 10 Layout

# 10.1 Layout Guidelines

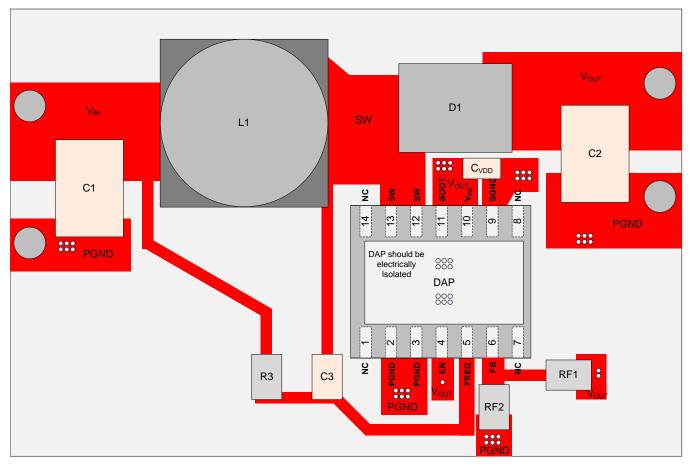

Il 12 follows proper layout guidelines — use as a guide for laying out the LM2623-Q1 circuit. The LM2623-Q1 inductive boost converter sees a high switched voltage at the SW pin and a step current through the Schottky diode and output capacitor each switching cycle. The high switching voltage can create interference into nearby nodes due to electric field coupling (I = C × dV/dt). The large step current through the diode and the output capacitor can cause a large voltage spike at the SW and BOOST pins due to parasitic inductance in the step current conducting path (V = L × di/dt). Board layout guidelines are geared towards minimizing this electric field coupling and conducted noise.

Boost Output Capacitor Placement, Schottky Diode Placement, and Boost Input / V<sub>DD</sub> Capacitor Placement detail the main (layout sensitive) areas of the LM2623-Q1 inductive boost converter in order of decreasing importance:

#### 10.1.1 Boost Output Capacitor Placement

Because the output capacitor is in the path of the inductor current discharge path, it experiences a high-current step from 0 A to the peak inductor current each time the switch turns off, and the Schottky diode turns on. Any inductance along this series path from the diodes cathode, through  $C_{OUT}$ , and back into the LM2623-Q1 GND pin contributes to voltage spikes at SW. These spikes can potentially overvoltage the SW and BOOST pins, or feed through to GND. To avoid this, COUT+ must be connected as close as possible to the cathode of the Schottky diode, and COUT- must be connected as close as possible to the LM2623-Q1 GND bumps. The best placement for  $C_{OUT}$  is on the same layer as the LM2623-Q1 to avoid any vias that can add excessive series inductance.

# 10.1.2 Schottky Diode Placement

In the LM2623-Q1 device boost circuit the Schottky diode is in the path of the inductor current discharge. As a result the Schottky diode detects a high-current step from 0 A to the peak inductor current each time the switch turns off, and the diode turns on. Any inductance in series with the diode causes a voltage spike at SW. This can potentially overvoltage the SW pin, or feed through to VOUT and through the output capacitor, into GND. Connecting the anode of the diode as close as possible to the SW pin, and connecting the cathode of the diode as close as possible to  $C_{\text{OUT}}$  reduces the parasitic inductance and minimizes these voltage spikes.

# 10.1.3 Boost Input / V<sub>DD</sub> Capacitor Placement

The LM2623-Q1 input capacitor filters the inductor current ripple and the internal MOSFET driver currents. The inductor current ripple can add input voltage ripple due to any series resistance in the input power path. The MOSFET driver currents can add voltage spikes on the input due to the inductance in series with the VIN/ $V_{DD}$  and the input capacitor. Place the input capacitor close to the inductor and minimize the current-loop area. Close placement of the  $V_{DD}$  capacitor to the  $V_{DD}$  and GND pins is critical because any series inductance can create voltage spikes that could appear on the VIN/ $V_{DD}$  supply line.

# 10.2 Layout Example

图 12. LM2623-Q1 Layout Example

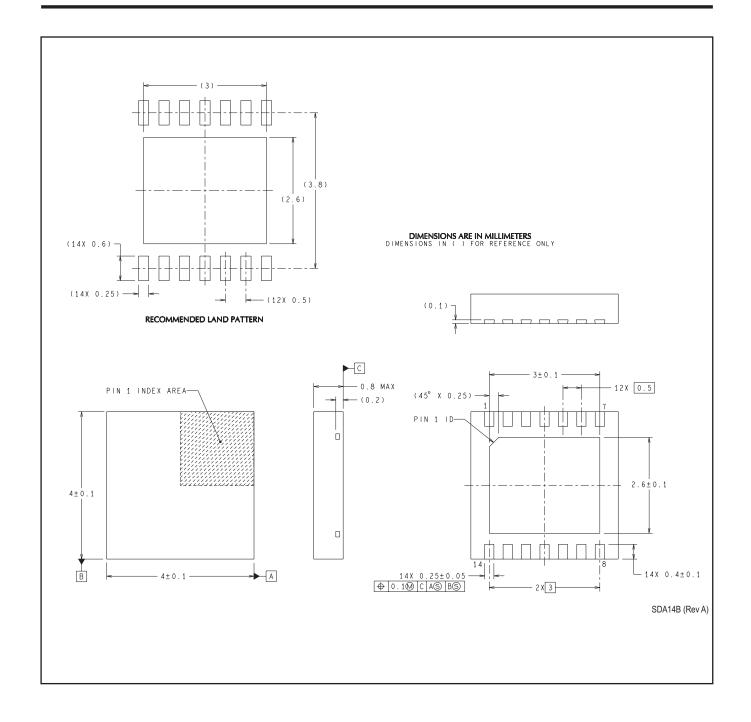

# 10.3 WSON Package Devices

The LM2623-Q1 is offered in the 14-pin WSON surface mount package — for details of the thermal performance as well as mounting and soldering specifications, refer to *Leadless Leadframe Package (LLP)*.

# 11 器件和文档支持

#### 11.1 器件支持

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

# 11.2 文档支持

#### 11.2.1 相关文档

相关文档如下:

- 《AN-1187 无引线框架封装 (LLP)》

- 《AN-1221 LM2623 通用升压转换器电路》

- 《AN-1258 LM2623 升压转换器 简单电源》

# 11.3 接收文档更新通知

要接收文档更新通知,请转至 Tl.com 上的器件产品文件夹。单击右上角的通知我 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

# 11.4 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 71 参考设计支持 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 11.5 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

# 11.6 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

# 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。这些数据如有变更,恕不另行通知 和修订此文档。如欲获取此数据表的浏览器版本,请参阅左侧的导航。 www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | (4)                           | (5)                        |              | (6)          |

| LM2623QNHLRQ1         | Active | Production    | WSON (NHL)   14 | 4500   LARGE T&R      | Yes  | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 2623Q1       |

| LM2623QNHLRQ1.A       | Active | Production    | WSON (NHL)   14 | 4500   LARGE T&R      | Yes  | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 2623Q1       |

| LM2623QNHLTQ1         | Active | Production    | WSON (NHL)   14 | 250   SMALL T&R       | Yes  | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 2623Q1       |

| LM2623QNHLTQ1.A       | Active | Production    | WSON (NHL)   14 | 250   SMALL T&R       | Yes  | SN                            | Level-2-260C-1 YEAR        | -40 to 125   | 2623Q1       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LM2623-Q1:

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月