Sample &

Buy

LM22680, LM22680-Q1

ZHCS545L-SEPTEMBER 2008-REVISED NOVEMBER 2014

#### LM22680/-Q1 42V、2A SIMPLE SWITCHER<sup>®</sup> 特性

降压稳压器

#### 特性 1

- 宽输入电压范围: 4.5V 至 42V

- 内部补偿电压模式控制

- 在使用低等效串联电阻 (ESR) 陶瓷电容器时保持稳 定

- 200mΩN沟道金属氧化物半导体场效应晶体管 (MOSFET)

- 输出电压选项: -ADJ (输出低至 1.285V)

- ±1.5% 反馈基准精度

- 500kHz 默认开关频率

- 可调开关频率和同步

- -40°C 至 125°C 的工作结温范围

- 精密使能引脚

- 集成引导加载二极管

- 可调节软启动

- 完全 WEBENCH<sup>®</sup> 启用

- LM22680-Q1 是一款汽车级产品, 符合 AEC-Q100 1 级标准(运行结温范围为 –40℃ 至 +125°C)

- 小外形尺寸 (SO) PowerPAD™ (外露焊盘) ٠

## 2 应用

- 工业控制

- 电信和数据通信系统

- 嵌入式系统

- 转换自标准 24V、12V 和 5V 输入电源轨

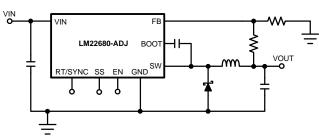

#### 简化应用电路原理图

## 3 说明

LM22680 开关稳压器可使用最少的外部元件来提供实 现高效高压降压稳压器所需的全部功能。 这款稳压器 易于使用,且集成了一个 42V N 沟道 MOSFET 开 关,可提供高达 2A 的负载电流。并且特有出色的线 路和负载调节以及高效率 (> 90%)。 电压模式控制提 供较短的最小接通时间,从而实现了输入和输出电压间 的最宽比率。内部环路补偿意味着用户无需承担计算 环路补偿组件的枯燥工作。 这款稳压器提供有 5V 固 定输出和可调输出电压两种选项。 默认开关频率设为 500kHz,这样便可以使用小型外部元件并且能够提供 良好的瞬态响应。 此外,还可以使用单个外部电阻在 200kHz 至 1MHz 的范围内对频率进行调节。 内部振 荡器可被同步至一个系统时钟或同步至其它稳压器的振 荡器。 精密使能输入可实现稳压器控制和系统电源排 序的优化。在关断模式下,稳压器流耗只有 25µA (典 型值)。可通过选择单个外部电容来提供可调节软启 动功能。LM22680器件还内置有热关断和限流功能, 可防止器件发生意外过载。

LM22680 器件是德州仪器 (TI) 的成员 SIMPLE SWITCHER<sup>®</sup>系列产品。 SIMPLE SWITCHER 概念 使用最少量的外部组件和德州仪器 (TI) WEBENCH 设 计工具提供了一套易于使用的完整设计。 为了简化设 计,TI的WEBENCH工具包含诸如外部元件计算、电 气模拟、散热模拟以及内置电路板等特性。

器件信息(1)

| 器件型号       | 封装       | 封装尺寸(标称值)       |  |  |  |  |

|------------|----------|-----------------|--|--|--|--|

| LM22680    |          | 4.80mm v 2.00mm |  |  |  |  |

| LM22680-Q1 | HSOP (8) | 4.89mm x 3.90mm |  |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

## 目录

8

9

11.2 11.3

11.4

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   |                                    |

| 3 | 说明   |                                    |

| 4 | 修订   | 历史记录                               |

| 5 |      | Configuration and Functions        |

| 6 | Spe  | cifications                        |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | Handling Ratings: LM22680 4        |

|   | 6.3  | Handling Ratings: LM22680-Q1 4     |

|   | 6.4  | Recommended Operating Conditions 4 |

|   | 6.5  | Thermal Information 4              |

|   | 6.6  | Electrical Characteristics 5       |

|   | 6.7  | Typical Characteristics 6          |

| 7 | Deta | ailed Description 8                |

|   | 7.1  | Overview                           |

|   | 7.2  | Functional Block Diagram 8         |

|   | 7.3  | Feature Description9               |

Changes from Revision K (April 2013) to Revision L

## 4 修订历史记录

| Cł | hanges from Revision J (April 2013) to Revision K                                     | Page |

|----|---------------------------------------------------------------------------------------|------|

| •  | Deleted Inverting Regulator Application                                               | 15   |

| •  | 已添加 引脚配置和功能部分,处理额定值表,特性描述部分,器件功能模式,应用和实施部分,电源相关建议部分,<br>布局部分,器件和文档支持部分以及机械、封装和可订购信息部分 | 1    |

|    |                                                                                       |      |

已更改 为新的 TI 格式......1

2

7.4 Device Functional Modes..... 12 Application and Implementation ...... 15

8.1 Application Information..... 15 8.2 Typical Application ..... 16

Power Supply Recommendations ...... 19 10.1 Layout Guidelines ..... 19 10.2 Layout Example ..... 20 10.3 Thermal Considerations ...... 20 11 器件和文档支持...... 21 11.1 文档支持...... 21 相关链接...... 21

> 商标......21 静电放电警告...... 21

11.5 Glossary ...... 21 12 机械、封装和可订购信息...... 21

www.ti.com.cn

Page

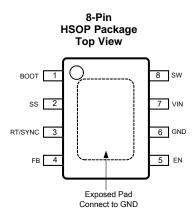

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN     |     | TYPE | DESCRIPTION                 | APPLICATION INFORMATION                                                                                                                      |  |

|---------|-----|------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO. | TIPE | DESCRIPTION                 | APPLICATION INFORMATION                                                                                                                      |  |

| BOOT    | 1   | I    | Bootstrap input             | Provides the gate voltage for the high side NFET.                                                                                            |  |

| EN      | 5   | I    | Enable pin                  | Used to control regulator start-up and shut-down. See <i>Precision Enable and UVLO</i> section of data sheet.                                |  |

| EP      | EP  | _    | Exposed pad                 | Connect to ground. Provides thermal connection to PCB. See <i>Application and Implementation</i> .                                           |  |

| FB      | 4   | I    | Feedback pin                | Feedback input to regulator.                                                                                                                 |  |

| GND     | 6   | _    | System ground               | System ground pin.                                                                                                                           |  |

| RT/SYNC | 3   | I    | Oscillator mode control pin | Used to control oscillator mode of regulator. See <i>Switching</i><br><i>Frequency Adjustment and Synchronization</i> section of data sheet. |  |

| SS      | 2   | 0    | Soft-start pin              | Used to increase soft-start time. See <i>Soft-Start</i> section of data sheet.                                                               |  |

| SW      | 8   | 0    | Switch pin                  | Switching output of regulator.                                                                                                               |  |

| VIN     | 7   | I    | Input voltage pin           | Supply input to the regulator.                                                                                                               |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                     | MIN            | MAX                 | UNIT |

|-------------------------------------|----------------|---------------------|------|

| VIN to GND                          |                | 43                  |      |

| EN Pin Voltage                      | -0.5           | 6                   |      |

| SS, RT/SYNC Pin Voltage             | -0.5           | 7                   | V    |

| SW to GND <sup>(3)</sup>            | -5             | $V_{IN}$            | v    |

| BOOT Pin Voltage                    | V              | ′ <sub>SW</sub> + 7 |      |

| FB Pin Voltage                      | -0.5           | 7                   |      |

| Power Dissipation                   | Internally Lir | nited               |      |

| Junction Temperature <sup>(4)</sup> |                | 150                 | °C   |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the absolute-maximum-ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and should not be operated beyond such conditions.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications

(3) The absolute maximum specification of the 'SW to GND' applies to dc voltage. An extended negative voltage limit of -10 V applies to a pulse of up to 50 ns.

(4) For soldering specifications, refer to Application Report Absolute Maximum Ratings for Soldering (SNOA549).

## 6.2 Handling Ratings: LM22680

|                    |                          |                                                                             | MIN | MAX | UNIT |

|--------------------|--------------------------|-----------------------------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub>   | Storage temperature rang | e                                                                           | -65 | 150 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | -2  | 2   | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Handling Ratings: LM22680-Q1

|                    |                           |                                                         | MIN | MAX | UNIT |

|--------------------|---------------------------|---------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub>   | Storage temperature range |                                                         | -65 | 150 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | -2  | 2   | kV   |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                            | MIN | MAX | UNIT |

|----------|----------------------------|-----|-----|------|

| $V_{IN}$ | Supply Voltage             | 4.5 | 42  | V    |

|          | Junction Temperature Range | -40 | 125 | °C   |

#### 6.5 Thermal Information

|                  | THERMAL METRIC <sup>(1)</sup>                         |    |      |  |

|------------------|-------------------------------------------------------|----|------|--|

|                  |                                                       |    |      |  |

| R <sub>0JA</sub> | lunction-to-ambient thermal resistance <sup>(2)</sup> | 60 | °C/W |  |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report (SPRA953).

The value of R<sub>0JA</sub> for the SO PowerPAD exposed pad (MR) package of 60°C/W is valid if package is mounted to 1 square inch of

copper. The R<sub>6,IA</sub> value can range from 42 to 115°C/W depending on the amount of PCB copper dedicated to heat transfer.

## 6.6 Electrical Characteristics

Typical values represent the most likely parametric norm at  $T_A = T_J = 25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise specified:  $V_{IN} = 12 \text{ V}$ .

|                     | PARAMETER                            | CONDITIONS                                                                    | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT           |  |

|---------------------|--------------------------------------|-------------------------------------------------------------------------------|--------------------|--------------------|--------------------|----------------|--|

|                     |                                      | V <sub>IN</sub> = 4.7 V to 42 V                                               | 1.266              | 1.285              | 1.304              |                |  |

| V <sub>FB</sub>     | Feedback Voltage                     | $V_{IN}$ = 4.7 V to 42 V, -40°C ≤ T <sub>J</sub> ≤ 125°C                      | 1.259              |                    | 1.311              | V              |  |

|                     | Quiescent Current                    | V <sub>FB</sub> = 5 V                                                         |                    | 3.4                |                    | m۸             |  |

| l <sub>Q</sub>      | Quescent Current                     | $V_{FB} = 5 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ |                    |                    | 6                  | mA             |  |

| ISTDBY              | Standby Quiescent Current            | EN Pin = 0 V                                                                  |                    | 25                 | 40                 | μA             |  |

|                     | Ourseast Lineit                      |                                                                               |                    | 2.8                |                    |                |  |

| I <sub>CL</sub>     | Current Limit                        | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                                     | 2.32               |                    | 3.4                | A              |  |

|                     | Output Looks to Output               | V <sub>IN</sub> = 42 V, EN Pin = 0 V, V <sub>SW</sub> = 0 V                   |                    | 0.2                | 2                  | μA             |  |

| IL                  | Output Leakage Current               | $V_{SW} = -1 V$                                                               |                    | 0.1                | 3                  | μA             |  |

| D                   |                                      |                                                                               |                    | 0.2                | 0.24               | 0.24<br>0.32 Ω |  |

| R <sub>DS(ON)</sub> | Switch On-Resistance                 | –40°C ≤ T <sub>J</sub> ≤ 125°C                                                |                    |                    | 0.32               |                |  |

| f <sub>O</sub>      | Oscillator Frequency                 |                                                                               |                    | 500                |                    | kHz            |  |

|                     |                                      | –40°C ≤ T <sub>J</sub> ≤ 125°C                                                | 400                |                    | 600                |                |  |

| <b>-</b>            | NF 1 0777                            |                                                                               |                    | 200                |                    | ns             |  |

| T <sub>OFFMIN</sub> | Minimum Off-time                     | –40°C ≤ T <sub>J</sub> ≤ 125°C                                                | 100                |                    | 300                |                |  |

| T <sub>ONMIN</sub>  | Minimum On-time                      |                                                                               |                    | 100                |                    | ns             |  |

| I <sub>BIAS</sub>   | Feedback Bias Current                | V <sub>FB</sub> = 1.3 V                                                       |                    | 230                |                    | nA             |  |

|                     |                                      | Falling                                                                       |                    | 1.6                |                    | V              |  |

| V <sub>EN</sub>     | Enable Threshold Voltage             | Falling, $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                            | 1.3                |                    | 1.9                | V              |  |

| V <sub>ENHYST</sub> | Enable Voltage Hysteresis            |                                                                               |                    | 0.6                |                    | V              |  |

| I <sub>EN</sub>     | Enable Input Current                 | EN Input = 0 V                                                                |                    | 6                  |                    | μA             |  |

| F <sub>SYNC</sub>   | Maximum Synchronization<br>Frequency | V <sub>SYNC</sub> = 3.5 V, 50% duty-cycle                                     |                    | 1                  |                    | MHz            |  |

| V <sub>SYNC</sub>   | Synchronization Threshold Voltage    |                                                                               |                    | 1.75               |                    | V              |  |

|                     |                                      |                                                                               |                    | 50                 |                    |                |  |

| I <sub>SS</sub>     | Soft-Start Current                   | –40°C ≤ T <sub>J</sub> ≤ 125°C                                                | 30                 |                    | 70                 | μA             |  |

| T <sub>SD</sub>     | Thermal Shutdown Threshold           |                                                                               |                    | 150                |                    | °C             |  |

(1) MIN and MAX limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate TI's Average Outgoing Quality Level (AOQL).

(2) Typical values represent most likely parametric norms at the conditions specified and are not ensured.

#### LM22680, LM22680-Q1

ZHCS545L-SEPTEMBER 2008-REVISED NOVEMBER 2014

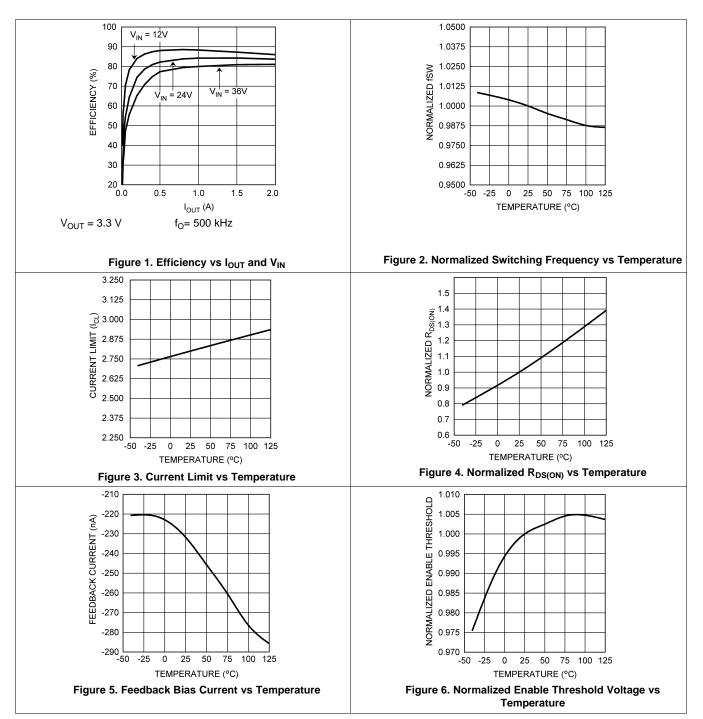

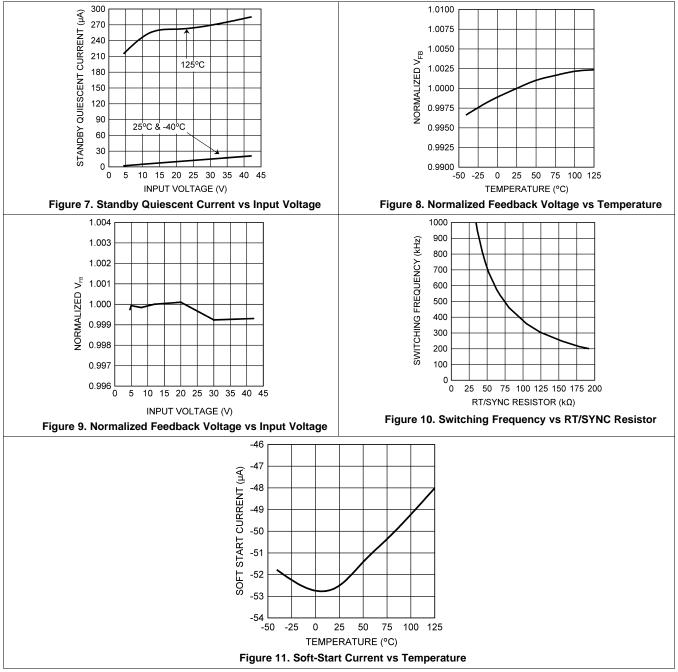

## 6.7 Typical Characteristics

$V_{in} = 12 \text{ V}, \text{ } \text{T}_{J} = 25^{\circ}\text{C}$  (unless otherwise specified)

www.ti.com.cn

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

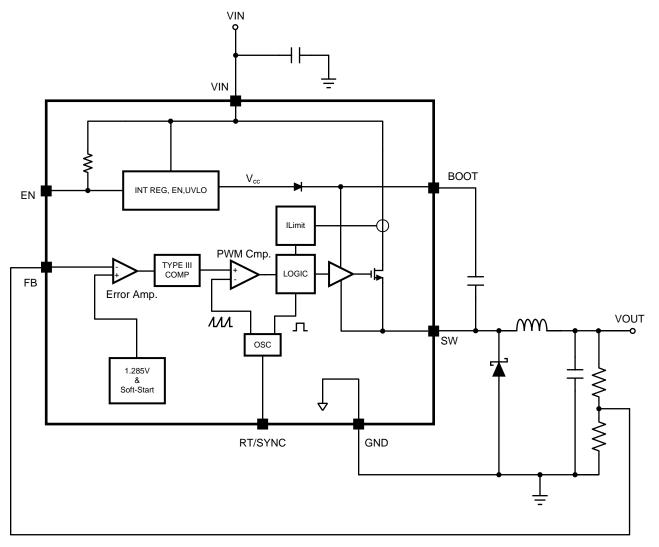

The LM22680 device incorporates a voltage mode constant frequency PWM architecture. In addition, input voltage feedforward is used to stabilize the loop gain against variations in input voltage. This allows the loop compensation to be optimized for transient performance. The power MOSFET, in conjunction with the diode, produce a rectangular waveform at the switch pin, that swings from about zero volts to VIN. The inductor and output capacitor average this waveform to become the regulator output voltage. By adjusting the duty cycle of this waveform, the output voltage can be controlled. The error amplifier compares the output voltage with the internal reference and adjusts the duty cycle to regulate the output at the desired value.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

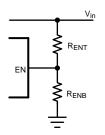

## 7.3.1 Precision Enable and UVLO

The precision enable input (EN) is used to control the regulator. The precision feature allows simple sequencing of multiple power supplies with a resistor divider from another supply. Connecting this pin to ground or to a voltage less than 1.6 V (typ) will turn off the regulator. The current drain from the input supply, in this state, is  $25 \ \mu$ A (typ) at an input voltage of 12 V. The EN input has an internal pullup of about 6  $\mu$ A. Therefore this pin can be left floating or pulled to a voltage greater than 2.2 V (typ) to turn the regulator on. The hysteresis on this input is about 0.6 V (typ) above the 1.6 V (typ) threshold. When driving the enable input, the voltage must never exceed the 6 V absolute maximum specification for this pin.

Although an internal pullup is provided on the EN pin, it is good practice to pull the input high, when this feature is not used, especially in noisy environments. This can most easily be done by connecting a resistor between VIN and the EN pin. The resistor is required, because the internal zener diode, at the EN pin, will conduct for voltages above about 6V. The current in this zener must be limited to less than 100  $\mu$ A. A resistor of 470 k $\Omega$  will limit the current to a safe value for input voltages as high 42 V. Smaller values of resistor can be used at lower input voltages.

The LM22680 device also incorporates an input undervoltage lock-out (UVLO) feature. This prevents the regulator from turning on when the input voltage is not great enough to properly bias the internal circuitry. The rising threshold is 4.3 V (typ) while the falling threshold is 3.9 V (typ). In some cases these thresholds may be too low to provide good system performance. The solution is to use the EN input as an external UVLO to disable the part when the input voltage falls below a lower boundary. This is often used to prevent excessive battery discharge or early turn-on during start-up. This method is also recommended to prevent abnormal device operation in applications where the input voltage falls below the minimum of 4.5 V. Figure 12 shows the connections to implement this method of UVLO. Equation 1 and Equation 2 can be used to determine the correct resistor values.

$$R_{ENT} = R_{ENB} \cdot \left( \frac{V_{off}}{V_{EN}} - 1 \right)$$

$$V_{on} = V_{off} \cdot \left( \frac{V_{EN} + V_{ENHYST}}{V_{EN}} \right)$$

(2)

Where:

V<sub>off</sub> is the input voltage where the regulator shuts off.

$V_{on}$  is the voltage where the regulator turns on.

Due to the 6  $\mu$ A pullup, the current in the divider should be much larger than this. A value of 20 k $\Omega$ , for R<sub>ENB</sub> is a good first choice. Also, a zener diode may be needed between the EN pin and ground, in order to comply with the absolute maximum ratings on this pin.

Figure 12. External UVLO Connections

## 7.3.2 Soft-Start

The soft-start feature allows the regulator to gradually reach steady-state operation, thus reducing start-up stresses. The internal soft-start feature brings the output voltage up in about 500  $\mu$ s. This time can be extended by using an external capacitor connected to the SS pin. Values in the range of 100 nF to 1  $\mu$ F are recommended. The approximate soft-start time can be estimated from Equation 3.

$$T_{SS} \approx 26 \times 10^3 \times C_{SS}$$

## **Feature Description (continued)**

Soft-start is reset any time the part is shut down or a thermal overload event occurs.

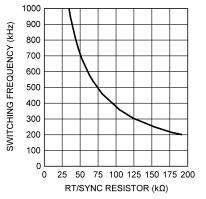

#### 7.3.3 Switching Frequency Adjustment and Synchronization

The LM22680 device will operate in three different modes, depending on the condition of the RT/SYNC pin. With the RT/SYNC pin floating, the regulator will switch at the internally set frequency of 500 kHz (typ). With a resistor in the range of 25 k $\Omega$  to 200 k $\Omega$ , connected from RT/SYNC to ground, the internal switching frequency can be adjusted from 1 MHz to 200 kHz. Figure 13 shows the typical curve for switching frequency versus the external resistance connected to the RT/SYNC pin. The accuracy of the switching frequency, in this mode, is slightly worse than that of the internal oscillator; about ±25% is to be expected. Finally, an external clock can be applied to the RT/SYNC pin to allow the regulator to synchronize to a system clock or another LM22680. The mode is set during start-up of the regulator. When the LM22680 is enabled, or after V<sub>IN</sub> is applied, a weak pullup is connected to the RT/SYNC pin and, after approximately 100  $\mu$ s, the voltage on the pin is checked against a threshold of about 0.8 V. With the RT/SYNC pin open, the voltage floats above this threshold, and the mode is set to run with the internal clock. With a frequency set resistor present, an internal reference holds the pin voltage at 0.8 V; thus, the resulting current sets the mode to allow the resistor to control the clock frequency. If the external circuit forces the RT/SYNC pin to a voltage much greater or less than 0.8 V, the mode is set to allow external synchronization. The mode is latched until either the EN or the input supply is cycled.

The choice of switching frequency is governed by several considerations. As an example, lower frequencies may be desirable to reduce switching losses or improve duty cycle limits. Higher frequencies, or a specific frequency, may be desirable to avoid problems with EMI or reduce the physical size of external components. The flexibility of increasing the switching frequency above 500 kHz can also be used to operate outside a critical signal frequency band for a given application. Keep in mind that the values of inductor and output capacitor cannot be reduced dramatically, by operating above 500 kHz. This is true because the design of the internal loop compensation restricts the range of these components.

Frequency synchronization requires some care. First the external clock frequency must be greater than the internal clock frequency, and less than 1 MHz. The maximum internal switching frequency is ensured in the *Electrical Characteristics* table. Note that the frequency adjust feature and the synchronization feature can not be used simultaneously. The synchronizing frequency must always be greater than the internal clock frequency. Secondly, the RT/SYNC pin must see a valid high or low voltage, during start-up, in order for the regulator to go into the synchronizing mode. Also, the amplitude of the synchronizing pulses must comport with V<sub>SYNC</sub> levels found in the Electrical Characteristics table. The regulator will synchronize on the rising edge of the external clock. If the external clock is lost during normal operation, the regulator will revert to the 500 kHz (typ) internal clock.

If the frequency synchronization feature is used, current limit foldback is not operational (see the *Current Limit* section for details).

Figure 13. Switching Frequency vs RT/SYNC Resistor

#### Feature Description (continued)

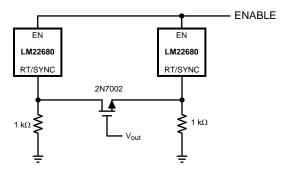

#### 7.3.4 Self Synchronization

It is possible to synchronize multiple LM22680 regulators together to share the same switching frequency. This can be done by tying the RT/SYNC pins together through a MOSFET and connecting a 1 k $\Omega$  resistor to ground at each pin. Figure 14 shows this connection. The gate of the MOSFET should be connected to the regulator with the highest output voltage. Also, the EN pins of both regulators should be tied to the common system enable, in order to properly initialize both regulators. The operation is as follows: When the regulators are enabled, the outputs are low and the MOSFET is off. The 1 k $\Omega$  resistors pull the RT/SYNC pins low, thus enabling the synchronization mode. These resistors are small enough to pull the RT/SYNC pin low, rather than activate the frequency adjust mode. Once the output voltage of one of the regulators is sufficient to turn on the MOSFET, the two RT/SYNC pins are tied together and the regulators will run in synchronized mode. The two regulators will be clocked at the same frequency but slightly phase shifted according to the minimum off-time of the regulator with the fastest internal oscillator. The slight phase shift helps to reduce stress on the input capacitors of the regulator. It is important to choose a MOSFET with a low gate threshold voltage so that the MOSFET will be fully enhanced. Also, a MOSFET with low inter-electrode capacitance is required. The 2N7002 is a good choice.

Figure 14. Self Synchronizing Setup

#### 7.3.5 Boot-Strap Supply

The LM22680 incorporates a floating high-side gate driver to control the power MOSFET. The supply for this driver is the external boot-strap capacitor connected between the BOOT pin and SW. A good quality 10 nF ceramic capacitor must be connected to these pins with short, wide PCB traces. One reason the regulator imposes a minimum off-time is to ensure that this capacitor recharges every switching cycle. A minimum load of about 5 mA is required to fully recharge the boot-strap capacitor in the minimum off-time. Some of this load can be provided by the output voltage divider, if used.

#### 7.3.6 Internal Loop Compensation

The LM22680 has internal loop compensation designed to provide a stable regulator over a wide range of external power stage components.

Ensuring stability of a design with a specific power stage (inductor and output capacitor) can be tricky. The LM22680 stability can be verified using the WEBENCH Designer online circuit simulation tool. A quick start spreadsheet can also be downloaded from the online product folder.

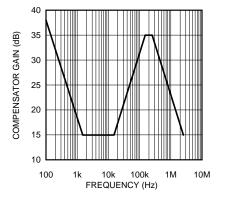

The complete transfer function for the regulator loop is found by combining the compensation and power stage transfer functions. The LM22680 has internal type III loop compensation, as detailed in Figure 15. This is the approximate "straight line" function from the FB pin to the input of the PWM modulator. The power stage transfer function consists of a dc gain and a second order pole created by the inductor and output capacitor(s). Due to the input voltage feedforward employed in the LM22680, the power stage dc gain is fixed at 20dB. The second order pole is characterized by its resonant frequency and its quality factor (Q). For a first pass design, the product of inductance and output capacitance should conform to Equation 4.

Alternatively, this pole should be placed between 1.5 kHz and 15 kHz and is given by Equation 5.

## Feature Description (continued)

$$F_o = \frac{1}{2\pi \cdot \sqrt{L \cdot C_{out}}}$$

The Q factor depends on the parasitic resistance of the power stage components and is not typically in the control of the designer. Of course, loop compensation is only one consideration when selecting power stage components (see the *Application and Implementation* section for more details).

Figure 15. Compensator Gain

In general, hand calculations or simulations can only aid in selecting good power stage components. Good design practice dictates that load and line transient testing should be done to verify the stability of the application. Also, Bode plot measurements should be made to determine stability margins. *AN-1889 How to Measure the Loop Transfer Function of Power Supplies* (SNVA364) shows how to perform a loop transfer function measurement with only an oscilloscope and function generator.

## 7.4 Device Functional Modes

#### 7.4.1 Current Limit

The LM22680 has current limiting to prevent the switch current from exceeding safe values during an accidental overload on the output. This peak current limit is found in the Electrical Characteristics table under the heading of  $I_{CL}$ . The maximum load current that can be provided, before current limit is reached, is determined from Equation 6.

$$|\mathbf{I}_{out}|_{max} \approx |\mathbf{I}_{CL} - \frac{(\mathbf{V}_{in} - \mathbf{V}_{out})}{2 \cdot \mathbf{L} \cdot \mathbf{F}_{sw}} \cdot \frac{\mathbf{V}_{out}}{\mathbf{V}_{in}}$$

Where:

L is the value of the power inductor.

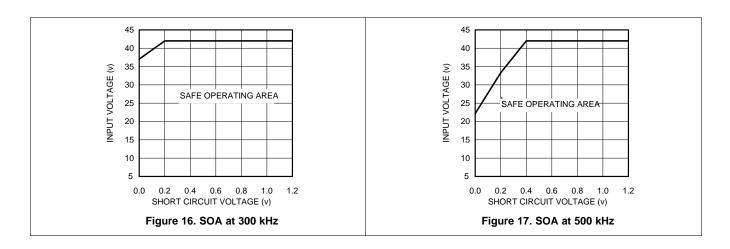

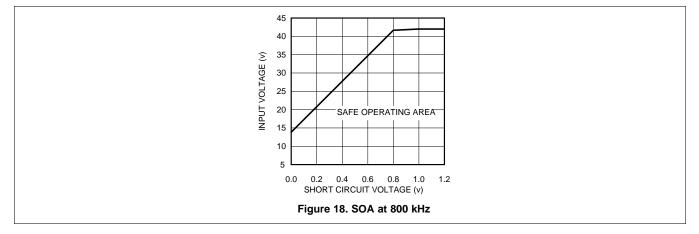

When the LM22680 enters current limit, the output voltage will drop and the peak inductor current will be fixed at  $I_{CL}$  at the end of each cycle. The switching frequency will remain constant while the duty cycle drops. The load current will not remain constant, but will depend on the severity of the overload and the output voltage.

For very severe overloads ("short-circuit"), the regulator changes to a low frequency current foldback mode of operation. The frequency foldback is about 1/5 of the nominal switching frequency. This will occur when the current limit trips before the minimum on-time has elapsed. This mode of operation is used to prevent inductor current "run-away", and is associated with very low output voltages when in overload. Equation 7 can be used to determine what level of output voltage will cause the part to change to low frequency current foldback.

$$V_x \le V_{in} \cdot F_{sw} \cdot T_{on} \cdot 1.8$$

Where:

$F_{sw}$  is the normal switching frequency.  $V_{in}$  is the maximum for the application.

**ISTRUMENTS**

FXAS

**\** - .

(7)

#### **Device Functional Modes (continued)**

If the overload drives the output voltage to less than or equal to  $V_x$ , the part will enter current foldback mode. If a given application can drive the output voltage to  $\leq V_x$ , during an overload, then a second criterion must be checked. Equation 8 gives the maximum input voltage, when in this mode, before damage occurs.

$$V_{in} \le \frac{V_{sc} + 0.4}{T_{on} \cdot F_{sw} \cdot 0.36}$$

(8)

Where:

$V_{sc}$  is the value of output voltage during the overload.

$f_{sw}$  is the normal switching frequency.

#### NOTE

If the input voltage should exceed this value, while in foldback mode, the regulator and/or the diode may be damaged.

It is important to note that the voltages in these equations are measured at the inductor. Normal trace and wiring resistance will cause the voltage at the inductor to be higher than that at a remote load. Therefore, even if the load is shorted with zero volts across its terminals, the inductor will still see a finite voltage. It is this value that should be used for  $V_x$  and  $V_{sc}$  in the calculations. In order to return from foldback mode, the load must be reduced to a value much lower than that required to initiate foldback. This load "hysteresis" is a normal aspect of any type of current limit foldback associated with voltage regulators.

If the frequency synchronization feature is used, the current limit frequency fold-back is not operational, and the system may not survive a hard short-circuit at the output.

The safe operating areas, when in short circuit mode, are shown in Figure 16 through Figure 18, for different switching frequencies. Operating points below and to the right of the curve represent safe operation.

# **NOTE** Figure 16, Figure 17, and Figure 18 curves are not valid when the LM22680 is in frequency synchronization mode.

**NSTRUMENTS**

FXAS

#### **Device Functional Modes (continued)**

#### 7.4.2 Thermal Protection

Internal thermal shutdown circuitry protects the LM22680 should the maximum junction temperature be exceeded. This protection is activated at about 150°C, with the result that the regulator will shut down until the temperature drops below about 135°C.

#### 7.4.3 Duty-Cycle Limits

Ideally the regulator would control the duty cycle over the full range of zero to one. However due to inherent delays in the circuitry, there are limits on both the maximum and minimum duty cycles that can be reliably controlled. This in turn places limits on the maximum and minimum input and output voltages that can be converted by the LM22680. A minimum on-time is imposed by the regulator in order to correctly measure the switch current during a current limit event. A minimum off-time is imposed in order the re-charge the bootstrap capacitor. Equation 9 can be used to determine the approximate maximum input voltage for a given output voltage.

$$V_{in}|_{max} \approx \frac{V_{out} + 0.4}{T_{on} \cdot F_{sw} \cdot 1.8}$$

Where:

F<sub>sw</sub> is the switching frequency.

$T_{ON}$  is the minimum on-time.

Both parameters are found in the Electrical Characteristics table.

If the frequency adjust feature is used, that value should be used for  $F_{sw}$ . Nominal values should be used. The worst case is lowest output voltage, and highest switching frequency. If this input voltage is exceeded, the regulator will skip cycles, effectively lowering the switching frequency. The consequences of this are higher output voltage ripple and a degradation of the output voltage accuracy.

The second limitation is the maximum duty cycle before the output voltage will "dropout" of regulation. Equation 10 can be used to approximate the minimum input voltage before dropout occurs.

$$V_{in}\Big|_{min} \approx \frac{V_{out} + 0.4 + I_{out} \cdot R_L}{1 - T_{off} \cdot F_{sw} \cdot 1.8} + I_{out} \cdot R_{dson}$$

(10)

Where:

The values of T<sub>OFF</sub> and R<sub>DS(ON)</sub> are found in the *Electrical Characteristics* table.

The worst case here is highest switching frequency and highest load. In this equation,  $R_{L}$  is the dc inductor resistance. Of course, the lowest input voltage to the regulator must not be less than 4.5 V (typ).

(9)

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LM22680 device is a step down dc-to-dc regulator. It is typically used to convert a higher dc voltage to a lower dc voltage with a maximum output current of 2 A. *Detailed Design Procedure* can be used to select components for the LM22680 device. Alternately, the WEBENCH® software may be used to generate complete designs. When generating a design, the WEBENCH® software utilizes iterative design procedure and accesses comprehensive databases of components. Go to WEBENCH Designer for more details. This section presents a simplified discussion of the design process.

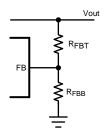

#### 8.1.1 Output Voltage Divider Selection

For output voltages greater than  $V_{FB}$  (1.285 V typ), a voltage divider is used between the output and the FB pin, as shown in Figure 19. Equation 11 can be used to calculate the resistor values of this divider.

$$R_{FBT} = \left[\frac{V_{out}}{1.285} - 1\right] \cdot R_{FBB}$$

(11)

A good value for  $R_{FBB}$  is 1 k $\Omega$ . This will help to provide some of the minimum load current requirement and reduce susceptibility to noise pick-up. The top of  $R_{FBT}$  should be connected directly to the output capacitor or to the load for remote sensing. If the divider is connected to the load, a local high-frequency bypass should be provided at that location.

Figure 19. Resistive Feedback Divider

A maximum value of 10 k $\Omega$  is recommended for the sum of  $R_{FBB}$  and  $R_{FBT}$  to maintain good output voltage accuracy.

The output voltage divider should be placed as close as possible to the FB pin of the LM22680, because this is a high impedance input and is susceptible to noise pick-up.

#### 8.1.2 Power Diode

A Schottky-type power diode is required for all LM22680 applications. Ultra-fast diodes are not recommended and may result in damage to the IC due to reverse recovery current transients. The near ideal reverse recovery characteristics and low forward voltage drop of Schottky diodes are particularly important for high input voltage and low output voltage applications common to the LM22680. The reverse breakdown rating of the diode should be selected for the maximum  $V_{IN}$ , plus some safety margin. A good rule of thumb is to select a diode with a reverse voltage rating of 1.3 times the maximum input voltage.

Select a diode with an average current rating at least equal to the maximum load current that will be seen in the application.

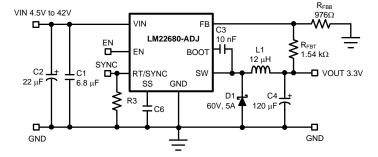

## 8.2 Typical Application

## 8.2.1 Typical Buck Regulator Application

Figure 20 shows an example of converting an input voltage range of 5.5 V to 42 V, to an output of 3.3 V at 2 A.

Figure 20. Typical Buck Regulator Application

#### 8.2.1.1 Design Requirements

| DESIGN PARAMETERS           | EXAMPLE VALUE                                           |

|-----------------------------|---------------------------------------------------------|

| Driver Supply Voltage (VIN) | 5.5 to 42 V                                             |

| Output Voltage (VOUT)       | 3.3 V                                                   |

| R <sub>FBT</sub>            | Calculated based on $R_{FBB}$ and $V_{REF}$ of 1.285 V. |

| R <sub>FBB</sub>            | 1 kΩ to 10 kΩ                                           |

| I <sub>OUT</sub>            | 2 A                                                     |

## 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 External Components

The following guidelines should be used when designing a step-down (buck) converter with the LM22680.

#### 8.2.1.2.2 Inductor

The inductor value is determined based on the load current, ripple current, and the minimum and maximum input voltages. To keep the application in continuous conduction mode (CCM), the maximum ripple current, IRIPPLE, should be less than twice the minimum load current. The general rule of keeping the inductor current peak-topeak ripple around 30% of the nominal output current is a good compromise between excessive output voltage ripple and excessive component size and cost. Using this value of ripple current, the value of inductor, L, is calculated using Equation 12.

$$L = \frac{(V_{in} - V_{out}) \cdot V_{out}}{0.3 \cdot I_{out} \cdot F_{sw} \cdot V_{in}}$$

(12)

Where:

F<sub>sw</sub> is the switching frequency.

V<sub>in</sub> should be taken at its maximum value, for the given application.

The formula in Equation 12 provides a guide to select the value of the inductor L; the nearest standard value will then be used in the circuit.

Once the inductor is selected, the actual ripple current can be found from Equation 13.

$$\Delta I = \frac{(V_{in} - V_{out}) \cdot V_{out}}{L \cdot F_{sw} \cdot V_{in}}$$

www.ti.com.cn

(13)

Increasing the inductance will generally slow down the transient response but reduce the output voltage ripple. Reducing the inductance will generally improve the transient response but increase the output voltage ripple.

The inductor must be rated for the peak current,  $I_{PK}$ , in a given application, to prevent saturation. During normal loading conditions, the peak current is equal to the load current plus 1/2 of the inductor ripple current.

During an overload condition, as well as during certain load transients, the controller may trip current limit. In this case the peak inductor current is given by  $I_{CL}$ , found in the *Electrical Characteristics* table. Good design practice requires that the inductor rating be adequate for this overload condition.

#### NOTE

If the inductor is not rated for the maximum expected current, it can saturate resulting in damage to the LM22680 and/or the power diode.

#### 8.2.1.2.3 Input Capacitor

The input capacitor selection is based on both input voltage ripple and RMS current. Good quality input capacitors are necessary to limit the ripple voltage at the VIN pin while supplying most of the regulator current during switch on-time. Low ESR ceramic capacitors are preferred. Larger values of input capacitance are desirable to reduce voltage ripple and noise on the input supply. This noise may find its way into other circuitry, sharing the same input supply, unless adequate bypassing is provided. A very approximate formula for determining the input voltage ripple is shown in Equation 14.

$$V_{\rm ri} \approx \frac{I_{\rm out}}{4 \cdot F_{\rm sw} \cdot C_{\rm in}}$$

(14)

Where:

V<sub>ri</sub> is the peak-to-peak ripple voltage at the switching frequency.

Another concern is the RMS current passing through this capacitor. Equation 15 gives an approximation to this current.

$$I_{\rm rms} \approx \frac{I_{\rm out}}{2}$$

(15)

The capacitor must be rated for at least this level of RMS current at the switching frequency.

All ceramic capacitors have large voltage coefficients, in addition to normal tolerances and temperature coefficients. To help mitigate these effects, multiple capacitors can be used in parallel to bring the minimum capacitance up to the desired value. This may also help with RMS current constraints by sharing the current among several capacitors. Many times it is desirable to use an electrolytic capacitor on the input, in parallel with the ceramics. The moderate ESR of this capacitor can help to damp any ringing on the input supply caused by long power leads. This method can also help to reduce voltage spikes that may exceed the maximum input voltage rating of the LM22680.

It is good practice to include a high frequency bypass capacitor as close as possible to the LM22680. This small case size, low ESR, ceramic capacitor should be connected directly to the VIN and GND pins with the shortest possible PCB traces. Values in the range of 0.47  $\mu$ F to 1  $\mu$ F are appropriate. This capacitor helps to provide a low impedance supply to sensitive internal circuitry. It also helps to suppress any fast noise spikes on the input supply that may lead to increased EMI.

#### 8.2.1.2.4 Output Capacitor

The output capacitor is responsible for filtering the output voltage and supplying load current during transients. Capacitor selection depends on application conditions as well as ripple and transient requirements. Best performance is achieved with a parallel combination of ceramic capacitors and a low ESR SP<sup>™</sup> or POSCAP<sup>™</sup> type. Very low ESR capacitors such as ceramics reduce the output ripple and noise spikes, while higher value electrolytics or polymer provide large bulk capacitance to supply transients. Assuming very low ESR, Equation 16 gives an approximation to the output voltage ripple:

$$V_{ro} \approx \frac{(V_{in} - V_{out}) \cdot V_{out}}{8 \cdot V_{in}} \cdot \frac{1}{F_{sw}^2 \cdot L \cdot C_{out}}$$

(16)

Typically, a total value of 100 µF or greater is recommended for output capacitance.

In applications with V<sub>out</sub> less than 3.3 V, it is critical that low ESR output capacitors are selected. This will limit potential output voltage overshoots as the input voltage falls below the device normal operating range.

If the switching frequency is set higher than 500 kHz, the capacitance value may not be reduced proportionally due to stability requirements. The internal compensation is optimized for circuits with a 500-kHz switching frequency. See the *Internal Loop Compensation* section for more details.

#### 8.2.1.2.5 Boot-Strap Capacitor

The bootstrap capacitor between the BOOT pin and the SW pin supplies the gate current to turn on the Nchannel MOSFET. The recommended value of this capacitor is 10 nF and should be a good quality, low ESR ceramic capacitor. In some cases it may be desirable to slow down the turn-on of the internal power MOSFET, in order to reduce EMI. This can be done by placing a small resistor in series with the  $C_{boot}$  capacitor. Resistors in the range of 10 $\Omega$  to 50 $\Omega$  can be used. This technique should only be used when absolutely necessary, because it will increase switching losses and thereby reduce efficiency.

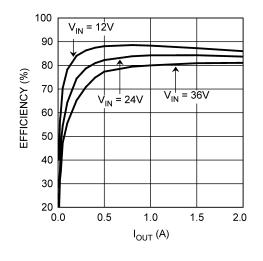

#### 8.2.1.3 Application Curves

$V_{OUT} = 3.3 \text{ V}$  f<sub>O</sub>= 500 kHz

Figure 21. Efficiency vs  $I_{OUT}$  and  $V_{IN}$

## 9 Power Supply Recommendations

The LM22680 device is designed to operate from an input voltage supply range between 4.5 V and 42 V. This input supply should be well regulated and able to withstand maximum input current and maintain a stable voltage. The resistance of the input supply rail should be low enough that an input current transient does not cause a high enough drop at the LM22680 supply voltage that can cause a false UVLO fault triggering and system reset. If the input supply is located more than a few inches from the LM22680, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. The amount of bulk capacitance is not critical, but a 47  $\mu$ F or 100  $\mu$ F electrolytic capacitor is a typical choice.

## 10 Layout

#### **10.1 Layout Guidelines**

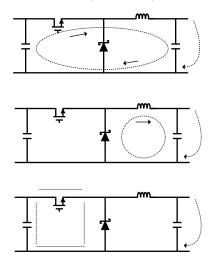

Board layout is critical for the proper operation of switching power supplies. First, the ground plane area must be sufficient for thermal dissipation purposes. Second, appropriate guidelines must be followed to reduce the effects of switching noise. Switch mode converters are very fast switching devices. In such cases, the rapid increase of input current combined with the parasitic trace inductance generates unwanted L di/dt noise spikes. The magnitude of this noise tends to increase as the output current increases. This noise may turn into electromagnetic interference (EMI) and can also cause problems in device performance. Therefore, care must be taken in layout to minimize the effect of this switching noise.

The most important layout rule is to keep the ac current loops as small as possible. Figure 22 shows the current flow in a buck converter. The top schematic shows a dotted line which represents the current flow during the FET switch on-state. The middle schematic shows the current flow during the FET switch off-state.

The bottom schematic shows the currents referred to as ac currents. These ac currents are the most critical because they are changing in a very short time period. The dotted lines of the bottom schematic are the traces to keep as short and wide as possible. This will also yield a small loop area reducing the loop inductance. To avoid functional problems due to layout, review the PCB layout example. Best results are achieved if the placement of the LM22680, the bypass capacitor, the Schottky diode,  $R_{FBB}$ ,  $R_{FBT}$ , and the inductor are placed as shown in Figure 23. Note that, in the layout shown, R1 =  $R_{FBB}$  and R2 =  $R_{FBT}$ . It is also recommended to use 2oz copper boards or heavier to help thermal dissipation and to reduce the parasitic inductances of board traces. See *AN-1229 SIMPLE SWITCHER® PCB Layout Guidelines* (SNVA054) for more information.

Figure 22. Current Flow in a Buck Application

## 10.2 Layout Example

Figure 23. LM2280 Layout Example

## **10.3 Thermal Considerations**

The components with the highest power dissipation are the power diode and the power MOSFET internal to the LM22680 regulator. The easiest method to determine the power dissipation within the LM22680 is to measure the total conversion losses then subtract the power losses in the diode and inductor. The total conversion loss is the difference between the input power and the output power. An approximation for the power diode loss is shown in Equation 17.

$$\mathbf{P}_{\mathrm{D}} = \mathbf{I}_{\mathrm{out}} \cdot \mathbf{V}_{\mathrm{D}} \cdot \left[ \mathbf{1} - \frac{\mathbf{V}_{\mathrm{out}}}{\mathbf{V}_{\mathrm{in}}} \right]$$

Where:

$V_D$  is the diode voltage drop.

An approximation for the inductor power is shown in Equation 18.

$$P_L = I_{out}^2 \cdot R_L \cdot 1.1$$

Where:

R<sub>L</sub> is the dc resistance of the inductor.

The 1.1 factor is an approximation for the ac losses.

The regulator has an exposed thermal pad to aid power dissipation. Adding multiple vias under the device to the ground plane will greatly reduce the regulator junction temperature. Selecting a diode with an exposed pad will also aid the power dissipation of the diode. The most significant variables that affect the power dissipation of the regulator are output current, input voltage and operating frequency. The power dissipated while operating near the maximum output current and maximum input voltage can be appreciable. The junction-to-ambient thermal resistance of the LM22680 will vary with the application. The most significant variables are the area of copper in the PC board, the number of vias under the IC exposed pad and the amount of forced air cooling provided. A large continuous ground plane on the top or bottom PCB layer will provide the most effective heat dissipation. The integrity of the solder connection from the IC exposed pad to the PC board is critical. Excessive voids will greatly diminish the thermal dissipation capacity. The junction-to-ambient thermal resistance of the LM22680 SO PowerPAD package is specified in the *Electrical Characteristics* table. See *AN-2020 Thermal Design By Insight, Not Hindsight* (SNVA419) for more information.

www.ti.com.cn

(17)

(18)

## 11 器件和文档支持

## 11.1 文档支持

## 11.1.1 相关文档

- AN-2020《富于洞见的热设计》(文献编号: SNVA419)

- 《AN-1229 SIMPLE SWITCHER® PCB 布局指南》(文献编号: SNVA054)

- AN-1911《LM22680 评估板》(文献编号: SNVA378)

- AN-1889《如何测量电源的环路传递函数》(文献编号: SNVA364)

## 11.2 相关链接

下面的表格列出了快速访问链接。 范围包括技术文档、支持与社区资源、工具和软件,以及样片或购买的快速访问。

#### 表 1. 相关链接

| 部件         | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|------------|-------|-------|-------|-------|-------|

| LM22680    | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| LM22680-Q1 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

## 11.3 商标

PowerPAD is a trademark of Texas Instruments. WEBENCH, SIMPLE SWITCHER are registered trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### **11.4** 静电放电警告

这些装置包含有限的内置 ESD 保护。存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

## 11.5 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不 对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

## PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-----------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM22680MR-ADJ/NOPB    | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 95   TUBE             | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>-ADJ      |

| LM22680MR-ADJ/NOPB.A  | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 95   TUBE             | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>-ADJ      |

| LM22680MRE-ADJ/NO.A   | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>-ADJ      |

| LM22680MRE-ADJ/NOPB   | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>-ADJ      |

| LM22680MRX-ADJ/NO.A   | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>-ADJ      |

| LM22680MRX-ADJ/NOPB   | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>-ADJ      |

| LM22680QMR-ADJ/NO.A   | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 95   TUBE             | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>Q-ADJ     |

| LM22680QMR-ADJ/NOPB   | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 95   TUBE             | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>Q-ADJ     |

| LM22680QMRE-ADJ/NO.A  | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>Q-ADJ     |

| LM22680QMRE-ADJ/NOPB  | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 250   SMALL T&R       | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>Q-ADJ     |

| LM22680QMRX-ADJ/NO.A  | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>Q-ADJ     |

| LM22680QMRX-ADJ/NOPB  | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes             | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680<br>Q-ADJ     |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

(2) Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

www.ti.com

# PACKAGE OPTION ADDENDUM

23-May-2025

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LM22680, LM22680-Q1 :

Catalog : LM22680

• Automotive : LM22680-Q1

NOTE: Qualified Version Definitions:

Catalog - TI's standard catalog product

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

Texas

STRUMENTS

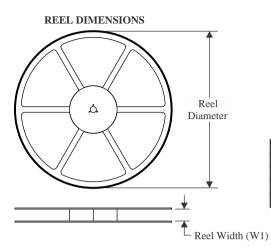

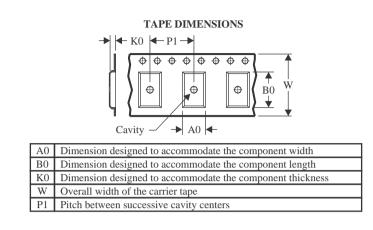

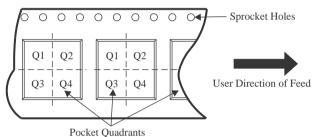

## TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM22680MRE-ADJ/NOPB         | SO<br>PowerPAD  | DDA                | 8 | 250  | 177.8                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM22680MRX-ADJ/NOPB         | SO<br>PowerPAD  | DDA                | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM22680QMRE-<br>ADJ/NOPB    | SO<br>PowerPAD  | DDA                | 8 | 250  | 177.8                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM22680QMRX-<br>ADJ/NOPB    | SO<br>PowerPAD  | DDA                | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

www.ti.com

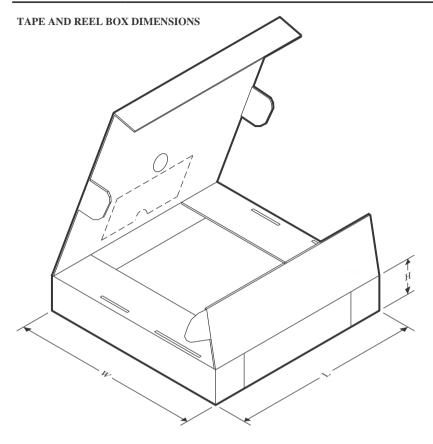

# PACKAGE MATERIALS INFORMATION

23-Jul-2025

\*All dimensions are nominal

| Device                   | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM22680MRE-ADJ/NOPB      | SO PowerPAD  | DDA             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LM22680MRX-ADJ/NOPB      | SO PowerPAD  | DDA             | 8    | 2500 | 356.0       | 356.0      | 36.0        |

| LM22680QMRE-<br>ADJ/NOPB | SO PowerPAD  | DDA             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LM22680QMRX-<br>ADJ/NOPB | SO PowerPAD  | DDA             | 8    | 2500 | 356.0       | 356.0      | 36.0        |

## TEXAS INSTRUMENTS

www.ti.com

23-Jul-2025

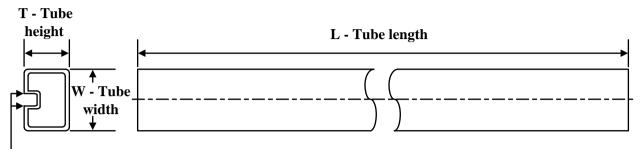

## TUBE

## - B - Alignment groove width

#### \*All dimensions are nominal

| Device               | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|----------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LM22680MR-ADJ/NOPB   | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LM22680MR-ADJ/NOPB.A | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LM22680QMR-ADJ/NO.A  | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LM22680QMR-ADJ/NOPB  | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064   | 3.05   |

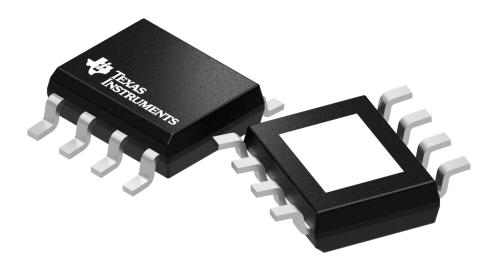

## **GENERIC PACKAGE VIEW**

# **DDA 8**

# PowerPAD<sup>™</sup> SOIC - 1.7 mm max height PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行 复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索 赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司