LDC1312, LDC1314

ZHCSHX3A - DECEMBER 2014 - REVISED MARCH 2018

# 适用于电感感应的 LDC1312、LDC1314 多通道 12 位电感数字转换器 (LDC)

## 1 特性

- 易于使用 配置要求极低

- 多达 4 个具有匹配传感器驱动器的通道

- 多个通道支持环境和老化补偿

- 大于 20cm 的远程传感器位置支持在严苛的环境下 运行

- 与中等分辨率和高分辨率选项引脚兼容:

- LDC1312/4: 2/4 通道 12 位 LDC

- LDC1612/4: 2/4 通道 28 位 LDC

- 支持 1kHz 至 10MHz 的宽传感器频率范围

- 功耗:

- 35µA (低功耗休眠模式)

- 200nA (美断模式)

- 2.7V 至 3.6V 工作电压

- 多个基准时钟选项:

- 包含内部时钟,以降低系统成本

- 支持 40MHz 外部时钟,以提高系统性能

- 抗直流磁场和磁体干扰

#### 2 应用

- 消费类产品、电器和汽车中的旋钮

- 线性和旋转编码器

- 家用电子产品、可穿戴设备、制造业和汽车中的按钮

- 制造业和电器中的键盘

- 消费类产品中的滑动按钮

- 工业和汽车中的金属探测

- POS 和 EPOS

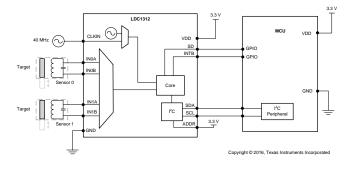

- 消费类产品和电器中的流量计 简化原理图

## 3 说明

LDC1312 和 LDC1314 分别是用于电感感测解决方案的 2 通道和 4 通道 12 位电感数字转换器 (LDC)。由于具备多通道且支持远程感测,LDC1312 和 LDC1314 能以最低的成本和功耗实现高性能且可靠的电感感测。此类产品使用简便,仅需要传感器频率处于 1kHz 至10MHz 的范围内即可开始工作。由于支持的传感器频率范围 1kHz 至10MHz 较宽,因此还支持使用非常小的 PCB 线圈,从而进一步降低感测解决方案的成本和尺寸。

LDC1312 和 LDC1314 提供匹配良好的通道,可实现差分测量与比率测量。因此,设计人员能够利用一个通道来补偿感测过程中的环境条件和老化条件,例如温度、湿度和机械漂移。得益于易用、低能耗、低系统成本等特性,这些产品有助于设计人员大幅提高现有传感解决方案的性能、可靠性和灵活性,并将全新的传感功能引入到了所有市场(尤其是消费品和工业应用)中的产品。相比同类感测技术,电感感测具有更高的性能、可靠性和灵活性,而且系统成本与功耗更低。

LDC1312 和 LDC1314 能够通过 I2C 接口轻松进行配置。双通道 LDC1312 采用 WSON-12 封装,四通道 LDC1314 采用 WQFN-16 封装。

## 器件信息<sup>(1)</sup>

| 器件型号    | 封装      | 封装尺寸 (标称值) |

|---------|---------|------------|

| LDC1312 | WSON-12 | 4mm × 4mm  |

| LDC1314 | WQFN-16 | 4mm × 4mm  |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

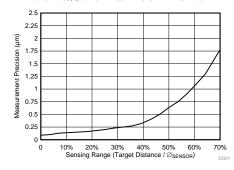

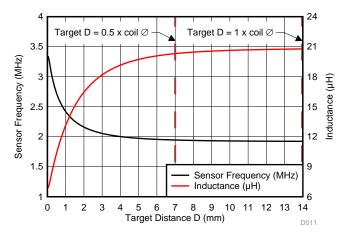

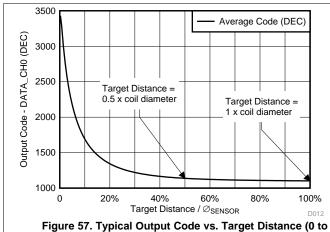

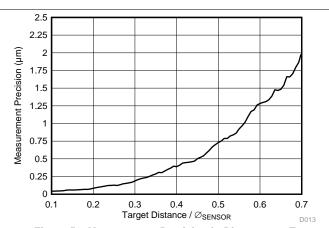

#### 测量精度与目标距离间的关系

# 目录

| 1 | 特性 1                                 |    | 7.6 Register Maps              | 14         |

|---|--------------------------------------|----|--------------------------------|------------|

| 2 | 应用 1                                 | 8  | Application and Implementation | 31         |

| 3 | 说明1                                  |    | 8.1 Application Information    | 31         |

| 4 | 修订历史记录 2                             |    | 8.2 Typical Application        | 47         |

| 5 | Pin Configuration and Functions      | 9  | Power Supply Recommendations   | <u>5</u> 1 |

| 6 | Specifications4                      | 10 | Layout                         | <u>52</u>  |

| • | 6.1 Absolute Maximum Ratings 4       |    | 10.1 Layout Guidelines         | 52         |

|   | 6.2 ESD Ratings                      |    | 10.2 Layout Example            | 52         |

|   | 6.3 Recommended Operating Conditions | 11 | 器件和文档支持                        | 53         |

|   | 6.4 Thermal Information              |    | 11.1 器件支持                      | 53         |

|   | 6.5 Electrical Characteristics       |    | 11.2 文档支持                      | 53         |

|   | 6.6 Switching Characteristics - I2C6 |    | 11.3 相关链接                      | 53         |

|   | 6.7 Typical Characteristics          |    | 11.4 接收文档更新通知                  | <u>53</u>  |

| 7 | Detailed Description9                |    | 11.5 社区资源                      | 53         |

| - | 7.1 Overview                         |    | 11.6 商标                        | 53         |

|   | 7.2 Functional Block Diagram         |    | 11.7 静电放电警告                    | 54         |

|   | 7.3 Feature Description              |    | 11.8 Glossary                  | 54         |

|   | 7.4 Device Functional Modes 11       | 12 | 机械、封装和可订购信息                    | <u>54</u>  |

|   | 7.5 Programming                      |    |                                |            |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Original (December 2014) to Revision A

Page

| • | Changed ESD values from 1000 to 2000 and from 250 to 750 on both packages                                                                                          | 4    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added logic levels for ADDR, INTB, and SD pins.                                                                                                                    | 5    |

| • | Changed description of clocking architecture for improved clarity.                                                                                                 | . 10 |

| • | Changed register names and field names from CHx_NAME and NAME_CHx to NAMEx.                                                                                        | . 14 |

| • | Added instructions on setting registers with both R and R/W fields                                                                                                 | . 14 |

| • | Changed register names from DATA_CHx to DATAx; and CHx_ERR_YY field names to ERR_YYx                                                                               | . 15 |

| • | Changed ERR_AE field description on DATA0, DATA1, DATA2 and DATA3 tables.                                                                                          | . 15 |

| • | Changed register names from RCOUNT_CHx to RCOUNTx; and CHx_RCOUNT field names to RCOUNTx                                                                           | . 17 |

| • | Changed register names from OFFSET_CHx to OFFSETx; and CHx_OFFSET field names to OFFSETx                                                                           | . 18 |

| • | Changed register names from SETTLECOUNT_CHx to SETTLECOUNTx; and CHx_SETTLECOUNT field names to SETTLECOUNTx                                                       | . 19 |

| • | Changed Address of SETTLECOUNT0 and SETTLECOUNT1 were not correct on table.                                                                                        | . 20 |

| • | Changed register names from CLOCK_DIVIDERS_CHx to CLOCK_DIVIDERSx; CHx_FIN_DIVIDER field names to FIN_DIVIDERx, and CHx_FREF_DIVIDER field names to FREF_DIVIDERx. | . 21 |

| • | Changed CHx_UNREADCONV field names to UNREADCONVx                                                                                                                  | . 23 |

| • | Changed register names from DRIVE_CURRENT_CHx to DRIVE_CURRENTx; CHx_IDRIVE field names to IDRIVEx, and CHx_INIT_IDRIVE to INIT_IDRIVEx                            | . 28 |

| • | Changed Application Information section for clarity, and provided additional information on device configuration and operation.                                    | . 31 |

| • | Added instructions for using an oscilloscope to configure sensor drive current                                                                                     | . 42 |

| • | Changed description of clocking usage for clarity.                                                                                                                 | . 43 |

| • | Changed reference frequency limits from < to ≤                                                                                                                     | . 44 |

| • | Changed to a ≥ symbol in the Clock Configuration Requirements table.                                                                                               | . 44 |

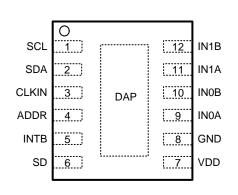

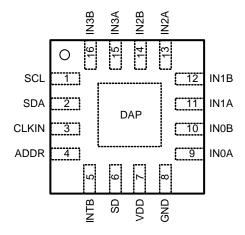

## 5 Pin Configuration and Functions

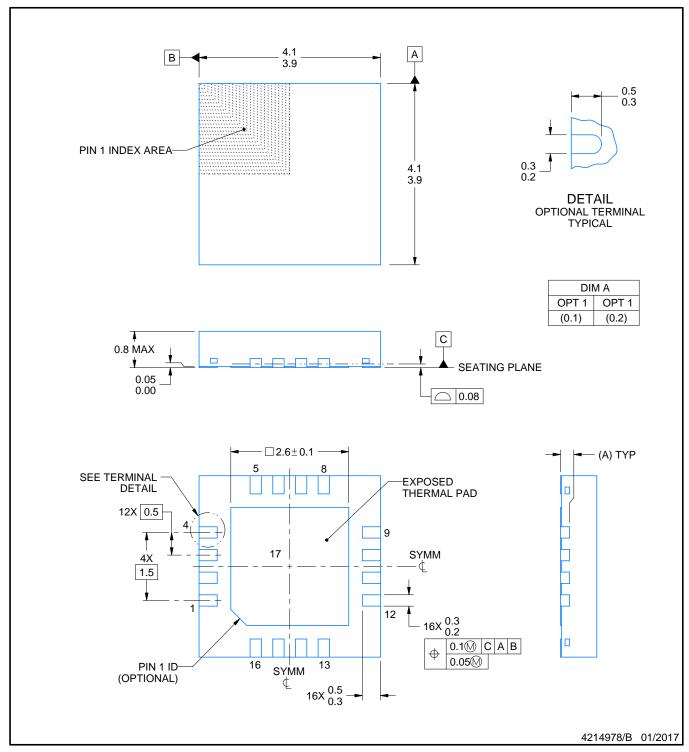

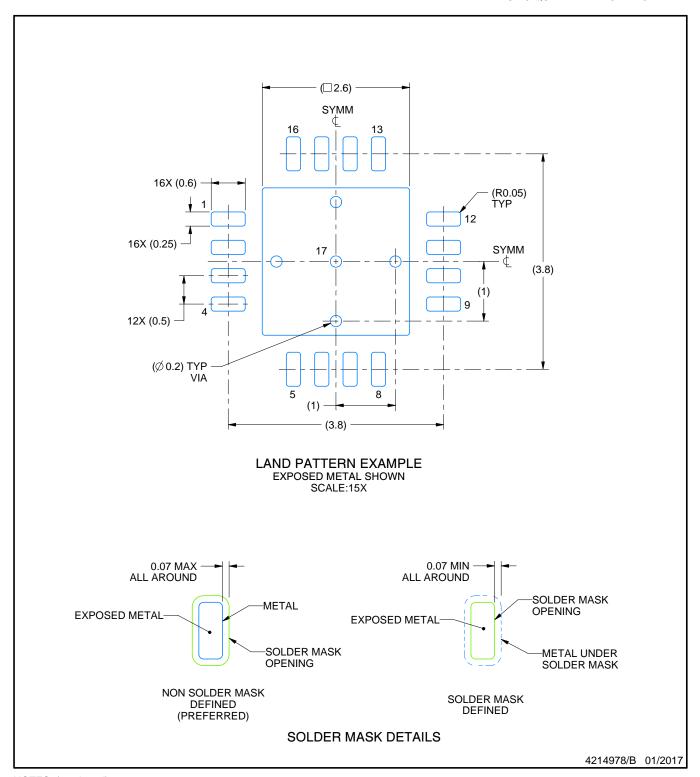

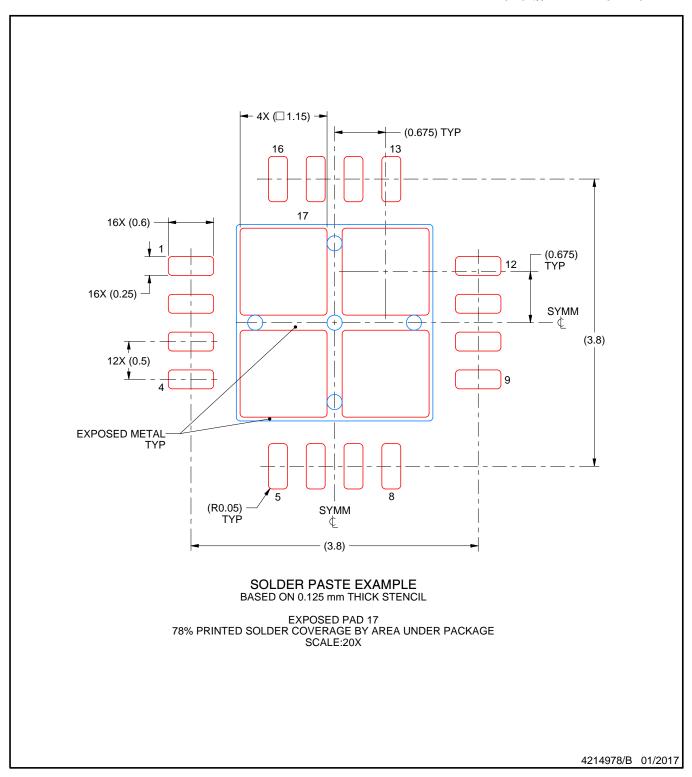

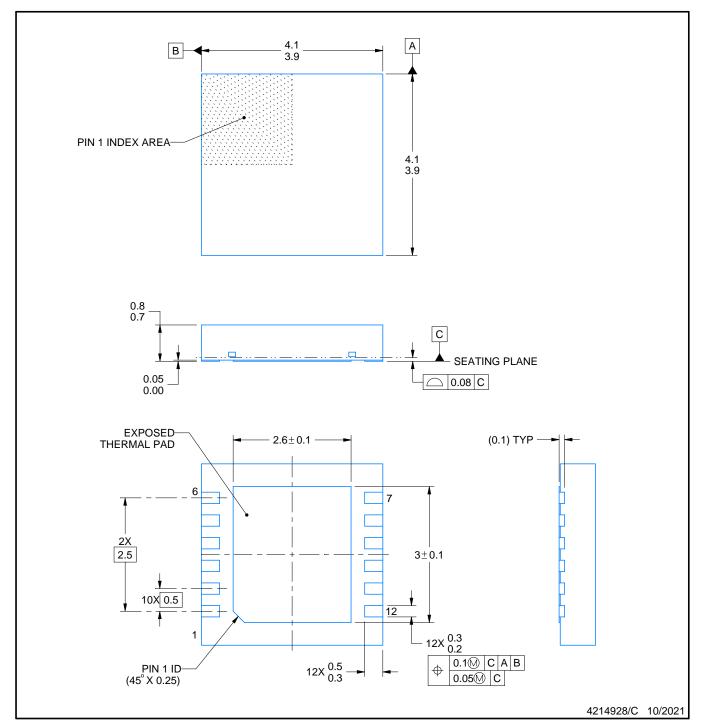

#### DNT and RGH Packages Top View

LDC1312 WSON-12

LDC1314 WQFN-16

#### **Pin Functions**

| PIN TYPE <sup>(1)</sup> |     | T) (D=(1) | DECORPORAL                                                                                                                            |  |

|-------------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                    | NO. | IYPE      | DESCRIPTION                                                                                                                           |  |

| SCL                     | 1   | 1         | I2C Clock input. Open drain output; requires resistive pullup to logic high level.                                                    |  |

| SDA                     | 2   | I/O       | I2C Data input/output. Open drain output; requires resistive pullup to logic high level.                                              |  |

| CLKIN                   | 3   | 1         | External Reference Clock input. Tie this pin to GND if internal oscillator is used.                                                   |  |

| ADDR                    | 4   | ı         | I2C Address selection pin: when ADDR=L, I2C address = 0x2A, when ADDR=H, I2C address = 0x2B. This input must not be allowed to float. |  |

| INTB                    | 5   | 0         | Configurable Interrupt output pin. Push-pull output; does not require pullup.                                                         |  |

| SD                      | 6   | ı         | Shutdown input: set SD = L for normal operation, set SD=H for inactive mode. This input must not be allowed to float.                 |  |

| VDD                     | 7   | Р         | Power Supply                                                                                                                          |  |

| GND                     | 8   | G         | Ground                                                                                                                                |  |

| IN0A                    | 9   | А         | External LC sensor 0 connection                                                                                                       |  |

| IN0B                    | 10  | А         | External LC sensor 0 connection                                                                                                       |  |

| IN1A                    | 11  | Α         | External LC sensor 1 connection                                                                                                       |  |

| IN1B                    | 12  | А         | External LC sensor 1 connection                                                                                                       |  |

| IN2A                    | 13  | А         | External LC sensor 2 connection (LDC1314 only)                                                                                        |  |

| IN2B                    | 14  | Α         | External LC sensor 2 connection (LDC1314 only)                                                                                        |  |

| IN3A                    | 15  | А         | External LC sensor 3 connection (LDC1314 only)                                                                                        |  |

| IN3B                    | 16  | А         | External LC sensor 3 connection (LDC1314 only)                                                                                        |  |

| DAP (2)                 | DAP | N/A       | Connect to Ground                                                                                                                     |  |

<sup>(1)</sup> I = Input, O = Output, P=Power, G=Ground, A=Analog

<sup>(2)</sup> There is an internal electrical connection between the exposed Die Attach Pad (DAP) and the GND pin of the device. Although the DAP can be left floating, for best performance the DAP should be connected to the same potential as the device's GND pin. Do not use the DAP as the primary ground for the device. The device GND pin must always be connected to ground.

## 6 Specifications

## 6.1 Absolute Maximum Ratings

|                  |                                  | MIN  | MAX                  | UNIT |

|------------------|----------------------------------|------|----------------------|------|

| $V_{DD}$         | Supply Voltage Range             |      | 5                    | V    |

| Vi               | Voltage on any pin               | -0.3 | V <sub>DD</sub> +0.3 | V    |

| I <sub>A</sub>   | Input current on any INx pin     | -8   | 8                    | mA   |

| $I_D$            | Input current on any Digital pin | -5   | 5                    | mA   |

| T <sub>j</sub>   | Junction Temperature             | -55  | 150                  | °C   |

| T <sub>stg</sub> | Storage temperature range        | -65  | 150                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                                            |                                                                                |                                                        | VALUE | UNIT |  |

|--------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|-------|------|--|

| LDC131                                     | 2 in WSON-12 package                                                           |                                                        |       |      |  |

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000                                                  |       |      |  |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750                                                   | V     |      |  |

| LDC131                                     | LDC1314 in WQFN-16 package                                                     |                                                        |       |      |  |

|                                            |                                                                                | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 |      |  |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750                                                   | V     |      |  |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

Unless otherwise specified, all limits ensured for  $T_A = 25$ °C,  $V_{DD} = 3.3 \text{ V}$

|                |                       | MIN | NOM MAX | UNIT |

|----------------|-----------------------|-----|---------|------|

| $V_{DD}$       | Supply Voltage        | 2.7 | 3.6     | V    |

| T <sub>A</sub> | Operating Temperature | -40 | 125     | °C   |

#### 6.4 Thermal Information

|                                                         | LDC1312    | LDC1314    |      |

|---------------------------------------------------------|------------|------------|------|

| THERMAL METRIC <sup>(1)</sup>                           | WSON (DNT) | WQFN (RGH) | UNIT |

|                                                         | 12 PINS    | 16 PINS    |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 50         | 38         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.5 Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_A = 25$ °C,  $V_{DD} = 3.3$  V. See <sup>(1)</sup>

|                           |                                                                | X                                                                         | (2)                 | -> (-) (1)         | ×(2)                |      |

|---------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------|---------------------|--------------------|---------------------|------|

|                           | PARAMETER                                                      | TEST CONDITIONS <sup>(2)</sup>                                            | MIN <sup>(3)</sup>  | TYP <sup>(4)</sup> | MAX <sup>(3)</sup>  | UNIT |

| POWER                     |                                                                |                                                                           | 1                   |                    |                     |      |

| $V_{DD}$                  | Supply Voltage                                                 | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                            | 2.7                 |                    | 3.6                 | V    |

| I <sub>DD</sub>           | Supply Current (not including sensor current) (5)              | f <sub>CLKIN</sub> = 10 MHz <sup>(6)</sup>                                | 2.1                 |                    |                     | mA   |

| I <sub>DDSL</sub>         | Sleep Mode Supply Current <sup>(5)</sup>                       | SLEEP_MODE_EN = b1                                                        |                     | 35                 | 60                  | μΑ   |

| I <sub>SD</sub>           | Shutdown Mode Supply<br>Current <sup>(5)</sup>                 | $SD = V_{DD}$                                                             |                     | 0.2                | 1                   | μΑ   |

| SENSOR                    |                                                                |                                                                           | 1                   |                    |                     |      |

| I <sub>SENSORMAX</sub>    | Sensor Maximum Current drive                                   | HIGH_CURRENT_DRV = b0                                                     |                     | 1.5                |                     | mA   |

| R <sub>P</sub>            | Sensor R <sub>P</sub>                                          | DRIVE_CURRENTx = 0xF800                                                   | 1                   |                    | 100                 | kΩ   |

| IHD <sub>SENSORMAX</sub>  | High current sensor drive mode: Sensor Maximum Current         | HIGH_CURRENT_DRV = b1<br>DRIVE_CURRENT0 = 0xF800                          |                     | 6                  |                     | mA   |

| R <sub>P HD MIN</sub>     | Minimum sensor R <sub>P</sub>                                  | Channel 0 only                                                            |                     | 250                |                     | Ω    |

| $f_{\sf SENSOR}$          | Sensor Resonance Frequency                                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                      | 0.001               |                    | 10                  | MHz  |

| V <sub>SENSORMAX</sub>    | Maximum oscillation amplitude (peak)                           |                                                                           |                     | 1.8                |                     | V    |

| N <sub>BITS</sub>         | Number of bits                                                 | RESET_DEV.OUTPUT_GAIN=b00                                                 |                     |                    | 12                  | bits |

| fcs                       | Maximum Channel Sample Rate                                    | RCOUNTx ≥ 0x0400 single active channel continuous conversion, SCL=400 kHz |                     |                    | 13.3                | kSPS |

| C <sub>IN</sub>           | Sensor Pin input capacitance                                   | ,                                                                         |                     | 4                  |                     | pF   |

| DIGITAL PIN LEV           |                                                                |                                                                           |                     |                    |                     |      |

| V <sub>IL</sub>           | Low voltage threshold (ADDR and SD)                            |                                                                           |                     |                    | 0.3*V <sub>DD</sub> | V    |

| V <sub>IH</sub>           | High voltage threshold (ADDR and SD)                           |                                                                           | 0.7*V <sub>DD</sub> |                    |                     | V    |

| V <sub>OL</sub>           | INTB low voltage output level                                  | 3mA sink current                                                          |                     |                    | 0.4                 | V    |

| V <sub>OH</sub>           | INTB high voltage output level                                 |                                                                           | 2.4                 |                    |                     | V    |

| REFERENCE CL              | оск                                                            |                                                                           |                     |                    | +                   |      |

| fCLKIN                    | External Reference Clock Input Frequency (CLKIN)               | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                      | 2                   |                    | 40                  | MHz  |

| CLKIN <sub>DUTY_MIN</sub> | External Reference Clock minimum acceptable duty cycle (CLKIN) |                                                                           |                     | 40%                |                     |      |

| CLKIN <sub>DUTY_MAX</sub> | External Reference Clock maximum acceptable duty cycle (CLKIN) |                                                                           |                     | 60%                |                     |      |

| V <sub>CLKIN_LO</sub>     | CLKIN low voltage threshold                                    |                                                                           |                     |                    | 0.3*V <sub>DD</sub> | V    |

| V <sub>CLKIN_HI</sub>     | CLKIN high voltage threshold                                   |                                                                           | 0.7*V <sub>DD</sub> |                    |                     | V    |

- (1) Electrical Characteristics Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>. Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

- (2) Register values are represented as either binary (b is the prefix to the digits), or hexadecimal (0x is the prefix to the digits). Decimal values have no prefix.

- (3) Limits are ensured by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (4) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

- (5) I<sup>2</sup>C read/write communication and pull-up resistors current through SCL, SDA not included.

- (6) Sensor inductor: 2 layer, 32 turns/layer, 14 mm diameter, PCB inductor with L=19.4 μH, R<sub>P</sub>=5.7 kΩ at 2 MHz Sensor capacitor: 330 pF 1% COG/NP0 Target: Aluminum, 1.5 mm thickness Channel = Channel 0 (continuous mode) f<sub>CLKIN</sub> = 40 MHz, FIN\_DIVIDER0 = b0000, FREF\_DIVIDER0 = 0x0001, RCOUNT0 = 0xFFFF, SETTLECOUNT0 = 0x0100, RP\_OVERRIDE = b1, AUTO\_AMP\_DIS = b1, DRIVE CURRENT0 = 0x9800

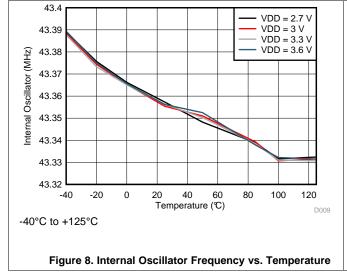

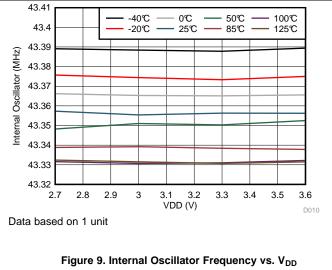

## **Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for  $T_A$  = 25°C,  $V_{DD}$  = 3.3 V. See  $^{(1)}$

|                         | PARAMETER                                                | TEST CONDITIONS <sup>(2)</sup> | MIN <sup>(3)</sup> | TYP <sup>(4)</sup> | MAX <sup>(3)</sup> | UNIT   |

|-------------------------|----------------------------------------------------------|--------------------------------|--------------------|--------------------|--------------------|--------|

| $f_{INTCLK}$            | Internal Reference Clock<br>Frequency range              |                                | 35                 | 43.4               | 55                 | MHz    |

| $T_{Cf\_int\_\mu}$      | Internal Reference Clock<br>Temperature Coefficient mean |                                |                    | -13                |                    | ppm/°C |

| TIMING CHARA            | ACTERISTICS                                              |                                |                    |                    |                    |        |

| t <sub>WAKEUP</sub>     | Wake-up Time from SD high-low transition to I2C readback |                                |                    |                    | 2                  | ms     |

| t <sub>WD-TIMEOUT</sub> | Sensor recovery time (after watchdog timeout)            |                                |                    | 5.2                |                    | ms     |

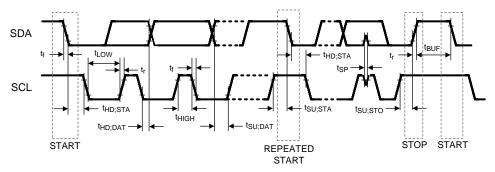

## 6.6 Switching Characteristics - I2C

Unless otherwise specified, all limits ensured for  $T_A$  = 25°C, VDD = 3.3 V

|                     | PARAMETER                                                                        | TEST CONDITIONS                                       | MIN                 | TYP | MAX              | UNIT |

|---------------------|----------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|-----|------------------|------|

| VOLTAGE L           | EVELS                                                                            |                                                       | <u> </u>            |     | <u>'</u>         |      |

| V <sub>IH</sub>     | Input High Voltage                                                               |                                                       | 0.7×V <sub>DD</sub> |     |                  | V    |

| V <sub>IL</sub>     | Input Low Voltage 0.3×V <sub>DD</sub>                                            |                                                       |                     |     | $0.3$ × $V_{DD}$ | V    |

| V <sub>OL</sub>     | Output Low Voltage (3mA sink current)                                            |                                                       |                     |     | V                |      |

| HYS                 | Hysteresis 0.1×V <sub>DD</sub>                                                   |                                                       |                     |     | V                |      |

| I2C TIMING          | CHARACTERISTICS                                                                  |                                                       |                     |     | <u>.</u>         |      |

| $f_{SCL}$           | Clock Frequency                                                                  |                                                       | 10                  |     | 400              | kHz  |

| t <sub>LOW</sub>    | Clock Low Time                                                                   |                                                       | 1.3                 |     |                  | μS   |

| t <sub>HIGH</sub>   | Clock High Time                                                                  |                                                       | 0.6                 |     |                  | μS   |

| t <sub>HD;STA</sub> | Hold Time (repeated) START condition                                             | After this period, the first clock pulse is generated | 0.6                 |     |                  | μS   |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition                                       |                                                       | 0.6                 |     |                  | μS   |

| t <sub>HD;DAT</sub> | Data hold time                                                                   |                                                       | 0                   |     |                  | μS   |

| t <sub>SU;DAT</sub> | Data setup time                                                                  |                                                       | 100                 |     |                  | ns   |

| t <sub>SU;STO</sub> | Set-up time for STOP condition                                                   |                                                       | 0.6                 |     |                  | μS   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                 |                                                       | 1.3                 |     |                  | μS   |

| t <sub>VD;DAT</sub> | Data valid time                                                                  |                                                       |                     |     | 0.9              | μS   |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                                                      |                                                       |                     |     | 0.9              | μS   |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by the input filter <sup>(1)</sup> |                                                       |                     |     | 50               | ns   |

(1) This parameter is specified by design and/or characterization and is not tested in production.

Figure 1. I2C Timing

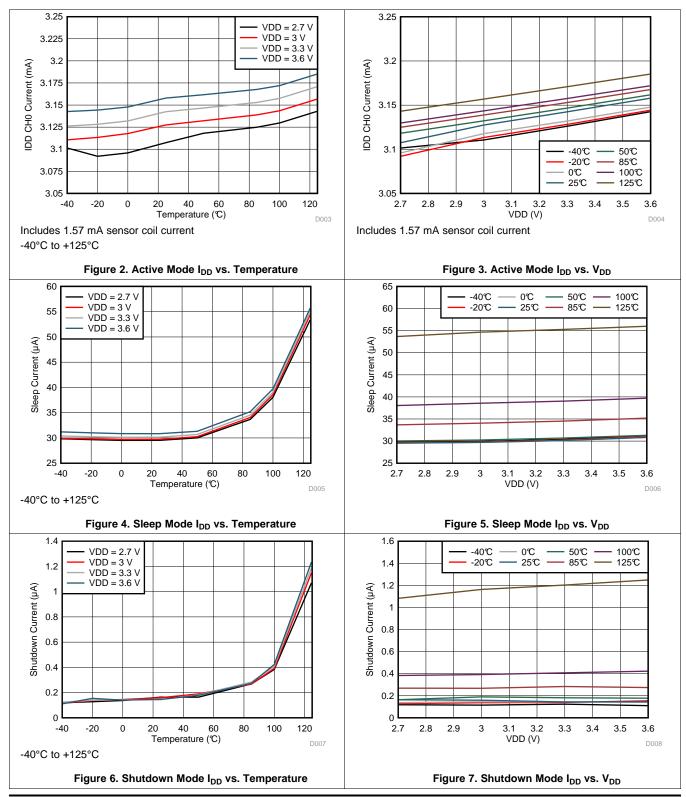

#### 6.7 Typical Characteristics

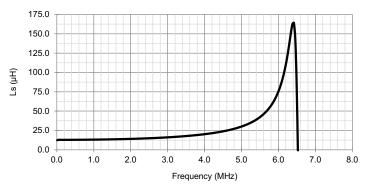

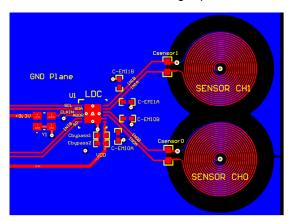

Common test conditions (unless specified otherwise): Sensor inductor: 2 layer, 32 turns/layer, 14 mm diameter, PCB inductor with L=19.4  $\mu$ H, R<sub>P</sub>=5.7 k $\Omega$  at 2 MHz; Sensor capacitor: 330 pF 1% COG/NP0; Target: Aluminum, 1.5 mm thickness; Channel = Channel 0 (continuous mode);  $f_{\text{CLKIN}}$  = 40 MHz, FIN\_DIVIDER0 = 0x1, FREF\_DIVIDER0 = 0x001, RCOUNT0 = 0xFFFF, SETTLECOUNT0 = 0x0100, RP\_OVERRIDE = 1, AUTO\_AMP\_DIS = 1, DRIVE\_CURRENT0 = 0x9800

## **Typical Characteristics (continued)**

Common test conditions (unless specified otherwise): Sensor inductor: 2 layer, 32 turns/layer, 14 mm diameter, PCB inductor with L=19.4  $\mu$ H, R<sub>P</sub>=5.7 k $\Omega$  at 2 MHz; Sensor capacitor: 330 pF 1% COG/NP0; Target: Aluminum, 1.5 mm thickness; Channel = Channel 0 (continuous mode);  $f_{\text{CLKIN}}$  = 40 MHz, FIN\_DIVIDER0 = 0x1, FREF\_DIVIDER0 = 0x001, RCOUNT0 = 0xFFFF, SETTLECOUNT0 = 0x0100, RP\_OVERRIDE = 1, AUTO\_AMP\_DIS = 1, DRIVE\_CURRENT0 = 0x9800

# 7 Detailed Description

#### 7.1 Overview

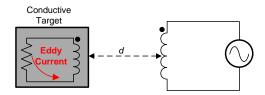

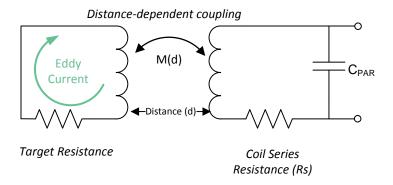

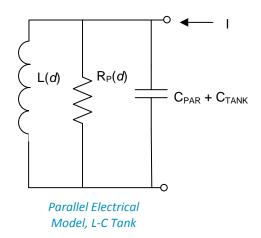

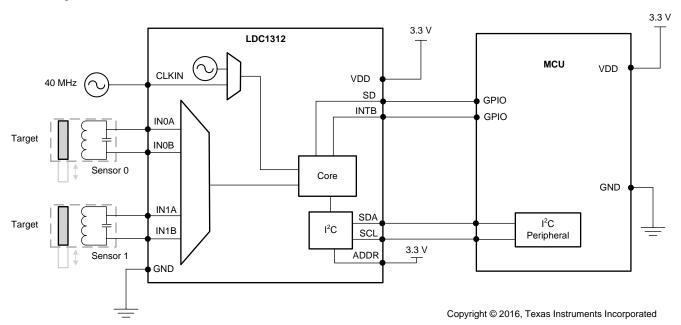

The LDC1312/LDC1314 is an inductance-to-digital converter (LDC) that measures the oscillation frequency of multiple LC resonators. The device outputs a digital value that is proportional to frequency, with 12 bits of measurement resolution. This frequency measurement can be converted to an equivalent inductance, or mapped to the movement of an conductive object. The LDC1312/LDC1314 supports a wide range of inductance and capacitor combinations with oscillation frequencies varying from 1 kHz to 10 MHz with equivalent parallel resistances as low as 1.0 k $\Omega$ . The device includes a stable internal reference to reduce overall system cost, while also providing the option to drive a clean external oscillator for improved measurement noise. The conversion time of the LDC1312/LDC1314 is configurable per channel, where longer conversion times provide higher effective resolution.

The LDC1312/LDC1314 is configured through a 400-kbit/s I2C bus and includes the ADDR input pin to select an address. The power supply of the device ranges from 2.7 V to 3.6 V. The only external components necessary for operation are the supply bypassing capacitors and I2C pull-ups.

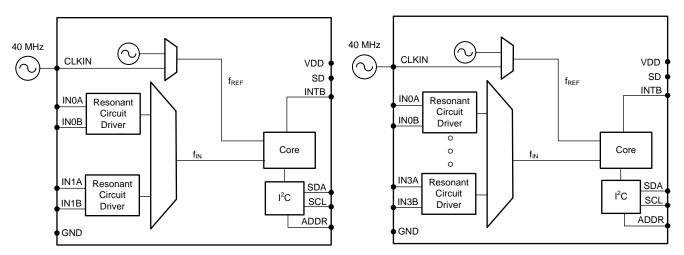

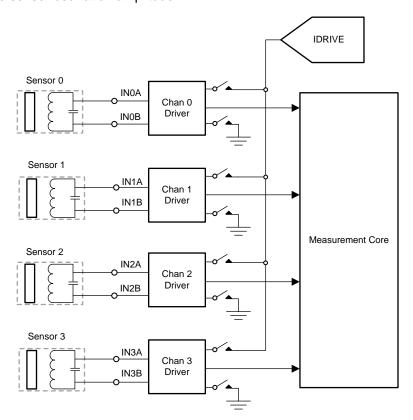

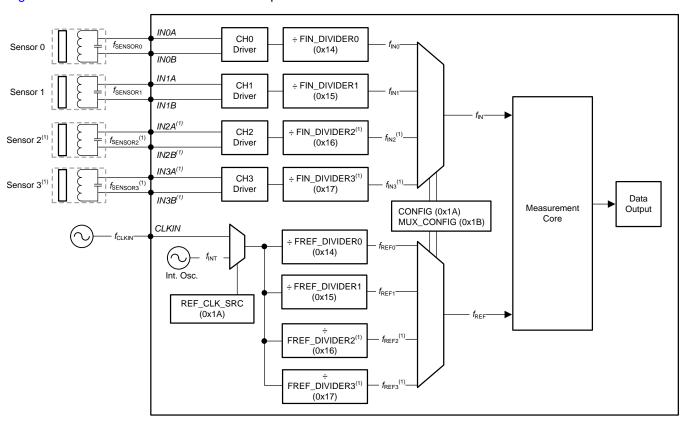

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 10. Block Diagrams for the LDC1312 (Left) and LDC1314 (Right)

The LDC1312/LDC1314 is composed of front-end resonant circuit drivers, followed by a multiplexer that sequences through the active channels, connecting them to the core that measures and digitizes the sensor frequency ( $f_{\rm SENSOR}$ ). The core uses a reference frequency ( $f_{\rm REF}$ ) to measure the sensor frequency.  $f_{\rm REF}$  is derived from either the internal reference clock (oscillator), or an externally supplied clock. The digitized output for each channel is proportional to the ratio of  $f_{\rm SENSOR}/f_{\rm REF}$ . The I2C interface is used to support device configuration and to transmit the digitized frequency values to a host processor. The LDC can be placed in an inactive shutdown mode to reduce current consumption by setting the SD pin to  $V_{\rm DD}$ . The INTB pin may be configured to notify the host of changes in system status.

## 7.3 Feature Description

#### 7.3.1 Multi-Channel and Single Channel Operation

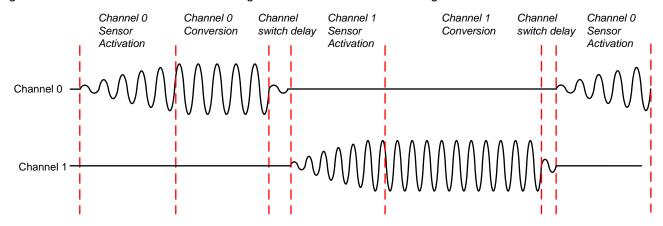

The LDC1312/LDC1314 provides flexibility in channel sampling. It can continuously convert on any available single channel or automatically sequence conversions across multiple channels. When operated in multi-channel mode, the LDC sequentially samples the selected channels. In single channel mode, the LDC continuously samples only the selected channel.

#### **Feature Description (continued)**

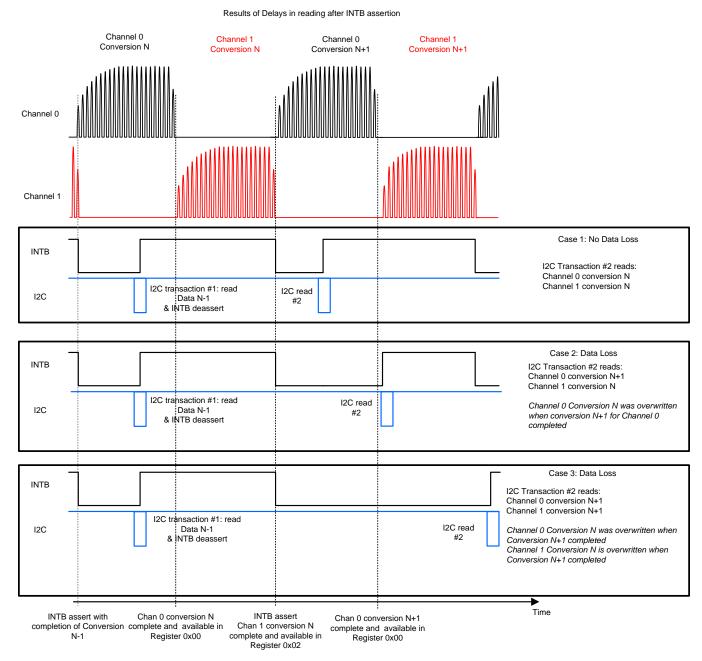

At the end of each conversion in single channel mode, or after converting all selected channels when in multichannel mode, the LDC1312/LDC1314 can be configured to assert the INTB pin to indicate completion of the conversion.

Refer to *Multi-Channel and Single Channel Operation* for details on the LDC1312/LDC1314 channel functionality and configuration.

#### 7.3.2 Adjustable Conversion Time

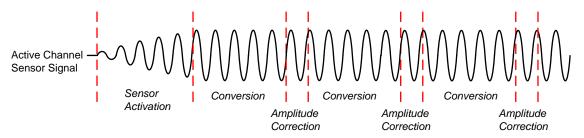

The LDC1312/LDC1314 conversion provides a tradeoff between measurement resolution and conversion interval. Longer conversion intervals have higher measurement resolution. The conversion interval can be configured from 3.2 µs to >26.2 ms with 16 bits of resolution. Note that it is possible to configure the conversion interval to be shorter than the time required to read back the DATAx registers. The LDC1312/LDC1314 supports per-channel adjustment of the conversion interval by setting the RCOUNTx register.

Refer to Sensor Conversion Time for details on the LDC1312/LDC1314 configuration and details on the setting conversion interval.

## 7.3.3 Digital Signal Gain

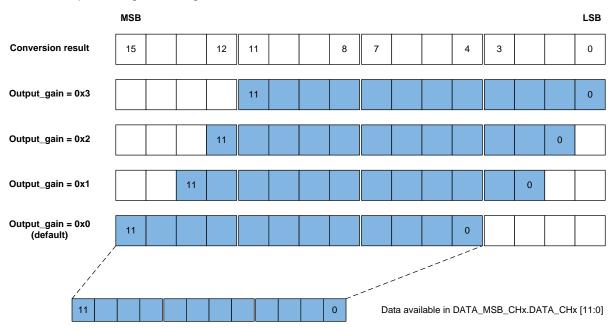

The LDC1312/LDC1314 output resolution is 12 bits, but the internal signal path supports 16 bits of output resolution by use of the GAIN setting.

Refer to Digital Signal Gain for details on the configuration and details on the setting conversion interval.

#### 7.3.4 Sensor Startup and Glitch Configuration

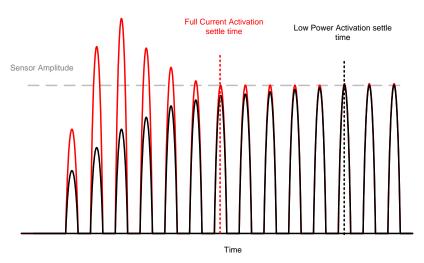

For minimum noise, the sensor measurement should be performed after the sensor amplitude has stabilized. The LDC1312/LDC1314 provides an adjustable sensor startup timing per channel. The timing can be varied from 1.2 µs to >26.2 ms by setting the SETTLECOUNTx register. Sensors with lower resonant frequencies or higher Qs may require additional time to stabilize.

Refer to Settling Time for details on the LDC1312/LDC1314 configuration and details on the setting conversion interval.

The LDC1312/LDC1314 can be configured with a faster sensor activation, or to use a lower current sensor activation. Refer to Sensor Activation for details on this capability.

The LDC1312/LDC1314 provides an internal filter to attenuate interference from external noise sources. Refer to *Input Deglitch Filter* for information on configuration on the deglitch filter.

#### 7.3.5 Reference Clock

Optimum LDC1312/LDC1314 performance requires a clean reference clock. This reference frequency is equivalent to the reference voltage of an Analog-to-Digital converter. The LDC1312/LDC1314 provide an internal reference oscillator with a typical frequency of 43 MHz. This internal oscillator has good stability, with a typical temperature coefficient of -13 ppm/°C. For applications requiring higher resolution or improved performance across temperature, an external reference frequency can be applied to the CLKIN input.

The LDC1312/LDC1314 provides digital dividers for the  $f_{\rm CLK}$  and the sensor inputs to adjust the effective frequency measured by the LDC core. The dividers provide flexibility in system design, so that the full range of sensor frequencies can be supported with a wide range of  $f_{\rm CLK}$ . Each channel has a dedicated divider configuration. Higher reference frequencies provide a higher sample rate for a given resolution.

Refer to *Reference Clock* for details on clocking requirements, configuration, and divider setup.

#### **Feature Description (continued)**

#### 7.3.6 Sensor Current Drive Control

The lossy characteristic of the sensors used for inductive sensing require injection of energy to maintain a constant sensor amplitude. The LDC1312/LDC1314 provides this energy by driving an AC current matching the sensor resonant frequency across the LC sensor. To achieve optimum performance, it is necessary to set the current drive so that the sensor amplitude is within the range of 1.2  $V_P$  to 1.8  $V_P$ . Each channel current drive is set independently between 16  $\mu$ A and 1.6 mA by setting the corresponding IDRIVEx register field. The LDC1312/LDC1314 can also automatically determine the appropriate sensor current drive, and even dynamically adjust the sensor current by use of the RP\_OVERRIDE\_EN function.

Refer to Sensor Current Drive Configuration for detailed information on configuration of the sensor drive.

#### 7.3.7 Device Status Monitoring

The LDC1312/LDC1314 can monitor attached sensors and can report on device status and sensor status via the I2C interface. Reported conditions include:

- Sensor Amplitude outside of optimum range

- · Sensor unable to oscillate

- New conversion data available

- · Conversion errors

Use of this monitoring functionality can alert the system MCU of unexpected conditions such as sensor damage. Refer to *Device Status Registers* for more information.

#### 7.4 Device Functional Modes

#### 7.4.1 Startup Mode

When the LDC powers up, it enters into Sleep Mode and will wait for configuration. Once the device is configured, exit Sleep Mode and begin conversions by setting CONFIG.SLEEP\_MODE\_EN to b0.

It is recommended to configure the LDC while in Sleep Mode. If a setting on the LDC needs to be changed, return the device to Sleep Mode, change the appropriate register, and then exit Sleep Mode.

#### 7.4.2 Sleep Mode (Configuration Mode)

Sleep Mode is entered by setting the CONFIG.SLEEP\_MODE\_EN register field to 1. While in this mode, the device configuration is retained, but the device does not perform conversions. To enter Normal mode to perform conversions, set the CONFIG.SLEEP\_MODE\_EN register field to 0. After setting CONFIG.SLEEP\_MODE\_EN to b0, sensor activation for the first conversion will begin after  $16,384 \div f_{\text{INT}}$  elapses. Refer to *Clocking Architecture* for more information on the device timing.

While in Sleep Mode the I2C interface is functional so that register reads and writes can be performed. Entering Sleep Mode will clear all conversion results, any error conditions, and de-assert the INTB pin.

For applications which do not require continuous conversions, returning the device to Sleep mode after completion and readback of the desired number of conversions can provide power consumption savings. Refer to the TI Applications Note *Power Reduction Techniques for the LDC131x/161x for Inductive Sensing* for more information.

#### 7.4.3 Normal (Conversion) Mode

When operating in the normal (conversion) mode, the LDC is repeatedly sampling the frequency of the sensor(s) and generating sample outputs for the active channel(s) based on the device configuration.

#### 7.4.4 Shutdown Mode

When the SD pin is set to high, the LDC will enter Shutdown Mode. Shutdown Mode is the lowest power state. To exit Shutdown Mode and enter Sleep Mode, set the SD pin to low. Entering Shutdown Mode will return all registers to their default state.

#### **Device Functional Modes (continued)**

While in Shutdown Mode, no conversions are performed. In addition, entering Shutdown Mode will clear any error condition and de-assert the INTB pin (when de-asserted, INTB will be actively driven high). While the device is in Shutdown Mode, is not possible to read to or write from the device via the I2C interface.

It is permitted to change the ADDR pin setting while in Shutdown Mode.

#### 7.4.4.1 Reset

The device can be reset by writing to RESET\_DEV.RESET\_DEV. Any active conversion will stop and all registers will return to their default values. This register bit will always return 0b when read.

## 7.5 Programming

The LDC1312/4 device uses an I2C interface to access control and data registers. The recommended configuration procedure is to put the device into Sleep Mode, set the appropriate registers, and then enter Normal Mode. Conversion results must be read while the device is in Normal Mode. Setting the device into Shutdown mode will reset the device configuration.

## 7.5.1 I2C Interface Specifications

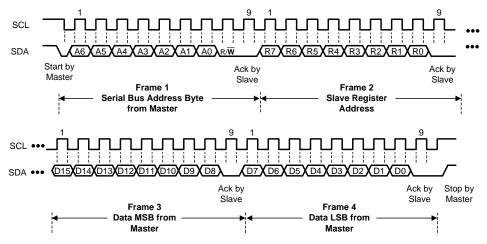

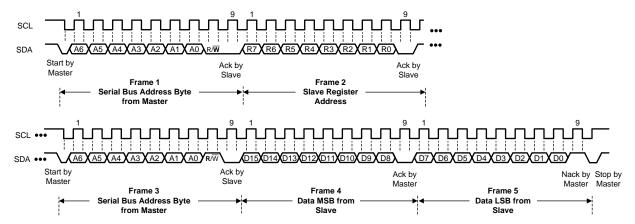

The LDC1312/4 use I2C for register access with a maximum speed of 400 kbit/s. The device registers are 16 bits wide, and so a repeated start is used to access the 2<sup>nd</sup> byte of data. This sequence follows the standard I2C 7bit slave address followed by an 8 bit pointer register byte to set the register address. Refer to Figure 11 and Figure 12 for proper protocol diagrams. The device does not use I2C clock stretching.

When the ADDR pin is set low, the device I2C address is 0x2A; when the ADDR pin is set high, the I2C address is 0x2B. The ADDR pin setting can be changed while the device is in Shutdown Mode to select the alternate I2C address.

Figure 11. I2C Write Register Sequence

## **Programming (continued)**

Figure 12. I2C Read Register Sequence

#### 7.5.2 Pulses on I2C

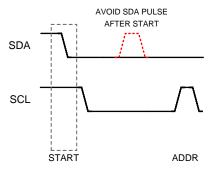

The I2C interface of the LDC is designed to operate with the standard I2C transactions detailed in the I2C specification; however it is not suitable for use in an I2C system which supports early termination of transactions. A STOP condition or other early termination occurring before the normal end of a transaction (ACK) is not supported and may corrupt that transaction and/or the following transaction. The device is also sensitive to any (extraneous) pulse on SDA during the SCL low period of the first bit position of the i2c\_address byte. To ensure proper LDC operation, the master device should not transmit this type of waveform. An example of an unsupported I2C waveform is shown in Figure 13. Any such pulses should not have a duration which exceeds the device t<sub>SP</sub> specification.

Figure 13. Example of SDA Pulse Between I2C START and ADDR Which Must be Avoided by the I2C Master

## 7.6 Register Maps

## 7.6.1 Register List

Fields indicated with **Reserved** must be written only with indicated value, otherwise improper device operation may occur. The R/W column indicates the Read-Write status of the corresponding field. A 'R/W' entry indicates read and write capability, a 'R' indicates read-only, and a 'W' indicates write-only.

For registers with R and R/W fields, write the reset value to the field when setting the R/W fields.

Figure 14. Register List

| ADDRESS | NAME            | DEFAULT VALUE | DESCRIPTION                                                        |

|---------|-----------------|---------------|--------------------------------------------------------------------|

| 0x00    | DATA0           | 0x0000        | Channel 0 Conversion Result and Error Status                       |

| 0x02    | DATA1           | 0x0000        | Channel 1 Conversion Result and Error Status                       |

| 0x04    | DATA2           | 0x0000        | Channel 2 Conversion Result and Error Status (LDC1314 only)        |

| 0x06    | DATA3           | 0x0000        | Channel 3 Conversion Result and Error Status (LDC1314 only)        |

| 0x08    | RCOUNT0         | 0x0080        | Reference Count setting for Channel 0                              |

| 0x09    | RCOUNT1         | 0x0080        | Reference Count setting for Channel 1                              |

| 0x0A    | RCOUNT2         | 0x0080        | Reference Count setting for Channel 2. (LDC1314 only)              |

| 0x0B    | RCOUNT3         | 0x0080        | Reference Count setting for Channel 3.(LDC1314 only)               |

| 0x0C    | OFFSET0         | 0x0000        | Offset value for Channel 0                                         |

| 0x0D    | OFFSET1         | 0x0000        | Offset value for Channel 1                                         |

| 0x0E    | OFFSET2         | 0x0000        | Offset value for Channel 2 (LDC1314 only)                          |

| 0x0F    | OFFSET3         | 0x0000        | Offset value for Channel 3 (LDC1314 only)                          |

| 0x10    | SETTLECOUNT0    | 0x0000        | Channel 0 Settling Reference Count                                 |

| 0x11    | SETTLECOUNT1    | 0x0000r_      | Channel 1 Settling Reference Count                                 |

| 0x12    | SETTLECOUNT2    | 0x0000        | Channel 2 Settling Reference Count (LDC1314 only)                  |

| 0x13    | SETTLECOUNT3    | 0x0000        | Channel 3 Settling Reference Count (LDC1314 only)                  |

| 0x14    | CLOCK_DIVIDERS0 | 0x0000        | Reference and Sensor Divider settings for Channel 0                |

| 0x15    | CLOCK_DIVIDERS1 | 0x0000        | Reference and Sensor Divider settings for Channel 1                |

| 0x16    | CLOCK_DIVIDERS2 | 0x0000        | Reference and Sensor Divider settings for Channel 2 (LDC1314 only) |

| 0x17    | CLOCK_DIVIDERS3 | 0x0000        | Reference and Sensor Divider settings for Channel 3 (LDC1314 only) |

| 0x18    | STATUS          | 0x0000        | Device Status Report                                               |

| 0x19    | ERROR_CONFIG    | 0x0000        | Error Reporting Configuration                                      |

| 0x1A    | CONFIG          | 0x2801        | Conversion Configuration                                           |

| 0x1B    | MUX_CONFIG      | 0x020F        | Channel Multiplexing Configuration                                 |

| 0x1C    | RESET_DEV       | 0x0000        | Reset Device                                                       |

| 0x1E    | DRIVE_CURRENT0  | 0x0000        | Channel 0 sensor current drive configuration                       |

| 0x1F    | DRIVE_CURRENT1  | 0x0000        | Channel 1 sensor current drive configuration                       |

| 0x20    | DRIVE_CURRENT2  | 0x0000        | Channel 2 sensor current drive configuration (LDC1314 only)        |

| 0x21    | DRIVE_CURRENT3  | 0x0000        | Channel 3 sensor current drive configuration (LDC1314 only)        |

| 0x7E    | MANUFACTURER_ID | 0x5449        | Manufacturer ID                                                    |

| 0x7F    | DEVICE_ID       | 0x3054        | Device ID                                                          |

## 7.6.2 Address 0x00, DATA0

## Figure 15. Address 0x00, DATA0

| 15          | 14      | 13      | 12      | 11          | 10 | 9 | 8 |

|-------------|---------|---------|---------|-------------|----|---|---|

| ERR_UR0     | ERR_OR0 | ERR_WD0 | ERR_AE0 | DATA0[11:0] |    |   |   |

| 7           | 6       | 5       | 4       | 3           | 2  | 1 | 0 |

| DATA0[11:0] |         |         |         |             |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 1. Address 0x00, DATA0 Field Descriptions

| Bit  | Field       | Туре | Reset | Description                                                                  |

|------|-------------|------|-------|------------------------------------------------------------------------------|

| 15   | ERR_UR0     | R    | 0     | Channel 0 Conversion Under-range Error Flag Cleared by reading the bit.      |

| 14   | ERR_OR0     | R    | 0     | Channel 0 Conversion Over-range Error Flag Cleared by reading the bit.       |

| 13   | ERR_WD0     | R    | 0     | Channel 0 Conversion Watchdog Timeout Error Flag Cleared by reading the bit. |

| 12   | ERR_AE0     | R    | 0     | Channel 0 Conversion Amplitude Error Flag. Cleared by reading the bit.       |

| 11:0 | DATA0[11:0] | R    | 0x000 | Channel 0 Conversion Result                                                  |

## 7.6.3 Address 0x02, DATA1

## Figure 16. Address 0x02, DATA1

| 15          | 14      | 13      | 12      | 11 | 10          | 9 | 8 |

|-------------|---------|---------|---------|----|-------------|---|---|

| ERR_UR1     | ERR_OR1 | ERR_WD1 | ERR_AE1 |    | DATA1[11:0] |   |   |

| 7           | 6       | 5       | 4       | 3  | 2           | 1 | 0 |

| DATA1[11:0] |         |         |         |    |             |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 2. Address 0x02, DATA1 Field Descriptions

| Bit  | Field       | Туре | Reset | Description                                                                  |

|------|-------------|------|-------|------------------------------------------------------------------------------|

| 15   | ERR_UR1     | R    | 0     | Channel 1 Conversion Under-range Error Flag<br>Cleared by reading the bit.   |

| 14   | ERR_OR1     | R    | 0     | Channel 1 Conversion Over-range Error Flag Cleared by reading the bit.       |

| 13   | ERR_WD1     | R    | 0     | Channel 1 Conversion Watchdog Timeout Error Flag Cleared by reading the bit. |

| 12   | ERR_AE1     | R    | 0     | Channel 1 Conversion Amplitude Error Flag Cleared by reading the bit.        |

| 11:0 | DATA1[11:0] | R    | 0x000 | Channel 1 Conversion Result                                                  |

## 7.6.4 Address 0x04, DATA2 (LDC1314 only)

## Figure 17. Address 0x04, DATA2

| 15          | 14      | 13      | 12      | 11          | 10 | 9 | 8 |

|-------------|---------|---------|---------|-------------|----|---|---|

| ERR_UR2     | ERR_OR2 | ERR_WD2 | ERR_AE2 | DATA2[11:0] |    |   |   |

| 7           | 6       | 5       | 4       | 3           | 2  | 1 | 0 |

| DATA2[11:0] |         |         |         |             |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 3. Address 0x04, DATA2 Field Descriptions

| Bit  | Field       | Туре | Reset | Description                                                                  |

|------|-------------|------|-------|------------------------------------------------------------------------------|

| 15   | ERR_UR2     | R    | 0     | Channel 2 Conversion Under-range Error Flag Cleared by reading the bit.      |

| 14   | ERR_OR2     | R    | 0     | Channel 2 Conversion Over-range Error Flag Cleared by reading the bit.       |

| 13   | ERR_WD2     | R    | 0     | Channel 2 Conversion Watchdog Timeout Error Flag Cleared by reading the bit. |

| 12   | ERR_AE2     | R    | 0     | Channel 2 Conversion Amplitude Error Flag Cleared by reading the bit.        |

| 11:0 | DATA2[11:0] | R    | 0x000 | Channel 2 Conversion Result                                                  |

## 7.6.5 Address 0x06, DATA3 (LDC1314 only)

## Figure 18. Address 0x06, DATA3

| 15      | 14      | 13      | 12       | 11       | 10 | 9 | 8 |

|---------|---------|---------|----------|----------|----|---|---|

| ERR_UR3 | ERR_OR3 | ERR_WD3 | ERR_AE3  |          |    |   |   |

| 7       | 6       | 5       | 1        | 3        | 2  | 1 | 0 |

| 7 6 5 4 |         |         |          | 3 [11:0] | 2  |   | 0 |

|         |         |         | Dittitte | 5 [11.0] |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 4. Address 0x06, DATA3 Field Descriptions

| Bit  | Field       | Туре | Reset | Description                                                                  |

|------|-------------|------|-------|------------------------------------------------------------------------------|

| 15   | ERR_UR3     | R    | 0     | Channel 3 Conversion Under-range Error Flag<br>Cleared by reading the bit.   |

| 14   | ERR_OR3     | R    | 0     | Channel 3 Conversion Over-range Error Flag<br>Cleared by reading the bit.    |

| 13   | ERR_WD3     | R    | 0     | Channel 3 Conversion Watchdog Timeout Error Flag Cleared by reading the bit. |

| 12   | ERR_AE3     | R    | 0     | Channel 3 Conversion Amplitude Error Flag<br>Cleared by reading the bit.     |

| 11:0 | DATA3[11:0] | R    | 0x000 | Channel 3 Conversion Result                                                  |

#### 7.6.6 Address 0x08, RCOUNT0

#### Figure 19. Address 0x08, RCOUNT0

| 15      | 14 | 13 | 12   | 11   | 10 | 9 | 8 |

|---------|----|----|------|------|----|---|---|

|         |    |    | RCOL | JNT0 |    |   |   |

| 7       | 6  | 5  | 4    | 3    | 2  | 1 | 0 |

| RCOUNT0 |    |    |      |      |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 5. Address 0x08, RCOUNT0 Field Descriptions

| Bit  | Field   | Туре | Reset | Description                                                                                                                                                   |

|------|---------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | RCOUNT0 | R/W  |       | Channel 0 Reference Count Conversion Interval Time 0x0000-0x0004: Reserved 0x0005-0xFFFF: Conversion Time (t <sub>C0</sub> ) = (RCOUNT0×16)/f <sub>REF0</sub> |

## 7.6.7 Address 0x09, RCOUNT1

#### Figure 20. Address 0x09, RCOUNT1

| 15 | 14      | 13 | 12   | 11   | 10 | 9 | 8 |

|----|---------|----|------|------|----|---|---|

|    |         |    | RCOL | JNT1 |    |   |   |

|    |         |    |      |      |    |   |   |

| 7  | 6       | 5  | 4    | 3    | 2  | 1 | 0 |

|    | RCOUNT1 |    |      |      |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 6. Address 0x09, RCOUNT1 Field Descriptions

| Bit  | Field   | Туре | Reset | Description                                                                                                                                                  |

|------|---------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | RCOUNT1 | R/W  |       | Channel 1 Reference Count Conversion Interval Time 0x0000-0x0004: Reserved 0x0005-0xFFFF: Conversion Time (t <sub>C1</sub> )= (RCOUNT1×16)/f <sub>REF1</sub> |

#### 7.6.8 Address 0x0A, RCOUNT2 (LDC1314 only)

## Figure 21. Address 0x0A, RCOUNT2

|                 | 15       | 14 | 13 | 12  | 11   | 10      | 9 | 8 |  |  |  |  |  |

|-----------------|----------|----|----|-----|------|---------|---|---|--|--|--|--|--|

|                 | RCOUNT2  |    |    |     |      |         |   |   |  |  |  |  |  |

| 7 0 5 4 0 0 4 0 |          |    |    |     |      | 0       |   |   |  |  |  |  |  |

|                 | PCOLINTS |    |    |     |      |         |   |   |  |  |  |  |  |

|                 |          |    |    | RCO | UNIZ | RCOUNT2 |   |   |  |  |  |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 7. Address 0x0A, RCOUNT2 Field Descriptions

| Bit  | Field   | Туре | Reset  | Description                                                                                                                                       |

|------|---------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | RCOUNT2 | R/W  | 0x0080 | Channel 2 Reference Count Conversion Interval Time $0x0000-0x0004$ : Reserved $0x0005-0xFFFF$ : Conversion Time $(t_{C2})=(RCOUNT2^x16)/f_{REF2}$ |

#### 7.6.9 Address 0x0B, RCOUNT3 (LDC1314 only)

#### Figure 22. Address 0x0B, RCOUNT3

| 15              | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|-----------------|----|----|----|----|----|---|---|

| RCOUNT3         |    |    |    |    |    |   |   |

| 7 6 5 4 3 2 1 0 |    |    |    |    |    |   | 0 |

| RCOUNT3         |    |    |    |    |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 8. Address 0x0B, RCOUNT3 Field Descriptions

| Bit  | Field   | Туре | Reset | Description                                                                                                                                      |

|------|---------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | RCOUNT3 | R/W  |       | Channel 3 Reference Count Conversion Interval Time 0x0000-0x0004: Reserved 0x0005-0xFFFF: Conversion Time ( $t_{C3}$ )= (RCOUNT3×16)/ $f_{REF3}$ |

## 7.6.10 Address 0x0C, OFFSET0

#### Figure 23. Address 0x0C, OFFSET0

| 15      | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---------|----|----|----|----|----|---|---|

| OFFSET0 |    |    |    |    |    |   |   |

|         |    |    |    |    |    |   |   |

| 7       | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

| OFFSET0 |    |    |    |    |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### **Table 9. OFFSET0 Field Descriptions**

| Bit  | Field   | Туре | Reset  | Description                                                                       |

|------|---------|------|--------|-----------------------------------------------------------------------------------|

| 15:0 | OFFSET0 | R/W  | 0x0000 | Channel 0 Conversion Offset $f_{OFFSET0} = (OFFSET0 \div 2^{16}) \times f_{REF0}$ |

#### 7.6.11 Address 0x0D, OFFSET1

#### Figure 24. Address 0x0D, OFFSET1

| 15              | 14      | 13 | 12 | 11 | 10 | 9 | 8 |  |

|-----------------|---------|----|----|----|----|---|---|--|

|                 | OFFSET1 |    |    |    |    |   |   |  |

| 7 6 5 4 3 2 1 0 |         |    |    |    |    | 0 |   |  |

| OFFSET1         |         |    |    |    |    |   |   |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 10. Address 0x0D, OFFSET1 Field Descriptions

| Bit  | Field   | Туре | Reset  | Description                                                                       |

|------|---------|------|--------|-----------------------------------------------------------------------------------|

| 15:0 | OFFSET1 | R/W  | 0x0000 | Channel 1 Conversion Offset $f_{OFFSET1} = (OFFSET1 \div 2^{16}) \times f_{REF1}$ |

#### 7.6.12 Address 0x0E, OFFSET2 (LDC1314 only)

## Figure 25. Address 0x0E, OFFSET2

| 15              | 14 | 13 | 12 | 11 | 10 | 9 | 8 |  |

|-----------------|----|----|----|----|----|---|---|--|

| OFFSET2         |    |    |    |    |    |   |   |  |

| 7 6 5 4 3 2 1 0 |    |    |    |    |    | 0 |   |  |

| OFFSET2         |    |    |    |    |    |   |   |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 11. Address 0x0E, OFFSET2 Field Descriptions

| Bit  | Field   | Туре | Reset  | Description                                                                          |

|------|---------|------|--------|--------------------------------------------------------------------------------------|

| 15:0 | OFFSET2 | R/W  | 0x0000 | Channel 2 Conversion Offset $f_{OFFSET\ 2} = (OFFSET^2 \div 2^{16}) \times f_{REF2}$ |

## 7.6.13 Address 0x0F, OFFSET3 (LDC1314 only)

## Figure 26. Address 0x0F, OFFSET3

| 15              | 14      | 13 | 12 | 11 | 10 | 9 | 8 |  |

|-----------------|---------|----|----|----|----|---|---|--|

|                 | OFFSET3 |    |    |    |    |   |   |  |

| 7 6 5 4 3 2 1 0 |         |    |    |    |    | 0 |   |  |

| OFFSET3         |         |    |    |    |    |   |   |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 12. Address 0x0F, OFFSET3 Field Descriptions

| Bit  | Field   | Туре | Reset  | Description                                                                       |

|------|---------|------|--------|-----------------------------------------------------------------------------------|

| 15:0 | OFFSET3 | R/W  | 0x0000 | Channel 3 Conversion Offset $f_{OFFSET3} = (OFFSET3 \div 2^{16}) \times f_{REF3}$ |

#### 7.6.14 Address 0x10, SETTLECOUNT0

#### Figure 27. Address 0x10, SETTLECOUNT0

| 15 | 14 | 13 | 12     | 11     | 10 | 9 | 8 |

|----|----|----|--------|--------|----|---|---|

|    |    |    | SETTLE | COUNT0 |    |   |   |

| 7  | 6  | 5  | 4      | 3      | 2  | 1 | 0 |

|    |    |    | SETTLE | COUNT0 |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 13. Address 0x10, SETTLECOUNT0 Field Descriptions

| Bit  | Field        | Туре | Reset  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|--------------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | SETTLECOUNT0 | R/W  | 0x0000 | Channel 0 Conversion Settling The LDC will use this settling time to allow the LC sensor to stabilize before initiation of a conversion on Channel 0. If the amplitude has not settled prior to the conversion start, an Amplitude error will be generated if reporting of this type of error is enabled. 0x0000: Settle Time $(t_{S0})$ = $32 \div f_{REF0}$ 0x0001: Settle Time $(t_{S0})$ = $32 \div f_{REF0}$ 0x0002 - 0xFFFF: Settle Time $(t_{S0})$ = (SETTLECOUNT0×16) $\div f_{REF0}$ |

#### 7.6.15 Address 0x11, SETTLECOUNT1

#### Figure 28. Address 0x11, SETTLECOUNT1

| 15 | 14           | 13 | 12 | 11 | 10 | 9 | 8 |

|----|--------------|----|----|----|----|---|---|

|    | SETTLECOUNT1 |    |    |    |    |   |   |

| 7  | 6            | 5  | 4  | 3  | 2  | 1 | 0 |

|    | SETTLECOUNT1 |    |    |    |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 14. Address 0x11, SETTLECOUNT1 Field Descriptions

| Bit  | Field        | Туре | Reset  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | SETTLECOUNT1 | R/W  | 0x0000 | Channel 1 Conversion Settling The LDC will use this settling time to allow the LC sensor to stabilize before initiation of a conversion on a Channel 1. If the amplitude has not settled prior to the conversion start, an Amplitude error will be generated if reporting of this type of error is enabled. $0x0000$ : Settle Time $(t_{S1})$ = $32 \div f_{REF1}$ $0x0001$ : Settle Time $(t_{S1})$ = $32 \div f_{REF1}$ $0x0002 - 0xFFFF$ : Settle Time $(t_{S1})$ = (SETTLECOUNT1×16) $\div f_{REF1}$ |

## 7.6.16 Address 0x12, SETTLECOUNT2 (LDC1314 only)

## Figure 29. Address 0x12, SETTLECOUNT2

| 15 | 14           | 13 | 12 | 11 | 10 | 9 | 8 |

|----|--------------|----|----|----|----|---|---|

|    | SETTLECOUNT2 |    |    |    |    |   |   |

| 7  | 6            | 5  | 4  | 3  | 2  | 1 | 0 |

|    | SETTLECOUNT2 |    |    |    |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 15. Address 0x12, SETTLECOUNT2 Field Descriptions

| Bit  | Field        | Туре | Reset  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|--------------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | SETTLECOUNT2 | R/W  | 0x0000 | Channel 2 Conversion Settling The LDC will use this settling time to allow the LC sensor to stabilize before initiation of a conversion on Channel 2. If the amplitude has not settled prior to the conversion start, an Amplitude error will be generated if reporting of this type of error is enabled. 0x0000: Settle Time ( $t_{S2}$ )= $32 \div f_{REF2}$ 0x0001: Settle Time ( $t_{S2}$ )= $32 \div f_{REF2}$ 0x0002 - 0xFFFF: Settle Time ( $t_{S2}$ )= (SETTLECOUNT2×16) $\div f_{REF2}$ |

## 7.6.17 Address 0x13, SETTLECOUNT3 (LDC1314 only)

## Figure 30. Address 0x13, SETTLECOUNT3

| 15 | 14           | 13 | 12     | 11     | 10 | 9 | 8 |

|----|--------------|----|--------|--------|----|---|---|

|    |              |    | SETTLE | COUNT3 |    |   |   |

| 7  | 6            | 5  | 4      | 3      | 2  | 1 | 0 |

|    | SETTLECOUNT3 |    |        |        |    |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 16. Address 0x13, SETTLECOUNT3 Field Descriptions

| Bit  | Field        | Туре | Reset  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | SETTLECOUNT3 | R/W  | 0x0000 | Channel 3 Conversion Settling The LDC will use this settling time to allow the LC sensor to stabilize before initiation of a conversion on Channel 3. If the amplitude has not settled prior to the conversion start, an Amplitude error will be generated if reporting of this type of error is enabled 0x0000: Settle Time ( $t_{S3}$ )= 32 ÷ $f_{REF3}$ 0x0001: Settle Time ( $t_{S3}$ )= 32 ÷ $f_{REF3}$ 0x0002 - 0xFFFF: Settle Time ( $t_{S3}$ )= (SETTLECOUNT3×16) ÷ $f_{REF3}$ |

## 7.6.18 Address 0x14, CLOCK\_DIVIDERS0

## Figure 31. Address 0x14, CLOCK\_DIVIDERS0

| 15           | 14 | 13 | 12      | 11     | 10   | 9      | 8       |

|--------------|----|----|---------|--------|------|--------|---------|

| FIN_DIVIDER0 |    |    |         | RESE   | RVED | FREF_D | IVIDER0 |

| 7            | 6  | 5  | 4       | 3      | 2    | 1      | 0       |

|              |    |    | FREF_DI | VIDER0 |      |        |         |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 17. Address 0x14, CLOCK\_DIVIDERS0 Field Descriptions

| Bit   | Field         | Туре | Reset | Description                                                                                                                                                                                                                       |

|-------|---------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | FIN_DIVIDER0  | R/W  | 0000  | Channel 0 Input Divider Sets the divider for Channel 0 input. Must be set to ≥2 if the Sensor frequency is ≥ 8.75MHz b0000: Reserved. Do not use. FIN_DIVIDER0 ≥ b0001: $f_{\text{in0}} = f_{\text{SENSOR0}}/\text{FIN_DIVIDER0}$ |

| 11:10 | RESERVED      | R/W  | 00    | Reserved. Set to b00.                                                                                                                                                                                                             |

| 9:0   | FREF_DIVIDER0 | R/W  | 0x000 | Channel 0 Reference Divider Sets the divider for Channel 0 reference. Use this to scale the maximum conversion frequency.  0x000: Reserved. Do not use.  FREF_DIVIDER0 $\geq$ 0x001: $f_{REF0} = f_{CLK}/FREF_DIVIDER0$           |

#### 7.6.19 Address 0x15, CLOCK\_DIVIDERS1

# Figure 32. Address 0x15, CLOCK\_DIVIDERS1

| 15 | 14     | 13     | 12      | 11     | 10   | 9      | 8       |

|----|--------|--------|---------|--------|------|--------|---------|

|    | FIN_DI | /IDER1 |         | RESE   | RVED | FREF_D | IVIDER1 |

| 7  | 6      | 5      | 4       | 3      | 2    | 1      | 0       |

|    |        |        | FREF_DI | VIDER1 |      |        |         |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 18. Address 0x15, CLOCK\_DIVIDERS1 Field Descriptions

| Bit   | Field         | Туре | Reset | Description                                                                                                                                                                                                                            |

|-------|---------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | FIN_DIVIDER1  | R/W  | 0000  | Channel 1 Input Divider Sets the divider for Channel 1 input. Used when the Sensor frequency is greater than the maximum $F_{IN}$ . b0000: Reserved. Do not use.  FIN_DIVIDER1 $\geq$ b0001: $f_{In1} = f_{SENSOR1} \div FIN_DIVIDER1$ |

| 11:10 | RESERVED      | R/W  | 00    | Reserved. Set to b00.                                                                                                                                                                                                                  |

| 9:0   | FREF_DIVIDER1 | R/W  | 0x000 | Channel 1 Reference Divider Sets the divider for Channel 1 reference. Use this to scale the maximum conversion frequency. $0x000$ : Reserved. Do not use. $FREF\_DIVIDER1 \ge 0x001$ : $f_{REF1} = f_{CLK} \div FREF\_DIVIDER1$        |

## 7.6.20 Address 0x16, CLOCK\_DIVIDERS2 (LDC1314 only)

## Figure 33. Address 0x16, CLOCK\_DIVIDERS2

| 15 | 14      | 13     | 12      | 11     | 10   | 9      | 8       |

|----|---------|--------|---------|--------|------|--------|---------|

|    | FIN_DI\ | /IDER2 |         | RESE   | RVED | FREF_D | IVIDER2 |

| 7  | 6       | 5      | 4       | 3      | 2    | 1      | 0       |

|    |         |        | FREF_DI | VIDER2 |      |        |         |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 19. Address 0x16, CLOCK\_DIVIDERS2 Field Descriptions

| Bit   | Field         | Туре | Reset | Description                                                                                                                                                                                                                                            |

|-------|---------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | FIN_DIVIDER2  | R/W  | 0000  | Channel 2 Input Divider Sets the divider for Channel 2 input. Must be set to $\geq 2$ if the Sensor frequency is $\geq 8.75$ MHz. b0000: Reserved. Do not use. FIN_DIVIDER2 $\geq$ b0001: $f_{\text{IN2}} = f_{\text{SENSOR2}}\div\text{FIN}_DIVIDER2$ |

| 11:10 | RESERVED      | R/W  | 00    | Reserved. Set to b00.                                                                                                                                                                                                                                  |

| 9:0   | FREF_DIVIDER2 | R/W  | 0x000 | Channel 2 Reference Divider Sets the divider for Channel 2 reference. Use this to scale the maximum conversion frequency.  0x000: Reserved. Do not use.  FREF_DIVIDER2 $\geq$ 0x001: $f_{REF2} = f_{CLK} \div FREF_DIVIDER2$                           |

## 7.6.21 Address 0x17, CLOCK\_DIVIDERS3 (LDC1314 only)

## Figure 34. Address 0x17, CLOCK\_DIVIDERS3

| 15 | 14           | 13 | 12      | 11     | 10   | 9             | 8 |

|----|--------------|----|---------|--------|------|---------------|---|

|    | FIN_DIVIDER3 |    |         |        | RVED | FREF_DIVIDER3 |   |

| 7  | 6            | 5  | 4       | 3      | 2    | 1             | 0 |

|    |              |    | FREF_DI | VIDER3 |      |               |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 20. Address 0x17, CLOCK\_DIVIDERS3

| Bit   | Field         | Туре | Reset | Description                                                                                                                                                                                                                         |

|-------|---------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | FIN_DIVIDER3  | R/W  | 0000  | Channel 3 Input Divider Sets the divider for Channel 3 input. Must be set to ≥2 if the Sensor frequency is ≥ 8.75MHz. b0000: Reserved. Do not use. FIN_DIVIDER3 ≥ b0001: $f_{IN3} = f_{SENSOR3}$ ÷FIN_DIVIDER3                      |