# DRV8000-Q1 Automotive Highly-Integrated, Multifunction Driver for Door Control

#### 1 Features

- AEC-Q100 qualified for automotive applications:

- Temperature grade 1: –40°C to +125°C, T<sub>△</sub>

- **Functional Safety-Compliant Targeted**

- Developed for functional safety applications

- Documentation to aid ISO26262 system design

- Systematic integrity up to ASIL D

- Hardware integrity up to ASIL B

- 5V to 35V (40V abs. max) operating range

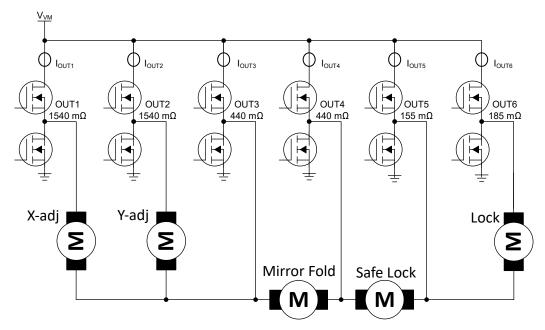

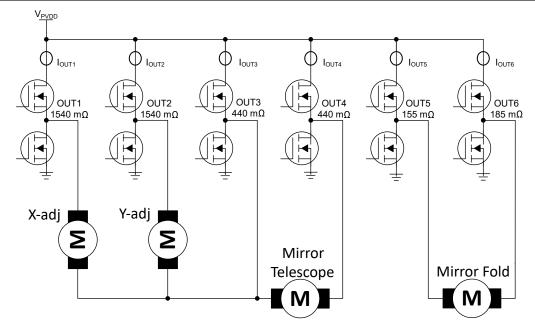

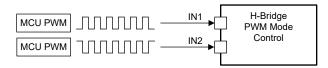

- H-bridge or dual-channel half-bridge gate drivers

- Smart gate drive architecture

- Tripler charge pump for 100% PWM

- Wide common mode current shunt amplifier

- 1 Integrated half-bridge with I<sub>OUT</sub> max 8A (R<sub>DSON</sub> HS +LS FET =  $155m\Omega$ )

- 1 Integrated half-bridge with I<sub>OUT</sub> max 7A (R<sub>DSON</sub> HS +LS FET =  $185m\Omega$ )

- 2 Integrated half-bridges with I<sub>OUT</sub> max 4A (R<sub>DSON</sub> HS +LS FET =  $440 \text{m}\Omega$ )

- 2 Integrated half-bridges with IOUT max 1.3A load  $(R_{DSON} HS + LS FET = 1540 m\Omega)$

- 1 Configurable integrated high-side driver as lamp or LED driver with  $I_{OUT}$  Max 1.5/0.5A ( $R_{DSON}$  =  $0.4/1.2\Omega$ )

- 5 Configurable integrated high-side drivers for 0.5/0.25A load (R<sub>DSON</sub> =  $1.2\Omega$ )

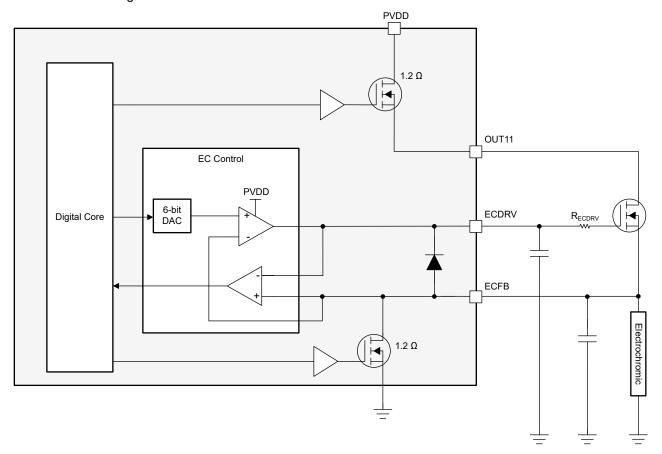

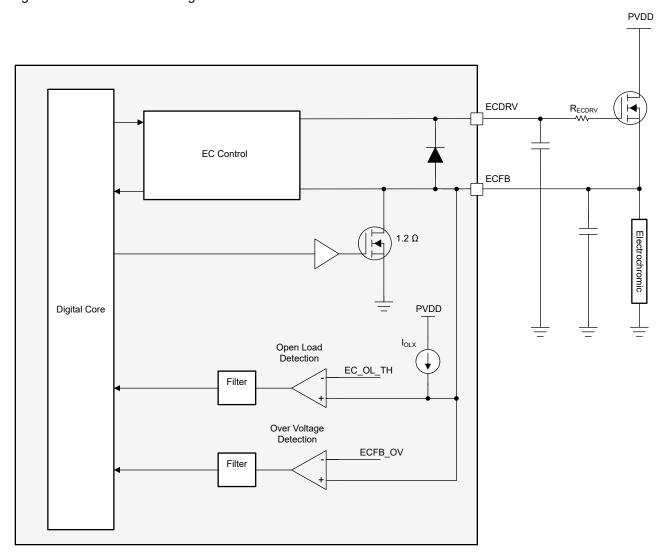

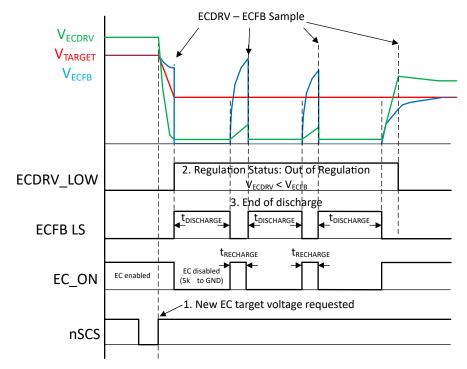

- 1 External MOSFET gate driver for charge of electrochromic glass

- 1 Integrated low-side FET for discharge of electrochromic glass

- Internal 10bit PWM generator for high-side drivers

- All high-side drivers support a low- or high- current threshold constant current mode to drive a wide range of LED modules

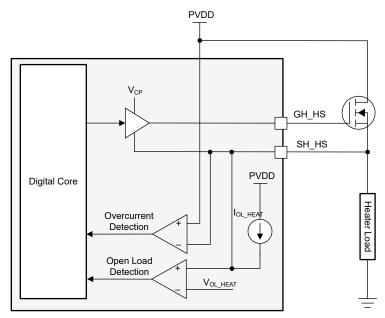

- 1 external MOSFET gate driver for heater

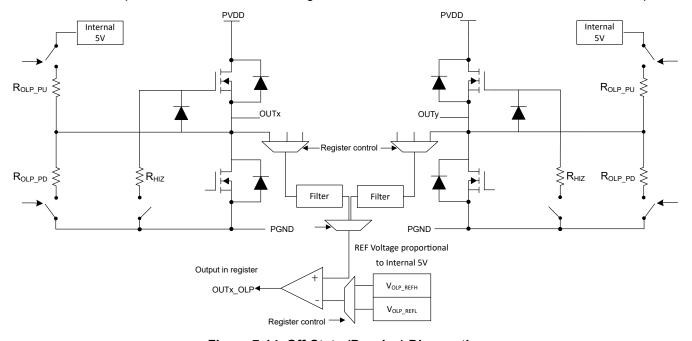

- Offline open load detection

- V<sub>DS</sub> monitoring of low R<sub>DSON</sub> MOSFET for short-circuit detection

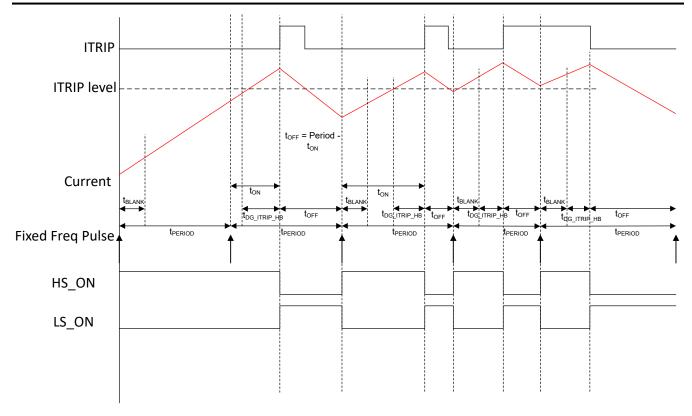

- Integrated driver output features current regulation (ITRIP)

- Muxable sense output (IPROPI)

- Internal current sensing with proportional current output (IPROPI)

- Advanced die temperature monitoring with multiple thermal clusters

- Motor supply voltage monitor

- Protection and diagnostic features with configurable fault behavior

- Load diagnostics in both the off-state and onstate to detect open load and short-circuit

- Overcurrent and over temperature protection

**Device Comparison Table**

# 2 Applications

- Door module

- Body control modules

- Zonal module

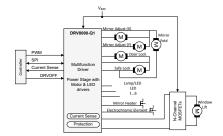

# 3 Description

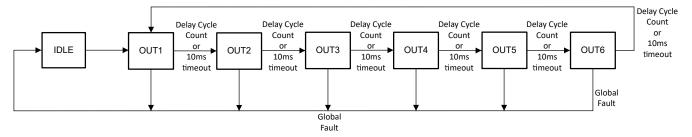

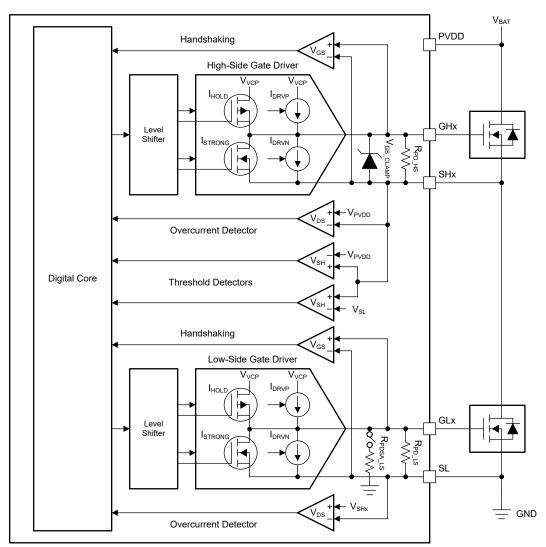

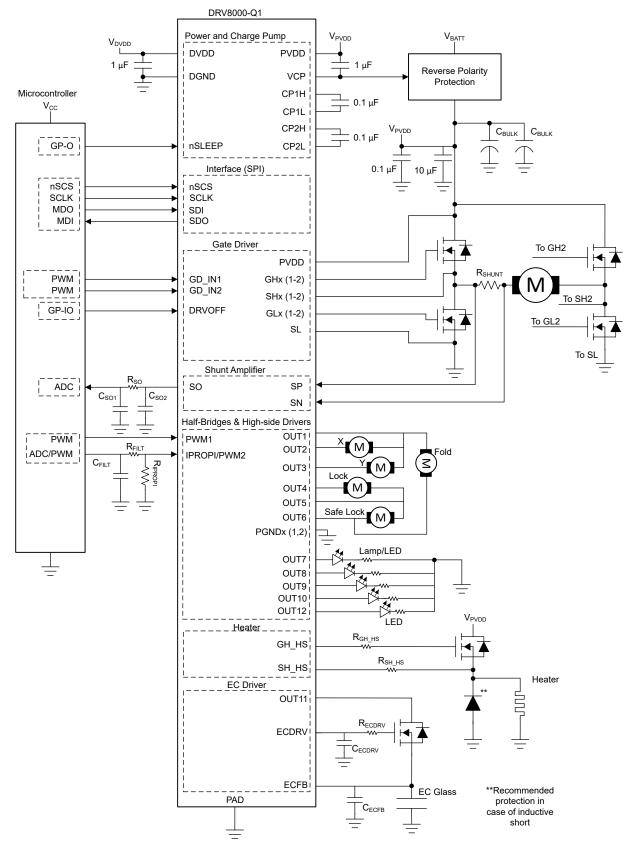

The DRV8000-Q1 device integrates multiple door control specific functions: driving and diagnosing motor (inductive), resistive and capacitive loads, driving a lamp or LEDs, drive MOSFETs for special loads such as heating element or electrochromic elements. These drivers include protection features for offline and active diagnostics such as under and over voltage monitors, offline open load and short-circuit diagnostics, and zone-based thermal monitoring and shutdown protection. The device features two half-bridge gate drivers, 6 integrated halfbridges (2 high-side alternate modes), 6 integrated high-side drivers, one external high-side gate driver for heater, one external high-side gate driver for electrochromic charge and one integrated low-side driver for electrochromic load discharge. The halfbridge, high-side, heater and gate drivers have PWM input control configuration, sensing, diagnostics and device system protection. There is a dedicated internal programmable PWM generators for each high-side driver. Proportional current sense pin output is available for all integrated drivers, along with a robust and flexible current shunt amplifier for the gate driver.

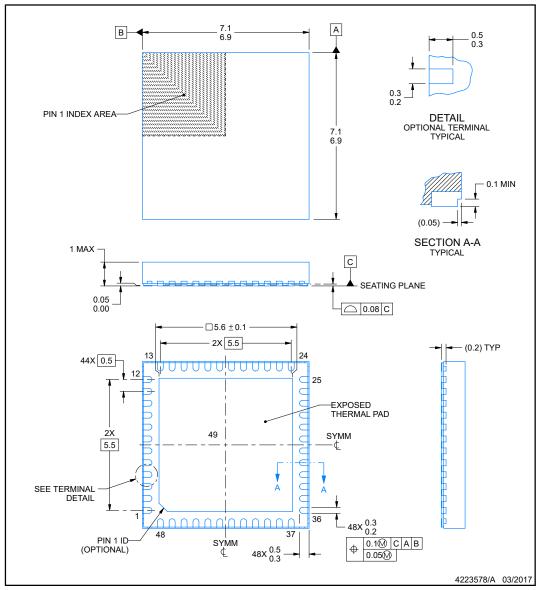

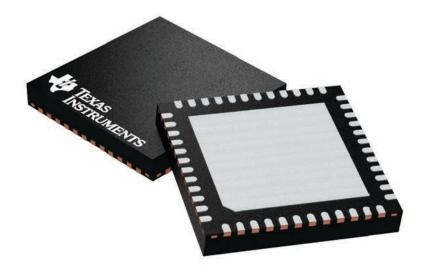

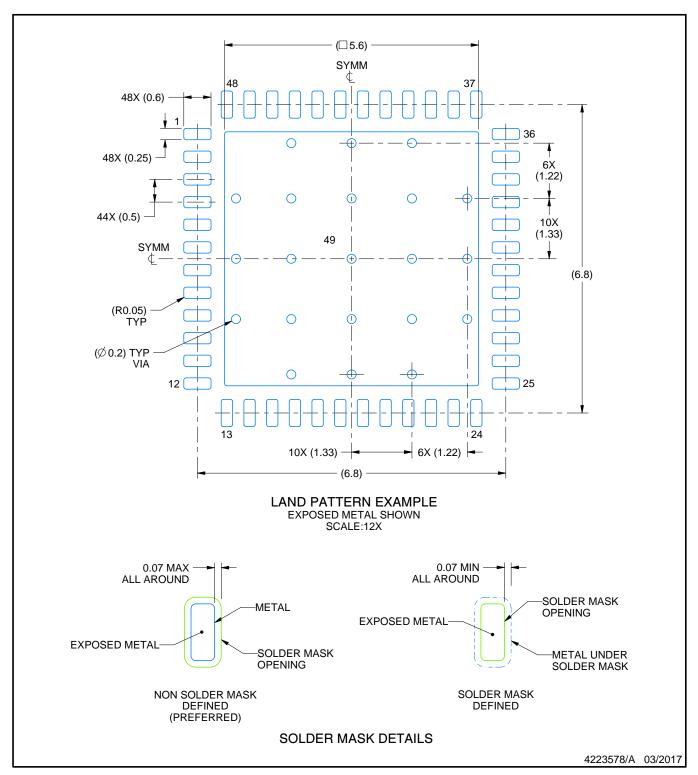

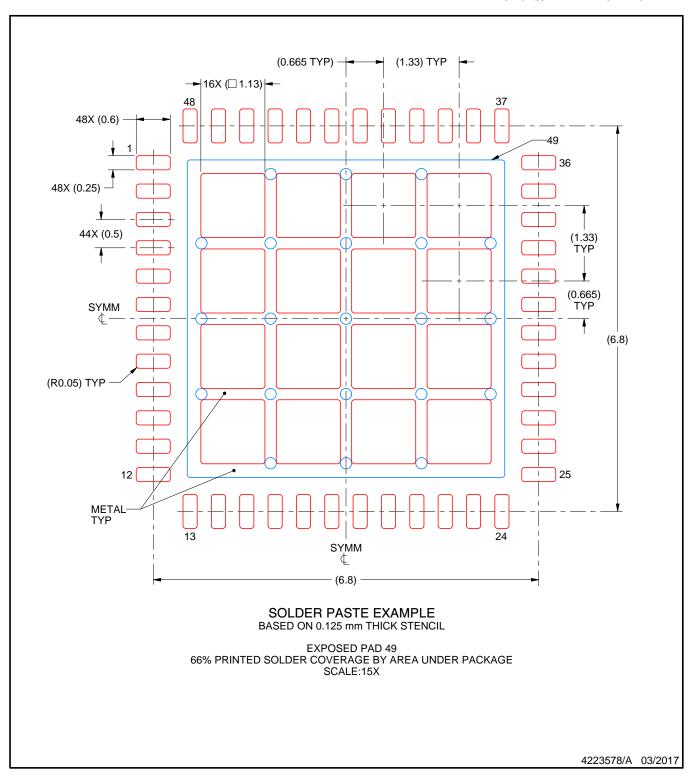

### **Package Information**

| PART NUMBER | DACKACL   | PACKAGE SIZE (NOM) <sup>(2)</sup> |  |

|-------------|-----------|-----------------------------------|--|

| DRV8000-Q1  | VQFN (48) | 7.00mm × 7.00mm                   |  |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

# **Table of Contents**

| 1 Features1                           | 8.2 DRV8000-Q1_CNFG Registers94                          |

|---------------------------------------|----------------------------------------------------------|

| 2 Applications1                       | 8.3 DRV8000-Q1_CTRL Registers130                         |

| 3 Description1                        | 9 Application and Implementation140                      |

| 4 Device Comparison3                  | 9.1 Application Information140                           |

| 5 Pin Configuration and Functions4    | 9.2 Typical Application140                               |

| 6 Specifications7                     | 9.3 Initialization Setup144                              |

| 6.1 Absolute Maximum Ratings7         | 9.4 Power Supply Recommendations144                      |

| 6.2 ESD Ratings Auto8                 | 9.5 Layout144                                            |

| 6.3 Recommended Operating Conditions8 | 10 Device and Documentation Support147                   |

| 6.4 Thermal Information RGZ package8  | 10.1 Receiving Notification of Documentation Updates 147 |

| 6.5 Electrical Characteristics9       | 10.2 Support Resources147                                |

| 6.6 Timing Requirements24             | 10.3 Trademarks147                                       |

| 7 Detailed Description25              | 10.4 Electrostatic Discharge Caution147                  |

| 7.1 Overview                          | 10.5 Glossary147                                         |

| 7.2 Functional Block Diagram26        | 11 Pre-Production Revision History 147                   |

| 7.3 External Components27             | 12 Mechanical, Packaging, and Orderable                  |

| 7.4 Feature Description27             | Information147                                           |

| 7.5 Programming                       | 12.1 Package Option Addendum152                          |

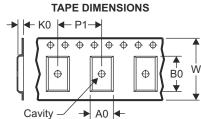

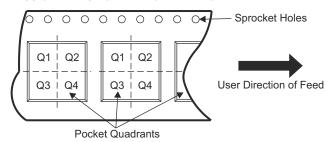

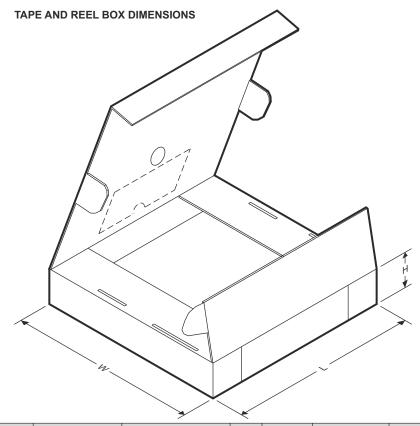

| 8 DRV8000-Q1 Register Map 81          | 12.2 Tape and Reel Information153                        |

| 8.1 DRV8000-Q1_STATUS Registers84     |                                                          |

# **4 Device Comparison**

## **Table 4-1. Device Comparison**

|             |                         |                       |                     | 0 0 . 0               |                   |                          |                      |                                 |

|-------------|-------------------------|-----------------------|---------------------|-----------------------|-------------------|--------------------------|----------------------|---------------------------------|

| Device Name | H-Bridge<br>Gate Driver | Half-bridge<br>Driver | High-side<br>Driver | Lamp/LED<br>HS Driver | EC Gate<br>Driver | Heater HS<br>Gate Driver | Current<br>Shunt Amp | Package                         |

| DRV8000-Q1  | 1x                      | 6x                    | 5x                  | 1x                    | 1x                | 1x                       | 1x                   | 7x7 QFN-48<br>Wettable<br>Flank |

| DRV8001-Q1  | Х                       | 6x                    | 5x                  | 1x                    | 1x                | 1x                       | Х                    | 6x6 QFN-40<br>Wettable<br>Flank |

| DRV8002-Q1  | 1x                      | 6x                    | 5x                  | 1x                    | Х                 | Х                        | 1x                   | 7x7 QFN-48<br>Wettable<br>Flank |

### **Table 4-2. Device Orderable Information**

| Device     | Pre-production Part Number | Orderable Part Number | EVM             |  |  |  |  |

|------------|----------------------------|-----------------------|-----------------|--|--|--|--|

| DRV8000-Q1 | PDRV8000QWRGZRQ1           | DRV8000QWRGZRQ1       | DRV8000-Q1EVM   |  |  |  |  |

| DRV0000-Q1 | P2DRV8000QWRGZRQ1          | DRV0000QWRGZRQ1       | DRV8000-Q TEVIW |  |  |  |  |

| DRV8001-Q1 | PDRV8001QWRHARQ1           | DRV8001QWRHARQ1       | DRV8001-Q1EVM   |  |  |  |  |

| DRV8002-Q1 | PDRV8002QRGZRQ1            | DRV8002QWRGZRQ1       | DRV8000-Q1EVM   |  |  |  |  |

|            | P2DRV8002QWRGZRQ1          | DIVOUUZQWNGZKQT       | DIVOUU-Q IEVIVI |  |  |  |  |

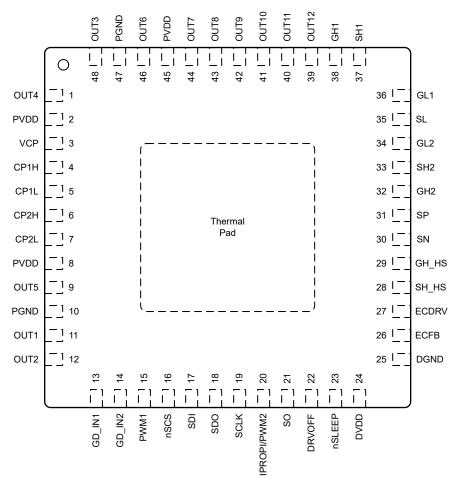

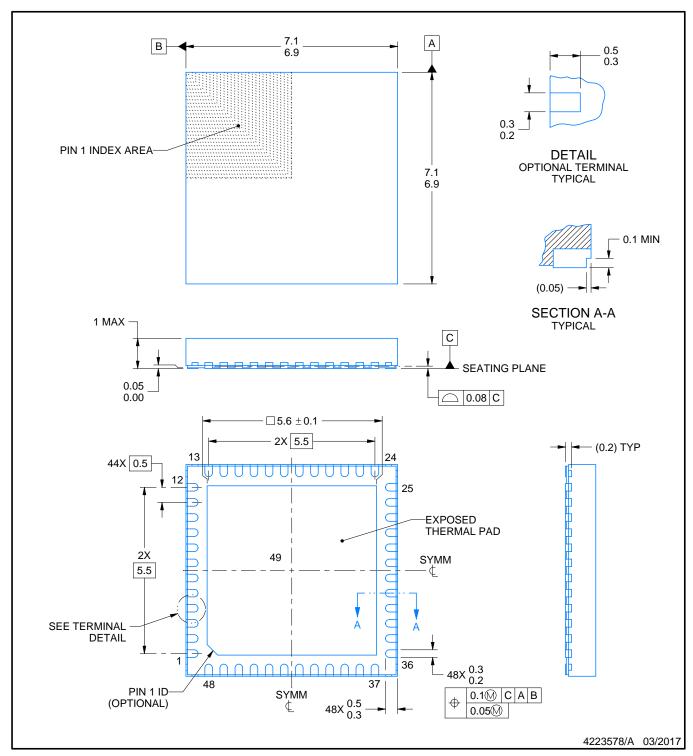

# **5 Pin Configuration and Functions**

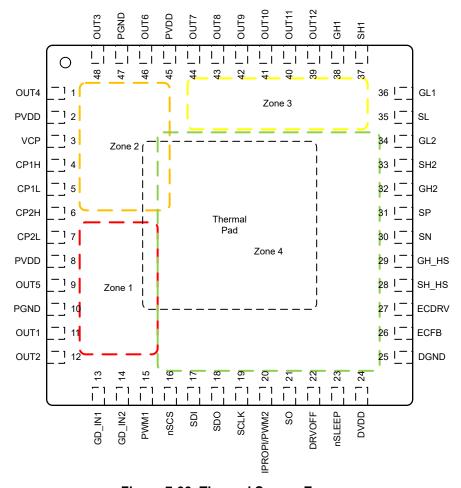

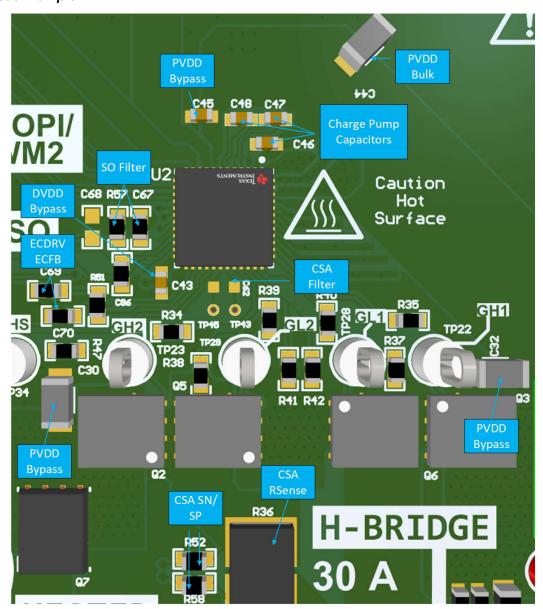

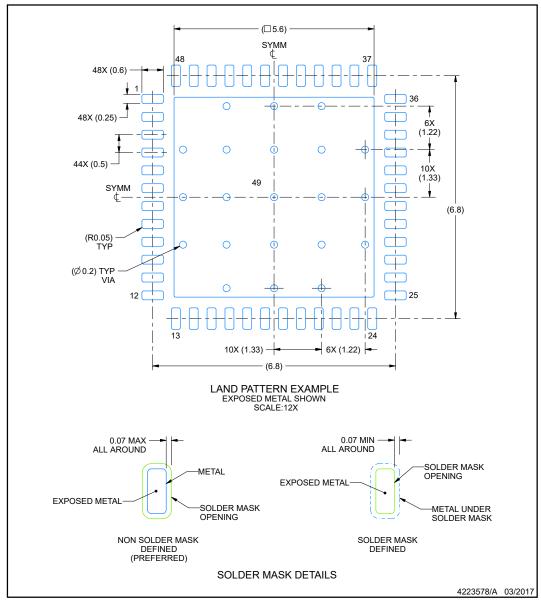

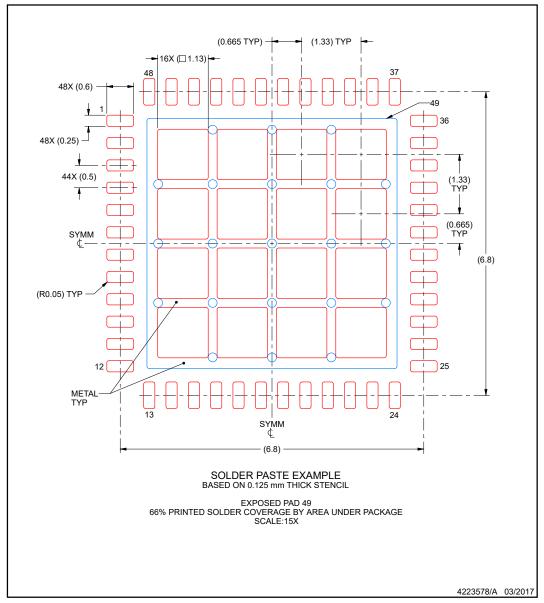

Figure 5-1. VQFN (RGZ) 48-Pin Package and Pin Functions

**Table 5-1. Pin Functions**

|     | PIN  | I/O <sup>(1)</sup> | TYPE   | DESCRIPTION                                                                                                                                                                                             |  |  |  |

|-----|------|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME |                    | ITPE   | DESCRIPTION                                                                                                                                                                                             |  |  |  |

| 1   | OUT4 | 0                  | Power  | 440mΩ half-bridge output 4.                                                                                                                                                                             |  |  |  |

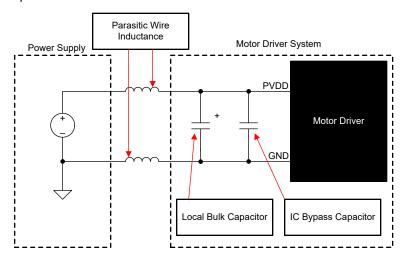

| 2   | PVDD | I                  | Power  | Device driver power supply input. Connect to the bridge power supply. Connect a 0.1µF, PVDD-rated ceramic capacitor and local bulk capacitance greater than or equal to 10µF between PVDD and GND pins. |  |  |  |

| 3   | VCP  | I/O                | Power  | Charge pump output. Connect a 1μF, 16V ceramic capacitor between VCP a PVDD pins.                                                                                                                       |  |  |  |

| 4   | CP1H | I/O                | Power  | Charge pump switching node. Connect a 100nF, PVDD-rated ceramic                                                                                                                                         |  |  |  |

| 5   | CP1L | I/O                | Power  | capacitor between the CP1H and CP1L pins.                                                                                                                                                               |  |  |  |

| 6   | CP2H | I/O                | Power  | Charge pump switching node. Connect a 100nF, PVDD-rated ceramic                                                                                                                                         |  |  |  |

| 7   | CP2L | I/O                | Power  | capacitor between the CP2H and CP2L pins.                                                                                                                                                               |  |  |  |

| 8   | PVDD | I                  | Power  | Device driver power supply input. Connect to the bridge power supply. Connect a 0.1µF, PVDD-rated ceramic capacitor and local bulk capacitance greater than or equal to 10µF between PVDD and GND pins. |  |  |  |

| 9   | OUT5 | 0                  | Power  | 155mΩ half-bridge output 5.                                                                                                                                                                             |  |  |  |

| 10  | PGND | I/O                | Ground | Device ground. Connect to system ground.                                                                                                                                                                |  |  |  |

| 11  | OUT1 | 0                  | Power  | 1.54Ω half-bridge output 1.                                                                                                                                                                             |  |  |  |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# Table 5-1. Pin Functions (continued)

|     | Table 5-1. Pin Functions (continued) |                    |         |                                                                                                                                                                                                               |  |

|-----|--------------------------------------|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | PIN                                  | I/O <sup>(1)</sup> | TYPE    | DESCRIPTION                                                                                                                                                                                                   |  |

| NO. | NAME                                 |                    | ITPE    | DESCRIPTION                                                                                                                                                                                                   |  |

| 12  | OUT2                                 | 0                  | Power   | 1.54Ω half-bridge output 2.                                                                                                                                                                                   |  |

| 13  | GD_IN1                               | I                  | Digital | Gate Driver Half-bridge and H-bridge control input 1.                                                                                                                                                         |  |

| 14  | GD_IN2                               | ı                  | Digital | Gate Driver Half-bridge and H-bridge control input 2.                                                                                                                                                         |  |

| 15  | PWM1                                 | I                  | Digital | PWM input 1 for regulation of all drivers except electrochrome and Gate Drivers.                                                                                                                              |  |

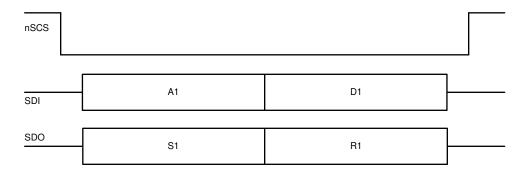

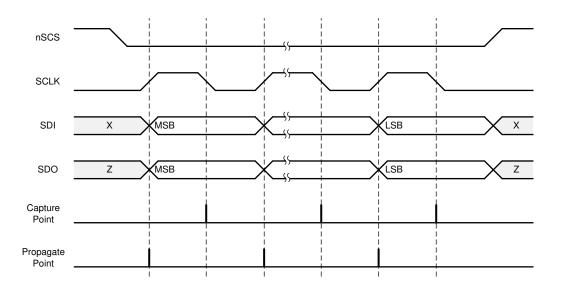

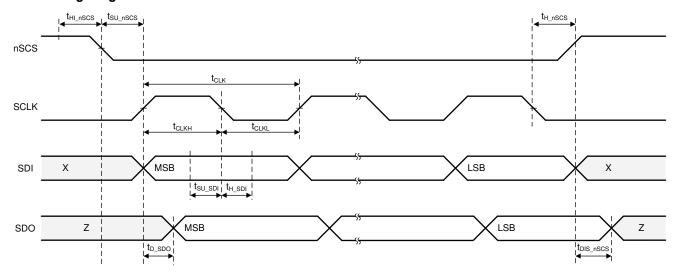

| 16  | nSCS                                 | I                  | Digital | Serial chip select. A logic low on this pin enables serial interface communication. Internal pullup resistor.                                                                                                 |  |

| 17  | SDI                                  | I                  | Digital | Serial data input. Data is captured on the falling edge of the SCLK pin. Internal pulldown resistor.                                                                                                          |  |

| 18  | SDO                                  | 0                  | Digital | Serial data output. Data is shifted out on the rising edge of the SCLK pin. Push-pull output.                                                                                                                 |  |

| 19  | SCLK                                 | I                  | Digital | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. Internal pulldown resistor.                                                             |  |

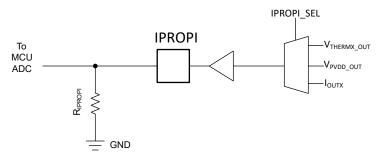

| 20  | IPROPI/PWM2                          | I/O                | Analog  | Sense output is multiplexed from any of driver load current feedback, PVDD voltage feedback, or thermal cluster temperature feedback. Can also be configured as second PWM pin input for half-bridge drivers. |  |

| 21  | so                                   | 0                  | Analog  | Shunt amplifier output.                                                                                                                                                                                       |  |

| 22  | DRVOFF                               | I                  | Analog  | Gate driver shutdown pin. Logic high to pulldown both high-side and low-side gate driver outputs. Internal pulldown resistor.                                                                                 |  |

| 23  | nSLEEP                               | I                  | Analog  | Device enable pin. Logic low to shutdown the device and enter sleep mode. Internal pulldown resistor.                                                                                                         |  |

| 24  | DVDD                                 | I                  | Power   | Device logic and digital output power supply input. Recommended to connect a 1.0µF, 6.3V ceramic capacitor between the DVDD and GND pins.                                                                     |  |

| 25  | DGND                                 | I/O                | Ground  | Device ground. Connect to system ground.                                                                                                                                                                      |  |

| 26  | ECFB                                 | I/O                | Power   | For EC control, pin is used as voltage monitor input and fast discharge low-side switch. If the EC drive function is not used, connect this pin to GND through $10k\Omega$ resistor.                          |  |

| 27  | ECDRV                                | 0                  | Analog  | For EC control, pin controls the gate of external MOSFET for EC voltage regulation                                                                                                                            |  |

| 28  | SH_HS                                | I                  | Analog  | Source pin of high-side heater MOSFET and output to heater load. Connect to source of high-side MOSFET.                                                                                                       |  |

| 29  | GH_HS                                | 0                  | Analog  | Gate driver output for heater MOSFET. Connect to gate of high-side MOSFET.                                                                                                                                    |  |

| 30  | SN                                   | I                  | Analog  | Amplifier negative input. Connect to negative terminal of the shunt resistor. Additional filtering is not recommended to the input of the Shunt Amplifier.                                                    |  |

| 31  | SP                                   | I                  | Analog  | Amplifier positive input. Connect to positive terminal of the shunt resistor. Additional filtering is not recommended to the input of the Shunt Amplifier.                                                    |  |

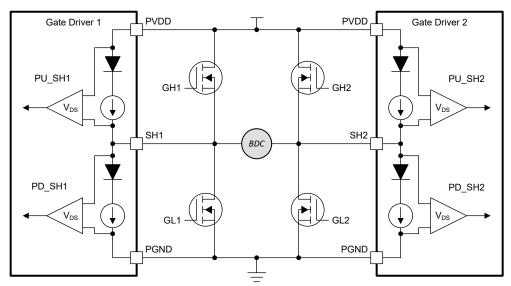

| 32  | GH2                                  | 0                  | Analog  | High-side gate driver output. Connect to the gate of the high-side MOSFET. Gate drive series resistance is not recommended as the impact crossover transition timing.                                         |  |

| 33  | SH2                                  | I                  | Analog  | High-side source sense input. Connect to the high-side MOSFET source.                                                                                                                                         |  |

| 34  | GL2                                  | 0                  | Analog  | Low-side gate driver output. Connect to the gate of the low-side MOSFET.                                                                                                                                      |  |

| 35  | SL                                   | I                  | Analog  | Low-side MOSFET gate drive sense and power return. Connect to system ground with low impedance path to the low-side MOSFET ground return.                                                                     |  |

| 36  | GL1                                  | 0                  | Analog  | Low-side gate driver output. Connect to the gate of the low-side MOSFET.                                                                                                                                      |  |

| 37  | SH1                                  | I                  | Analog  | High-side source sense input. Connect to the high-side MOSFET source.                                                                                                                                         |  |

| 38  | GH1                                  | 0                  | Power   | High-side gate driver output. Connect to the gate of the high-side MOSFET. Gate drive series resistance is not recommended as the impact crossover transition timing.                                         |  |

| 39  | OUT12                                | 0                  | Power   | 1.2Ω high-side driver output 12. Connect to low-side load.                                                                                                                                                    |  |

|     |                                      |                    |         |                                                                                                                                                                                                               |  |

# **Table 5-1. Pin Functions (continued)**

|     | PIN   | I/O <sup>(1)</sup> | TYPE   | DESCRIPTION                                                                                                                                                                                             |

|-----|-------|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME  |                    | ITPE   | DESCRIPTION                                                                                                                                                                                             |

| 40  | OUT11 | 0                  | Power  | 1.2 $\Omega$ high-side driver output 11. Configurable as SC protection switch for EC drive. Connect to low-side load.                                                                                   |

| 41  | OUT10 | 0                  | Power  | 1.2Ω high-side driver output 10. Connect to low-side load.                                                                                                                                              |

| 42  | OUT9  | 0                  | Power  | 1.2Ω high-side driver output 9. Connect to low-side load.                                                                                                                                               |

| 43  | OUT8  | 0                  | Power  | 1.2Ω high-side driver output 8. Connect to low-side load.                                                                                                                                               |

| 44  | OUT7  | 0                  | Power  | High-side driver output with configurable $R_{DSON}$ (400m $\Omega$ /1200m $\Omega$ ). Connect to low-side load.                                                                                        |

| 45  | PVDD  | I                  | Power  | Device driver power supply input. Connect to the bridge power supply. Connect a 0.1µF, PVDD-rated ceramic capacitor and local bulk capacitance greater than or equal to 10µF between PVDD and GND pins. |

| 46  | OUT6  | 0                  | Power  | 185mΩ half-bridge output 6.                                                                                                                                                                             |

| 47  | PGND  | I/O                | Ground | Device ground. Connect to system ground.                                                                                                                                                                |

| 48  | OUT3  | 0                  | Power  | 440mΩ half-bridge output 3.                                                                                                                                                                             |

(1) I = Input, O = Output

# **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating temperature range (unless otherwise noted) (1)

|                                                                                                                  |                                                               | MIN                                                    | MAX                     | UNIT |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|-------------------------|------|

| Power supply pin voltage                                                                                         | PVDD                                                          | -0.3                                                   | 40                      | V    |

| Power supply transient voltage ramp                                                                              | PVDD                                                          |                                                        | 2                       | V/µs |

| Digital Logic power supply voltage ramp                                                                          | DVDD                                                          |                                                        | 2                       | V/µs |

| Voltage difference between ground pins                                                                           | GND, PGND                                                     | -0.3                                                   | 0.3                     | V    |

| Charge pump pin voltage                                                                                          | VCP                                                           | -0.3                                                   | PVDD + 15               | V    |

| Charge pump high-side pin voltage                                                                                | CP1H                                                          | V <sub>PVDD</sub> - 0.3                                | V <sub>VCP</sub> + 0.3  | V    |

| Charge pump high-side pin voltage                                                                                | СР2Н                                                          | V <sub>PVDD</sub> – 0.6                                | V <sub>VCP</sub> + 0.3  | V    |

| Charge pump low-side pin voltage                                                                                 | CP1L, CP2L                                                    | -0.3                                                   | V <sub>PVDD</sub> + 0.3 | V    |

| Digital regulator pin voltage                                                                                    | DVDD                                                          | -0.3                                                   | 5.75                    | V    |

| Logic pin voltage                                                                                                | GD_INx, PWM1, IPROPI/PWM2,<br>DRVOFF, nSLEEP, SCLK, SDI, nSCS | -0.3                                                   | 5.75                    | V    |

| Output logic pin voltage                                                                                         | SDO                                                           | -0.3                                                   | V <sub>DVDD</sub> + 0.3 | V    |

| Output pin voltage                                                                                               | OUT1-OUT12                                                    | -0.3                                                   | V <sub>PVDD</sub> + 0.9 | V    |

| Output current                                                                                                   | OUT1-OUT12, ECFB, ECDRV                                       | Internally<br>Limited                                  | Internally<br>Limited   | Α    |

| Heater and Electrochromic MOSFET gate drive pin voltage                                                          | GH_HS                                                         | V <sub>SH_HS</sub> - 0.3<br>to V <sub>SH_HS</sub> + 13 | V <sub>VCP</sub> + 0.3  | V    |

| Heater and Electrochromic MOSFET source pin voltage                                                              | SH_HS, ECFB, ECDRV                                            | -0.3                                                   | V <sub>PVDD</sub> + 0.3 | V    |

| High-side driver and Heater MOSFET source pin maximum energy dissipation, $T_J$ = 25°C, $L_{LOAD}$ < 100 $\mu$ H | OUT7-OUT12, SH_HS                                             | -                                                      | 1                       | mJ   |

| High-side gate drive pin voltage                                                                                 | GHx <sup>(2)</sup>                                            | -2                                                     | V <sub>VCP</sub> + 0.3  | V    |

| Transient 1-µs high-side gate drive pin voltage                                                                  | GHx <sup>(2)</sup>                                            | -5                                                     | V <sub>VCP</sub> + 0.3  | V    |

| High-side gate drive pin voltage with respect to SHx                                                             | GHx <sup>(2)</sup>                                            | -0.3                                                   | 13.5                    | V    |

| High-side sense pin voltage                                                                                      | SHx <sup>(2)</sup>                                            | -2                                                     | 40                      | V    |

| Transient 1-µs high-side sense pin voltage                                                                       | SHx <sup>(2)</sup>                                            | -5                                                     | 40                      | V    |

| Low-side gate drive pin voltage                                                                                  | GLx <sup>(2)</sup>                                            | -2                                                     | 13.5                    | V    |

| Transient 1-µs low-side gate drive pin voltage                                                                   | GLx <sup>(2)</sup>                                            | -3                                                     | 13.5                    | V    |

| Low-side gate drive pin voltage with respect to SL                                                               | GLx <sup>(2)</sup>                                            | -0.3                                                   | 13.5                    | V    |

| Low-side sense pin voltage                                                                                       | SL <sup>(2)</sup>                                             | -2                                                     | 2                       | V    |

| Transient 1-µs low-side sense pin voltage                                                                        | SL <sup>(2)</sup>                                             | -3                                                     | 3                       | V    |

| Gate drive current                                                                                               | GHx, GLx                                                      | Internally<br>Limited                                  | Internally<br>Limited   | Α    |

| Amplifier input pin voltage                                                                                      | SN, SP                                                        | -2                                                     | V <sub>VCP</sub> + 0.3  | V    |

| Transient 1-µs amplifier input pin voltage                                                                       | SN, SP                                                        | -5                                                     | V <sub>VCP</sub> + 0.3  | V    |

| Amplifier input differential voltage                                                                             | SN, SP                                                        | -5.75                                                  | 5.75                    | V    |

| Amplifier output pin voltage                                                                                     | so                                                            | -0.3                                                   | V <sub>DVDD</sub> + 0.3 | V    |

| Ambient temperature, T <sub>A</sub>                                                                              |                                                               | -40                                                    | 125                     | °C   |

| Junction temperature, T <sub>J</sub>                                                                             |                                                               | -40                                                    | 150                     | °C   |

| Storage temperature, T <sub>stg</sub>                                                                            |                                                               | -65                                                    | 150                     | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) PVDD with respect to GHx, SHx, GLx, or SL should not exceed 40 V. When PVDD is greater than 35 V, negative voltage on GHx, SHx GLx, and SL should be limited to ensure this rating is not exceeded. When PVDD is less than 35 V, the full negative rating of GHx, SHx, GLx, and SL is available.

## **6.2 ESD Ratings Auto**

|                    |                                            |                                                                                        |                               | VALUE | UNIT |

|--------------------|--------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------|-------|------|

|                    |                                            | Human body model (HBM), per AEC Q100-002 HBM ESD <sup>(1)</sup> Classification Level 2 | PVDD, OUT1 - OUT12, ECFB, GND | ±4000 | V    |

| V <sub>(ESD)</sub> | V <sub>(ESD)</sub> Electrostatic discharge | TIBIN ESD. Glassification Level 2                                                      | All other pins                | ±2000 |      |

|                    |                                            | Charged device model (CDM), per AEC Q100-011                                           | Corner pins                   | ±750  | V    |

|                    |                                            | CDM ESD Classification Level C4B                                                       | Other pins                    | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### **6.3 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                                |                                                   |                                                  | MIN | NOM MAX                    | UNIT |

|--------------------------------|---------------------------------------------------|--------------------------------------------------|-----|----------------------------|------|

| V <sub>PVDD</sub>              | Power supply voltage                              | PVDD                                             | 5   | 35                         | V    |

| I <sub>HS</sub> <sup>(1)</sup> | High-side average gate-drive current              | GHx                                              | 0   | 15                         | mA   |

| I <sub>LS</sub> (1)            | Low-side average gate-drive current               | GLx                                              | 0   | 15                         | mA   |

| $V_{DVDD}$                     | Logic input voltage                               | DVDD                                             | 3.1 | 5.5                        | V    |

| V <sub>DIN</sub>               | Digital input voltage                             | GD_INx, PWM1, IPROPI/PWM2, DRVOFF, SO, SCLK, SDI | 0   | 5.5                        | V    |

| I <sub>DOUT</sub>              | Digital output current                            | SDO                                              | 0   | 5                          | mA   |

| f <sub>PWM</sub>               | Input PWM frequency                               | PWM1, IPROPI/PWM2                                | 0   | 25                         | kHz  |

| V <sub>IPROPI</sub>            | Analog output voltage for V <sub>PVDD</sub> > 7 V | IPROPI (IPROPI/PWM2 pin)                         | 0   | 5.2                        | V    |

| V <sub>IPROPI</sub>            | Analog output voltage for V <sub>PVDD</sub> < 7 V | IPROPI (IPROPI/PWM2 pin)                         | 0   | V <sub>PVDD</sub> -<br>1.8 | V    |

| I <sub>SO</sub>                | Shunt amplifier output current                    | so                                               | 0   | 5                          | mA   |

| T <sub>A</sub>                 | Operating ambient temperature                     | •                                                | -40 | 125                        | °C   |

| TJ                             | Operating junction temperature                    |                                                  | -40 | 150                        | °C   |

<sup>(1)</sup> Power dissipation and thermal limits must be observed.

# 6.4 Thermal Information RGZ package

|                       | THERMAL METRIC <sup>(1)</sup>                | RGZ Package | UNIT |

|-----------------------|----------------------------------------------|-------------|------|

|                       |                                              |             |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 23.3        | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 11.7        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.0         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 7.0         | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.3         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: DRV8000-Q1

## **6.5 Electrical Characteristics**

$5 \text{ V} \le \text{V}_{\text{PVDD}} \le 35 \text{ V}, 3.1 \text{ V} \le \text{V}_{\text{DVDD}} \le 5.5 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$  (unless otherwise noted). Typical limits apply for  $\text{V}_{\text{PVDD}} = 13.5 \text{ V}, \text{V}_{\text{DVDD}} = 5 \text{ V}$  and  $\text{T}_{\text{J}} = 25^{\circ}\text{C}$ .

|                              | PARAMETER                                                               | TEST CONDITIONS                                                                                                  | MIN                        | TYP                         | MAX                        | UNIT |

|------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|----------------------------|------|

| POWER SUF                    | PPLIES (DVDD, VCP, PVDD)                                                |                                                                                                                  |                            |                             | 1                          |      |

| I <sub>PVDDQ</sub>           | PVDD sleep mode current                                                 | V <sub>PVDD</sub> = 13.5 V, nSLEEP = 0 V -40 ≤ T <sub>J</sub> ≤ 85°C                                             |                            | 3.5                         | 5.5                        | μA   |

| I <sub>DVDDQ</sub>           | DVDD sleep mode current                                                 | V <sub>PVDD</sub> = 13.5 V, nSLEEP = 0 V -40 ≤ T <sub>J</sub> ≤ 85°C                                             |                            | 3                           | 4                          | μA   |

| I <sub>PVDD</sub>            | PVDD active mode current                                                | V <sub>PVDD</sub> = 13.5, nSLEEP = V <sub>DVDD</sub>                                                             |                            | 8.7                         | 14.5                       | mA   |

| I <sub>PVDD</sub>            | PVDD active mode current, reduced options.                              | V <sub>PVDD</sub> = 13.5, nSLEEP = V <sub>DVDD</sub> ; Charge pump in doubler mode.                              |                            | 7                           | 11.5                       | mA   |

| I <sub>DVDD</sub>            | DVDD active mode current                                                | SDO = 0 V                                                                                                        |                            | 5                           | 8.5                        | mA   |

| I <sub>DVDD</sub>            | DVDD active mode current, reduced options                               | SDO = 0 V; Charge pump in doubler mode.                                                                          |                            | 3.3                         | 7                          | mA   |

| I <sub>PVDD_CP_DIS</sub>     | PVDD charge pump disabled mode current                                  | V <sub>PVDD</sub> = 13.5 V, DIS_CP = 1, EN_GD = 0, HEAT_EN = 0, EC_ON = 0, OUTx_EN = 0                           |                            | 1.2                         | 4.5                        | mA   |

| I <sub>DVDD_CP_DIS</sub>     | DVDD charge pump disabled mode current                                  | V <sub>PVDD</sub> = 13.5 V, DIS_CP = 1, EN_GD = 0, HEAT_EN = 0, EC_ON = 0, OUTx_EN = 0                           |                            | 3.4                         | 8.5                        | mA   |

| t <sub>WAKE</sub>            | Turnon time                                                             | nSLEEP = V <sub>DVDD</sub> to active mode                                                                        |                            | 670                         | 850                        | μs   |

| t <sub>SLEEP</sub>           | Turnoff time                                                            | nSLEEP = 0 V to sleep mode                                                                                       |                            |                             | 1                          | ms   |

| t <sub>DRVOFF_FLT</sub><br>R | Filter time for DRVOFF signal asserted                                  | DRVOFF = 0 V to V <sub>DVDD</sub>                                                                                |                            | 15                          |                            | μs   |

| $f_{VDD}$                    | Digital oscillator switching frequency                                  | Primary frequency of spread spectrum                                                                             | 12.83                      | 14.25                       | 15.68                      | MHz  |

| f <sub>VDD</sub>             | Digital oscillator spread spectrum range                                | Center spread on primary frequency                                                                               | -7                         |                             | 7                          | %    |

| $V_{VCP}$                    | Charge pump regulator voltage with respect to PVDD                      | V <sub>PVDD</sub> ≥ 9 V, I <sub>VCP</sub> ≤ 20 mA                                                                | 9.5                        | 10.5                        | 12.5                       | V    |

| $V_{VCP}$                    | Charge pump regulator voltage with respect to PVDD                      | V <sub>PVDD</sub> = 7 V, I <sub>VCP</sub> ≤ 15 mA                                                                | 8.5                        | 9                           | 12                         | V    |

| $V_{VCP}$                    | Charge pump regulator voltage with respect to PVDD                      | V <sub>PVDD</sub> = 5 V, I <sub>VCP</sub> ≤ 12 mA                                                                | 6.8                        | 7.5                         | 11                         | V    |

| t <sub>CP_tran</sub>         | Charge pump transition time between doubler and tripler mode            |                                                                                                                  |                            |                             | 300                        | μs   |

| t <sub>CP_EN</sub>           | Charge pump turn on time after enable command. Includes initialization. |                                                                                                                  |                            | 500                         | 550                        | μs   |

| I <sub>VCP_LIM</sub>         | Charge pump output current limit                                        | $V_{PVDD}$ = 13.5 V, $C_{FLY1}$ = $C_{FLY2}$ = 100 nF, $C_{VCP}$ = 1 $\mu$ F, inrush during charge pump start-up |                            |                             | 500                        | mA   |

| f <sub>VCP</sub>             | Charge pump switching frequency                                         | Primary frequency of spread spectrum                                                                             |                            | 400                         |                            | kHz  |

| LOGIC-LEVE                   | EL INPUTS (INx, nSLEEP, SCLK, SDI, etc                                  | c)                                                                                                               |                            |                             |                            |      |

| V <sub>IL</sub>              | Input logic low voltage                                                 | DRVOFF, GD_INx, PWM1, IPROPI/<br>PWM2, nSLEEP, SCLK, SDI                                                         | 0.3                        |                             | V <sub>DVDD</sub> x<br>0.3 | V    |

| V <sub>IH</sub>              | Input logic high voltage                                                | DRVOFF, GD_INx, PWM1, IPROPI/<br>PWM2, nSLEEP, SCLK, SDI                                                         | V <sub>DVDD</sub> x<br>0.7 |                             | 5.5                        | V    |

| V <sub>HYS</sub>             | Input hysteresis                                                        | DRVOFF, GD_INx, PWM1, IPROPI/<br>PWM2, nSLEEP, SCLK, SDI                                                         |                            | V <sub>DVDD</sub> x<br>0.15 |                            | V    |

| I <sub>IL</sub>              | Input logic low current                                                 | V <sub>DIN</sub> = 0 V, DRVOFF, GD_INx, PWM1, IPROPI/PWM2, nSLEEP, SCLK, SDI                                     | -5                         |                             | 5                          | μΑ   |

| I <sub>IL</sub>              | Input logic low current                                                 | V <sub>DIN</sub> = 0 V, nSCS                                                                                     |                            | 25                          | 50                         | μA   |

| I <sub>IH</sub>              | Input logic high current                                                | V <sub>DIN</sub> = V <sub>DVDD</sub> , nSCS                                                                      | -5                         |                             | 5                          | μA   |

$5 \text{ V} \le \text{V}_{\text{PVDD}} \le 35 \text{ V}, 3.1 \text{ V} \le \text{V}_{\text{DVDD}} \le 5.5 \text{ V}, -40 ^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150 ^{\circ}\text{C}$  (unless otherwise noted). Typical limits apply for  $\text{V}_{\text{PVDD}} = 13.5 \text{ V}, \text{V}_{\text{DVDD}} = 5 \text{ V}$  and  $\text{T}_{\text{J}} = 25 ^{\circ}\text{C}$ .

|                       | PARAMETER                     | TEST CONDITIONS                                                                                                                                                                                         | MIN           | TYP  | MAX  | UNIT |

|-----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------|------|

| I <sub>IH</sub>       | Input logic high current      | V <sub>DIN</sub> = V <sub>DVDD</sub> , DRVOFF, GD_INx,<br>PWM1, IPROPI/PWM2, nSLEEP, SCLK,<br>SDI                                                                                                       |               | 25   | 50   | μΑ   |

| R <sub>PD</sub>       | Input pulldown resistance     | To GND, DRVOFF, GD_INx, PWM1, IPROPI/PWM2, nSLEEP, SCLK, SDI                                                                                                                                            | 140           | 200  | 260  | kΩ   |

| R <sub>PU</sub>       | Input pullup resistance       | To DVDD, nSCS                                                                                                                                                                                           | 140           | 200  | 265  | kΩ   |

| PUSH-PU               | LL OUTPUT SDO                 |                                                                                                                                                                                                         |               |      |      |      |

| V <sub>OL</sub>       | Output logic low voltage      | I <sub>OD</sub> = 5 mA                                                                                                                                                                                  |               |      | 0.5  | V    |

| √ <sub>OH</sub>       | Output logic high voltage     | $I_{OD} = -5 \text{ mA, SDO}$                                                                                                                                                                           | DVDD x<br>0.8 |      |      | V    |

| GATE DR               | IVERS (GHx, GLx, SHx, SL)     |                                                                                                                                                                                                         |               |      |      |      |

| $V_{\mathrm{GHx\_L}}$ | GHx low level output voltage  | $I_{DRVN\_HS} = I_{STRONG}$ , $I_{GHx} = 1mA$ , GHx to SHx                                                                                                                                              | 0             |      | 0.25 | V    |

| / <sub>GLx_L</sub>    | GLx low level output voltage  | $I_{DRVN\_LS} = I_{STRONG}$ , $I_{GLx} = 1mA$ , GLx to SL                                                                                                                                               | 0             |      | 0.25 | V    |

| V <sub>GHx_H</sub>    | GHx high level output voltage | $I_{DRVP\_HS} = I_{HOLD}$ , $I_{GHx} = 1mA$ , VCP to $GHx$                                                                                                                                              | 0             |      | 0.25 | ٧    |

| √ <sub>GLx_H</sub>    | GLx high level output voltage | $\begin{split} &I_{DRVP\_LS} = I_{HOLD}, I_{GLx} = 1 mA \ , 10.5 \ V \leq \\ &V_{PVDD} \leq V_{PVDD\_OV}, \ GLx \ to \ SL. \ Gate \\ &driver \ turned \ off \ if \ V_{PVDD} > V_{PVDD\_OV} \end{split}$ | 9.35          | 10.5 | 12.5 | V    |

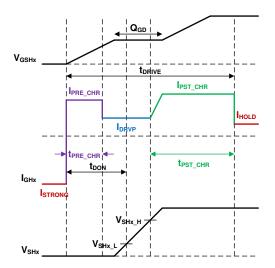

|                       |                               | IDRVP_x = 0000b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 0.2           | 0.5  | 0.83 | mA   |

|                       |                               | IDRVP_x = 0001b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 0.5           | 1    | 1.6  | mA   |

|                       |                               | IDRVP_x = 0010b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 1.3           | 2    | 2.8  | mA   |

|                       |                               | IDRVP_x = 0011b, $V_{GSx} = 3 \text{ V}$ , $V_{PVDD} \ge 7 \text{ V}$                                                                                                                                   | 2.1           | 3    | 4    | mA   |

|                       |                               | IDRVP_x = 0100b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 2.9           | 4    | 5.3  | mA   |

|                       |                               | IDRVP_x = 0101b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 3.7           | 5    | 6.45 | mA   |

|                       |                               | IDRVP_x = 0110b, $V_{GSx} = 3 \text{ V}, V_{PVDD} \ge 7 \text{ V}$                                                                                                                                      | 4.45          | 6    | 7.65 | mA   |

| ı                     | Dook gots surrent (source)    | IDRVP_x = 0111b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 5.5           | 7    | 9    | mA   |

| DRVP                  | Peak gate current (source)    | IDRVP_x = 1000b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 5.6           | 8    | 10.2 | mA   |

|                       |                               | IDRVP_x = 1001b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 8.8           | 12   | 15.2 | mA   |

|                       |                               | IDRVP_x = 1010b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 11.6          | 16   | 20.4 | mA   |

|                       |                               | IDRVP_x = 1011b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 16            | 20   | 25.4 | mA   |

|                       |                               | IDRVP_x = 1100b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 17.6          | 24   | 30.4 | mA   |

|                       |                               | IDRVP_x = 1101b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 24            | 31   | 40   | mA   |

|                       |                               | IDRVP_x = 1110b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V                                                                                                                                        | 28            | 48   | 62   | mA   |

|                       |                               | IDRVP_x = 1111b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7                                                                                                                                          | 46            | 62   | 78   | mA   |

www.ti.com

|                         | PARAMETER                                                        | TEST CONDITIONS                                                  | MIN  | TYP | MAX  | UNIT |

|-------------------------|------------------------------------------------------------------|------------------------------------------------------------------|------|-----|------|------|

|                         |                                                                  | IDRVN_x = 0000b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 0.07 | 0.5 | 0.85 | mA   |

|                         |                                                                  | IDRVN_x = 0001b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 0.23 | 1   | 1.7  | mA   |

|                         |                                                                  | IDRVN_x = 0010b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 0.7  | 2   | 3.2  | mA   |

|                         |                                                                  | IDRVN_x = 0011b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 1.2  | 3   | 4.6  | mA   |

|                         |                                                                  | IDRVN_x = 0100b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 1.75 | 4   | 5.9  | mA   |

|                         |                                                                  | IDRVN_x = 0101b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 2.4  | 5   | 7.2  | mA   |

|                         | IDRVN_x = 0110b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 3                                                                | 6    | 8.5 | mA   |      |

| l                       | Peak gate current (sink)                                         | IDRVN_x = 0111b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 3.6  | 7   | 9.8  | mA   |

| I <sub>DRVN</sub>       |                                                                  | IDRVN_x = 1000b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 4.3  | 8   | 11   | mA   |

|                         | IDRVN_x = 1001b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 7.3                                                              | 12   | 16  | mA   |      |

|                         |                                                                  | IDRVN_x = 1010b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 10.6 | 16  | 20.4 | mA   |

|                         |                                                                  | IDRVN_x = 1011b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7   | 14   | 20  | 25.3 | mA   |

|                         |                                                                  | IDRVN_x = 1100b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7   | 17.8 | 24  | 30.2 | mA   |

|                         |                                                                  | IDRVN_x = 1101b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7   | 23.8 | 31  | 40.2 | mA   |

|                         |                                                                  | IDRVN_x = 1110b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 27   | 48  | 63   | mA   |

|                         |                                                                  | IDRVN_x = 1111b, V <sub>GSx</sub> = 3 V, V <sub>PVDD</sub> ≥ 7 V | 45   | 62  | 79   | mA   |

| I <sub>HOLD</sub>       | Gate pullup hold current                                         | Gate hold source current, V <sub>GSx</sub> = 3 V                 | 5    | 16  | 30   | mA   |

| I <sub>STRONG</sub>     | Gate pulldown strong current                                     | V <sub>GSx</sub> = 3 V I <sub>DRV</sub> = 0.5 to 12 mA           | 30   | 62  | 100  | mA   |

| STRONG                  | Gate pulldown strong current                                     | V <sub>GSx</sub> = 3 V I <sub>DRV</sub> = 16 to 62 mA            | 45   | 128 | 200  | mA   |

| R <sub>PDSA_LS</sub>    | Low-side semi-active gate pulldown                               | GLx to SL, V <sub>GSx</sub> = 3 V                                |      | 1.8 |      | kΩ   |

| R <sub>PDSA_LS</sub>    | Low-side semi-active gate pulldown                               | GLx to SL, V <sub>GSx</sub> = 1 V                                |      | 5   |      | kΩ   |

| R <sub>PD_HS</sub>      | High-side passive gate pulldown resistor                         | GHx to SHx                                                       |      | 150 |      | kΩ   |

| R <sub>PD_LS</sub>      | Low-side passive gate pulldown resistor                          | GLx to SL                                                        |      | 150 |      | kΩ   |

| SHx                     | Switch-node sense leakage current                                | Into SHx, SHx = PVDD < 28 V GHx -<br>SHx = 0 V, nSLEEP = 0 V     | -5   | 0   | 20   | μA   |

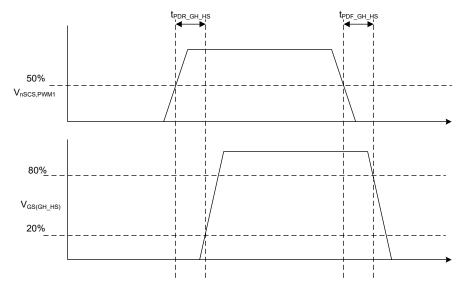

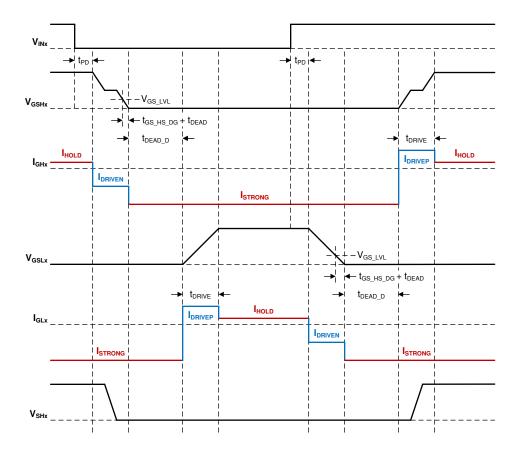

| GATE DRIV               | /ER TIMINGS (GHx, GLx)                                           | -                                                                |      |     |      |      |

| t <sub>PDR_LS</sub>     | Low-side rising propagation delay                                | Input to GLx rising                                              |      | 300 | 850  | ns   |

| <br>t <sub>PDF_LS</sub> | Low-side falling propagation delay                               | Input to GLx falling                                             |      | 300 | 600  | ns   |

| <br>t <sub>PDR_HS</sub> | High-side rising propagation delay                               | Input to GHx rising                                              |      | 300 | 600  | ns   |

| t <sub>PDF_HS</sub>     | High-side falling propagation delay                              | Input to GHx rising                                              |      | 300 | 600  | ns   |

| t <sub>DEAD</sub>       | Internal handshake dead-time                                     | GLx/GHx falling 10% to GHx/GLx rising 10%                        |      | 350 |      | ns   |

$5 \text{ V} \le \text{V}_{\text{PVDD}} \le 35 \text{ V}, 3.1 \text{ V} \le \text{V}_{\text{DVDD}} \le 5.5 \text{ V}, -40 ^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150 ^{\circ}\text{C}$  (unless otherwise noted). Typical limits apply for  $\text{V}_{\text{PVDD}} = 13.5 \text{ V}, \text{V}_{\text{DVDD}} = 5 \text{ V}$  and  $\text{T}_{\text{J}} = 25 ^{\circ}\text{C}$ .

|                       | PARAMETER                            | TEST CONDITIONS                                                                     | MIN            | TYP                 | MAX                      | UNIT  |

|-----------------------|--------------------------------------|-------------------------------------------------------------------------------------|----------------|---------------------|--------------------------|-------|

|                       |                                      | VGS_TDEAD = 00b, Handshake only                                                     |                | 0                   |                          | μs    |

| •                     | Incortable digital dead time         | VGS_TDEAD = 01b                                                                     | 1.6            | 2                   | 2.4                      | μs    |

| t <sub>DEAD_D</sub>   | Insertable digital dead-time         | VGS_TDEAD = 10b                                                                     | 3.4            | 4                   | 4.6                      | μs    |

|                       |                                      | VGS_TDEAD = 11b                                                                     | 6              | 8                   | 10                       | μs    |

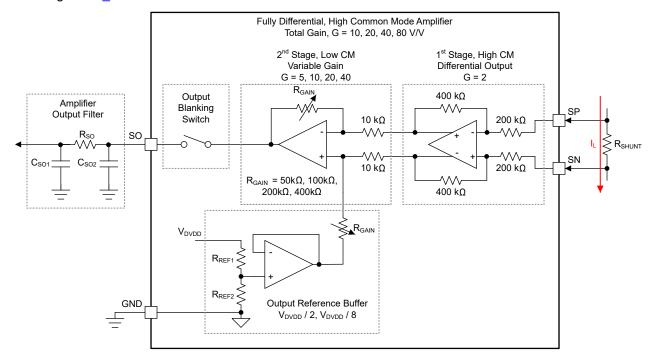

| CURRENT               | SHUNT AMPLIFIERS (SN, SO, SP)        |                                                                                     |                |                     |                          |       |

| V <sub>COM</sub>      | Common mode input range              |                                                                                     | -2             |                     | V <sub>PVDD</sub> + 2    | ٧     |

|                       |                                      | CSA_GAIN = 00b                                                                      | 9.75           | 10                  | 10.25                    | V/V   |

| _                     | 0 115                                | CSA_GAIN = 01b                                                                      | 19.5           | 20                  | 20.5                     | V/V   |

| G <sub>CSA</sub>      | Sense amplifier gain                 | CSA_GAIN = 10b                                                                      | 38.8           | 40                  | 41.2                     | V/V   |

|                       |                                      | CSA_GAIN = 11b                                                                      | 77.6           | 80                  | 82.4                     | V/V   |

|                       | Sense amplifier settling time to 1%  | V <sub>SO_STEP</sub> = 1.5 V, G <sub>CSA</sub> = 10 V/V C <sub>SO</sub> = 60 pF     |                | 2.2                 |                          | μs    |

|                       |                                      | V <sub>SO_STEP</sub> = 1.5 V, G <sub>CSA</sub> = 20 V/V C <sub>SO</sub> = 60 pF     |                | 2.2                 |                          | μs    |

| t <sub>SET</sub>      |                                      | V <sub>SO_STEP</sub> = 1.5 V, G <sub>CSA</sub> = 40 V/V C <sub>SO</sub> = 60 pF     |                | 2.2                 |                          | μs    |

|                       |                                      | V <sub>SO_STEP</sub> = 1.5 V, G <sub>CSA</sub> = 80 V/V C <sub>SO</sub> = 60 pF     |                | 3                   |                          | μs    |

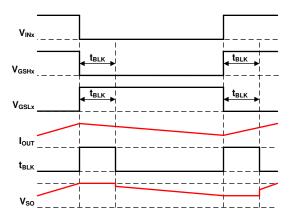

|                       |                                      | CSA_BLK = 000b                                                                      |                | 0                   |                          | %     |

|                       |                                      | CSA_BLK = 001b                                                                      |                | 25                  |                          | %     |

|                       |                                      | CSA_BLK = 010b                                                                      |                | 37.5                |                          | %     |

| t <sub>BLK_CSA</sub>  | Sense amplifier output blanking time | CSA_BLK = 011b                                                                      |                | 50                  |                          | %     |

|                       | (% of Gate driver TDRIVE)            | CSA_BLK = 100b                                                                      |                | 62.5                |                          | %     |

|                       |                                      | CSA_BLK = 101b                                                                      |                | 75                  |                          | %     |

|                       |                                      | CSA_BLK = 110b                                                                      |                | 87.5                |                          | %     |

|                       |                                      | CSA_BLK = 111b                                                                      |                | 100                 |                          | %     |

| t <sub>SLEW CSA</sub> | Output slew rate                     | C <sub>SO</sub> = 60 pF                                                             |                | 2.5                 |                          | V/µs  |

|                       |                                      | V <sub>SPx</sub> = V <sub>SNx</sub> = 0 V, CSA_DIV = 0b                             | V <sub>C</sub> | <sub>OVDD</sub> / 2 |                          | V     |

| $V_{BIAS}$            | Output voltage bias                  | V <sub>SPx</sub> = V <sub>SNx</sub> = 0 V, CSA_DIV = 1b                             | V              | <sub>DVDD</sub> / 8 |                          | V     |

| V <sub>LINEAR</sub>   | Linear output voltage range          | V <sub>DVDD</sub> = 3.3 V = 5 V                                                     | 0.25           |                     | V <sub>DVDD</sub> – 0.25 | V     |

| V <sub>OFF</sub>      | Input offset voltage                 | V <sub>SPx</sub> = V <sub>SNx</sub> = 0V, T <sub>J</sub> = 25°C                     | -1             |                     | 1                        | mV    |

| V <sub>OFF_D</sub>    | Input offset voltage drift           | V <sub>SPx</sub> = V <sub>SNx</sub> = 0 V                                           |                | ±10                 | ±25                      | μV/°C |

| I <sub>BIAS</sub>     | Input bias current                   | V <sub>SPx</sub> = V <sub>SNx</sub> = 0 V                                           |                |                     | 100                      | μA    |

| I <sub>BIAS OFF</sub> | Input bias current offset            | I <sub>SPx</sub> - I <sub>SNx</sub>                                                 |                |                     | 100                      | μA    |

| D.,, 10_0             | ·                                    | DC, -40 ≤ T <sub>J</sub> ≤ 125°C                                                    | 72             | 90                  |                          | dB    |

| CMRR                  | Common mode rejection ratio          | DC, -40 ≤ T <sub>J</sub> ≤ 150°C                                                    | 69             | 90                  |                          | dB    |

|                       |                                      | 20kHz                                                                               |                | 80                  |                          | dB    |

|                       |                                      | PVDD to SOx, DC                                                                     |                | 100                 |                          | dB    |

| PSRR                  | Power supply rejection ratio         | PVDD to SOx, 20kHz                                                                  |                | 90                  |                          | dB    |

|                       |                                      | PVDD to SOx, 400kHz                                                                 |                | 70                  |                          | dB    |

| GATE DRIV             | /ER PROTECTION CIRCUITS              | - 12 - 21., 12 - 1.                                                                 |                |                     |                          |       |

|                       |                                      | V <sub>VCP</sub> - V <sub>PVDD</sub> , V <sub>VCP</sub> falling<br>VCP_UV_MODE = 0b | 4              | 4.75                | 5.5                      | V     |

| V <sub>CP_UV</sub>    | Charge pump undervoltage threshold   | V <sub>VCP</sub> - V <sub>PVDD</sub> , V <sub>VCP</sub> falling<br>VCP_UV_MODE = 1b | 5.5            | 6.25                | 7                        | V     |

www.ti.com

|                        | PARAMETER                                                     | TEST CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNIT |

|------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|------|

| t <sub>CP_UV_DG</sub>  | Charge pump undervoltage deglitch time                        |                                                                                           | 8     | 10    | 12.75 | μs   |

| V <sub>CP_SO</sub>     | Charge pump tripler to doubler switch over threshold          | V <sub>PVDD</sub> rising                                                                  | 17.75 | 18.75 | 19.75 | V    |

| V <sub>CP_SO</sub>     | Charge pump tripler to doubler switch over threshold          | V <sub>PVDD</sub> falling                                                                 | 16.75 | 17.75 | 18.75 | V    |

| t <sub>CP_SO_HYS</sub> | Charge pump tripler to doubler switch over hysteresis         |                                                                                           |       | 1.15  |       | V    |

| t <sub>CP_SO_DG</sub>  | Charge pump tripler to doubler switch over threshold deglitch |                                                                                           | 8     | 10    | 12.75 | μs   |

| V <sub>GS_CLP</sub>    | High-side driver VGS protection clamp                         |                                                                                           | 12.5  | 15    | 17    | V    |

|                        | Coto voltago manitar threshold                                | V <sub>GHx</sub> - V <sub>SHx</sub> , V <sub>GLx</sub> - V <sub>PGND</sub> , VGS_LVL = 0b | 1.1   | 1.4   | 1.75  | V    |

| $V_{GS\_LVL}$          | Gate voltage monitor threshold                                | $V_{GHx} - V_{SHx}$ , $V_{GLx} - V_{PGND}$ , $VGS\_LVL = 1b$                              | 0.75  | 1     | 1.2   | V    |

| t <sub>GS_FLT_DG</sub> | V <sub>GS</sub> fault monitor deglitch time                   |                                                                                           | 1.5   | 2     | 2.75  | μs   |

| t <sub>GS_HS_DG</sub>  | V <sub>GS</sub> handshake monitor deglitch time               |                                                                                           |       | 210   |       | ns   |

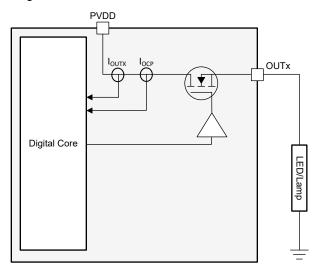

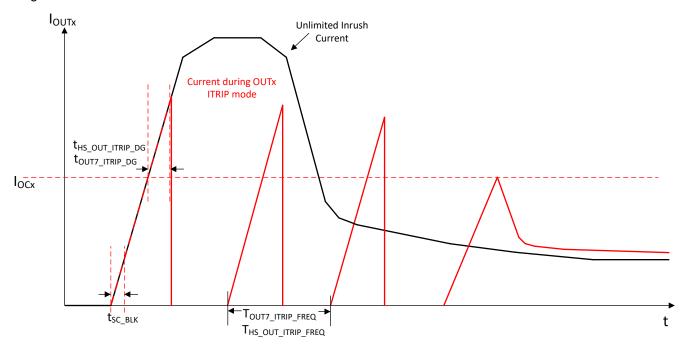

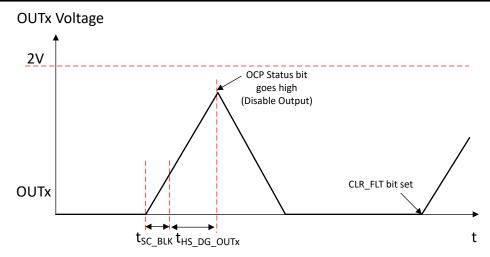

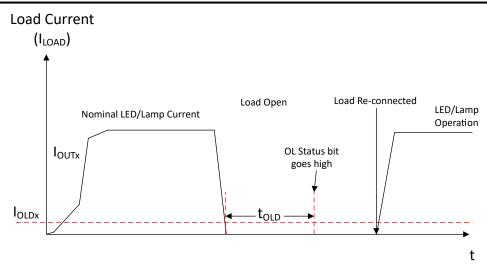

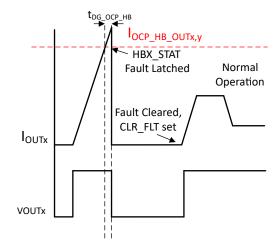

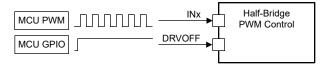

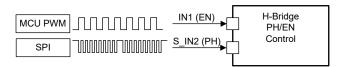

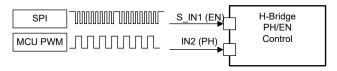

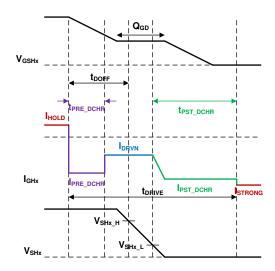

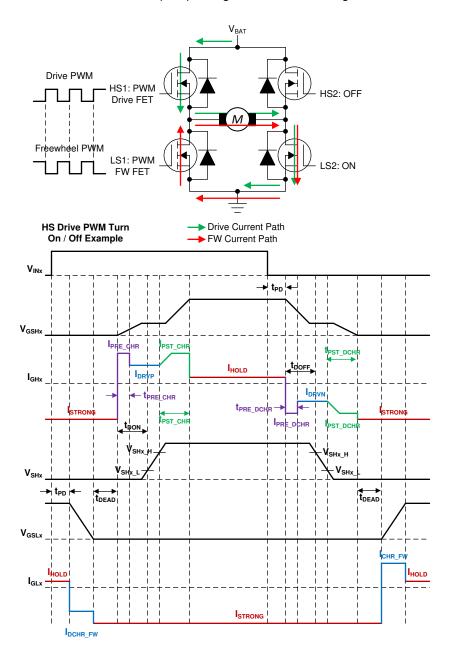

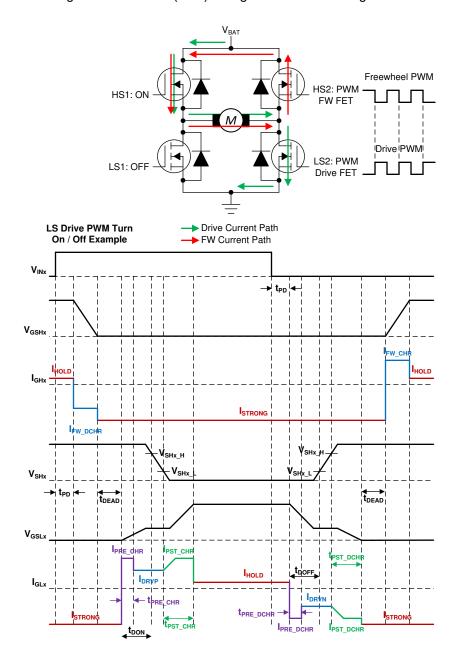

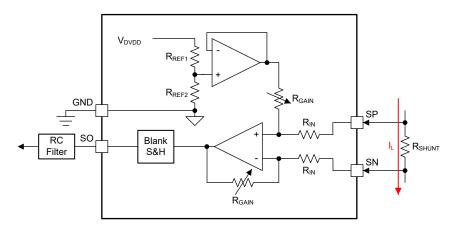

|                        |                                                               | VGS_TDRV = 000b                                                                           | 1.5   | 2     | 2.5   | μs   |