# 省电型流控螺线管驱动器

查询样品: DRV120

## 特性

- 用于控制螺线管电流的带有脉宽调制 (PWM) 的集成金属氧化物半导体场效应晶体管 (MOSFET)

- 用于调节螺线管电流的外部感测电阻器

- 螺线管电流的快速斜升以保证激活

- 在保持模式中,为了实现低功耗和热耗散,螺线管 电流被减少

- 可外部设定峰值电流、峰值电流的保持时间、保持 电流和 PWM 时钟频率。它们还可以在无需外部组 件的情况下在标称值上运行。

- 内部电源电压调节

- 高达 28V 的外部电源电压

- 保护

- 热关断

- 欠压闭锁 (UVLO)

- 最大斜升时间

- 可选状态 (STATUS) 输出

- 运行温度范围: -40℃ 至 105℃

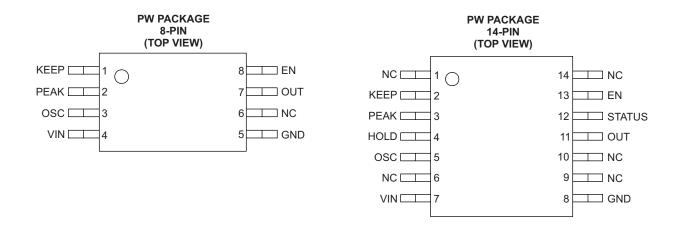

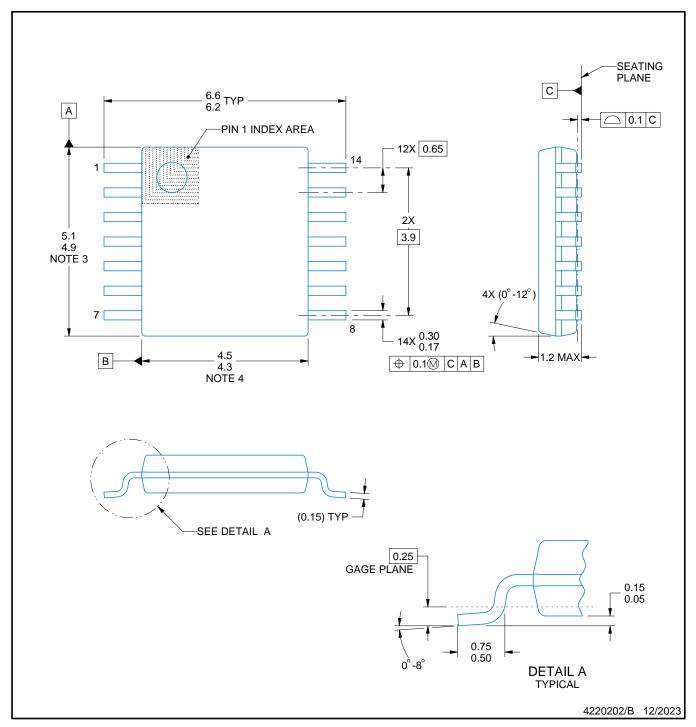

- 8 引脚和 14 引脚 薄型小外形尺寸 (TSSOP) 封装 选项

# 应用范围

- 电动机械驱动器: 螺线管、阀门、继电器

- 大型家用电器、太阳能、运输

# 说明

DRV120 是一款针对螺线管的 PWM 电流驱动器。 它被设计成使用控制良好的电流来调节电流以确保激活并同时减少功率耗散。 螺线管电流快速斜升以确保阀门或者继电器的打开。 在最初的斜升后,螺线管电流被保持在峰值以确保正确运行,这之后,为了避免过热问题并减少功率耗散,这个电流被减少至较低的保持水平。

使用一个外部电容器对峰值电流的持续时间进行设定。 电流斜波峰值和保持电平、以及 PWM 频率可由外部电阻器 独立设定。 如果针对相应参数的默认值适用于应用的话,外部设置电阻器也可被省略。

DRV120 可由 6V 至 28V 的外部电源供电运行。

### ORDERING INFORMATION(1)

| PACKAGE <sup>(2)</sup> |                             | ORDERABLE PART<br>NUMBER | TOP-SIDE<br>MARKING |

|------------------------|-----------------------------|--------------------------|---------------------|

| (TSSOP-8) - PW         | (TSSOP-8) - PW Reel of 2000 |                          | 120                 |

| (TSSOP-14) - PW        | Reel of 2000                | DRV120APWR               | 120A                |

<sup>(1)</sup> For the most current packaging and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **TYPICAL APPLICATION**

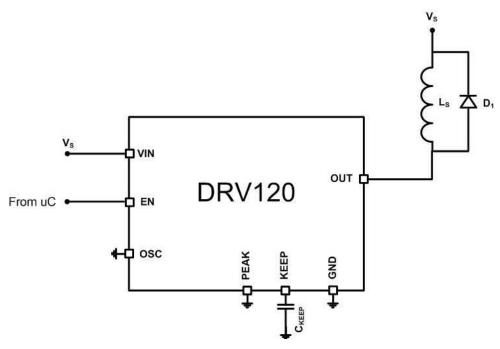

Figure 1. Default Configuration With 8-Pin TSSOP Option

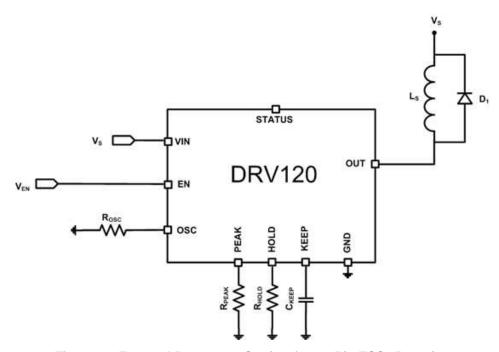

Figure 2. External Parameter Setting for 14-Pin TSSOP Option

# **DEVICE INFORMATION**

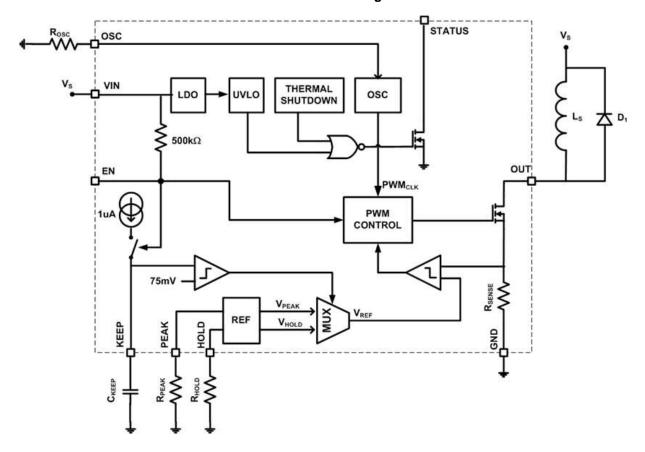

# **Functional Block Diagram**

### **Table 1. TERMINAL FUNCTIONS**

| NAME   | PIN<br>(8-PIN PW) <sup>(1)</sup> | PIN<br>(14-PIN PW) | DESCRIPTION                |

|--------|----------------------------------|--------------------|----------------------------|

| NC     | 6                                | 1, 6, 9, 10, 14    | No connect                 |

| KEEP   | 1                                | 2                  | Keep time set              |

| PEAK   | 2                                | 3                  | Peak current set           |

| HOLD   | -                                | 4                  | Hold current set           |

| OSC    | 3                                | 5                  | PWM frequency set          |

| VIN    | 4                                | 7                  | 6-V to 28-V supply         |

| GND    | 5                                | 8                  | Ground                     |

| OUT    | 7                                | 11                 | Controlled current sink    |

| STATUS | -                                | 12                 | Open drain fault indicator |

| EN     | 8                                | 13                 | Enable                     |

(1) In the 8-pin package, the HOLD pin is not bonded out. For this package, the HOLD mode is configured to default (internal) settings.

# ABSOLUTE MAXIMUM RATINGS(1)(2)

|                  |                                                           |                            | VALUE      | UNIT |

|------------------|-----------------------------------------------------------|----------------------------|------------|------|

| VIN              | Input voltage range                                       |                            | -0.3 to 28 | V    |

|                  | Voltage range on EN, STATUS, PEAK, HOLD, OSC, SENSE, RAMP |                            | –0.3 to 7  | V    |

|                  | Voltage range on OUT                                      |                            | -0.3 to 28 | V    |

|                  | ECD notice                                                | HBM (human body model)     |            |      |

|                  | ESD rating                                                | CDM (charged device model) | 500        | V    |

| TJ               | Operating virtual junction tempe                          | rature range               | -40 to 125 | °C   |

| T <sub>stg</sub> | Storage temperature range                                 |                            | -65 to 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                  |                               | MIN | NOM | MAX | UNIT |

|------------------|-------------------------------|-----|-----|-----|------|

| I <sub>OUT</sub> | Average solenoid DC current   |     |     | 125 | mA   |

| V <sub>IN</sub>  | Supply voltage                | 6   | 12  | 26  | V    |

| C <sub>IN</sub>  | Input capacitor               | 1   | 4.7 |     | μF   |

| L                | Solenoid inductance           |     | 1   |     | Н    |

| T <sub>A</sub>   | Operating ambient temperature | -40 |     | 105 | °C   |

### THERMAL INFORMATION

|                    |                                                             | DRV120                                                                                                                                                                                        | DRV120 |       |

|--------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

|                    | THERMAL METRIC                                              | PW                                                                                                                                                                                            | PW     | UNITS |

|                    |                                                             | PW         PW           8 PINS         14 PINS           183.8         122.6           69.2         51.2           112.6         64.3           10.4         6.5           110.9         63.7 |        |       |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance <sup>(1)</sup>       | 183.8                                                                                                                                                                                         | 122.6  |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance (2)               | 69.2                                                                                                                                                                                          | 51.2   |       |

| $\theta_{JB}$      | Junction-to-board thermal resistance (3)                    | 112.6                                                                                                                                                                                         | 64.3   | 0000  |

| ΨЈΤ                | Junction-to-top characterization parameter <sup>(4)</sup>   | 10.4                                                                                                                                                                                          | 6.5    | °C/W  |

| ΨЈВ                | Junction-to-board characterization parameter <sup>(5)</sup> | 110.9                                                                                                                                                                                         | 63.7   |       |

| $\theta_{JCbot}$   | Junction-to-case (bottom) thermal resistance (6)            | N/A                                                                                                                                                                                           | N/A    |       |

- (1) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环 境热阻。

- (2) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

- 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。

- 结至顶部特征参数, ψ,ιτ,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该参 数以便获得 θ<sub>JA</sub>。

- 结至电路板特征参数, Ψ<sub>JB</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该 参数以便获得 θ l<sub>A</sub>。 通过在外露(电源)焊盘上进行冷板测试仿真来获得 结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准 测试,但可在 ANSI SEMI

- 标准 G30-88 中能找到内容接近的说明。

All voltage values are with respect to network ground terminal.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 14 V,  $T_A$  = -40°C to 105°C, over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                | TEST CONDITIONS                                                                             | MIN  | TYP | MAX | UNIT |

|-----------------------|------------------------------------------|---------------------------------------------------------------------------------------------|------|-----|-----|------|

| SUPPLY                |                                          |                                                                                             |      |     |     |      |

|                       | Standby current                          | EN = 0, V <sub>IN</sub> = 14 V                                                              |      | 100 | 150 |      |

| IQ                    | Quiescent current                        | EN = 1, V <sub>IN</sub> = 14 V                                                              |      | 300 | 400 | μA   |

| CURREN                | T DRIVER                                 |                                                                                             |      |     | ,   |      |

| R <sub>OUT</sub>      | OUT to GND resistance                    | I <sub>OUT</sub> = 200 mA                                                                   |      | 1.7 | 2.5 | Ω    |

| f <sub>PWM</sub>      | PWM frequency                            | OSC = GND                                                                                   | 15   | 20  | 25  | kHz  |

| D <sub>MAX</sub>      | Maximum PWM duty cycle                   |                                                                                             |      | 100 |     | %    |

| D <sub>MIN</sub>      | Minimum PWM duty cycle                   |                                                                                             |      | 9   |     | %    |

| t <sub>D</sub>        | Start-up delay                           | Delay between EN going high until driver enabled <sup>(1)</sup> , f <sub>PWM</sub> = 20 kHz |      | 25  | 50  | μs   |

| CURREN'               | T CONTROLLER, INTERNAL SETTING           | s                                                                                           |      |     | ,   |      |

| I <sub>PEAK</sub>     | Peak current                             | PEAK = GND                                                                                  | 160  | 200 | 240 | mA   |

| I <sub>HOLD</sub>     | Hold current                             | HOLD = GND                                                                                  | 40   | 50  | 60  | mA   |

| CURREN                | T CONTROLLER, EXTERNAL SETTING           | GS .                                                                                        |      |     |     |      |

| t <sub>KEEP</sub> (2) | Externally set keep time at peak current | C <sub>KEEP</sub> = 1 μF                                                                    |      | 75  |     | ms   |

|                       |                                          | $R_{PEAK} = 50 \text{ k}\Omega$                                                             |      | 250 |     | _    |

| I <sub>PEAK</sub>     | Externally set peak current              | R <sub>PEAK</sub> = 200 kΩ                                                                  |      | 83  |     | mA   |

|                       |                                          | $R_{HOLD}$ = 50 kΩ $R_{HOLD}$ = 200 kΩ                                                      |      | 100 |     |      |

| I <sub>HOLD</sub>     | Externally set hold current              |                                                                                             |      | 33  |     | mA   |

|                       |                                          | $R_{OSC} = 50 \text{ k}\Omega$                                                              |      | 60  |     |      |

| t <sub>PWM</sub>      | Externally set PWM frequency             | R <sub>OSC</sub> = 200 kΩ                                                                   | 20   |     |     | kHz  |

| LOGIC IN              | PUT LEVELS (EN)                          | ,                                                                                           | 1    |     | Į.  |      |

| V <sub>IL</sub>       | Input low level                          |                                                                                             |      |     | 1.3 | V    |

| V <sub>IH</sub>       | Input high level                         |                                                                                             | 1.65 |     |     | V    |

| R <sub>EN</sub>       | Input pull-up resistance                 |                                                                                             | 350  | 500 |     | kΩ   |

| LOGIC O               | UTPUT LEVELS (STATUS)                    |                                                                                             |      |     | ,   |      |

| V <sub>OL</sub>       | Output low level                         | Pull-down activated, I <sub>STATUS</sub> = 2 mA                                             |      |     | 0.3 | V    |

| I <sub>IL</sub>       | Output leakage current                   | Pull-down deactivated, V(STATUS) = 5 V                                                      |      |     | 1   | μA   |

| UNDERV                | OLTAGE LOCKOUT                           | ,                                                                                           | 1    |     |     |      |

| V <sub>UVLO</sub>     | Undervoltage lockout threshold           |                                                                                             |      | 4.6 |     | V    |

|                       | L SHUTDOWN                               | •                                                                                           |      |     |     |      |

| T <sub>TSD</sub>      | Junction temperature shutdown threshold  |                                                                                             |      | 160 |     | °C   |

| T <sub>TSU</sub>      | Junction temperature startup threshold   |                                                                                             |      | 140 |     | °C   |

<sup>(1)</sup> Logic HIGH between 4 V and 7 V. Note: absolute max voltage rating is 7 V.

(2) Either internal or external t<sub>KEEP</sub> time setting is selected to be activated during manufacturing of production version of DRV120.

#### FUNCTIONAL DESCRIPTION

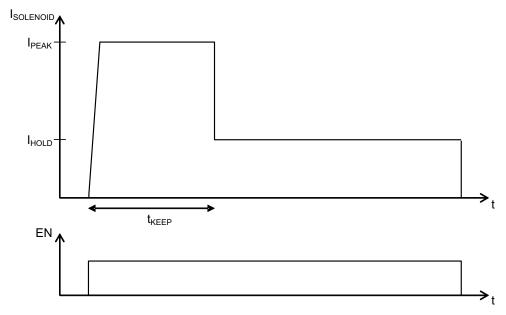

DRV120 controls the current through the solenoid as shown in Figure 3. Activation starts when EN pin voltage is pulled high either by an external driver or internal pull-up. In the beginning of activation, DRV120 allows the load current to ramp up to the peak value  $I_{PEAK}$  and it regulates it at the peak value for the time,  $t_{KEEP}$ , before reducing it to  $I_{HOLD}$ . The load current is regulated at the hold value as long as the EN pin is kept high. The initial current ramp-up time depends on the inductance and resistance of the solenoid. Once EN pin is driven to GND, DRV120 allows the solenoid current to decay to zero.

Figure 3. Typical Current Waveform Through the Solenoid

$t_{KEEP}$  is set externally by connecting a capacitor to the KEEP pin. A constant current is sourced from the KEEP pin that is driven into an external capacitor resulting in a linear voltage ramp. When the KEEP pin voltage reaches 75 mV, the current regulation reference voltage,  $V_{REF}$ , is switched from  $V_{PEAK}$  to  $V_{HOLD}$ . Dependency of  $t_{KEEP}$  from the external capacitor size can be calculated by:

$$t_{KEEP}[s] = C_{KEEP}[F] \cdot 75 \cdot 10^{3} \left[ \frac{s}{F} \right]$$

(1)

The current control loop regulates, cycle-by-cycle, the solenoid current by using an internal current sensing resistor and MOSFET switch. During the ON-cycle, current flows from OUT pin to GND pin through the internal switch as long as voltage over current sensing resistor is less than  $V_{REF}$ . As soon as the current sensing voltage is above  $V_{REF}$ , the internal switch is immediately turned off until the next ON-cycle is triggered by the internal PWM clock signal. In the beginning of each ON-cycle, the internal switch is turned on and stays on for at least the time determined by the minimum PWM signal duty cycle,  $D_{MIN}$ .

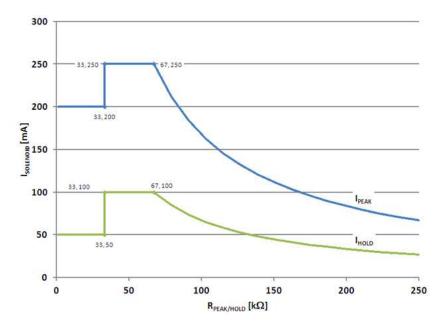

$I_{PEAK}$  and  $I_{HOLD}$  depend on fixed resistance values  $R_{PEAK}$  and  $R_{HOLD}$  as shown in Figure 4. If the PEAK pin is connected to ground or if  $R_{PEAK}$  is below 33.33 k $\Omega$  (typ value), then  $I_{PEAK}$  is at its default value (internal setting). The  $I_{PEAK}$  value can alternatively be set by connecting an external resistor to ground from the PEAK pin. For example, if a 50-k $\Omega$  (=  $R_{PEAK}$ ) resistor is connected between PEAK and GND, then the externally set  $I_{PEAK}$  level will be 250 mA. If  $R_{PEAK}$  = 200 k $\Omega$  is, then the externally set  $I_{PEAK}$  level will be 83 mA. HOLD current external setting,  $I_{HOLD}$ , works in the same way, but current levels are 40% of the  $I_{PEAK}$ . External settings for  $I_{PEAK}$  and  $I_{HOLD}$  are independent of each other.  $I_{PEAK}$  and  $I_{HOLD}$  values can be calculated by using the formula below.

$$I_{PEAK} = \frac{250\text{mA}}{R_{PEAK}} \cdot 66.67\text{k}\Omega; 66.67\text{k}\Omega < R_{PEAK} < 550\text{k}\Omega$$

(2)

$$I_{HOLD} = \frac{100\text{mA}}{R_{HOLD}} \cdot 66.67\text{k}\Omega; 66.67\text{k}\Omega < R_{HOLD} < 250\text{k}\Omega \tag{3}$$

Figure 4. PEAK and HOLD Mode Current Settings

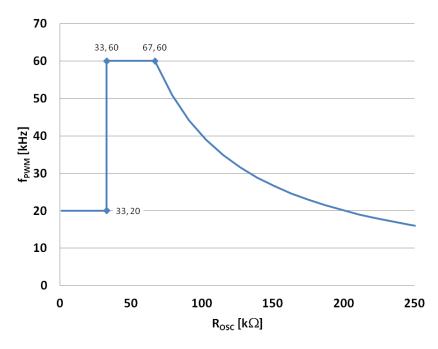

Frequency of the internal PWM clock signal,  $PWM_{CLK}$ , that triggers each ON-cycle can be adjusted by external resistor,  $R_{OSC}$ , connected between OSC and GND. Frequency as a function of resistor value is shown in Figure 5. Default frequency is used when OSC is connected to GND directly. PWM frequency as a function of external fixed adjustment resistor value (greater than 66.67 k $\Omega$ ) is given below.

$$f_{PWM} = \frac{60kHz}{R_{OSC}} \cdot 66.67k\Omega; 66.67k\Omega < R_{OSC} < 2M\Omega$$

(4)

Figure 5. PWM Clock Frequency Setting

Open-drain STATUS output is deactivated if either under voltage lockout or thermal shutdown blocks have triggered.

www.ti.com 11-Nov-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| DRV120APWR            | Active | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 120A         |

| DRV120APWR.B          | Active | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 120A         |

| DRV120APWRG4          | Active | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 120A         |

| DRV120APWRG4.B        | Active | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 120A         |

| DRV120PWR             | Active | Production    | TSSOP (PW)   8  | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 120          |

| DRV120PWR.B           | Active | Production    | TSSOP (PW)   8  | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 120          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

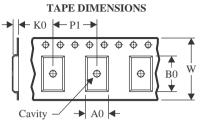

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

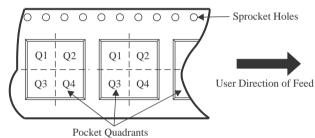

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV120APWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| DRV120APWRG4 | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| DRV120PWR    | TSSOP           | PW                 | 8  | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

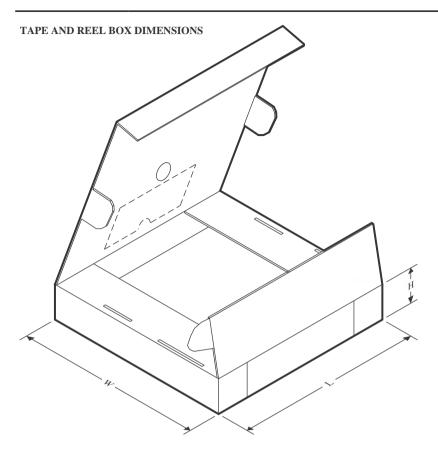

# \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV120APWR   | TSSOP        | PW              | 14   | 2000 | 353.0       | 353.0      | 32.0        |

| DRV120APWRG4 | TSSOP        | PW              | 14   | 2000 | 353.0       | 353.0      | 32.0        |

| DRV120PWR    | TSSOP        | PW              | 8    | 2000 | 353.0       | 353.0      | 32.0        |

### NOTES:

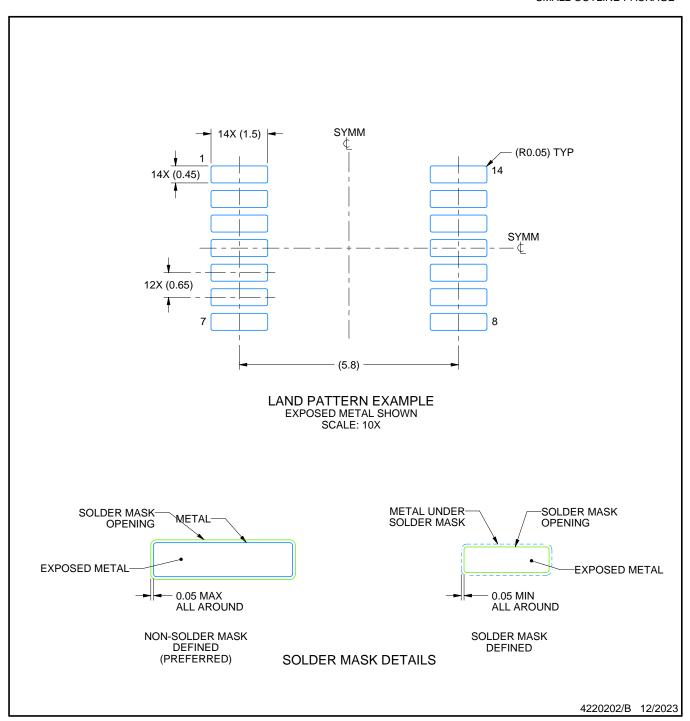

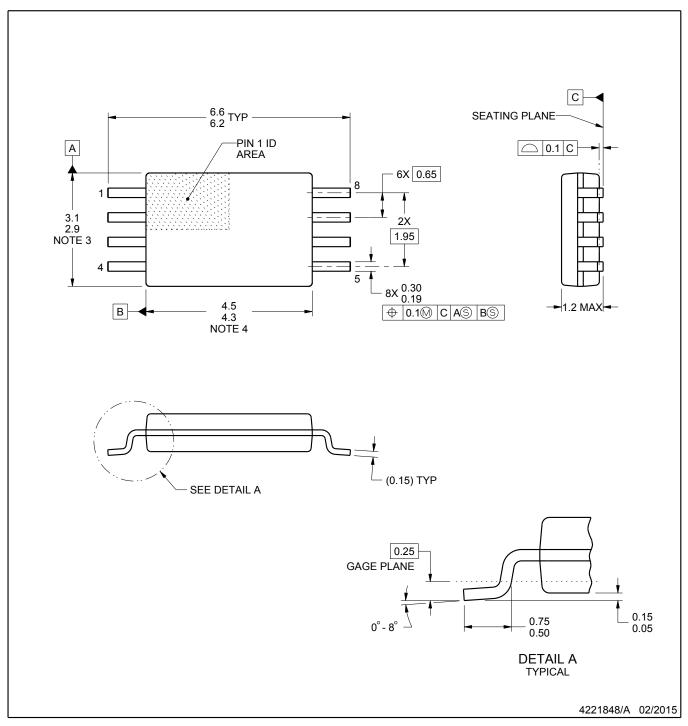

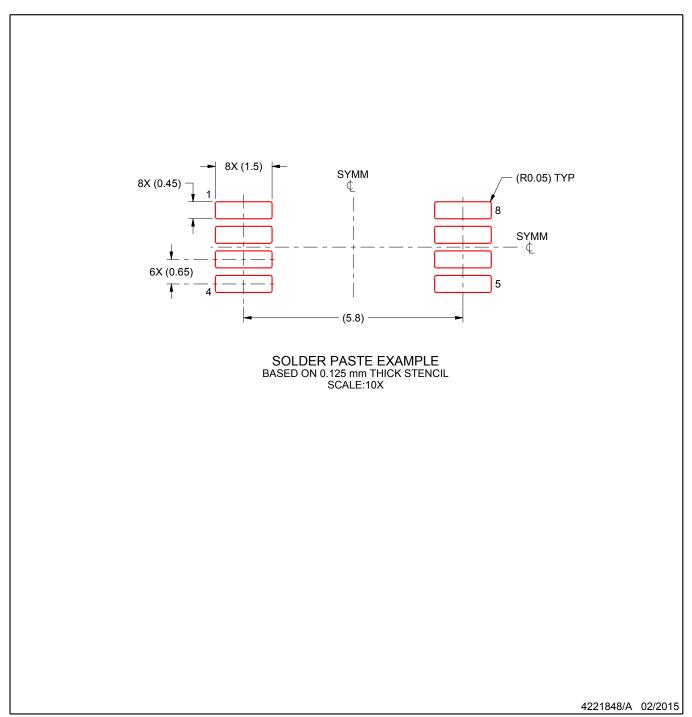

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

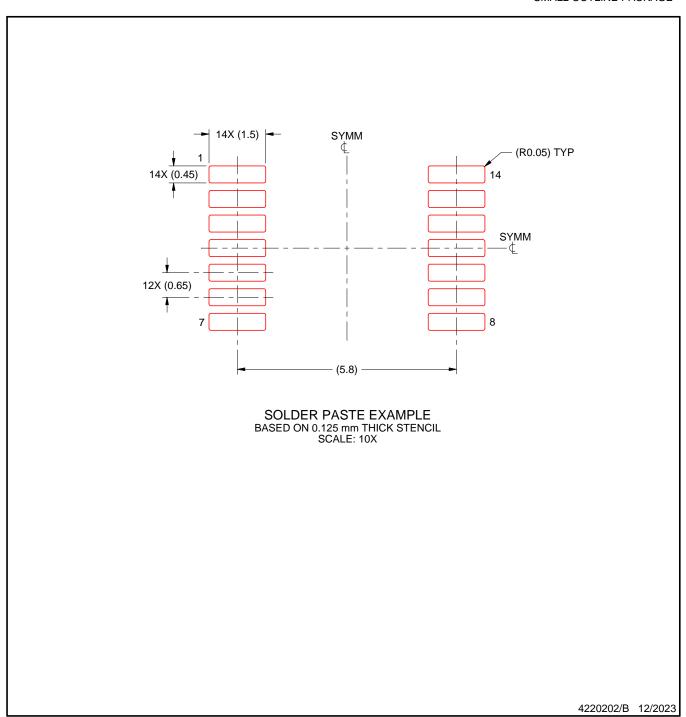

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

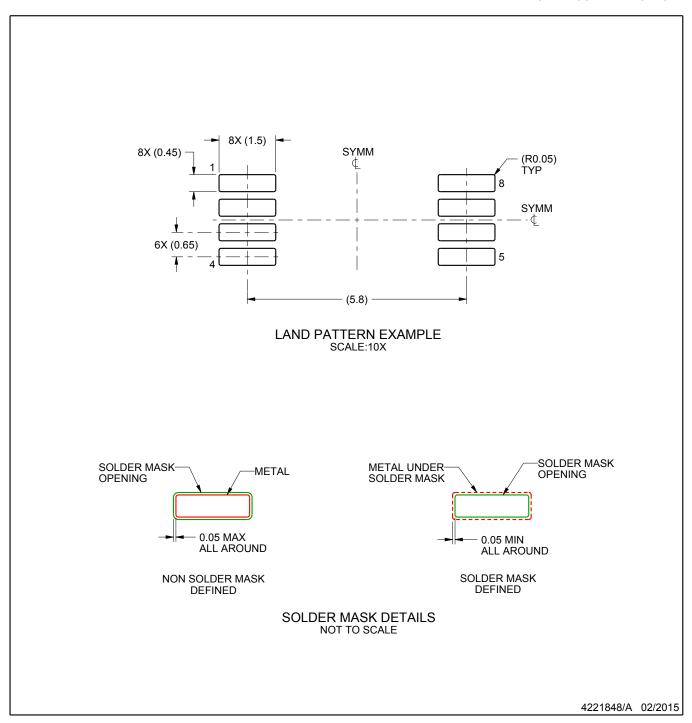

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153, variation AA.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月