DLPC6401

ZHCSC08C - DECEMBER 2013-REVISED AUGUST 2015

# DLPC6401 DLP® 数据处理器

# 1 特性

- 提供一个 30 位输入像素接口:

- YUV, YCrCb 或 RGB 数据格式

- 每个色彩 8,9 或 10 位

- 像素时钟支持高达 150MHz

- 提供一个单通道、基于低压差分信令 (LVDS) 且 兼容平板显示 (FPD)-Link 的输入接口:

- 支持有效像素时钟速率高达 90MHz 的输入源

- 支持四种经解调的像素映射模式,适用于 8、 9、10 路 YUV、YCrCb 或 RGB 格式的输入

- 支持 45Hz 至 120Hz 的帧速率

- 完全支持 Diamond 0.45 WXGA

- 高速、双倍数据速率 (DDR) 数字微镜器件 (DMD) 接口

- 149.33MHz ARM926™微处理器

- 微处理器外设:

- 可编程脉宽调制 (PWM) 和捕捉定时器

- 两个 I<sup>2</sup>C 端口

- 两个通用异步收发器 (UART) 端口(只用于调试)

- 32KB 内部随机存取存储器 (RAM)

- 专用发光二级管 (LED) PWM 发生器

- 图像处理:

- 针对标准、宽和黑边缘的自动锁

- 1D 梯形失真校正

- 可编程后期色彩校正 (Degamma)

- 屏幕显示 (OSD)

- 初始屏幕显示支持

- 集成型时钟生成电路

- 运行在单个 32MHz 晶振上

- 集成展频计时

- 集成 64Mb 帧存储器,无需使用外部高速存储器

- 外部存储器支持:针对微处理器和 PWM 序列的并 行闪存

- 系统控制:

- DMD 电源和复位驱动器控制

- DMD 水平和垂直显示图像抖动

- 支持边界扫描测试的 JTAG

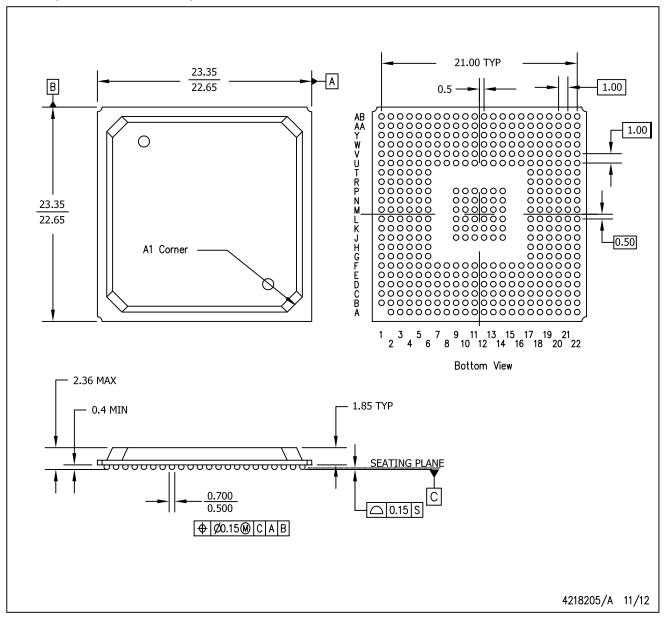

- 419 引脚塑料球状引脚栅格阵列封装

#### 2 应用

- 电池供电的移动式附件高清 (HD) 投影仪

- 电池供电的智能 HD 附件

- 无屏幕显示 交互式显示器

- 移动电影院

- 游戏显示

### 3 说明

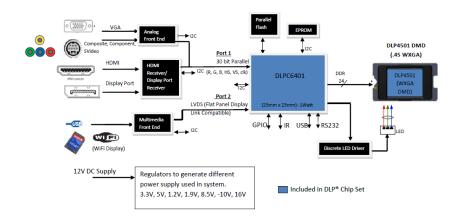

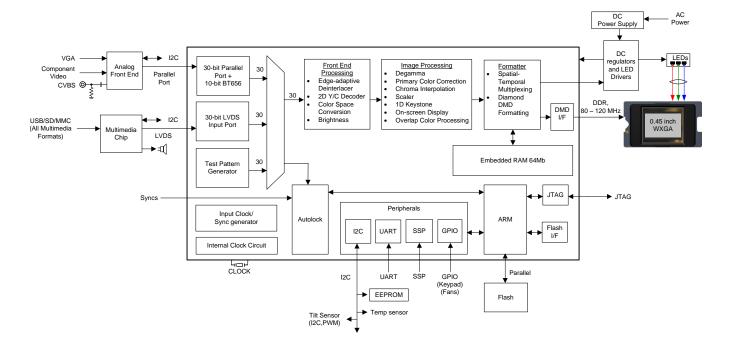

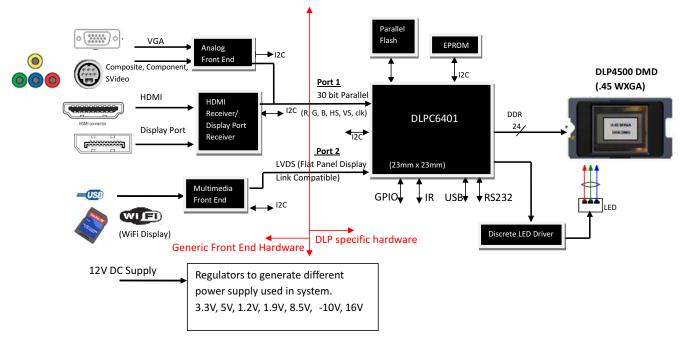

DLPC6401 数字控制器属于 DLP4500 (0.45 WXGA) 芯片组,用于支持 DLP4500 数字微镜器件 (DMD) 的可靠运行。DLPC6401 控制器在系统电子设备与 DMD 之间提供一个方便的多功能接口,从而实现了小外形尺寸的高分辨率 HD 显示屏。

#### 器件信息(1)

| 部件号      | 封装        | 阵列尺寸 (像素)         |

|----------|-----------|-------------------|

| DLPC6401 | BGA (419) | 23.00mm x 23.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

#### 典型应用图

Changes from Original (December 2013) to Revision A

|                            | 目录                                                                                           | L<br>C            |                           |      |

|----------------------------|----------------------------------------------------------------------------------------------|-------------------|---------------------------|------|

| 1<br>2<br>3<br>4<br>5<br>6 | 特性                                                                                           | 7<br>8<br>9<br>10 | Switching Characteristics |      |

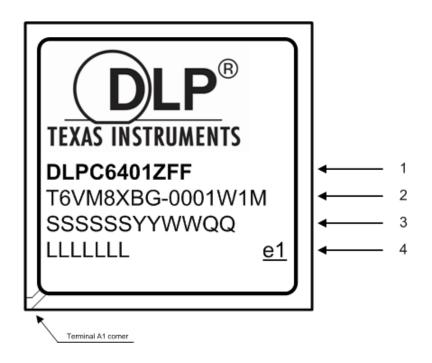

| 注: Z                       | 修订历史记录<br>之前版本的页码可能与当前版本有所不同。<br>nges from Revision B (June 2015) to Revision C<br>已更新器件标记图。 |                   |                           | Page |

|                            | nges from Revision A (January 2014) to Revision B                                            |                   |                           | Page |

| 桂                          | 已添加 ESD 额定值表,特性 描述部分,器件功能模式,应用和当支持部分以及机械、封装和可订购信息部分                                          |                   |                           |      |

已删除产品预览条.......1

Page

# 5 Pin Configuration and Functions

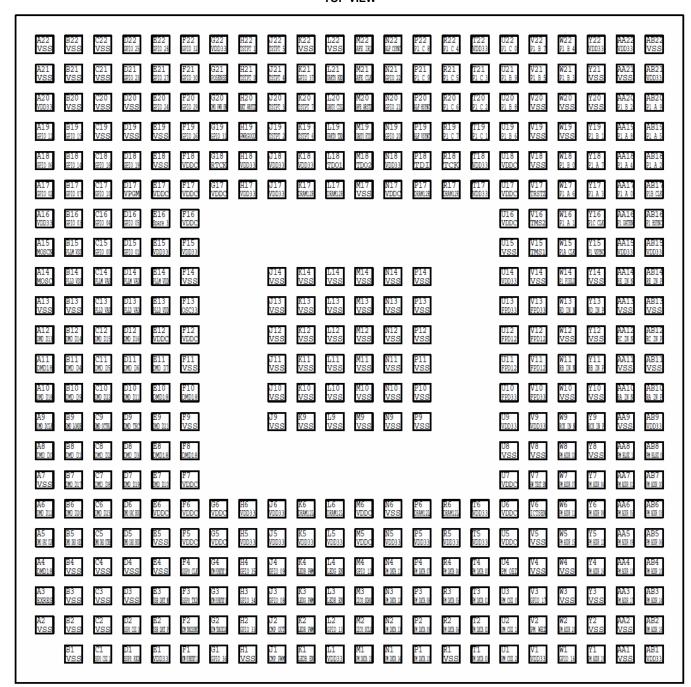

#### ZFF PACKAGE 419-PIN BGA TOP VIEW

#### **Pin Functions**

| Pin Functions  PIN <sup>(1)</sup> VO <sup>(2)</sup> |     |                      |                     |                                                                                             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------------------------|-----|----------------------|---------------------|---------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. POWER TYPE                                 |     | INTERNAL TERMINATION | CLK SYSTEM          | DESCRIPTION                                                                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| CONTROL                                             |     | 7 0 11 2 11          |                     |                                                                                             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| EXT_ARST                                            | H20 | VDD33                | O <sub>1</sub>      |                                                                                             | Async    | External reset output, LOW true. This output is asserted low immediately upon asserting power-up reset (POSENSE) low and remains low while POSENSE remains low. EXT_ARSTZ continues to be held low after the release of power-up reset (that is, POSENSE set high) until released by software. EXT_ARSTZ is also asserted low approximately 5 µs after the detection of a PWRGOOD or any internally-generated reset. In all cases, it remains active for a minimum of 2 ms after the reset condition is released by software. Note, the ASIC contains a software register that can be used to independently drive this output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

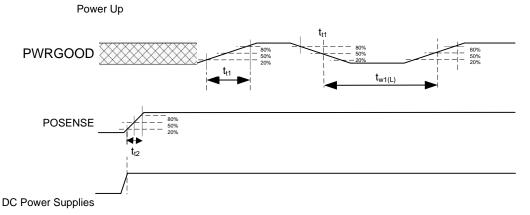

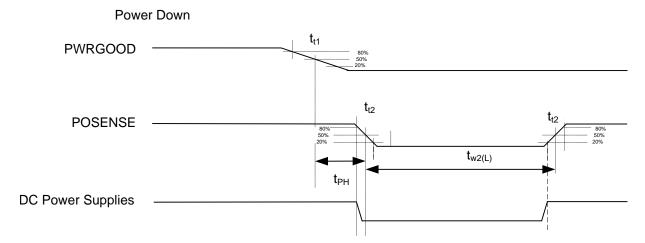

| PWRGOOD                                             | H19 | VDDC                 | l4<br>H             |                                                                                             | Async    | Power Good is an active-high signal with hysteresis that is generated by an external power supply or voltage monitor. A high value indicates all power is within operating voltage specifications and the system is safe to exit its reset state. A transition from high to low should indicate that the controller or DMD supply voltage will drop below their rated minimum level within the next 0.5 ms (POSENSE must remain active high during this interval). This is an early warning of an imminent power loss condition. This warning is required to enhance long-term DMD reliability. A DMD park sequence, followed by a full controller reset, is performed by the DLPC6401 when PWRGOOD goes low for a minimum of 4 µs protecting the DMD. This minimum de-assertion time is used to protect the input from glitches. Following this, the DLPC6401 is held in its reset state as long as PWRGOOD is low.  PWRGOOD must be driven high for typical operation. The DLPC6401 device acknowledges PWRGOOD as active after it is driven high for a minimum of 625 ns. Uses hysteresis. |  |  |

| POSENSE                                             | G21 |                      | I <sub>4</sub><br>H |                                                                                             | Async    | Power-On Sense is an active-high input signal with hysteresis that is generated by an external voltage monitor circuit. POSENSE must be driven inactive (low) when any of the controller supply voltages are below minimum operating voltage specifications. POSENSE must be active (high) when all controller supply voltages remain above minimum specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| POWER_ON_OFF                                        | N21 | VDD33                | B <sub>2</sub>      |                                                                                             | Async    | Power On or Power Off is an active-high signal that indicates the power of the system. Power On or Power Off is high when the system is in power-up state, and low when the system is in standby. Power On or Power Off can also be used to power on or off an external power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

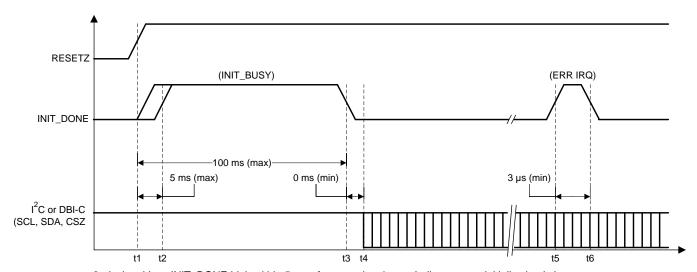

| INIT_DONE                                           | F19 | VDD33                | B <sub>2</sub>      |                                                                                             | Async    | Prior to transferring part of code from parallel flash content to internal memory, the internal memory is initialized and a memory test is performed. The result of this test (pass or fail) is recorded in the system status. If memory test fails, the initialization process is halted. INIT_DONE is asserted twice to indicate an error situation. See Figure 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| I2C_ADDR_SEL                                        | F21 | VDD33                | B <sub>2</sub>      |                                                                                             | Async    | This signal is sampled during power-up. If the signal is low, the I <sup>2</sup> C addresses are 0x34 and 0x35. If the signal is low, the I <sup>2</sup> C are 0x3A and 0x3B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| I2C1_SCL                                            | J3  | VDD33                | B <sub>2</sub>      | Requires an external pullup to 3.3 V. The minimum acceptable pullup value is 1 $k\Omega$ .  | N/A      | I <sup>2</sup> C clock. Bidirectional, open-drain signal. I <sup>2</sup> C slave clock input from the external processor. This bus supports 400 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| I2C1_SDA                                            | J4  | VDD33                | B <sub>2</sub>      | Requires an external pullup to 3.3 V. The minimum acceptable pullup value is 1 k $\Omega$ . | I2C1_SCL | I <sup>2</sup> C data. Bidirectional, open-drain signal. I <sup>2</sup> C slave to accept command or transfer data to and from the external processor. This bus supports 400 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

<sup>(1)</sup> For instructions on handling unused pins, see *General Handling Guidelines for Unused CMOS-Type Pins*.

(2) I/O Type: I = Input, O = Output, B = Bidirectional, and H = Hysteresis. See Table 1 for subscript explanation.

| ster for on-board peripherals nsor. This bus supports 400-n.              |

|---------------------------------------------------------------------------|

| nsor. This bus supports 400-<br>n.                                        |

| eter for on-hoard peripherals                                             |

| nsor. This bus supports 400-<br>n.                                        |

|                                                                           |

| nput (3.3-V LVCMOS). Note stable a maximum of 25 ms ons from high to low. |

|                                                                           |

|                                                                           |

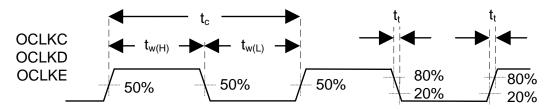

| rite clock 'A'                                                            |

| rite clock 'B'                                                            |

| rite clock 'C'                                                            |

| es hysteresis                                                             |

| Jses hysteresis                                                           |

|                                                                           |

| red for interlaced sources<br>re)                                         |

| pixel data (bit weight 128)                                               |

| oixel data (bit weight 64)                                                |

| pixel data (bit weight 32)                                                |

| oixel data (bit weight 16)                                                |

| pixel data (bit weight 8)                                                 |

| pixel data (bit weight 4)                                                 |

| pixel data (bit weight 2)                                                 |

| oixel data (bit weight 1)                                                 |

| pixel data (bit weight 0.5)                                               |

| oixel data (bit weight 0.25)                                              |

| pixel data (bit weight 128)                                               |

| pixel data (bit weight 64)                                                |

| pixel data (bit weight 32)                                                |

| pixel data (bit weight 16)                                                |

| pixel data (bit weight 8)                                                 |

| pixel data (bit weight 4)                                                 |

| ixel data (bit weight 2)                                                  |

| ixel data (bit weight 1)                                                  |

| pixel data (bit weight 0.5)                                               |

| pixel data (bit weight 0.25)                                              |

| pixel data (bit weight 128)                                               |

| inei data (bit weight 120)                                                |

|                                                                           |

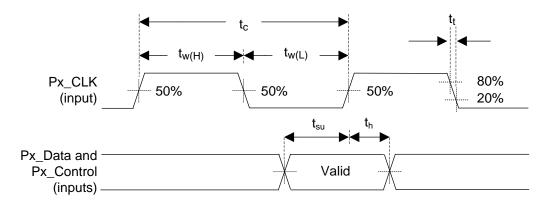

<sup>(3)</sup> Port 1 can be used to support multiple source options for a given product (that is, HDMI, BT656). To do so, the data bus from both source components must be connected to the same port 1 pins and control given to the DLPC6401 to tri-state the inactive source. Tying them together like this causes some signal degradation due to reflections on the tri-stated path.

<sup>(4)</sup> The A, B, and C input data channels of port 1 can be internally swapped for optimum board layout.

<sup>5)</sup> Sources feeding less than the full 10-bits per color component channel should be MSB justified when connected to the DLPC6401 and LSBs tied off to 0. For example, an 8-bit per color input should be connected to bits 9:2 of the corresponding A, B, or C input channel. BT656 are 8 or 10 bits in width. If a BT656-type input is used, the data bits must be MSB justified as with the other types of input sources on either of the A, B, or C data input channels.

| NAME NO. POWER  |         | I/O <sup>(2)</sup> |                | INTERNAL TERMINATION                                                                             | 0114 03407555                                               |                                                                          |  |

|-----------------|---------|--------------------|----------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|--|

|                 |         | POWER              | TYPE           | INTERNAL TERMINATION                                                                             | CLK SYSTEM                                                  | DESCRIPTION                                                              |  |

| P1_C_7          | R19     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 32)                        |  |

| P1_C_6          | R20     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 16)                        |  |

| P1_C_5          | R21     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 8)                         |  |

| P1_C_4          | R22     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 4)                         |  |

| P1_C_3          | T21     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 2)                         |  |

| P1_C_2          | T20     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 1)                         |  |

| P1_C_1          | T19     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 0.5)                       |  |

| P1_C_0          | U22     | VDD33              | I <sub>4</sub> | Includes an internal pulldown                                                                    | P1A_CLK                                                     | Port 1 C channel input pixel data (bit weight 0.25)                      |  |

| PORT 2: FPD-LII | NK COMP | ATIBLE VIDEO       | AND GF         | RAPHICS INPUT <sup>(6)</sup>                                                                     |                                                             |                                                                          |  |

| RCK_IN_P        | Y9      | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | N/A                                                         | Positive differential input signal for clock, FPD-Link receiver          |  |

| RCK_IN_N        | W9      | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | N/A                                                         | Negative differential input signal for clock, FPD-Link receiver          |  |

| RA_IN_P         | AB10    | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | RCK_IN                                                      | Positive differential input signal for data channel A, FPD-Link receiver |  |

| RA_IN_N         | AA10    | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | RCK_IN                                                      | Negative differential input signal for data channel A, FPD-Link receiver |  |

| RB_IN_P         | Y11     | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | RCK_IN                                                      | Positive differential input signal for data channel B, FPD-Link receiver |  |

| RB_IN_N         | W11     | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | RCK_IN                                                      | Negative differential input signal for data channel B, FPD-Link receiver |  |

| RC_IN_P         | AB12    | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | RCK_IN                                                      | Positive differential input signal for data channel C, FPD-Link receiver |  |

| RC_IN_N         | AA12    | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | RCK_IN                                                      | Negative differential input signal for data channel C, FPD-Link receiver |  |

| RD_IN_P         | Y13     | VDD33_FPD          | I <sub>5</sub> | Includes weak internal RCK_IN Positive differential input sign pulldown RCK_IN FPD-Link receiver |                                                             | Positive differential input signal for data channel D, FPD-Link receiver |  |

| RD_IN_N         | W13     | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown RCK_IN RCK_IN Negative differential input                        |                                                             | Negative differential input signal for data channel D, FPD-Link receiver |  |

| RE_IN_P         | AB14    | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | Includes weak internal Positive differential input signal f |                                                                          |  |

| RE_IN_N         | AA14    | VDD33_FPD          | I <sub>5</sub> | Includes weak internal pulldown                                                                  | Includes weak internal PCK IN Negative differential input   |                                                                          |  |

<sup>(6)</sup> Port 2 is a single-channel FPD-Link compatible input interface. FPD-Link is a defacto industry standard FPD interface, which uses the high-bandwidth capabilities of LVDS signaling to serialize video and graphics data down to a couple wires to provide a low-wire count and low-EMI interface. Port 2 supports source rates up to a maximum effective clock of 90 MHz. The port 2 input pixel data must adhere to one of four supported data mapping formats (see Table 2). Given that port 2 inputs contain weak pulldown resistors, they can be left floating when not used.

| PIN <sup>(1)</sup> |     | I/O <sup>(2)</sup> |                | INTERNAL TERMINATION CLK SYSTEM                                    |             |                                                                                                                                                       |  |  |

|--------------------|-----|--------------------|----------------|--------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.           |     | POWER TYPE         |                |                                                                    |             | DESCRIPTION                                                                                                                                           |  |  |

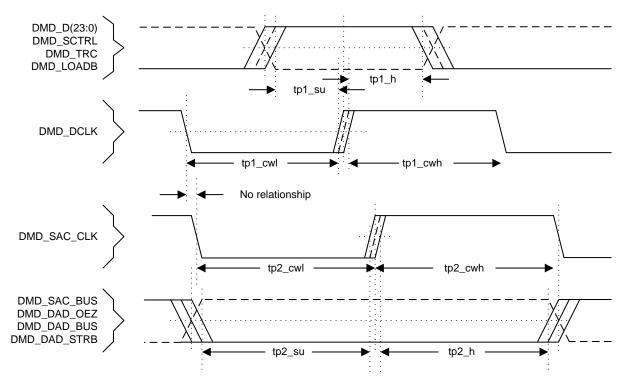

| DMD INTERFACE      |     | l                  |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D0             | A8  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D1             | B8  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D2             | C8  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D3             | D8  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D4             | B11 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D5             | C11 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D6             | D11 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D7             | E11 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D8             | C7  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D9             | B10 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D10            | E7  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D11            | D10 | VDD_DMD            | O <sub>7</sub> |                                                                    | DMD_DCLK    | DMD data pins. DMD data pins are DDR signals that are clocked on both edges of DMD_DCLK. All 24 DMD data signals are use to interface to the DLP4500. |  |  |

| DMD_D12            | A6  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D13            | A12 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D14            | B12 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D15            | C12 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D16            | D12 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D17            | В7  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D18            | A10 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D19            | D7  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D20            | B6  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D21            | E9  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D22            | C10 |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_D23            | C6  |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| DMD_DCLK           | A9  | VDD_DMD            | O <sub>7</sub> |                                                                    | N/A         | DMD data clock (DDR)                                                                                                                                  |  |  |

| DMD_LOADB          | B9  | VDD_DMD            | O <sub>7</sub> |                                                                    | DMD_DCLK    | DMD data load signal (active-low)                                                                                                                     |  |  |

| DMD_SCTRL          | C9  | VDD_DMD            | O <sub>7</sub> |                                                                    | DMD_DCLK    | DMD data serial control signal                                                                                                                        |  |  |

| DMD_TRC            | D9  | VDD_DMD            | O <sub>7</sub> |                                                                    | DMD_DCLK    | DMD data toggle rate control                                                                                                                          |  |  |

| DMD_DRC_BUS        | D5  | VDD_DMD            | O <sub>7</sub> |                                                                    | DMD_SAC_CLK | DMD reset control bus data                                                                                                                            |  |  |

| DMD_DRC_STRB       | C5  | VDD_DMD            | O <sub>7</sub> |                                                                    | DMD_SAC_CLK | DMD reset control bus strobe                                                                                                                          |  |  |

| DMD_DRC_OE         | B5  | VDD_DMD            | O <sub>7</sub> | Requires a 30 to $51-k\Omega$ external pullup resistor to VDD_DMD. | Async       | DMD reset control enable (active low)                                                                                                                 |  |  |

| DMD_SAC_BUS        | D6  | VDD_DMD            | 07             |                                                                    | DMD_SAC_CLK | DMD stepped-address control bus data                                                                                                                  |  |  |

| DMD_SAC_CLK        | A5  | VDD_DMD            | O <sub>7</sub> |                                                                    | N/A         | DMD stepped-address control bus clock                                                                                                                 |  |  |

| DMD_PWR_EN         | G20 | VDD_DMD            | O <sub>2</sub> |                                                                    | Async       | DMD Power Enable control. This signal indicates to an external regulator that the DMD is powered.                                                     |  |  |

| EXRES              | А3  |                    | 0              |                                                                    | Async       | DMD drive strength adjustment precision reference. A ±1% external precision resistor should be connected to this pin.                                 |  |  |

| FLASH INTERFACE    | E   |                    |                |                                                                    |             |                                                                                                                                                       |  |  |

| PM_CS_0            | U3  | VDD33              | O <sub>2</sub> | 7                                                                  | Async       | Reserved for future use. On the PCB, connect to VDD33 through a pullup resistor.                                                                      |  |  |

| PM_CS_1            | U2  | VDD33              | O <sub>2</sub> |                                                                    | Async       | Boot flash (active low). Required for boot memory                                                                                                     |  |  |

| PM_CS_2            | U1  | VDD33              | O <sub>2</sub> |                                                                    | Async       | Reserved for future use. On the PCB, connect to VDD33 through a pullup resistor.                                                                      |  |  |

| PIN <sup>(1)</sup> |             | I/O <sup>(2)</sup> |                |                      | •          |                                     |

|--------------------|-------------|--------------------|----------------|----------------------|------------|-------------------------------------|

| NAME NO.           |             | POWER              | TYPE           | INTERNAL TERMINATION | CLK SYSTEM | DESCRIPTION                         |

| PM_ADDR_22         | V3          | · OWER             | B <sub>2</sub> |                      |            |                                     |

| PM_ADDR_21         | W1          |                    |                |                      |            |                                     |

| PM_ADDR_20         | W2          |                    |                |                      |            |                                     |

| PM_ADDR_19         | Y1          |                    |                |                      |            |                                     |

| PM_ADDR_18         | AB2         |                    |                |                      |            |                                     |

| PM_ADDR_17         | AA3         |                    |                |                      |            |                                     |

| PM_ADDR_16         | 74 Y4       |                    |                |                      |            |                                     |

| PM_ADDR_15         | W5          |                    |                |                      |            |                                     |

| PM_ADDR_14         | AB3         |                    |                |                      |            |                                     |

| PM_ADDR_13         | AA4         |                    |                |                      |            |                                     |

| PM_ADDR_12         | Y5          |                    |                |                      |            |                                     |

| PM_ADDR_11         | W6          | VDD33              | O <sub>2</sub> |                      | Async      | Flash memory address bit            |

| PM_ADDR_10         | AB4         | VDD00              | 02             |                      | Adyllo     | riasii iiciiory addiess bit         |

| PM_ADDR_9          | AA5         |                    |                |                      |            |                                     |

| PM_ADDR_8          | Y6          |                    |                |                      |            |                                     |

| PM_ADDR_7          | W7          |                    |                |                      |            |                                     |

| PM_ADDR_6          | AB5         |                    |                |                      |            |                                     |

| PM_ADDR_5          | AA6         |                    |                |                      |            |                                     |

| PM_ADDR_4          | Y7          |                    |                |                      |            |                                     |

| PM_ADDR_3          | AB6         |                    |                |                      |            |                                     |

| PM_ADDR_2          | W8          |                    |                |                      |            |                                     |

| PM_ADDR_1          | AA7         |                    |                |                      |            |                                     |

| PM_ADDR_0          | AB7         |                    |                |                      |            |                                     |

| PM_WE              | V2          | VDD33              | O <sub>2</sub> |                      | Async      | Write enable (active low)           |

| PM_OE              | U4          | VDD33              | O <sub>2</sub> | Async                |            | Output enable (active low)          |

| PM_BLS_1           | AA8         | VDD33              | O <sub>2</sub> |                      | Async      | Upper byte(15:8) enable             |

| PM_BLS_0           | AB8         | VDD33              | O <sub>2</sub> |                      | Async      | Lower byte(7:0) enable              |

| PM_DATA_15         | M1          | VDD33              | 02             |                      | Asylic     | Lower byte(1.0) enable              |

| PM_DATA_14         | N1          |                    |                |                      |            |                                     |

| PM_DATA_13         | N2          |                    |                |                      |            |                                     |

| PM_DATA_12         | N3          | VDD33              | B <sub>2</sub> |                      | Async      | Data bits, upper byte               |

| PM_DATA_11         | N4          | VDD00              | D <sub>2</sub> |                      | Adyllo     | Bata bits, apper byte               |

| PM_DATA_10         | P1          |                    |                |                      |            |                                     |

| PM_DATA_9          | P2          |                    |                |                      |            |                                     |

| PM_DATA_8          | P3          |                    |                |                      |            |                                     |

| PM_DATA_7          | P4          |                    |                |                      |            |                                     |

| PM_DATA_6          | R2          |                    |                |                      |            |                                     |

| PM_DATA_5          | R3          |                    |                |                      |            |                                     |

| PM_DATA_4          | R4          | VDD33              | B <sub>2</sub> |                      | Async      | Data bits, lower byte               |

| PM_DATA_3          | T1          | VDD00              | 52             |                      | Adyllo     | Data bits, lower byte               |

| PM_DATA_2          | T2          |                    |                |                      |            |                                     |

| PM_DATA_1          | T3          |                    |                |                      |            |                                     |

| PM_DATA_0          | T4          |                    |                |                      |            |                                     |

| LED DRIVER INTE    | _           |                    | ļ              |                      | <u> </u>   |                                     |

| LEDR_PWM           | KFACE<br>K2 |                    |                |                      |            | LED red PWM output enable control   |

| LEDG_PWM           | K3          | VDD33              | 0              |                      | Acuno      | LED green PWM output enable control |

|                    |             | งกกรร              | O <sub>2</sub> |                      | Async      |                                     |

| LEDB_PWM           | K4          |                    |                |                      |            | LED blue PWM output enable control  |

| LEDR_EN            | L3          | VDDaa              |                |                      | A 0: / 0 0 | LED reap PWM output                 |

| LEDG_EN            | L4          | VDD33              | O <sub>2</sub> |                      | Async      | LED green PWM output                |

| LEDB_EN            | K1          |                    |                |                      |            | LED blue PWM output                 |

| PIN <sup>(1)</sup>                |           | I/O <sup>(2)</sup>   |                |                          | ,                                                 |                                                                         |

|-----------------------------------|-----------|----------------------|----------------|--------------------------|---------------------------------------------------|-------------------------------------------------------------------------|

| NAME NO. POWER TYPE               |           | INTERNAL TERMINATION | CLK SYSTEM     | DESCRIPTION              |                                                   |                                                                         |

| PERIPHERAL INTE                   | RFACE     |                      |                |                          |                                                   |                                                                         |

| UART_TXD L19 VDD33 O <sub>2</sub> |           |                      |                | Async                    | Transmit data output. Reserved for debug messages |                                                                         |

| UART_RXD                          | L21       | VDD33                | I <sub>4</sub> |                          | Async                                             | Receive data input. Reserved for debug messages                         |

| UART_RTS                          | M19       | VDD33                | O <sub>2</sub> |                          | Async                                             | Ready to send hardware flow control output. Reserved for debug messages |

| UART_CTS                          | L20       | VDD33                | I <sub>4</sub> |                          | Async                                             | Clear to send hardware flow control input. Reserved for debug messages  |

| GENERAL PURPO                     | SE I/O (0 | GPIO) <sup>(7)</sup> |                |                          |                                                   |                                                                         |

| GPIO_37                           | K21       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_36                           | G1        | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_35                           | H4        | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_34                           | НЗ        | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_33                           | H2        | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_32                           | F22       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_31                           | G19       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_29                           | F20       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_28                           | E22       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_27                           | E21       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_25                           | D22       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_24                           | E20       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_23                           | D21       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_21                           | N20       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_20                           | N19       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_19                           | D18       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_18                           | C18       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_15                           | B19       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_14                           | B18       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_13                           | L2        | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_12                           | M4        | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_11                           | A19       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_10                           | C17       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_06                           | A18       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_05                           | D16       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_04                           | C16       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_03                           | B16       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_02                           | A17       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| GPIO_00                           | C15       | VDD33                | B <sub>2</sub> |                          | Async                                             | None                                                                    |

| OTHER INTERFAC                    | ES        |                      |                |                          | -                                                 |                                                                         |

| FAN_LOCKED                        | B17       | VDD33                | B <sub>2</sub> |                          | Async                                             | Feedback from fan to indicate fan is connected and running              |

| FAN_PWM                           | D15       | VDD33                | B <sub>2</sub> |                          | Async                                             | Fan PWM speed control                                                   |

| BOARD LEVEL TE                    | ST AND    | DEBUG                |                |                          |                                                   | •                                                                       |

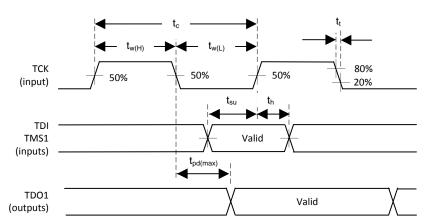

| TDI                               | P18       | VDD33                | I <sub>4</sub> | Includes internal pullup | TCK                                               | JTAG serial data in <sup>(8)</sup>                                      |

| TCK                               | R18       | VDD33                | I <sub>4</sub> | Includes internal pullup | N/A                                               | JTAG serial data clock <sup>(8)</sup>                                   |

| TMS1                              | V15       | VDD33                | I <sub>4</sub> | Includes internal pullup | TCK                                               | JTAG test mode select <sup>(8)</sup>                                    |

| TDO1                              | L18       | VDD33                | O <sub>1</sub> |                          | TCK                                               | JTAG serial data out <sup>(8)</sup>                                     |

|                                   |           |                      |                | +                        |                                                   | +                                                                       |

<sup>(7)</sup> GPIO signals must be configured by software for input, output, bidirectional, or open-drain. Some GPIOs have one or more alternate use modes, which are also software configurable. The reset default for all optional GPIOs is as an input signal. However, any alternate function connected to these GPIO pins with the exception of general-purpose clocks and PWM generation, are reset. An external pullup to the 3.3-V supply is required for each signal configured as open-drain. External pullup or pulldown resistors may be required to ensure stable operation before software is able to configure these ports.

<sup>(8)</sup> All JTAG signals are LVCMOS-compatible.

| PIN <sup>(1)</sup> |     | I/O <sup>(2)</sup> |                     | INTERNAL TERMINATION                                                             | CLK SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                   |  |

|--------------------|-----|--------------------|---------------------|----------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME               | NO. | POWER              | TYPE                | INTERNAL TERMINATION                                                             | CLK STSTEW | DESCRIPTION                                                                                                                                                                                                                                                                   |  |

| TRST               | V17 | VDD33              | I <sub>4</sub><br>H | Includes internal pullup                                                         | Async      | JTAG, RESET (active low). This pin should be pulled high (or left unconnected) when the JTAG interface is in use for boundary scan. Connect this pin to ground otherwise. Failure to tie this pin low during normal operation causes startup and initialization problems. (8) |  |

| RTCK               | G18 | VDD33              | O <sub>2</sub>      |                                                                                  | N/A        | JTAG return clock <sup>(9)</sup>                                                                                                                                                                                                                                              |  |

| ICTSEN             | V6  | VDD33              | I₄<br>H             | Includes internal pull down. External pulldown recommended for added protection. | Async      | IC Tri-State Enable (active high). Asserting high tri-<br>states all outputs except the JTAG interface.                                                                                                                                                                       |  |

(9) For instructions on handling unused pins, see General Handling Guidelines for Unused CMOS-Type Pins.

**Functional Pin Descriptions (Reserved Pins)**

|          | r unctional i in bescriptions (iteserved i ins) |                    |                     |                               |        |                                             |  |  |  |  |  |

|----------|-------------------------------------------------|--------------------|---------------------|-------------------------------|--------|---------------------------------------------|--|--|--|--|--|

| PII      | <b>V</b> <sup>(1)</sup>                         | I/O <sup>(2)</sup> |                     | INTERNAL TERMINATION          | CLK    | DESCRIPTION                                 |  |  |  |  |  |

| NAME     | NO.                                             | POWER              | TYPE                | INTERNAL TERMINATION          | SYSTEM | DESCRIPTION                                 |  |  |  |  |  |

| RESERVED | V7                                              | VDD33              | I <sub>4</sub><br>H | Includes internal pulldown    | N/A    | Connect directly to ground on the PCB.      |  |  |  |  |  |

| RESERVED | N22, M22,<br>P19, P20                           | VDD33              | I <sub>4</sub>      | Includes an internal pulldown | N/A    | - (4)                                       |  |  |  |  |  |

| RESERVED | V16                                             | VDD33              | I <sub>4</sub>      | Includes an internal pullup   | N/A    | Reserved <sup>(1)</sup>                     |  |  |  |  |  |

| RESERVED | D1, J2                                          | VDD33              | I <sub>4</sub>      |                               | N/A    |                                             |  |  |  |  |  |

| RESERVED | F1, F2, G2,<br>G3, G4                           | VDD33              | O <sub>2</sub>      | Includes internal pulldown    | N/A    |                                             |  |  |  |  |  |

| RESERVED | F3, J1, M21                                     | VDD33              | O <sub>2</sub>      |                               | N/A    | Leave these pins unconnected <sup>(1)</sup> |  |  |  |  |  |

| RESERVED | H20, M18,<br>M20                                | VDD33              | O <sub>1</sub>      |                               | N/A    |                                             |  |  |  |  |  |

| RESERVED | H21, H22,<br>J19, J20,<br>J21, J22,<br>K19, K20 | VDD33              | B <sub>2</sub>      | Includes internal pulldown    | N/A    | Reserved <sup>(1)</sup>                     |  |  |  |  |  |

| RESERVED | C1, D2, F4                                      | VDD33              | B <sub>2</sub>      |                               | N/A    |                                             |  |  |  |  |  |

| RESERVED | E3, E2                                          | VDD33              | _                   |                               | Async  | Reserved                                    |  |  |  |  |  |

- For instructions on handling unused pins, see *General Handling Guidelines for Unused CMOS-Type Pins*. I/O Type: I indicates input, O indicates output, B indicates bidirectional, and H indicates hysteresis. See Table 1 for subscript explanation.

Table 1. I/O Type Subscript Definition

|           | I/O                                       | ECO CTRUCTURE                |

|-----------|-------------------------------------------|------------------------------|

| SUBSCRIPT | DESCRIPTION                               | ESD STRUCTURE                |

| 1         | 3.3-V LVCMOS I/O buffer, with 4-mA drive  | ESD diode to VDD33 and GND   |

| 2         | 3.3-V LVCMOS I/O buffer, with 8-mA drive  | ESD diode to VDD33 and GND   |

| 3         | 3.3-V LVCMOS I/O buffer, with 12-mA drive | ESD diode to VDD33 and GND   |

| 4         | 3.3-V LVCMOS receiver                     | ESD diode to VDD33 and GND   |

| 5         | 3.3-V LVDS receiver (FPD-Link I/F)        | ESD diode to VDD33 and GND   |

| 6         | None                                      | N/A                          |

| 7         | 1.9-V LPDDR output buffer (DMD I/F)       | ESD diode to VDD_DMD and GND |

| 8         | 3.3-V I <sup>2</sup> C with 12-mA sink    | ESD diode to VDD33 and GND   |

| 10        | OSC 3.3-V I/O compatible LVCMOS           | ESD diode to VDD33 and GND   |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over recommended operating free-air temperature (unless otherwise noted) (1)

|                  |                         |                                                 | MIN  | MAX | UNIT |

|------------------|-------------------------|-------------------------------------------------|------|-----|------|

| ELEC             | TRICAL                  |                                                 |      |     | •    |

|                  |                         | VDDC (core 1.2-V power)                         | -0.5 | 1.7 |      |

|                  |                         | VDD33 (CMOS I/O)                                | -0.5 | 3.8 |      |

|                  |                         | VDD_DMD (DMD driver power)                      | -0.5 | 2.3 |      |

|                  |                         | VDD12_FPD (FPD-Link LVDS interface 1.2-V power) | -0.5 | 1.7 |      |

|                  | Supply voltage (2)      | VDD33_FPD (FPD-Link LVDS interface 3.3-V power) | -0.5 | 3.8 |      |

|                  |                         | VDD12_PLLD (DDR clock generator – digital)      | -0.5 | 1.7 |      |

|                  |                         | VDD12_PLLM (master clock generator – digital)   | -0.5 | 1.7 |      |

|                  |                         | VDD_18_PLLD (DDR clock generator – analog)      | -0.5 | 2.3 | V    |

|                  |                         | VDD_18_PLLM (master clock generator – analog)   | -0.5 | 2.3 |      |

|                  |                         | OSC (BC1850)                                    | -0.3 | 3.6 |      |

| .,               | In a t a It a a . a (3) | LVCMOS (BT3350)                                 | -0.5 | 3.6 |      |

| VI               | Input voltage (3)       | I <sup>2</sup> C (BT3350)                       | -0.5 | 3.6 |      |

|                  |                         | LVDS (BT3350)                                   | -0.5 | 3.6 |      |

|                  |                         | DMD LPDDR (BC1850)                              | -0.3 | 2.0 |      |

| $V_{O}$          | Output voltage          | LVCMOS (BT3350)                                 | -0.5 | 3.6 |      |

|                  |                         | I <sup>2</sup> C (BT3350)                       | -0.5 | 3.6 |      |

| ENVI             | RONMENTAL               |                                                 | -    |     | •    |

| TJ               | Operating junction te   | mperature                                       | 0    | 115 | °C   |

| T <sub>stg</sub> | Storage temperature     |                                                 | -40  | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

|                    |                         | Machine model (MM)                                                            | ±150  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltage values are with respect to GND.

<sup>(3)</sup> Applies to external input and bidirectional buffers.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                       | I/O <sup>(1)</sup>         | MIN   | NOM | MAX     | UNIT |

|----------------|---------------------------------------|----------------------------|-------|-----|---------|------|

| VDD33          | 3.3-V supply voltage, I/O             |                            | 3.135 | 3.3 | 3.465   | V    |

| VDD_DMD        | 1.9-V supply voltage, I/O             |                            | 1.8   | 1.9 | 2       | V    |

| VDD_18_PLLD    | 1.8-V supply voltage, PLL analog      |                            | 1.71  | 1.8 | 1.89    | V    |

| VDD_18_PLLM    | 1.8-V supply voltage, PLL analog      |                            | 1.71  | 1.8 | 1.89    | V    |

| VDD12          | 1.2-V supply voltage, core logic      |                            | 1.116 | 1.2 | 1.26    | V    |

| VDD12_PLLD     | 1.2-V supply voltage, PLL digital     |                            | 1.116 | 1.2 | 1.26    | V    |

| VDD12_PLLM     | 1.2-V supply voltage, PLL digital     |                            | 1.116 | 1.2 | 1.26    | V    |

|                | Input voltage                         | OSC (10)                   | 0     |     | VDD33   |      |

| V              |                                       | 3.3-V LVCMOS (1, 2, 3, 4)  | 0     |     | VDD33   | V    |

| VI             |                                       | 3.3-V I <sup>2</sup> C (8) | 0     |     | VDD33   | V    |

|                |                                       | 3.3-V LVDS (5)             | 0.6   |     | 2.2     |      |

|                |                                       | 3.3-V LVCMOS (1, 2, 3, 4)  | 0     |     | VDD33   |      |

| Vo             | Output voltage                        | 3.3-V I <sup>2</sup> C (8) | 0     |     | VDD33   | V    |

|                |                                       | 1.9-V LPDDR (7)            | 0     |     | VDD_DMD |      |

| T <sub>A</sub> | Operating ambient temperature range   | See (2)                    | 0     |     | 55      | °C   |

| T <sub>C</sub> | Operating top-center case temperature | See (3)(4)                 | 0     |     | 104     | °C   |

| $T_J$          | Operating junction temperature        |                            | 0     |     | 105     | °C   |

<sup>(1)</sup> The number inside each parenthesis for the I/O refers to the type defined in the I/O type subscript definition section.

# 6.4 Thermal Information<sup>(1)</sup>

|     | THERMAL METRIC <sup>(1)</sup>              | ZFF (BGA) | UNIT |

|-----|--------------------------------------------|-----------|------|

|     |                                            | 419 PINS  |      |

| Ψлт | Junction-to-top characterization parameter | 0.33      | °C/W |

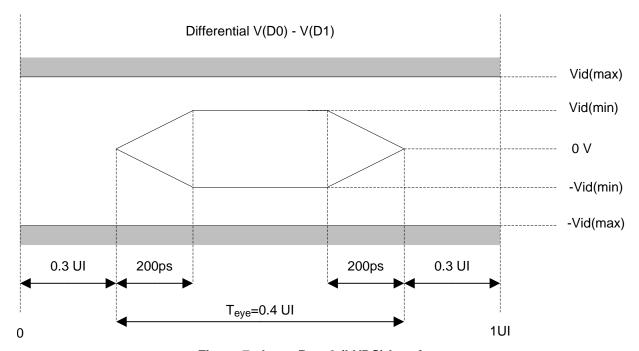

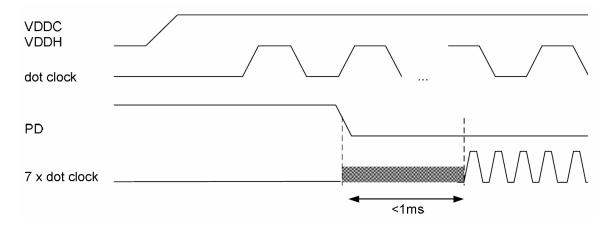

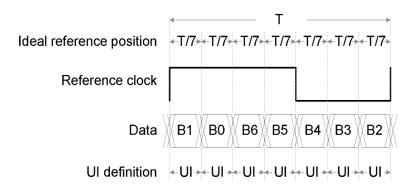

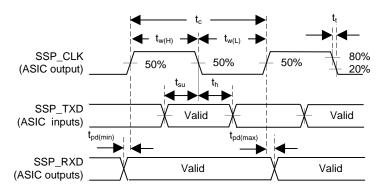

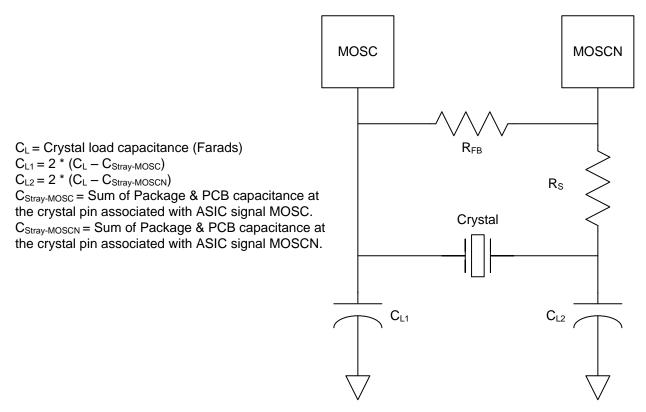

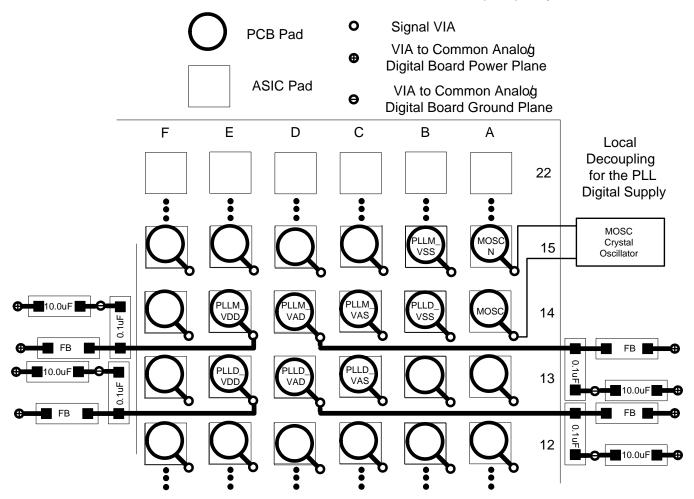

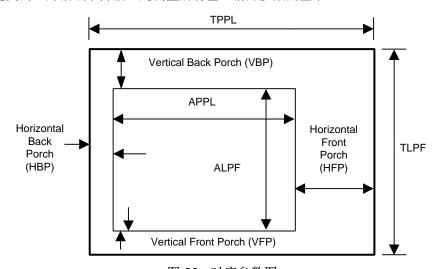

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics Application Report, SPRA953.