Sample &

🖥 Buy

**DLPC300**

Reference

Design

ZHCS244C - JANUARY 2012 - REVISED AUGUST 2015

Support &

Community

2.2

#### DLPC300 适用于 DLP3000 DMD 的 DLP® 数字控制器

Technical

Documents

#### 特性 1

- 用于确保 DLP3000 数字微镜器件 (DMD) 可靠运行

- 多模式,24 位输入端口:

- 支持最高像素时钟为 33.5MHz 的并行 RGB 和 3个输入颜色位深选项:

- 24 位 RGB8888 或者 4:4:4 YCrCb888

- 18 位 RGB666 或者 4:4:4 YCrCb666

- 16 位 RGB565 或者 4:2:2 YCrCb565

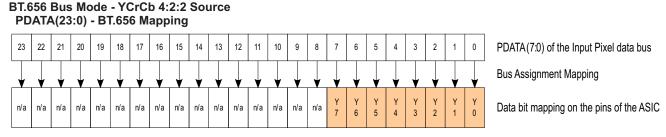

- 支持最高像素时钟为 33.5MHz 的 8 位 BT.656 总线模式

- 支持的输入分辨率包括 608 × 684、864 × 480、 854 × 480 (WVGA)、640 × 480 (VGA)、320 × 240 (QVGA)

- 样式输入模式 •

- 输入数据到微镜的一到一映射

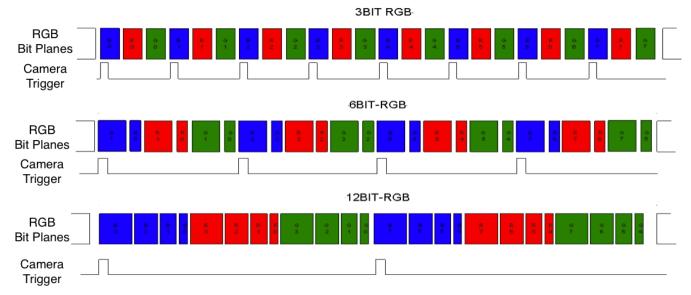

- 1 位二进制模式速率高达 4000Hz

- 高达 120Hz 的最高 8 位灰度样式速率

- 具有像素数据处理功能的视频输入模式

- 支持 1Hz 至 60Hz 的帧速率

- 可编程后期色彩校正 (Degamma)

- 空间-时间复用(抖动显示)

- 自动增益控制

- 颜色空间转换

- 输出触发信号,用于同步摄像机、传感器等外设

- 系统控制:

- 器件配置的 I<sup>2</sup>C 控制

- 高达 3 LED 的可编程电流控制

- 集成的 DMD 复位驱动器控制

- DMD 水平和垂直显示图像抖动

- 低功耗:低于 93mW (典型值)

- 支持外部存储器:

- 166MHz 移动 DDR SDRAM

- 33.3MHz 串行闪存

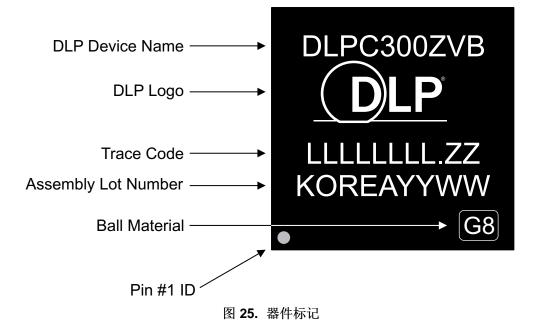

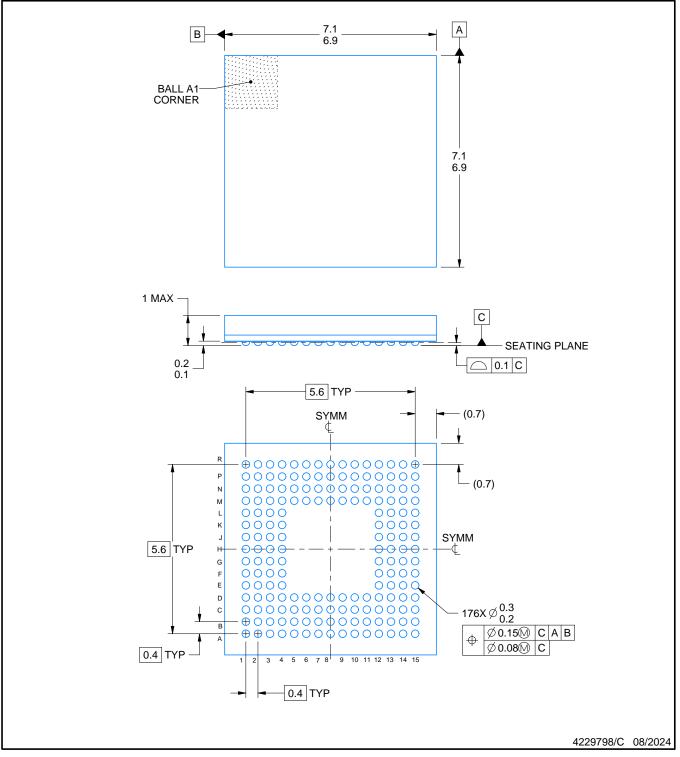

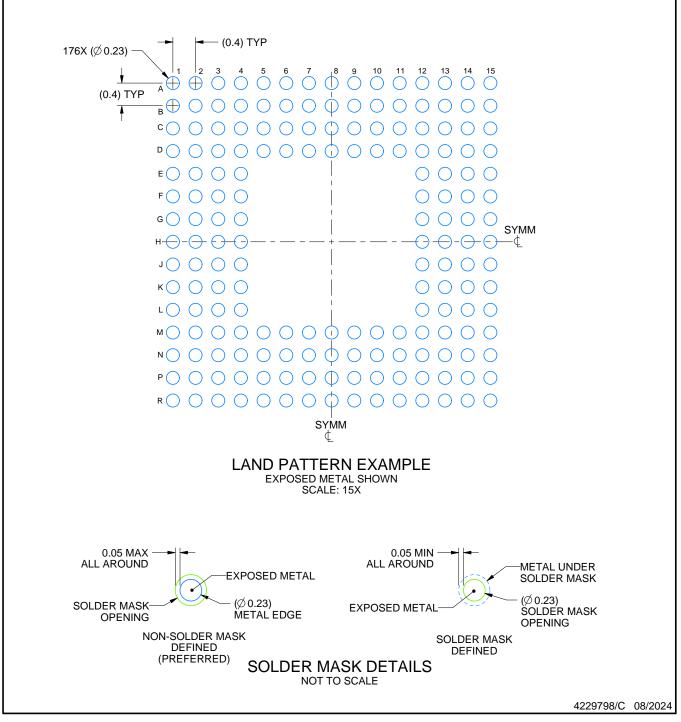

- 176 引脚、7mm×7mm、0.4mm 间距、NFBGA 封装

- 2 应用

- 3D 计量

- 3D 扫描

- 工厂自动化 •

- 指纹识别

- 条纹投影 .

- 工业联机检验

- 机器人视觉

- 立体视觉 ٠

- 化学检测

- 移动传感 ٠

- 光谱分析 •

- 扩增实境 ٠

- 信息叠加 ٠

- 医疗仪器

- 虚拟量规 •

### 3 说明

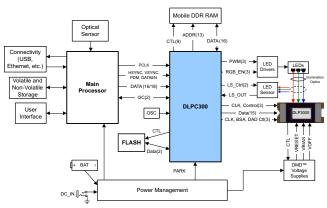

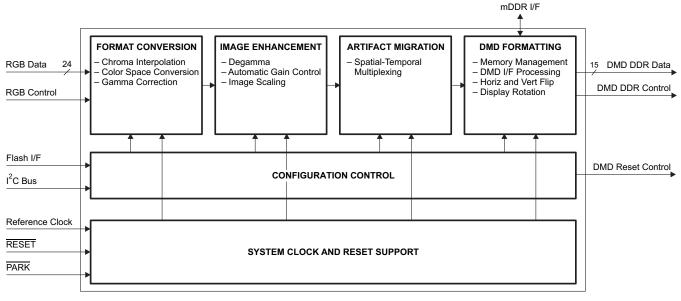

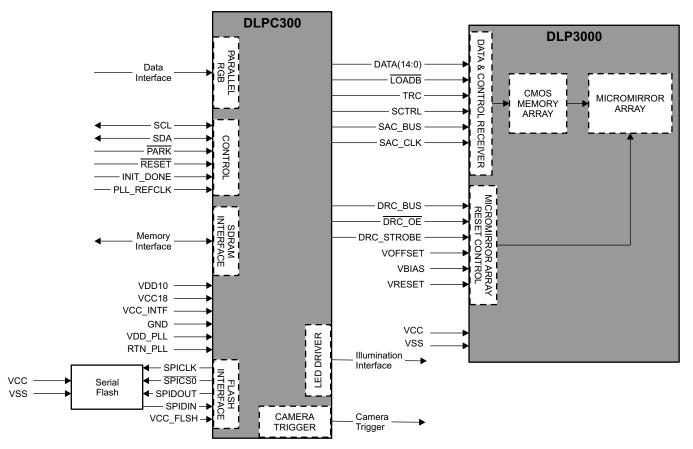

DLPC300 控制器在用户电子设备与 DMD 之间提供一 个方便的多功能接口,支持高速模式速率(最高可达 4kHz, 二进制模式)并提供 LED 控制和数据格式化, 适用于多种输入分辨率。DLPC300 数字控制器属于 DLP3000 芯片组,用于支持 DLP3000 DMD 的可靠运 行。DLPC300还提供输出触发信号,用于将显示的图 案与摄像机、传感器等外设同步。

### 器件信息(1)

| 器件型号    | 封装          | 封装尺寸(标称值)       |

|---------|-------------|-----------------|

| DLPC300 | NFBGA (176) | 7.00mm x 7.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

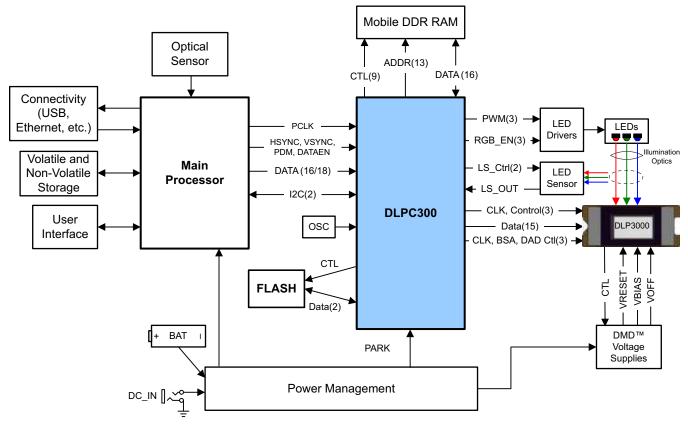

### 典型嵌入式系统框图

Tools &

Software

1 2

3

4

5 6

6.1

6.2

6.3

6.4

特性......1

应用......1

说明......1

修订历史记录 ...... 2 Pin Configuration and Functions ...... 4

Specifications..... 11

Absolute Maximum Ratings ..... 11 ESD Ratings..... 11

Recommended Operating Conditions ...... 11

Thermal Information ..... 12

6.5 I/O Electrical Characteristics ...... 12 6.6 Crystal Port Electrical Characteristics ...... 13 6.7 Power Consumption..... 13 6.8 I<sup>2</sup>C Interface Timing Requirements...... 13 6.9 Parallel Interface Frame Timing Requirements ..... 14 6.10 Parallel Interface General Timing Requirements.. 14 6.11 Parallel I/F Maximum Supported Horizontal Line 6.12 BT.565 I/F General Timing Requirements ...... 15 6.13 Flash Interface Timing Requirements ...... 16 6.14 DMD Interface Timing Requirements...... 16 6.15 Mobile Dual Data Rate (mDDR) Memory Interface Timing Requirements..... 17 6.16 JTAG Interface: I/O Boundary Scan Application Switching Characteristics ...... 17

### 目录

| 7  | Deta | iled Description                          | 22 |

|----|------|-------------------------------------------|----|

|    | 7.1  | Overview                                  | 22 |

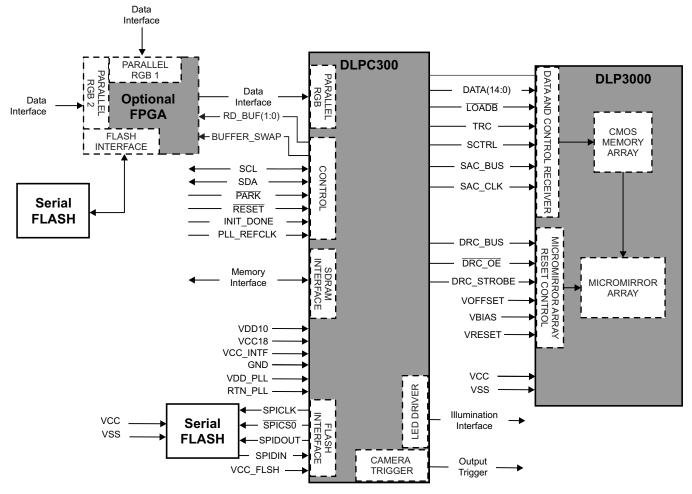

|    | 7.2  | Functional Block Diagram                  | 22 |

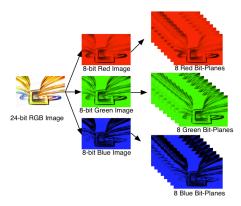

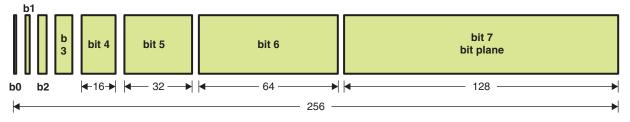

|    | 7.3  | Feature Description                       | 22 |

|    | 7.4  | Device Functional Modes                   | 23 |

| 8  | App  | lication and Implementation               | 26 |

|    | 8.1  | Application Information                   | 26 |

|    | 8.2  | Typical Application                       | 26 |

|    | 8.3  | System Examples                           | 32 |

| 9  | Pow  | er Supply Recommendations                 | 35 |

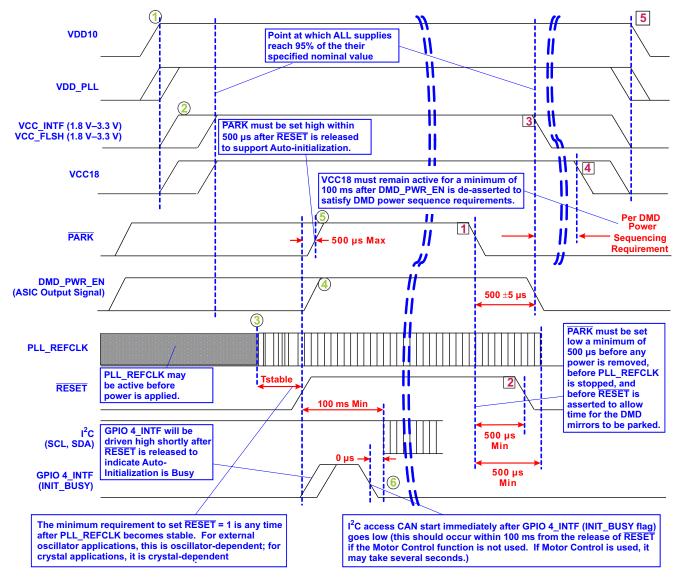

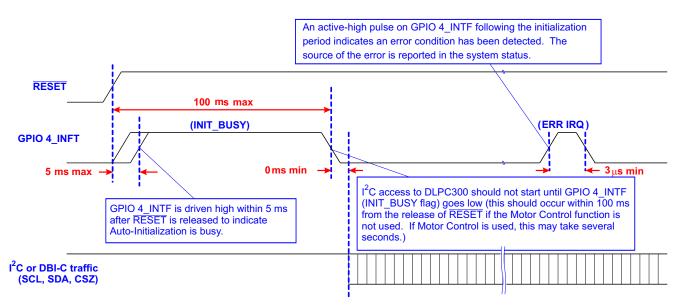

|    | 9.1  | System Power-Up and Power-Down Sequence . | 35 |

|    | 9.2  | System Power I/O State Considerations     | 37 |

|    | 9.3  | Power-Good (PARK) Support                 | 37 |

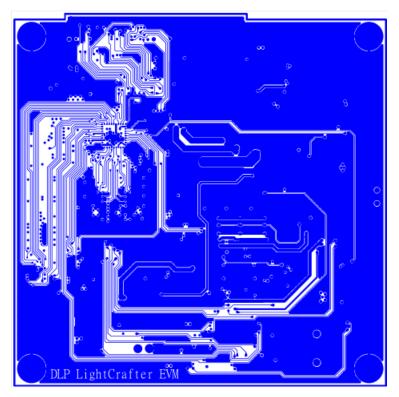

| 10 | Lay  | out                                       | 38 |

|    | 10.1 | Layout Guidelines                         | 38 |

|    | 10.2 | Layout Example                            | 42 |

|    | 10.3 | Thermal Considerations                    | 45 |

| 11 | 器件   | 和文档支持                                     | 46 |

|    | 11.1 | 器件支持                                      | 46 |

|    | 11.2 | 文档支持                                      | 47 |

|    | 11.3 | 社区资源                                      | 47 |

|    | 11.4 | 商标                                        | 47 |

|    | 11.5 | 静电放电警告                                    | 47 |

|    | 11.6 | Glossary                                  | 47 |

| 12 | 机械   | 、封装和可订购信息                                 | 47 |

|    |      |                                           |    |

### 4 修订历史记录

2

注: 之前版本的页码可能与当前版本有所不同。

### Changes from Revision B (July 2013) to Revision C

| • | Added active low to ME | M_RAS, MEM_O | CAS, and MEM | CS in Figure 7 |           |       |      | . 21 |

|---|------------------------|--------------|--------------|----------------|-----------|-------|------|------|

|   | 档支持部分以及机械、             | 封装和可订购信息     | 想部分          |                |           |       |      | 1    |

| • | 己添加 ESD 额定值表,          | 特性 描述部分,     | 器件功能模式,      | 应用和实施部分,       | 电源相关建议部分, | 布局部分, | 器件和文 |      |

### Changes from Revision A (July 2012) to Revision B

| • | 已更改 GPIO4_INF 至 INIT_DONE                               |     |

|---|---------------------------------------------------------|-----|

| • | Deleted "RESERVED0" and "RESERVED1" rows in             | . 4 |

| • | Deleted "d" from Terminal No. R12 in                    | . 4 |

| • | Deleted "RESERVED0" and "RESERVED1" rows in             |     |

| • | Deleted "d" from Terminal No. R12 in                    | . 5 |

| • | Changed pin name GPIO4_INTF to INIT_DONE                | . 5 |

|   | Changed INIT_DONE (formerly GPIO4_INTF) pin description |     |

| • | Deleted "RESERVED0" and "RESERVED1" rows in             | . 6 |

| • | Deleted "d" from Terminal No. R12 in                    |     |

| • | Deleted "RESERVED0" and "RESERVED1" rows in             | . 7 |

| • | Deleted "d" from Terminal No. R12 in                    |     |

| • | Deleted "RESERVED0" and "RESERVED1" rows in             | . 8 |

| • | Deleted "d" from Terminal No. R12 in                    | . 8 |

| • | Deleted "RESERVED0" and "RESERVED1" rows in             | . 9 |

|   |                                                         |     |

www.ti.com.cn

### Page

Page

Copyright © 2012–2015, Texas Instruments Incorporated

### DLPC300 ZHCS244C – JANUARY 2012–REVISED AUGUST 2015

| • | Deleted "d" from Terminal No. R12 in                                     | . 9 |

|---|--------------------------------------------------------------------------|-----|

| • | Changed pin name GPIO0_CMPPWR to CMP_PWR                                 | 9   |

| • | Deleted "RESERVED0" and "RESERVED1" rows in                              | 10  |

| • | Deleted "d" from Terminal No. R12 in                                     | 10  |

| • | Changed pin name JTAGRSTZ to JTAGRST                                     |     |

| • | Changed the "Reserved" row information in                                | 10  |

| • | Changed Note 1 From: "6 total reserved pins" To: "7 total reserved pins" | 10  |

| • | Added video mode non-linear gamma correction description                 | 23  |

| • | Added structured light mode linear gamma description                     | 23  |

| • | Added DDR DRAM devices to Table 6                                        | 29  |

| • | Changed GPIO4_INTF to INIT_DONE                                          | 30  |

| • | Changed GPIO4_INTF to INIT_DONE                                          | 33  |

| • | Changed GPIO4_INTF to INIT_DONE                                          | 36  |

| • | Changed GPIO4 to INIT_DONE                                               | 36  |

### Changes from Original (January 2012) to Revision A

#### Page

| • | 已更改 特性 项,从"支持的输入分辨率包括 608 × 684、854 × 480 (WVGA)、640 × 480 (VGA)、320 × 240 (QVGA)"     |

|---|----------------------------------------------------------------------------------------|

|   | 改为"支持的输入分辨率包括 608 × 684、864 × 480、854 × 480 (WVGA)、640 × 480 (VGA)、320 × 240 (QVGA)" 1 |

| • | Changed unit values from ms to $\mu$ s in $\beta C$ Interface Timing Requirements      |

| • | Changed Equation 1 33                                                                  |

www.ti.com.cn

\_

3

TEXAS INSTRUMENTS

www.ti.com.cn

### 5 Pin Configuration and Functions

|                               | ZVB Package<br>176-Pin NFBGA<br>Bottom View |

|-------------------------------|---------------------------------------------|

| R P N M L K J H G F E D C B A |                                             |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

#### **Pin Functions**

| PIN                            |     | I/O            |                 |        | DE00DIPTION                                                                                                                                                                                                                                                                                                    |  |

|--------------------------------|-----|----------------|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                           | NO. | POWER          | TYPE CLK SYSTEM |        | DESCRIPTION                                                                                                                                                                                                                                                                                                    |  |

| SIGNALS                        |     |                |                 |        |                                                                                                                                                                                                                                                                                                                |  |

| RESET                          | J14 | VCC18          | I <sub>1</sub>  | Async  | DLPC300 power-on reset. Self configuration starts when a low-to-high transition is detected on this pin. All device power and clocks must be stable and within recommended operating conditions before this reset is deasserted. Note that the following 7 signals are high-impedance while RESET is asserted: |  |

|                                |     |                |                 |        | DMD_PWR_EN, LEDDVR_ON, LED_SEL_0,<br>LED_SEL_1, SPICLK, SPIDOUT, and SPICS0<br>External pullups/pulldowns should be added as needed<br>to these signals to avoid floating inputs where these<br>signals are driven.                                                                                            |  |

| PARK                           | B8  | VCC_ INTF      | I <sub>3</sub>  | Async  | DMD park control (active-low). Is set high to enable normal operation. PARK must be set high within 500 µs after releasing RESET. PARK must be set low a minimum of 500 µs before any power is to be removed from the DLPC300 or DLP3000. See <i>System Power-Up/Power-Down Sequence</i> for more details.     |  |

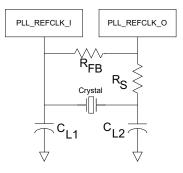

| PLL_REFCLK_I                   | K15 | VCC18 (filter) | I <sub>4</sub>  | N/A    | Reference clock crystal input. If an external oscillator is used in place of a crystal, then this pin should be used as the oscillator input.                                                                                                                                                                  |  |

| PLL_REFCLK_O                   | J15 | VCC18 (filter) | O <sub>14</sub> | N/A    | Reference clock crystal return. If an external oscillator is used<br>in place of a crystal, then this pin should be left unconnected<br>(floating).                                                                                                                                                            |  |

| FLASH INTERFACE <sup>(1)</sup> |     |                |                 |        |                                                                                                                                                                                                                                                                                                                |  |

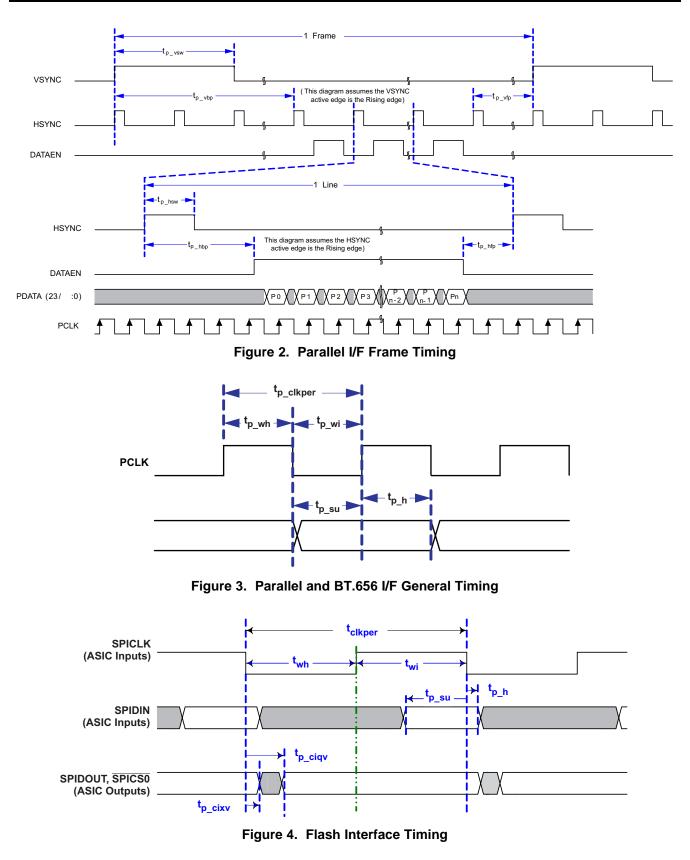

| SPICLK                         | A4  | VCC_FLSH       | O <sub>24</sub> | N/A    | SPI master clock output                                                                                                                                                                                                                                                                                        |  |

| SPIDIN                         | B4  | VCC_FLSH       | I <sub>2</sub>  | SPICLK | Serial data input from the external SPI slave FLASH device                                                                                                                                                                                                                                                     |  |

| SPICS0                         | A5  | VCC_FLSH       | O <sub>24</sub> | SPICLK | SPI master chip select 0 output. Active-low                                                                                                                                                                                                                                                                    |  |

| RESERVED                       | C6  | VCC_FLSH       | O <sub>24</sub> | SPICLK | Not used. Reserved for future use. Should be left unconnected                                                                                                                                                                                                                                                  |  |

| SPIDOUT                        | C5  | VCC_FLSH       | O <sub>24</sub> | SPICLK | Serial data output to the external SPI slave flash device. This<br>pin sends address and control information as well as data when<br>programming.                                                                                                                                                              |  |

(1) Each device connected to the SPI bus must operate from VCC\_FLSH.

#### **Pin Functions (continued)**

| PIN                  |     | I/O       | I/O             |            |                                                              |                                                                                                                                     |

|----------------------|-----|-----------|-----------------|------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO. | POWER     | TYPE            | CLK SYSTEM | DESC                                                         | RIPTION                                                                                                                             |

| CONTROL              |     |           |                 |            |                                                              |                                                                                                                                     |

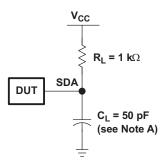

| SCL                  | A10 | VCC_ INTF | B <sub>38</sub> | N/A        | pullup is required. No I2                                    | pen-drain signal. An external<br>C <u>activity</u> is <u>permitted</u> for a<br>r PARK and RESET are set                            |

| SDA                  | C10 | VCC_ INTF | B <sub>38</sub> | SCL        | I <sup>2</sup> C data. Bidirectional, or pullup is required. | pen-drain signal. An external                                                                                                       |

| INIT_DONE            | C9  | VCC_ INTF | B <sub>34</sub> | Async      | complete, which is when<br>then low following release        | ate when auto-initialization is<br>INIT_DONE transitions high<br>of RESET. INIT_DONE also<br>or condition in the form of a<br>flag. |

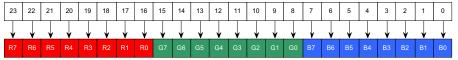

| PARALLEL RGB INTERFA | CE  |           |                 | •          | PARALLEL RGB MODE                                            | BT.656 I/F MODE                                                                                                                     |

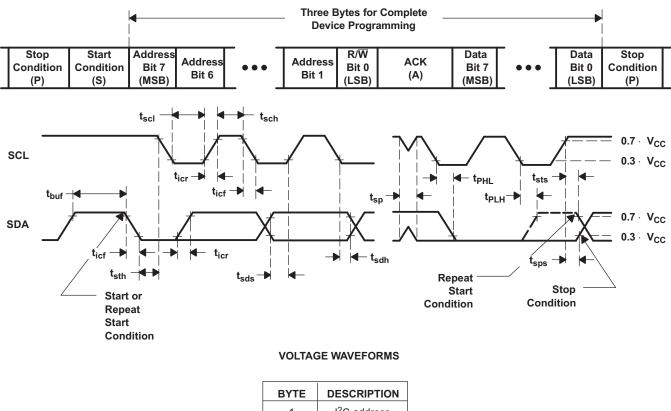

| PCLK                 | D13 | VCC_ INTF | I <sub>3</sub>  | N/A        | Pixel clock <sup>(2)</sup>                                   | Pixel clock <sup>(2)</sup>                                                                                                          |

| PDM                  | H15 | VCC_ INTF | B34             | ASYNC      | Not used, pulldown through an external resistor.             | Not used, pulldown through an external resistor.                                                                                    |

| VSYNC                | H14 | VCC_ INTF | I <sub>3</sub>  | ASYNC      | VSync <sup>(3)</sup>                                         | Unused <sup>(4)</sup>                                                                                                               |

| HSYNC                | H13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | HSync <sup>(3)</sup>                                         | Unused <sup>(4)</sup>                                                                                                               |

| DATEN                | G15 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data valid <sup>(2)</sup>                                    | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[0]             | G14 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data0 <sup>(5)</sup>                                         | Data0 <sup>(5)</sup>                                                                                                                |

| PDATA[1]             | G13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data1 <sup>(5)</sup>                                         | Data1 <sup>(5)</sup>                                                                                                                |

| PDATA[2]             | F15 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data2 <sup>(5)</sup>                                         | Data2 <sup>(5)</sup>                                                                                                                |

| PDATA[3]             | F14 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data3 <sup>(5)</sup>                                         | Data3 <sup>(5)</sup>                                                                                                                |

| PDATA[4]             | F13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data4 <sup>(5)</sup>                                         | Data4 <sup>(5)</sup>                                                                                                                |

| PDATA[5]             | E15 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data5 <sup>(5)</sup>                                         | Data5 <sup>(5)</sup>                                                                                                                |

| PDATA[6]             | E14 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data6 <sup>(5)</sup>                                         | Data6 <sup>(5)</sup>                                                                                                                |

| PDATA[7]             | E13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data7 <sup>(5)</sup>                                         | Data7 <sup>(5)</sup>                                                                                                                |

| PDATA[8]             | D15 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data8 <sup>(5)</sup>                                         | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[9]             | D14 | VCC_ INTF | l <sub>3</sub>  | PCLK       | Data9 <sup>(5)</sup>                                         | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[10]            | C15 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data10 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[11]            | C14 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data11 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[12]            | C13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data12 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[13]            | B15 | VCC_ INTF | l <sub>3</sub>  | PCLK       | Data13 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[14]            | B14 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data14 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[15]            | A15 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data15 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[16]            | A14 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data16 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[17]            | B13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data17 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[18]            | A13 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data18 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[19]            | C12 | VCC_ INTF | l <sub>3</sub>  | PCLK       | Data19 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[20]            | B12 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data20 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[21]            | A12 | VCC_ INTF | l <sub>3</sub>  | PCLK       | Data21 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[22]            | C11 | VCC_ INTF | l <sub>3</sub>  | PCLK       | Data22 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

| PDATA[23]            | B11 | VCC_ INTF | I <sub>3</sub>  | PCLK       | Data23 <sup>(5)</sup>                                        | Unused <sup>(4)</sup>                                                                                                               |

Pixel clock capture edge is software programmable. VSYNC, HSYNC and data valid polarity is software programmable. Unused inputs should be pulled down to ground through an external resistor. PDATA[23:0] bus mapping is pixel-format and source-mode dependent. See later sections for details. (2) (3) (4) (5)

DLPC300 ZHCS244C – JANUARY 2012 – REVISED AUGUST 2015 Texas Instruments

www.ti.com.cn

### Pin Functions (continued)

| PIN           |     | I/O        | I/O             |             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------|-----|------------|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME          | NO. | POWER TYPE |                 | CLK STSTEM  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD INTERFACE |     |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D0        | M15 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D1        | N14 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D2        | M14 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D3        | N15 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D4        | P13 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D5        | P14 |            |                 |             | DND data site DND data site and data data sate                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMD_D6        | P15 |            |                 |             | DMD data pins. DMD data pins are double data rate (DDR) signals that are clocked on both edges of                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| DMD_D7        | R15 | VCC18      | O <sub>58</sub> | DMD_DCLK    | DMD_DCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| DMD_D8        | R12 |            |                 |             | All 15 DMD data signals are use to interface to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| DMD_D9        | N11 |            |                 |             | DLP3000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DMD_D10       | P11 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D11       | R11 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D12       | N10 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D13       | P10 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_D14       | R10 |            |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_DCLK      | N13 | VCC18      | O <sub>58</sub> | N/A         | DMD data clock (DDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DMD_LOADB     | R13 | VCC18      | O <sub>58</sub> | DMD_DCLK    | DMD data load signal (active-low). This signal requires an<br>external pullup to VCC18.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DMD_SCTRL     | R14 | VCC18      | O <sub>58</sub> | DMD_DCLK    | DMD data serial control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMD_TRC       | P12 | VCC18      | O <sub>58</sub> | DMD_DCLK    | DMD data toggle rate control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| DMD_DRC_BUS   | L13 | VCC18      | O <sub>58</sub> | DMD_SAC_CLK | DMD reset control bus data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| DMD_DRC_STRB  | K13 | VCC18      | O <sub>58</sub> | DMD_SAC_CLK | DMD reset control bus strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| DMD_DRC_OE    | M13 | VCC18      | O <sub>58</sub> | Async       | DMD reset control enable (active-low). This signal requires an external pullup to VCC18.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DMD_SAC_BUS   | L15 | VCC18      | O <sub>58</sub> | DMD_SAC_CLK | DMD stepped-address control bus data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DMD_SAC_CLK   | L14 | VCC18      | O <sub>58</sub> | N/A         | DMD stepped-address control bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| DMD_PWR_EN    | K14 | VCC18      | O <sub>14</sub> | Async       | DMD power regulator enable (active-high). This is an active-<br>high output that should be used to control DMD V <sub>OFFSET</sub> , V <sub>BIAS</sub> ,<br>and V <sub>RESET</sub> voltages. DMD_PWR_EN is driven high as a result<br>of the PARK input signal being set high. However,<br>DMD_PWR_EN is held high for 500 $\mu$ s after the PARK input<br>signal is set low before it is driven low. A weak external<br>pulldown resistor is recommended to keep this signal at a<br>known state during power-up reset. |  |

### Pin Functions (continued)

| PIN                  |       | I/O   | I/O             | CLK SYSTEM  | DESCRIPTION                                                |

|----------------------|-------|-------|-----------------|-------------|------------------------------------------------------------|

| NAME                 | NO.   | POWER | TYPE            | CLK STSTEW  | DESCRIPTION                                                |

| SDRAM INTERFACE      | · · · |       |                 |             |                                                            |

| MEM_CLK_P            | D1    | VCC18 | O <sub>74</sub> | N/A         | mDDR memory differential memory cleak                      |

| MEM_CLK_N            | E1    | VCC18 | O <sub>74</sub> | N/A         | <ul> <li>mDDR memory, differential memory clock</li> </ul> |

| MEM_A0               | P1    |       |                 |             |                                                            |

| MEM_A1               | R3    |       |                 |             |                                                            |

| MEM_A2               | R1    |       |                 |             |                                                            |

| MEM_A3               | R2    |       |                 |             |                                                            |

| MEM_A4               | A1    |       |                 |             |                                                            |

| MEM_A5               | B1    |       |                 |             |                                                            |

| MEM_A6               | A2    | VCC18 | O <sub>64</sub> | MEM_CLK     | mDDR memory, multiplexed row and column address            |

| MEM_A7               | B2    |       |                 |             |                                                            |

| MEM_A8               | D2    |       |                 |             |                                                            |

| MEM_A9               | A3    |       |                 |             |                                                            |

| MEM_A10              | P2    |       |                 |             |                                                            |

| MEM_A11              | B3    |       |                 |             |                                                            |

| MEM_A12              | D3    |       |                 |             |                                                            |

| MEM_BA0              | M3    |       | _               |             |                                                            |

| MEM_BA1              | P3    | VCC18 | O <sub>64</sub> | MEM_CLK     | mDDR memory, bank select                                   |

| MEM_RAS              | P4    | VCC18 | O <sub>64</sub> | MEM_CLK     | mDDR memory, row address strobe (active-low)               |

| MEM_CAS              | R4    | VCC18 | O <sub>64</sub> | MEM_CLK     | mDDR memory, column address strobe (active-low)            |

| MEM_WE               | R5    | VCC18 | O <sub>64</sub> | MEM_CLK     | mDDR memory, write enable (active-low)                     |

| <br>MEM_CS           | J3    | VCC18 | O <sub>64</sub> | <br>MEM_CLK | mDDR memory, chip select (active-low)                      |

| MEM_CKE              | C1    | VCC18 | O <sub>64</sub> | <br>MEM_CLK | mDDR memory, clock enable (active-high)                    |

| <br>MEM_LDQS         | J2    | VCC18 | B <sub>64</sub> | <br>N/A     | mDDR memory, lower byte, R/W data strobe                   |

| MEM_LDM              | J1    | VCC18 | O <sub>64</sub> | MEM_LDQS    | mDDR memory, lower byte, write data mask                   |

| MEM_UDQS             | G1    | VCC18 | B <sub>64</sub> | N/A         | mDDR memory, upper byte, R/W data strobe                   |

| MEM_UDM              | H1    | VCC18 | O <sub>64</sub> | MEM_UDQS    | mDDR memory, upper byte, write data mask                   |

| MEM_DQ0              | N1    |       |                 |             |                                                            |

| MEM_DQ1              | M2    |       |                 |             |                                                            |

| MEM_DQ2              | M1    |       |                 |             |                                                            |

| MEM_DQ3              | L3    |       |                 |             |                                                            |

| MEM_DQ4              | L2    | VCC18 | B <sub>64</sub> | MEM_LDQS    | mDDR memory, lower byte, bidirectional R/W data            |

| MEM_DQ5              | K2    |       |                 |             |                                                            |

| MEM_DQ6              | L1    |       |                 |             |                                                            |

| MEM_DQ7              | K1    |       |                 |             |                                                            |

| MEM_DQ8              | H2    |       | -               |             |                                                            |

| MEM_DQ9              | G2    |       |                 |             |                                                            |

| MEM_DQ10             | H3    |       |                 |             |                                                            |

| MEM_DQ10             | F3    |       |                 |             |                                                            |

| MEM_DQ12             | F3    | VCC18 | B <sub>64</sub> | MEM_UDQS    | mDDR memory, upper byte, bidirectional R/W data            |

| MEM_DQ12             | E2    |       |                 |             |                                                            |

| MEM_DQ13<br>MEM_DQ14 | F2    |       |                 |             |                                                            |

| MEM_DQ14<br>MEM_DQ15 | E3    |       |                 |             |                                                            |

DLPC300 ZHCS244C – JANUARY 2012 – REVISED AUGUST 2015

#### TEXAS INSTRUMENTS

www.ti.com.cn

### Pin Functions (continued)

| PIN                  |     | 1/0      | I/O             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|-----|----------|-----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO. | POWER    | TYPE            | CLK SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LED DRIVER INTERFACE |     |          |                 | I          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RPWM                 | N8  | VCC18    | O <sub>14</sub> | Async      | Red LED PWM signal used to control the LED current <sup>(6)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPWM                 | P9  | VCC18    | O <sub>14</sub> | Async      | Green LED PWM signal used to control the LED current <sup>(6)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BPWM                 | R8  | VCC18    | O <sub>14</sub> | Async      | Blue LED PWM signal used to control the LED current <sup>(6)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LED_SEL_0            | R6  | VCC18    | O <sub>14</sub> | Async      | LED enable SELECT. Controlled by DMD sequence<br>timing.<br>LED_SEL(1:0) Selected LED<br>00 None<br>01 Red                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LED_SEL_1            | N6  |          | - 14            |            | 01 Red<br>10 Green<br>11 Blue<br>A decode circuit is required to decode the selected LED<br>enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LEDDRV_ON            | P7  | VCC18    | O <sub>14</sub> | Async      | LED driver master enable. Active-high output control to external<br>LED driver logic. This signal is driven high 100 ms after<br>LED_ENABLE is driven high. Driven low immediately when<br>either LED_ENABLE or PARK is driven low.                                                                                                                                                                                                                                                                                                                           |

| LED_ENABLE           | A11 | VCC_INTF | l <sub>3</sub>  | Async      | LED enable (active-high input). A logic low on this signal forces<br>LEDDRV_ON low and LED_SEL(1:0) = 00b. These signals are<br>enabled 100 ms after LED_ENABLE transitions from low to<br>high.                                                                                                                                                                                                                                                                                                                                                              |

| RED_EN               | B5  |          |                 |            | When not used with an optional FPGA, this signal should be connected to the RED LED enable circuit. When RED_EN is high, the red LED is enabled. When RED_EN is low, the red LED is disabled. When used with the optional FPGA, this signal should be pulled down to ground through an external resistor. This signal is configured as output and driven low when the DLPR300 serial flash PROM is loaded by the DLPC300, but the signal is not enabled. To enable this output, a write to I <sup>2</sup> C LED Enable and Buffer Control register.           |

| GREEN_EN             | Α7  | VCC18    | B <sub>18</sub> | Async      | When not used with an optional FPGA, this signal should be connected to the green LED enable circuit. When GREEN_EN is high, the green LED is enabled. When GREEN_EN is low, the green LED is disabled. When used with the optional FPGA, this signal should be pulled down to ground through an external resistor. This signal is configured as output and driven low when the DLPR300 serial flash PROM is loaded by the DLPC300, but the signal is not enabled. To enable this output, a write to I <sup>2</sup> C LED Enable and Buffer Control register. |

| BLUE_EN              | C8  |          |                 |            | When not used with an optional FPGA, this signal should be connected to the blue LED enable circuit. When BLUE_EN is high, the blue LED is enabled. When BLUE_EN is low, the blue LED is disabled. When used with the optional FPGA, this signal should be pulled down to ground through an external resistor. This signal is configured as output and driven low when the DLPR300 serial flash PROM is loaded by the DLPC300, but the signal is not enabled. To enable this output, a write to I <sup>2</sup> C LED Enable and Buffer Control register.      |

(6) All LED PWM signals are forced high when LEDDRV\_ON = 0, SW LED control is disabled, or the sequence stops.

### Pin Functions (continued)

| PIN                    |            | I/O            | I/O             | CLK SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|------------|----------------|-----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NO.        | POWER          | TYPE            | CLK STSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WHITE POINT CORRECTION | I LIGHT SI | ENSOR I/F      |                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CMP_OUT                | A6         | VCC18          | I <sub>1</sub>  | Async      | Successive approximation ADC comparator output (DLPC300 input). Assumes a successive approximation ADC is implemented with a light sensor and/or thermocouple feeding one input of an external comparator and the other side of the comparator driven from the DLPC300 CMP_PWM pin. If not used, this signal should be pulled down to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CMP_PWM                | B7         | VCC18          | O <sub>14</sub> | Async      | Successive approximation comparator pulse-duration<br>modulation input. Supplies a PWM signal to drive the<br>successive approximation ADC comparator used in light-to-<br>voltage light sensor applications. Should be left unconnected if<br>this function is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CMP_PWR                | P5         | VCC18          | B <sub>14</sub> | Async      | Power control signal for the WPC light sensor and other analog<br>support circuits using the DLPC300 ADC. Alternatively, it<br>provides general-purpose I/O to the WPC microprocessor<br>internal to the DLPC300. Should be left unconnected if not<br>used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TRIGGER CONTROL        |            |                |                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUTPUT_TRIGGER         | N9         | VCC18          | B <sub>18</sub> | Async      | Trigger output. Indicates that a pattern or image is displayed on<br>the screen and is ready to be captured. With an optional FPGA,<br>this signal is connected to the FPGA trigger input. This signal is<br>configured as output and driven low when the DLPR300 serial<br>flash PROM is loaded by the DLPC300, but the signal is not<br>enabled. To enable this output, a write to I <sup>2</sup> C LED Enable and<br>Buffer Control register. If not used, this signal should be pulled<br>down to ground through an external resistor.                                                                                                                                                                                                                                                                                             |

| PATTERN CONTROL        |            |                |                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PATTERN_INVERT         | C7         | VCC18          | B <sub>18</sub> | Async      | Inverts the current 1-bit pattern held in the DLPC300 buffer.<br>When used with an optional FPGA, this signal should be<br>connected to DMC_TRC of the FPGA. This signal is configured<br>as output and driven low when the DLPR300 serial flash PROM<br>is loaded by the DLPC300, but the signal is not enabled. To<br>enable this output, a write to I <sup>2</sup> C LED Enable and Buffer<br>Control register. If not used, this signal should be pulled down<br>to ground through an external resistor.                                                                                                                                                                                                                                                                                                                           |

| OPTIONAL FPGA BUFFER   | ANAGEM     | ENT INTERFACES |                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RD_BUF0                | B6         |                |                 |            | When not used with an optional FPGA, this signal should be<br>pulled down to ground through an external resistor. When used<br>with an optional FPGA, this signal should be connected to<br>RD_PTR_SDC[0] of the FPGA. RD_BUFF1 and RD_BUFF0<br>indicate to the FPGA one of the four buffers currently in use.<br>This signal is configured as output and driven low when the<br>DLPR300 serial flash PROM is loaded by the DLPC300, but<br>the signal is not enabled. To enable this output, a write to I <sup>2</sup> C<br>LED Enable and Buffer Control register.                                                                                                                                                                                                                                                                   |

| RD_BUF1/I2C_ADDR_SEL   | R9         | VCC18          | B <sub>18</sub> | Async      | This signal is sampled when RESET is deasserted to choose<br>between two predefined 7-bit I <sup>2</sup> C slave addresses. If<br>I2C_ADDR_SEL signal is pulled-low, then the DLPC300's I <sup>2</sup> C<br>slave address is 1Bh. If I2C_ADDR_SEL signal is pulled-high,<br>then the DLPC300's I <sup>2</sup> C slave address is 1Dh. When used with<br>an optional FPGA, this signal should be connected to<br>RD_PTR_SDC[1] of the FPGA. RD_BUFF1 and RD_BUFF0<br>indicate to the FPGA one of the four buffers currently in use.<br>This signal is set to input upon deassertion of RESET and<br>configured as output and driven low when the DLPR300 serial<br>flash PROM is loaded by the DLPC300, but the signal is not<br>enabled. To enable this output, a write to I <sup>2</sup> C LED Enable and<br>Buffer Control register. |

| BUFFER_SWAP            | A8         |                |                 |            | When not used with an optional FPGA, this signal should be<br>pulled down to ground through an external resistor. When used<br>with an optional FPGA, this signal should be connected to<br>BUFF_SWAP_SEQ of the FPGA. BUFFER_SWAP indicates to<br>the FPGA when to advance the buffer. This signal is configured<br>as output and driven low when the DLPR300 serial flash PROM<br>is loaded by the DLPC300, but the signal is not enabled. To<br>enable this output, a write to I <sup>2</sup> C LED Enable and Buffer<br>Control register.                                                                                                                                                                                                                                                                                          |

DLPC300 ZHCS244C – JANUARY 2012 – REVISED AUGUST 2015

www.ti.com.cn

ISTRUMENTS

**EXAS**

### Pin Functions (continued)

| PIN                    |      | I/O      | I/O             | CLK SYSTEM | DESCRIPTION                                                                                                                                                           |  |  |

|------------------------|------|----------|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                   | NO.  | POWER    | TYPE CLK SYSTEM |            | DESCRIPTION                                                                                                                                                           |  |  |

| TEST_EN                | A9   | VCC_INTF | l <sub>3</sub>  | N/A        | Reserved for test. Should be connected directly to ground on the PCB for normal operation. Includes weak internal pulldown                                            |  |  |

| BOARD LEVEL TEST AND D | EBUG |          |                 |            |                                                                                                                                                                       |  |  |

| JTAGTDI                | P6   | VCC18    | l <sub>1</sub>  | JTAGTCK    | JTAG, serial data in. Includes weak internal pullup                                                                                                                   |  |  |

| JTAGTCK                | N5   | VCC18    | l <sub>1</sub>  | N/A        | JTAG, serial data clock. Includes weak internal pullup                                                                                                                |  |  |

| JTAGTMS                | N7   | VCC18    | l <sub>1</sub>  | JTAGTCK    | JTAG, test mode select. Includes weak internal pullup                                                                                                                 |  |  |

| JTAGTDO                | R7   | VCC18    | I <sub>14</sub> | JTAGTCK    | JTAG, serial data out                                                                                                                                                 |  |  |

| JTAGRST                | P8   | VCC18    | I <sub>1</sub>  | ASYNC      | JTAG, RESET (active-low). Includes weak internal pullup. This signal must be tied to ground, through an external 15-k $\Omega$ or less resistor for normal operation. |  |  |

### Pin Functions — Power and Ground<sup>(1)</sup>

| POWER GROUP | PIN NUMBERS                                            | DESCRIPTION                                                                                                                                    |

|-------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

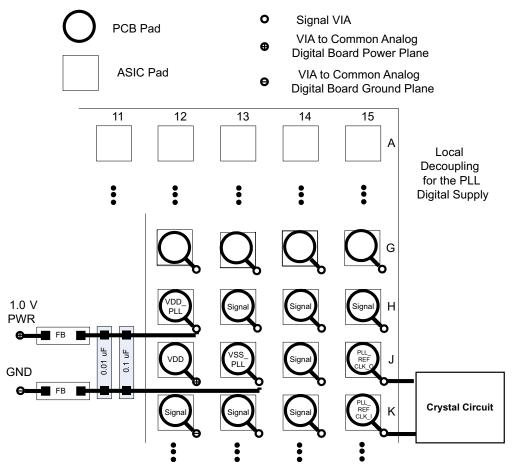

| VDD10       | D5, D9, F4, F12, J4, J12, M6,<br>M8, M11               | 1-V core logic power supply (9)                                                                                                                |

| VDD_PLL     | H12                                                    | 1-V power supply for the internal PLL (1)                                                                                                      |

| VCC18       | C4, D8, E4, G3, K3, K12, L4,<br>M5, M9, M12, N4, N12   | 1.8-V power supply for all I/O other than the host/ video interface and the SPI flash buses (12)                                               |

| VCC_FLSH    | D6                                                     | 1.8- , 2.5- or 3.3-V power supply for SPI flash bus I/O (1)                                                                                    |

| VCC_INTF    | D11, E12                                               | 1.8- , 2.5- or 3.3-V power supply for all I/Os on the host/video interface (includes $l^2C,$ PDATA, video syncs, PARK and LED_ENABLE pins) (2) |

| GND         | D4, D7, D10, D12, G4, G12,<br>H4, K4, L12, M4, M7, M10 | Common ground (12)                                                                                                                             |

| RTN_PLL     | J13                                                    | Analog ground return for the PLL (This should be connected to the common ground GND through a ferrite (1)                                      |

| Reserved    | B9, C2, C3, C6, N2, N3                                 |                                                                                                                                                |

| Reserved    | B10                                                    | This pin must be pulled up to VCC_INTF                                                                                                         |

(1) 132 total signal I/O pins, 38 total power/ground pins, 7 total reserved pins

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted).<sup>(1)</sup>

|                                   |                                           |   | MIN  | MAX  | UNIT |

|-----------------------------------|-------------------------------------------|---|------|------|------|

| ELECTRICAL                        |                                           |   |      |      |      |

|                                   | VDD10                                     |   | -0.5 | 1.32 | V    |

|                                   | VDD_PLL                                   |   | -0.5 | 1.32 | V    |

| Valtage explicit to $(2)$         | VCC18                                     |   | -0.5 | 2.75 | V    |

| Voltage applied to <sup>(2)</sup> | VCC_FLSH                                  |   | -0.5 | 3.60 | V    |

|                                   | VCC_INTF                                  |   | -0.5 | 3.60 | V    |

|                                   | All other input terminals, V <sub>O</sub> |   | -0.5 | 3.60 | V    |

| ENVIRONMENTAL                     |                                           | · |      |      |      |

| TJ                                | Junction temperature                      |   | -30  | 105  | ٥C   |

| T <sub>stg</sub>                  | Storage temperature                       |   | -40  | 125  | ٥C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages referenced to VSS (ground).

#### 6.2 ESD Ratings

|                    |               |                                                                                          | VALUE | UNIT |

|--------------------|---------------|------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | v    |

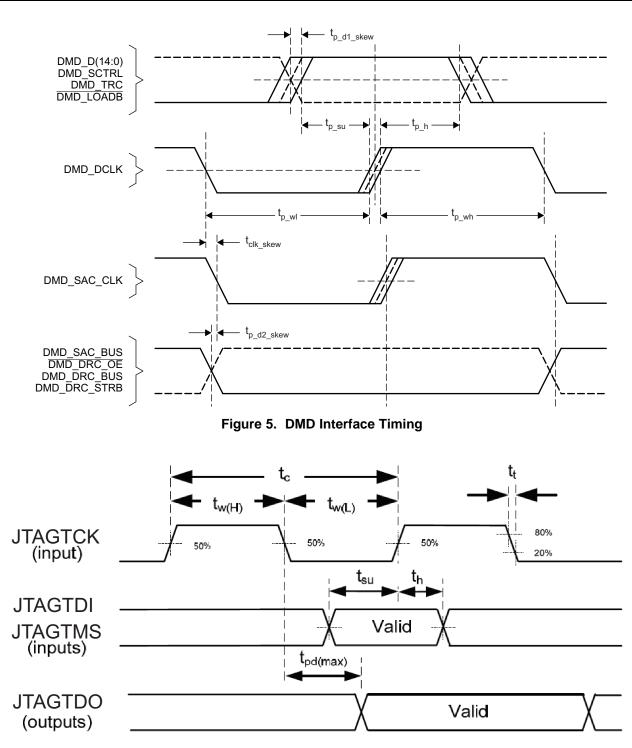

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.