DAC7811 ZHCSHU4E -APRIL 2005-REVISED MARCH 2018

# DAC7811 12 位串行输入乘法数模转换器

### 1 特性

- 2.7V 至 5.5V 电源供电

- 50MHz串口

- 10MHz 的乘法带宽

- ±15V 基准输入

- 低毛刺脉冲能量: 5 nV-s

- 工作温度范围:

- -40°C 至 +125°C

- 10 引脚超薄小外形尺寸 (VSSOP) 封装

- 12 位单调性

- 四象限乘法

- 上电复位(具有欠压保护功能)

- 菊链模式

- 读回功能

- 工业标准引脚配置

### 2 应用

- 便携式电池供电仪表

- 波形发生器

- 模拟处理

- 可编程放大器和衰减器

- 数控校准

- 可编程滤波器和振荡器

- 复合视频

- 超声波

### 3 说明

DAC7811 是一款 CMOS 12 位电流输出数模转换器 (DAC)。该器件由 2.7V 至 5.5V 电源供电,这使得该器件非常适合电池供电的应用和许多其他 应用。

该 DAC 使用与 SPI、 QSPI™、MICROWIRE 和大多数 DSP 接口标准相兼容的双缓冲 3 线串行接口。此外,在使用多个器件时,可以通过串行数据输出引脚(SDO) 实现菊链。利用数据读回功能,用户可以通过SDO 引脚读取 DAC 寄存器的内容。一旦加电,内部移位寄存器和锁存器中就会填充零,并且 DAC 输出将处于零标度。

DAC7811 可提供出色的四象限乘法特性以及 10MHz 的大信号乘法带宽。施加的外部基准输入电压 (V<sub>REF</sub>) 确定满标量程输出电流。与外部电流到电压精密放大器结合使用时,集成式反馈电阻器 (R<sub>FB</sub>) 可提供温度跟踪和满标量程电压输出。

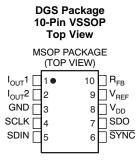

DAC7811 采用 10 引线 VSSOP 封装。

## 器件信息(1)

|         | HH 11 1H 10. |                 |

|---------|--------------|-----------------|

| 器件型号    | 封装           | 封装尺寸 (标称值)      |

| DAC7811 | VSSOP (10)   | 3.00mm x 3.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

Copyright © 2016, Texas Instruments Incorporated

|     | 目录                                                   | Ĺ   |                                |      |

|-----|------------------------------------------------------|-----|--------------------------------|------|

| 1   | 特性 1                                                 |     | 7.4 Device Functional Modes    | 12   |

| 2   | 应用                                                   | 8   | Application and Implementation |      |

| 3   | 说明1                                                  |     | 8.1 Application Information    |      |

| 4   | 修订历史记录                                               |     | 8.2 Typical Application        |      |

| _   |                                                      | 9   | Power Supply Recommendations   |      |

| 5   | Pin Configuration and Functions                      | 10  | Layout                         |      |

| 6   |                                                      |     | 10.1 Layout Guidelines         |      |

|     | 6.1 Absolute Maximum Ratings                         |     | 10.2 Layout Example            |      |

|     | 6.2 ESD Ratings                                      | 11  | 器件和文档支持                        |      |

|     | 6.3 Recommended Operating Conditions                 |     | 41.1 文档支持                      |      |

|     | 6.4 Thermal Information                              |     | 11.2 接收文档更新通知                  |      |

|     | 6.5 Electrical Characteristics                       |     | 11.3 社区资源                      |      |

|     | 6.6 Typical Characteristics: V <sub>DD</sub> = 5 V   |     |                                |      |

|     | 6.7 Typical Characteristics: V <sub>DD</sub> = 2.7 V |     | 11.4 商标<br>11.5 静电放电警告         |      |

| 7   |                                                      |     |                                |      |

|     | 7.1 Overview 11                                      | 40  | 11.6 Glossary                  |      |

|     | 7.2 Functional Block Diagram 11                      | 12  | 机械、封装和可订购信息                    | 22   |

|     | 7.3 Feature Description                              |     |                                |      |

| 注:  | <b>修订历史记录</b><br>之前版本的页码可能与当前版本有所不同。                 |     |                                |      |

| Cha | nges from Revision D (March 2016) to Revision E      |     |                                | Page |

| • ( | Changed Figure 28 SDO pin timing to remove Hi-Z      |     |                                | 14   |

| Cha | nges from Revision C (July 2007) to Revision D       |     |                                | Page |

| •   | 已添加 <b>ESD</b> 额定值 表、特性 说明 部分,器件功能模式,应用              | 和实施 | 5 部分,电源建议 部分,布局 部分、器件系         |      |

## 5 Pin Configuration and Functions

### **Pin Functions**

|     | PIN                | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME               | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | I <sub>OUT</sub> 1 | 0    | DAC Current Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | I <sub>OUT</sub> 2 | 0    | DAC Analog Ground. This pin is normally tied to the analog ground of the system.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3   | GND                | G    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4   | SCLK               | I    | Serial Clock Input. By default, data is clocked into the input shift register on the falling edge of the serial clock input. Alternatively, by means of the serial control bits, the device may be configured such that data is clocked into the shift register on the rising edge of SCLK.                                                                                                                                                                                        |

| 5   | SDIN               | I    | Serial Data Input. Data is clocked into the 16-bit input register on the active edge of the serial clock input. By default, on power-up, data is clocked into the shift register on the falling edge of SCLK. The control bits allow the user to change the active edge to the rising edge.                                                                                                                                                                                        |

| 6   | SYNC               | I    | Active Low Control Input. This is the frame synchronization signal for the input data. When \$\overline{SYNC}\$ goes low, it powers on the SCLK and DIN buffers, and the input shift register is enabled. Data is loaded to the shift register on the active edge of the following clocks (power-on default is falling clock edge). In stand-alone mode, the serial interface counts the clocks and data is latched to the shift register on the 16th active clock edge.           |

| 7   | SDO                | 0    | Serial Data Output. This allows a number of parts to be daisy-chained. By default, data is clocked into the shift register on the falling edge and out via SDO on the rising edge of SCLK. Data will always be clocked out on the alternate edge to loading data to the shift register. Writing the Readback control word to the shift register makes the DAC register contents available for readback on the SDO pin, clocked out on the opposite edges to the active clock edge. |

| 8   | $V_{DD}$           | I    | Positive Power Supply Input. These parts can be operated from a supply of 2.7 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                                                                          |

| 9   | $V_{REF}$          | I    | DAC Reference Voltage Input                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10  | R <sub>FB</sub>    | 0    | DAC Feedback Resistor pin. Establish voltage output for the DAC by connecting to external amplifier output.                                                                                                                                                                                                                                                                                                                                                                        |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               | MIN  | MAX            | UNIT |

|-----------------------------------------------|------|----------------|------|

| V <sub>DD</sub> to GND                        | -0.3 | 7              | V    |

| Digital input voltage to GND                  | -0.3 | $V_{DD} + 0.3$ | V    |

| I <sub>OUT</sub> 1, I <sub>OUT</sub> 2 to GND | -0.3 | $V_{DD} + 0.3$ | V    |

| Operating temperature                         | -40  | 125            | °C   |

| Junction temperature, (T <sub>J</sub> max)    |      | 150            | °C   |

| Storage temperature, T <sub>stg</sub>         | -65  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT       |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------------|

| V                  | Floatroototic disabores | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \ <u>/</u> |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V          |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                        |                          | MIN | NOM I | MAX | UNIT |

|-----------------|------------------------|--------------------------|-----|-------|-----|------|

| $V_{DD}$        | Supply voltage to GND  |                          | 2.7 |       | 5.5 | V    |

| $V_{REF}$       | Reference voltage      |                          | -15 |       | 15  | V    |

| .,              | lanut laurusliana      | $V_{DD} = 2.7 \text{ V}$ |     |       | 0.6 | V    |

| V <sub>IL</sub> | Input low voltage      | $V_{DD} = 5 V$           |     |       | 8.0 | V    |

| V               | Input high valtage     | $V_{DD} = 2.7 \text{ V}$ | 2.1 |       |     | V    |

| V <sub>IH</sub> | Input high voltage     | $V_{DD} = 5 V$           | 2.4 |       |     | V    |

| T <sub>A</sub>  | Operating ambient temp | erature                  | -40 |       | 125 | °C   |

### 6.4 Thermal Information

|                      |                                              | DAC7811     |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP) | UNIT |

|                      |                                              | 10 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 165.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 55.4        | °C/W |

| $R_{	heta JB}$       | Junction-to-board thermal resistance         | 85.6        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 6.2         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 84.2        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.5 Electrical Characteristics

$V_{DD}$  = 2.7 V to 5.5 V;  $I_{OUT}$ 1 = Virtual GND;  $I_{OUT}$ 2 = 0V;  $V_{REF}$  = 10 V;  $T_A$  = full operating temperature. All specifications -40°C to 125°C, unless otherwise noted.

| PARAMETER                                                         | TEST CONDITIONS                                                       | MIN | TYP                | MAX      | UNIT   |

|-------------------------------------------------------------------|-----------------------------------------------------------------------|-----|--------------------|----------|--------|

| STATIC PERFORMANCE                                                |                                                                       |     |                    |          |        |

| Resolution                                                        |                                                                       | 12  |                    |          | Bits   |

| Relative accuracy                                                 |                                                                       |     |                    | ±1       | LSB    |

| Differential nonlinearity                                         |                                                                       |     |                    | ±1       | LSB    |

| Output leakage current                                            | Data = 0000h, T <sub>A</sub> = 25°C                                   |     |                    | ±5       | nA     |

| Output leakage current                                            | Data = 0000h, T <sub>A</sub> = T <sub>MAX</sub>                       |     |                    | ±25      | nA     |

| Full-scale gain error                                             | All ones loaded to DAC register                                       |     | ±5                 | ±10      | mV     |

| Full-scale tempco <sup>(1)</sup>                                  |                                                                       |     | ±5                 |          | ppm/°C |

| Output capacitance <sup>(1)</sup>                                 | Code dependent                                                        |     | 5                  |          | pF     |

| REFERENCE INPUT                                                   | -                                                                     |     |                    | (1)      | •      |

| Input resistance                                                  |                                                                       | 8   | 10                 | 12       | kΩ     |

| R <sub>FB</sub> resistance                                        |                                                                       | 8   | 10                 | 12       | kΩ     |

| LOGIC INPUTS AND OUTPUT <sup>(1)</sup>                            | •                                                                     | 1   |                    |          |        |

| I <sub>IL</sub> Input leakage current                             |                                                                       |     |                    | 10       | μA     |

| C <sub>IL</sub> Input capacitance                                 |                                                                       |     |                    | 10       | pF     |

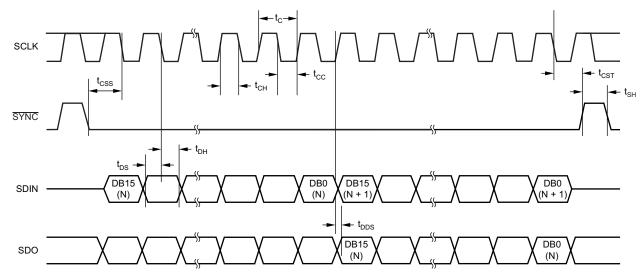

| INTERFACE TIMING (see Figure 28)                                  |                                                                       | -   |                    | <b>!</b> | •      |

| fclk                                                              |                                                                       |     |                    | 50       | MHz    |

| t <sub>C</sub> Clock period                                       |                                                                       | 20  |                    |          | ns     |

| t <sub>CH</sub> Clock pulse width high                            |                                                                       | 8   |                    |          | ns     |

| t <sub>CC</sub> Clock pulse width low                             |                                                                       | 8   |                    |          | ns     |

| t <sub>CSS</sub> SYNC falling edge to SCLK active edge setup time |                                                                       | 13  |                    |          | ns     |

| SCLK active edge to SYNC rising edge hold time                    |                                                                       | 5   |                    |          | ns     |

| t <sub>DS</sub> Data setup time                                   |                                                                       | 5   |                    |          | ns     |

| t <sub>DH</sub> Data hold time                                    |                                                                       | 3   |                    |          | ns     |

| t <sub>SH</sub> SYNC high time                                    |                                                                       | 30  |                    |          | ns     |

| SYNC inactive edge to SDO                                         | $V_{DD} = 2.7 \text{ V}$                                              |     | 25                 | 35       | ns     |

| t <sub>DDS</sub> valid                                            | $V_{DD} = 5 V$                                                        |     | 20                 | 30       | ns     |

| POWER REQUIREMENTS                                                |                                                                       |     |                    |          |        |

| I <sub>DD</sub> (normal operation)                                | Logic inputs = 0 V                                                    |     |                    | 5        | μΑ     |

| V <sub>DD</sub> = 4.5 V to 5.5 V                                  | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                                  |     | 0.8                | 5        | μA     |

| $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$                        | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                                  |     | 0.4                | 2.5      | μΑ     |

| AC CHARACTERISTICS <sup>(1)</sup>                                 |                                                                       |     |                    |          |        |

| Output voltage settling time                                      |                                                                       |     |                    | 0.2      | μs     |

| Reference multiplying BW                                          | $V_{REF} = 7 V_{PP}$ , Data = FFFh                                    | 10  |                    |          | MHz    |

| DAC glitch impulse                                                | $V_{REF} = 0 \text{ V to } 10 \text{ V},$ Data = 7FFh to 800h to 7FFh |     | 5                  |          | nV-s   |

| Feedthrough error V <sub>OUT</sub> /V <sub>REF</sub>              | Data = 000h, V <sub>REF</sub> = 100 kHz                               |     | -60                |          | dB     |

| Digital feedthrough                                               |                                                                       |     | 2                  |          | nV-s   |

| Total harmonic distortion                                         |                                                                       |     | -105               |          | dB     |

| Output spot noise voltage                                         |                                                                       |     | nV/√ <del>Hz</del> |          |        |

<sup>(1)</sup> Specified by design and characterization; not production tested.

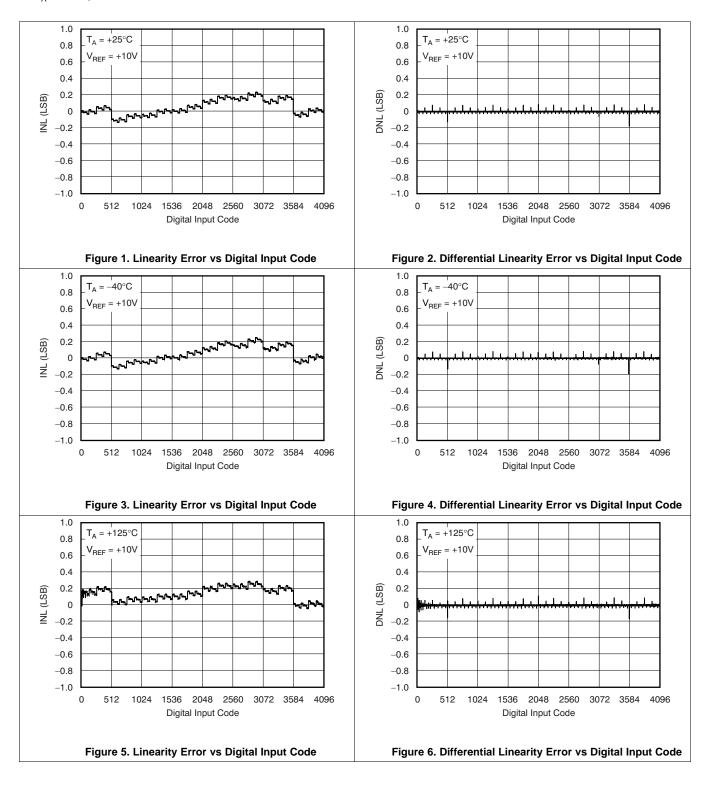

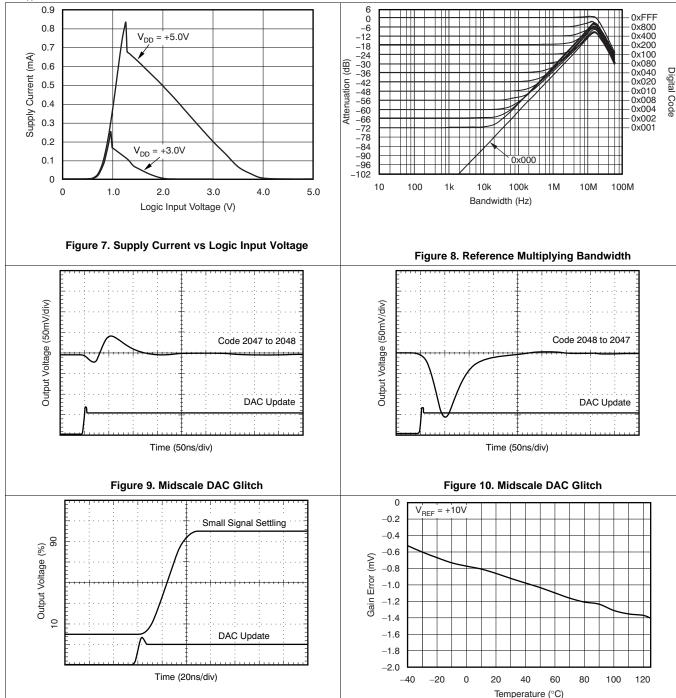

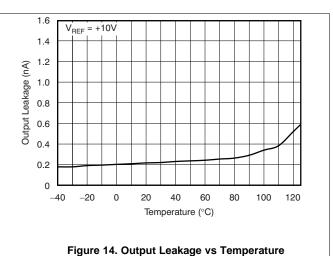

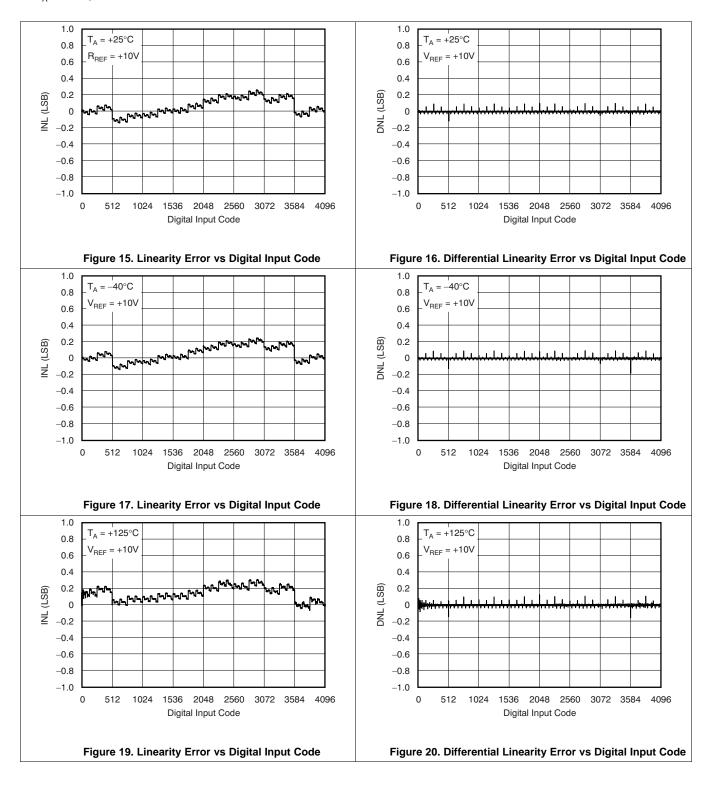

## 6.6 Typical Characteristics: $V_{DD} = 5 \text{ V}$

## Typical Characteristics: $V_{DD} = 5 V$ (continued)

Figure 11. DAC Settling Time

Figure 12. Gain Error vs Temperature

## Typical Characteristics: $V_{DD} = 5 \text{ V (continued)}$

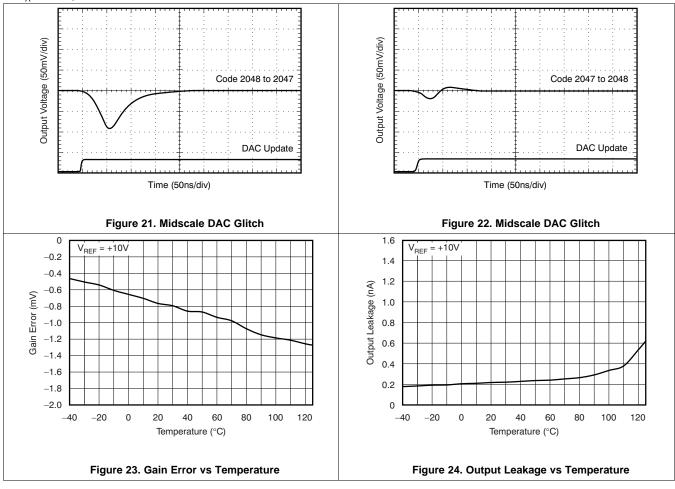

## 6.7 Typical Characteristics: $V_{DD} = 2.7 \text{ V}$

## Typical Characteristics: $V_{DD} = 2.7 \text{ V}$ (continued)

## 7 Detailed Description

#### 7.1 Overview

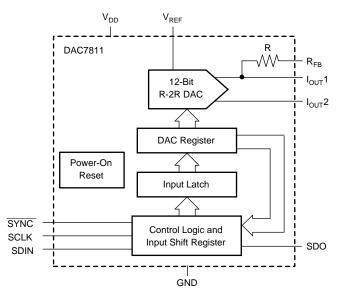

The DAC7811 is a CMOS, 12-bit, current output digital-to-analog converter (DAC). This device operates from a 2.7-V to 5.5-V power supply, making it suitable for battery-powered and many other applications. This DAC uses a double-buffered 3-wire serial interface that is compatible with SPI, QSPI™, MICROWIRE, and most DSP interface standards. In addition, a serial data out pin (SDO) allows for daisy-chaining when multiple devices are used. Data readback allows the user to read the contents of the DAC register via the SDO pin. On power-up, the internal shift register and latches are filled with zeroes and the DAC outputs are at zero scale.

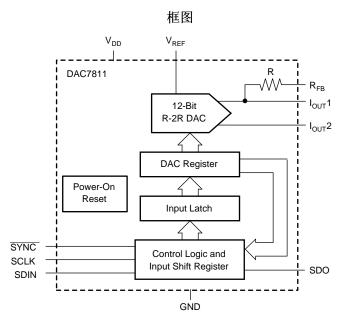

### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

### 7.3 Feature Description

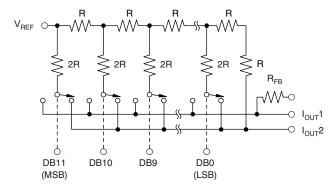

The DAC7811 is a single channel, current output, 12-bit digital-to-analog converter (DAC). The architecture, illustrated in Figure 25, is an R-2R ladder configuration with the three MSBs segmented. Each 2R leg of the ladder is either switched to  $I_{OUT}1$  or the  $I_{OUT}2$  terminal. The  $I_{OUT}1$  terminal of the DAC is held at a virtual GND potential by the use of an external I/V converter op amp. The R-2R ladder is connected to an external reference input  $V_{REF}$  that determines the DAC full-scale current. The R-2R ladder presents a code independent load impedance to the external reference of  $10k\Omega$  ±20%. The external reference voltage can vary over a range of -15V to +15V, thus providing bipolar  $I_{OUT}$  current operation. By using an external I/V converter and the DAC7811  $R_{FB}$  resistor, output voltage ranges of  $-V_{REF}$  to  $V_{REF}$  can be generated.

Figure 25. Equivalent R-2R DAC Circuit

### **Feature Description (continued)**

When using an external I/V converter and the DAC7811  $R_{FB}$  resistor, the DAC output voltage is given by Equation 1:

$$V_{OUT} = -V_{REF} \times \left(\frac{CODE}{4096}\right) \tag{1}$$

Each DAC code determines the 2R leg switch position to either GND or  $I_{OUT}$ . Because the DAC output impedance as seen looking into the  $I_{OUT}$ 1 terminal changes versus code, the external I/V converter noise gain will also change. Because of this, the external I/V converter op amp must have a sufficiently low offset voltage such that the amplifier offset is not modulated by the DAC  $I_{OUT}$ 1 terminal impedance change. External op amps with large offset voltages can produce INL errors in the transfer function of the DAC7811 due to offset modulation versus DAC code.

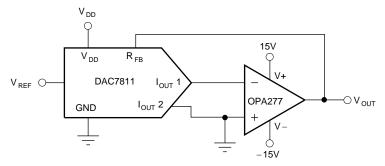

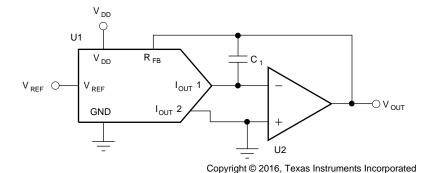

For best linearity performance of the DAC7811, a low offset voltage op amp (such as the OPA277) is recommended (see Figure 26). This circuit allows  $V_{REF}$  swinging from -10 V to 10 V.

Copyright © 2016, Texas Instruments Incorporated

Figure 26. Voltage Output Configuration

### 7.4 Device Functional Modes

### 7.4.1 Serial Interface

The DAC7811 has a 3-wire serial interface (\$\overline{SYNC}\$, SCLK, and SDIN), which is compatible with SPI, QSPI, and MICROWIRE interface standards as well as most Digital Signal Processor (DSP) devices. See the Serial Write Operation timing diagram (Figure 28) for an example of a typical write sequence. The write sequence begins by bringing the \$\overline{SYNC}\$ line low. Data from the DIN line are clocked into the 16-bit shift register on the falling edge of SCLK. The serial clock frequency can be as high as 50MHz, making the DAC7811 compatible with high-speed DSPs. The SDIN and SCLK input buffers are gated off while \$\overline{SYNC}\$ is high which minimizes the power dissipation of the digital interface. After \$\overline{SYNC}\$ goes low, the digital interface will respond to the \$\overline{SDIN}\$ and SCLK input signals and data can now be shifted into the device. If an inactive clock edge occurs after \$\overline{SYNC}\$ goes low, but before the first active clock edge, it will be ignored. If the SDO pin is being used then \$\overline{SYNC}\$ must remain low until after the inactive clock edge that follows the 16th active clock edge.

### 7.4.2 Input Shift Register

The input shift register is 16 bits wide, as shown in Figure 27. The four MSBs are the control bits C3–C0; these bits determine which function will be executed at the rising edge of SYNC in daisy-chain mode or the 16th active clock edge in stand-alone mode. The remaining 12 bits are the data bits. On a load and update command (C3–C0 = 0001) these 12 data bits will be transferred to the DAC register; otherwise, they have no effect. Table 1 shows serial shift register and DAC register operation with CLK and SYNC pin settings.

### **Device Functional Modes (continued)**

| 4 CONTROL BITS |     |     |     |      |     |    |    |    | 12 DAT | A BITS |    |    |    |    |             |

|----------------|-----|-----|-----|------|-----|----|----|----|--------|--------|----|----|----|----|-------------|

| B15<br>(MSB)   | B14 | B13 | B12 | B11  | B10 | В9 | B8 | B7 | В6     | B5     | B4 | В3 | B2 | B1 | B0<br>(LSB) |

| C3             | C2  | C1  | C0  | DB11 |     |    |    |    |        |        |    |    |    |    | DB0         |

Figure 27. Contents of the 16-Bit Input Shift Register

Table 1. Control Logic Truth Table (1)

| CLK     | SYNC      | SERIAL SHIFT REGISTER                                                 | DAC REGISTER                                                         |

|---------|-----------|-----------------------------------------------------------------------|----------------------------------------------------------------------|

| X       | Н         | No effect                                                             | Latched                                                              |

| <b></b> | L         | Shift register data advanced one bit                                  | Latched                                                              |

| Х       | <b>↑+</b> | In daisy-chain mode, the function as determined by C3-C0 is executed. | In daisy-chain mode, the contents may change as determined by C3-C0. |

<sup>(1) ⊥-</sup> Negative logic transition, default CLK mode: ↑+ Positive logic transition; **X** = Do not care.

### 7.4.3 SYNC Interrupt (Stand-Alone Mode)

In a normal write sequence, the SYNC line is kept low for at least 16 falling edges of SCLK and the DAC is updated on the 16th falling edge. However, if SYNC is brought high before the 16th falling edge, this acts as an interrupt to the write sequence. The shift register is reset and the write sequence is seen as invalid. Neither an update of the DAC register contents nor a change in the operating mode occurs.

### 7.4.4 Daisy-Chain

The DAC7811 powers up in the daisy-chain mode which must be used when two or more devices are connected in tandem. The SCLK and SYNC signals are shared across all devices while the SDO output of the first device connects to the SDIN input of the following device, and so forth. In this configuration 16 SCLK cycles for each DAC7811 in the chain are required. Please refer to the timing diagram of Figure 28.

For *n* devices in a daisy-chain configuration, 16*n* SCLK cycles are required to shift in the entire input data stream. After 16*n* active SCLK edges are received following a falling SYNC, the data stream becomes complete, and SYNC can brought high to update *n* devices simultaneously.

When SYNC is brought high, each device will execute the function defined by the four DAC control bits C3-C0 in its input shift register. For example, C3-C0 must be **0001** for each DAC in the chain that is to be updated with new data, and C3-C0 must be **0000** for each DAC in the chain whose contents are to remain unchanged.

A continuous stream containing the exact number of SCLK cycles may be sent first while the  $\overline{\text{SYNC}}$  signal is held low, and then raise  $\overline{\text{SYNC}}$  at a later time. Nothing happens until the rising edge of  $\overline{\text{SYNC}}$ , and then each DAC7811 in the chain will execute the function defined by the four DAC control bits C3-C0 in its input shift register.

Figure 28. DAC7811 Timing Diagram

### 7.4.5 Control Bits C3 to C0

Control Bits C3 to C0 allow control of various functions of the DAC; see Table 2. Default settings of the DAC on powering up are as follows: Data clocked into shift register on falling clock edges; daisy-chain mode is enabled. The device powers on with zero-scale loaded into the DAC register and I<sub>OUT</sub> lines. The DAC control bits allow the user to adjust certain features as part of an initialization sequence; for example, daisy-chaining may be disabled if not in use, active clock edge may be changed to rising edge, and DAC output may be cleared to either zero or midscale. The user may also initiate a readback of the DAC register contents for verification purposes.

Table 2. Serial Input Register Data Format, Data Loaded MSB First

|    |    |    | _          |                                             |  |  |

|----|----|----|------------|---------------------------------------------|--|--|

| C3 | C2 | C1 | C0         | FUNCTION IMPLEMENTED                        |  |  |

| 0  | 0  | 0  | 0          | No operation (power-on default)             |  |  |

| 0  | 0  | 0  | 1          | Load and update                             |  |  |

| 0  | 0  | 1  | 0          | Initiate readback                           |  |  |

| 0  | 0  | 1  | 1          | Reserved                                    |  |  |

| 0  | 1  | 0  | 0          | Reserved                                    |  |  |

| 0  | 1  | 0  | 1          | Reserved                                    |  |  |

| 0  | 1  | 1  | 0          | Reserved                                    |  |  |

| 0  | 1  | 1  | 1          | Reserved                                    |  |  |

| 1  | 0  | 0  | 0          | Reserved                                    |  |  |

| 1  | 0  | 0  | 1          | Daisy-chain disable                         |  |  |

| 1  | 0  | 1  | 0          | Clock data to shift register on rising edge |  |  |

| 1  | 0  | 1  | 1          | Clear DAC output to zero                    |  |  |

| 1  | 1  | 0  | 0          | Clear DAC output to midscale                |  |  |

| 1  | 1  | 0  | 1          | Reserved                                    |  |  |

| 1  | 1  | 1  | 0 Reserved |                                             |  |  |

| 1  | 1  | 1  | 1          | Reserved                                    |  |  |

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The 2.7-V to 5.5-V supply operation makes the DAC7811 a viable candidate for battery operated applications, such as waveform generators, programmable amplifiers, and any mobile platforms that may require analog outputs and processing. Additionally, the large signal multiplying bandwidth of the DAC7811 makes it an excellent choice for programmable filters and oscillators.

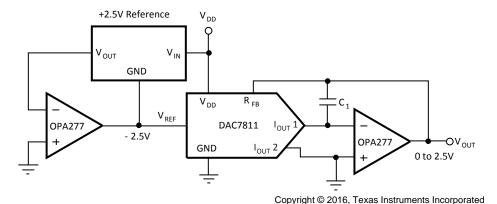

### 8.1.1 Unipolar Operation Using DAC7811

To generate a positive voltage output, a negative reference is input to the DAC7811. This design is suggested instead of using an inverting amp to invert the output as a result of resistor tolerance errors. For a negative reference, VOUT and GND of the reference are level-shifted to a virtual ground and a -2.5-V input to the DAC7811 with an op amp.

Figure 29. Positive Voltage Output Circuit

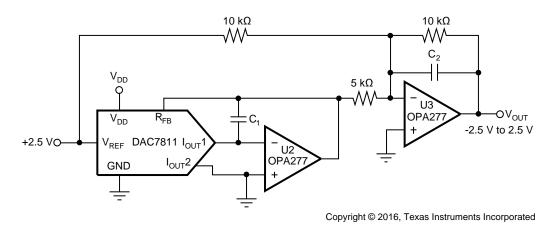

### 8.1.2 Bipolar Operation Using the DAC7811

The DAC7811, as a 2-quadrant multiplying DAC, can be used to generate a unipolar output. The polarity of the full-scale output IOUT is the inverse of the input reference voltage at VREF.

Some applications require full 4-quadrant multiplying capabilities or bipolar output swing. As shown in Figure 30, external op amp U3 is added as a summing amp and has a gain of 2X that widens the output span to 5 V. A 4-quadrant multiplying circuit is implemented by using a 2.5-V offset of the reference voltage to bias U3. According to the circuit transfer equation given in Equation 2, input data (D) from code 0 to full-scale produces output voltages of VOUT = -2.5 V to VOUT = +2.5 V

$$V_{OUT} = \left[ \left( \frac{D}{2^{11}} \right) - 1 \right] \times V_{REF} \tag{2}$$

External resistance mismatching is the significant error in Figure 30.

## **Application Information (continued)**

Figure 30. Bipolar Output Circuit

## 8.1.3 Stability Circuit

For a current-to-voltage design (see Figure 31), the DAC7811 current output ( $I_{OUT}$ ) and the connection with the inverting node of the op amp should be as short as possible and according to correct printed circuit board (PCB) layout design practices. For each code change, there is a step function. If the gain bandwidth product (GBP) of the op amp is limited and parasitic capacitance is excessive at the inverting node, then gain peaking is possible. Therefore, for circuit stability, a compensation capacitor  $C_1$  (1pF to 5pF typ) can be added to the design, as shown in Figure 31.

Figure 31. Gain Peaking Prevention Circuit With Compensation Capacitor

### 8.1.4 Amplifier Selection

There are many choices and many differences in selecting the proper operational amplifier for a multiplying DAC (MDAC). Making the analog signal out of the MDAC is one critical aspect. However, there are also other issues to take into account such as amplifier noise, input bias current, and offset voltage, as well as MDAC resolution and glitch energy. Table 3 and Table 4 suggest some suitable operational amplifiers for low power, fast settling, and high-speed applications. A greater selection of operational amplifiers can be found at www.ti.com/amplifier.

## **Application Information (continued)**

## Table 3. Suitable Precision Operational Amplifiers from Texas Instruments

| PRODUCT      | TOTAL<br>SUPPLY<br>VOLTAGE<br>(V) (min) | TOTAL<br>SUPPLY<br>VOLTAGE<br>(V) (max) | I <sub>Q</sub> PER CHANNEL (max) (mA) | GBW<br>(typ)<br>(MHz) | SLEW<br>RATE<br>(typ)<br>(V/μs) | OFFSET<br>DRIFT<br>(typ)<br>(μV/°C) | I <sub>IB</sub><br>(max)<br>(pA) | CMRR<br>(min)<br>(dB) | PACKAGE/<br>LEAD              | DESCRIPTION                                                                                   |  |  |

|--------------|-----------------------------------------|-----------------------------------------|---------------------------------------|-----------------------|---------------------------------|-------------------------------------|----------------------------------|-----------------------|-------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| LOW POWER    | LOW POWER                               |                                         |                                       |                       |                                 |                                     |                                  |                       |                               |                                                                                               |  |  |

| OPA703       | 4                                       | 12                                      | 0.2                                   | 1                     | 0.6                             | 4                                   | 10                               | 70                    | SOT5-23,<br>PDIP-8,<br>SOIC-8 | 12V, CMOS, Rail-to-Rail I/O,<br>Operational Amplifier                                         |  |  |

| OPA735       | 2.7                                     | 12                                      | 0.75                                  | 1.6                   | 1.5                             | 0.01                                | 200                              | 115                   | SOT5-23,<br>SOIC-8            | 0.05μV/°C (max), Single-<br>Supply CMOS Zero-Drift<br>Series Operational Amplifier            |  |  |

| OPA344       | 2.7                                     | 5.5                                     | 0.25                                  | 1                     | 1                               | 2.5                                 | 10                               | 80                    | SOT5-23,<br>PDIP-8,<br>SOIC-8 | Low Power, Single-Supply,<br>Rail-To-Rail Operational<br>Amplifiers MicroAmplifier<br>Series  |  |  |

| OPA348       | 2.1                                     | 5.5                                     | 0.065                                 | 1                     | 0.5                             | 2                                   | 10                               | 70                    | SC5-70,<br>SOT5-23,<br>SOIC-8 | 1MHz, 45μA, Rail-to-Rail I/O,<br>Single Op Amp                                                |  |  |

| OPA277       | 4                                       | 36                                      | 0.825                                 | 1                     | 0.8                             | 0.1                                 | 1000                             | 130                   | PDIP-8,<br>SOIC-8,<br>SON-8   | High Precision Operational<br>Amplifiers                                                      |  |  |

| FAST SETTLIN | iG                                      | •                                       | •                                     |                       |                                 |                                     |                                  |                       | •                             | •                                                                                             |  |  |

| OPA350       | 2.7                                     | 5.5                                     | 7.5                                   | 38                    | 22                              | 4                                   | 10                               | 76                    | MSOP-8,<br>PDIP-8,<br>SOIC-8  | High-Speed, Single-Supply,<br>Rail-to-Rail Operational<br>Amplifiers MicroAmplifier<br>Series |  |  |

| OPA727       | 4                                       | 12                                      | 6.5                                   | 20                    | 30                              | 0.6                                 | 500                              | 86                    | MSOP-8,<br>SON-8              | e-trim 20MHz, High Precision<br>CMOS Operational Amplifier                                    |  |  |

| OPA227       | 5                                       | 36                                      | 3.8                                   | 8                     | 2.3                             | 0.1                                 | 10000                            | 120                   | PDIP-8,<br>SOIC-8             | High Precision, Low Noise<br>Operational Amplifiers                                           |  |  |

## Table 4. Suitable High Speed Operational Amplifiers from Texas Instruments (Multiple Channel Options)

| PRODUCT        | SUPPLY<br>VOLTAGE<br>(V) | GBW<br>PRODUCT<br>(MHz) | VOLTAGE<br>NOISE<br>nV/√Hz | GBW<br>(typ)<br>(MHz) | SLEW<br>RATE<br>(V/μs) | V <sub>OS</sub><br>(typ)<br>(μV) | V <sub>OS</sub><br>(max)<br>(μV) | CMRR<br>(min)<br>(dB) | PACKAGE/<br>LEAD              | DESCRIPTION                                                                                         |

|----------------|--------------------------|-------------------------|----------------------------|-----------------------|------------------------|----------------------------------|----------------------------------|-----------------------|-------------------------------|-----------------------------------------------------------------------------------------------------|

| SINGLE CHANNEL |                          |                         |                            |                       |                        |                                  |                                  |                       |                               |                                                                                                     |

| THS4281        | ±2.7 to ±15              | 38                      | 12.5                       | 35                    | 500                    | 3500                             | 500                              | 1000                  | SOT5-23,<br>MSOP-8,<br>SOIC-8 | Very Low-Power High Speed<br>Rail-To-Rail Input/Output<br>Voltage Feedback<br>Operational Amplifier |

| THS4031        | ±4.5 to ±16.5            | 200                     | 1.6                        | 100                   | 500                    | 3000                             | 3000                             | 8000                  | CDIP-8,<br>MSOP-8,<br>SOIC-8  | 100-MHz Low Noise Voltage-<br>Feedback Amplifier                                                    |

| THS4631        | ±4.5 to ±16.5            | 210                     | 7                          | 900                   | 260                    | 2000                             | 50pA                             | 2                     | SOIC-8,<br>MSOP-8             | High Speed FET-Input<br>Operational Amplifier                                                       |

| OPA656         | ±4 to ±6                 | 230                     | 7                          | 290                   | 250                    | 2600                             | 2pA                              | 5pA                   | SOIC-8,<br>SOT5-23            | Wideband, Unity Gain Stable<br>FET-Input Operational<br>Amplifier                                   |

| OPA820         | ±2.5 to ±6               | 280                     | 2.5                        | 240                   | 200                    | 1200                             | 900                              | 23,000                | SOIC-8,<br>SOT5-23            | Unity Gain Stable, Low Noise,<br>Voltage Feedback<br>Operational Amplifier                          |

| DUAL CHAN      | NEL                      |                         |                            |                       |                        |                                  |                                  |                       |                               |                                                                                                     |

| THS4032        | ±4.5 to ±16.5            | 200                     | 1.6                        | 100                   | 500                    | 3000                             | 3000                             | 8000                  | SOIC-8,<br>MSOP-8             | 100-MHz Low Noise Voltage-<br>Feedback Amplifier, Dual                                              |

| OPA2822        | ±2 to ±6.3               | 220                     | 2                          | 170                   | 200                    | 1200                             | 9600                             | 12000                 | SOIC-8,<br>MSOP-8             | SpeedPlus Dual Wideband,<br>Low-Noise Operational<br>Amplifier                                      |

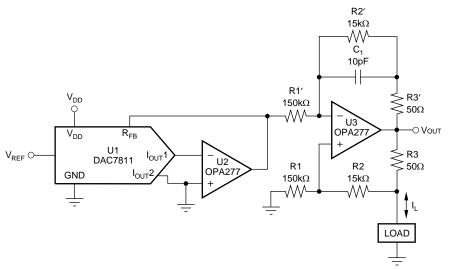

### 8.1.5 Programmable Current Source Circuit

A DAC7811 can be integrated into the circuit in Figure 32 to implement an improved Howland current pump for precise voltage to current conversions. Bidirectional current flow and high voltage compliance are two features of the circuit. With a matched resistor network, the load current of the circuit is shown by Equation 3:

$$I_{L} = \frac{(R2 + R3) / R1}{R3} \times V_{REF} \times \frac{D}{4096}$$

(3)

The value of R3 in Equation 3 can be reduced to increase the output current drive of U3. U3 can drive  $\pm 20$ mA in both directions with voltage compliance limited up to 15V by the U3 voltage supply. Elimination of the circuit compensation capacitor  $C_1$  in the circuit is not suggested as a result of the change in the output impedance  $Z_0$ , according to Equation 4:

$$Z_{O} = \frac{R1'R3(R1+R2)}{R1(R2'+R3') - R1'(R2+R3)}$$

(4)

As shown in Equation 4, with matched resistors,  $Z_O$  is infinite and the circuit is optimum for use as a current source. However, if unmatched resistors are used,  $Z_O$  is positive or negative with negative output impedance being a potential cause of oscillation. Therefore, by incorporating  $C_1$  into the circuit, possible oscillation problems are eliminated. The value of  $C_1$  can be determined for critical applications; for most applications, however, a value of several pF is suggested.

Copyright © 2016, Texas Instruments Incorporated

Figure 32. Programmable Bidirectional Current Source Circuit

### 8.2 Typical Application

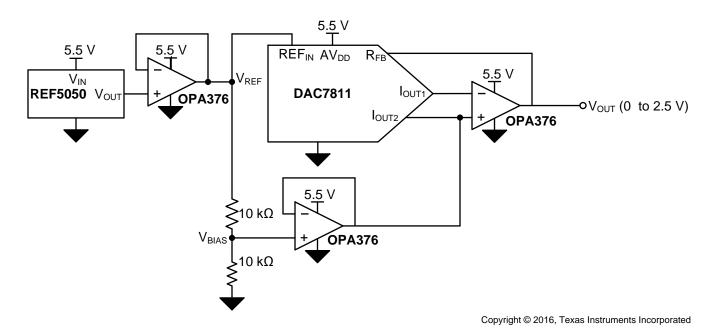

### 8.2.1 Single Supply Unipolar Multiplying DAC

Figure 33. Complete Circuit Schematic

### 8.2.1.1 Design Requirements

This multiplying DAC (MDAC) circuit outputs unipolar voltages from 0 V to 2.5 V. This design does not require dual supplies to realize a unipolar, positive output voltage. This design removes the need for a negative supply rail by applying a bias voltage the output transimpedance stage.

### 8.2.1.2 Detailed Design Procedure

The DAC7811 output current is converted into a voltage by including an op-amp in a transimpedance configuration at the DAC7811 current output terminal. The transimpedance stage creates an output voltage with opposite polarity to that of VREF and subsequently requires dual supplies. This circuit removes the need of dual power supplies and uses a single supply to power the circuit.

The transfer function from digital code to output voltage is shown in Equation 5.

$$V_{OUT}(Code) = V_{BIAS} - \frac{\left(V_{REF} - V_{BIAS}\right)}{2^{bits}} \times Code$$

(5)

More information regarding this design can be found in *Single-Supply Unipolar Multiplying DAC Reference Design* (TIDU300).

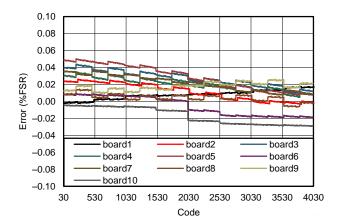

## 8.2.1.3 Application Curve

The Absolute error (TUE) in %FSR is shown the following graph, Figure 34. The plot below represents data ranging from code 30 to 4050. The figure shows the absolute error (TUE) has a maximum value of about 0.05% FSR.

## **Typical Application (continued)**

Figure 34. Absolute Error (TUE) in %FSR

## 9 Power Supply Recommendations

The DAC7811 can operate within the specified supply voltage range of 2.7 V to 5.5 V. The power applied to VDD should be well regulated and low noise. Switching power supplies and DC-DC converters often have high frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high-frequency spikes. This noise can easily couple into the DAC output voltage through various paths between the power connections and analog output. To further minimize noise from the power supply, a strong recommendation is to include a 1-µF to 10-µF capacitor and 0.1-µF bypass capacitor. The required supply current vs Logic Input voltage or temperature is displayed in *Typical Characteristics*. The power supply must meet the aforementioned current requirements.

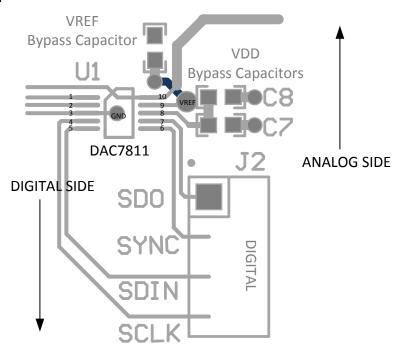

## 10 Layout

### 10.1 Layout Guidelines

A precision analog component requires careful layout, the list below provides some insight into good layout practices.

- All Power Supply pins should be bypassed to ground with a low ESR ceramic bypass capacitor. The typical recommended bypass capacitance is 0.1 to 0.22-µF ceramic with a X7R or NP0 dielectric.

- Power supplies and VREF bypass capacitors should be placed close to terminals or planes to minimize inductance and optimize performance.

- A high-quality ceramic type NP0 or X7R is recommended for its optimal performance across temperature, and very low dissipation factor.

- The digital and analog sections should have proper placement with respect to the digital pins and analog pins

of the DAC9881 device. The separation of analog and digital blocks will allow for better design and practice

as it will ensure less coupling into neighboring blocks, and will minimize the interaction between analog and

digital return currents.

### 10.2 Layout Example

Figure 35. DAC7811 Example Layout

### 11 器件和文档支持

### 11.1 文档支持

### 11.1.1 相关文档

如需相关文档,请参阅:

- 《TI Designs 高精度:验证设计电压模式倍增 DAC 参考设计》(TIDUAFO)

- 《TI Designs 高精度:验证设计单电源单极倍增 DAC 参考设计》(TIDU300)

- 《将 DAC7811 连接到 MSP430F449》(SLAA372)

- DAC7811EVM (SLAU163)

### 11.2 接收文档更新通知

要接收文档更新通知,请导航至 Tl.com.cn 上的器件产品文件夹。请单击右上角的提醒我进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 11.3 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 TI 参考设计支持 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

## 11.4 商标

E2E is a trademark of Texas Instruments.

QSPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

### 11.5 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 12 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且 不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。 www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                 |              |              |

| DAC7811IDGS           | Active | Production    | VSSOP (DGS)   10 | 80   TUBE             | Yes  | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGS.A         | Active | Production    | VSSOP (DGS)   10 | 80   TUBE             | Yes  | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGSG4         | Active | Production    | VSSOP (DGS)   10 | 80   TUBE             | Yes  | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGSR          | Active | Production    | VSSOP (DGS)   10 | 2500   LARGE T&R      | Yes  | NIPDAUAG   SN | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGSR.A        | Active | Production    | VSSOP (DGS)   10 | 2500   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGSRG4        | Active | Production    | VSSOP (DGS)   10 | 2500   LARGE T&R      | Yes  | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGSRG4.A      | Active | Production    | VSSOP (DGS)   10 | 2500   LARGE T&R      | Yes  | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGST          | Active | Production    | VSSOP (DGS)   10 | 250   SMALL T&R       | Yes  | NIPDAUAG   SN | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

| DAC7811IDGST.A        | Active | Production    | VSSOP (DGS)   10 | 250   SMALL T&R       | Yes  | SN            | Level-2-260C-1 YEAR | -40 to 125   | 7811         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## PACKAGE OPTION ADDENDUM

www.ti.com 23-May-2025

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 23-May-2025

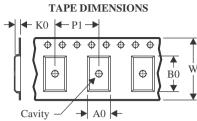

### TAPE AND REEL INFORMATION

|    | •                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

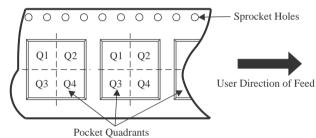

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DAC7811IDGSR   | VSSOP           | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.25       | 3.35       | 1.25       | 8.0        | 12.0      | Q1               |

| DAC7811IDGSRG4 | VSSOP           | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| DAC7811IDGST   | VSSOP           | DGS                | 10 | 250  | 330.0                    | 12.4                     | 5.25       | 3.35       | 1.25       | 8.0        | 12.0      | Q1               |

www.ti.com 23-May-2025

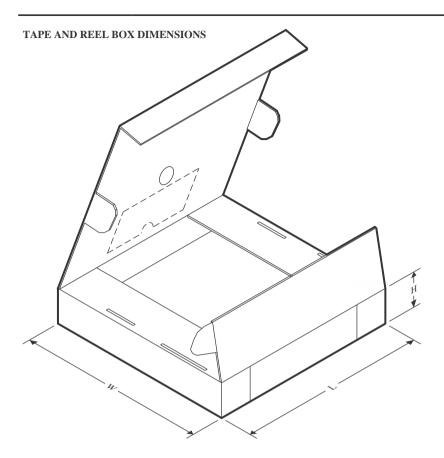

### \*All dimensions are nominal

| Device         | Package Type Package Drawing Pi |     | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|----------------|---------------------------------|-----|------|------|-------------|------------|-------------|--|

| DAC7811IDGSR   | VSSOP                           | DGS | 10   | 2500 | 366.0       | 364.0      | 50.0        |  |

| DAC7811IDGSRG4 | VSSOP                           | DGS | 10   | 2500 | 366.0       | 364.0      | 50.0        |  |

| DAC7811IDGST   | VSSOP                           | DGS | 10   | 250  | 366.0       | 364.0      | 50.0        |  |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

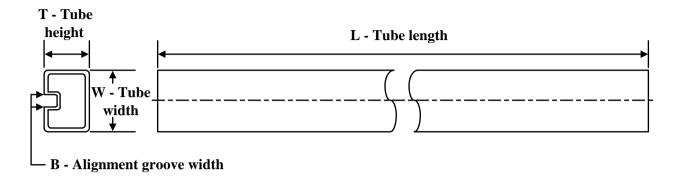

### **TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| DAC7811IDGS   | DGS          | VSSOP        | 10   | 80  | 330    | 6.55   | 500    | 2.88   |

| DAC7811IDGS.A | DGS          | VSSOP        | 10   | 80  | 330    | 6.55   | 500    | 2.88   |

| DAC7811IDGSG4 | DGS          | VSSOP        | 10   | 80  | 330    | 6.55   | 500    | 2.88   |

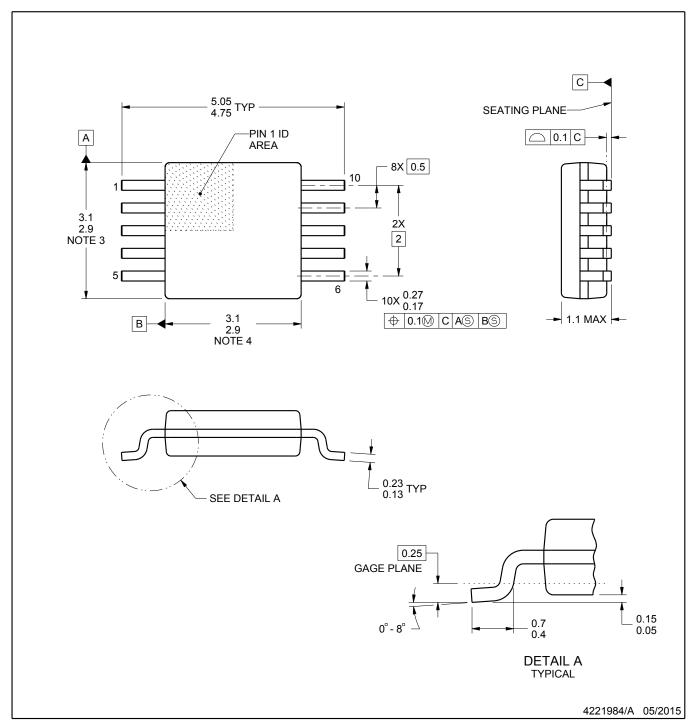

SMALL OUTLINE PACKAGE

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187, variation BA.

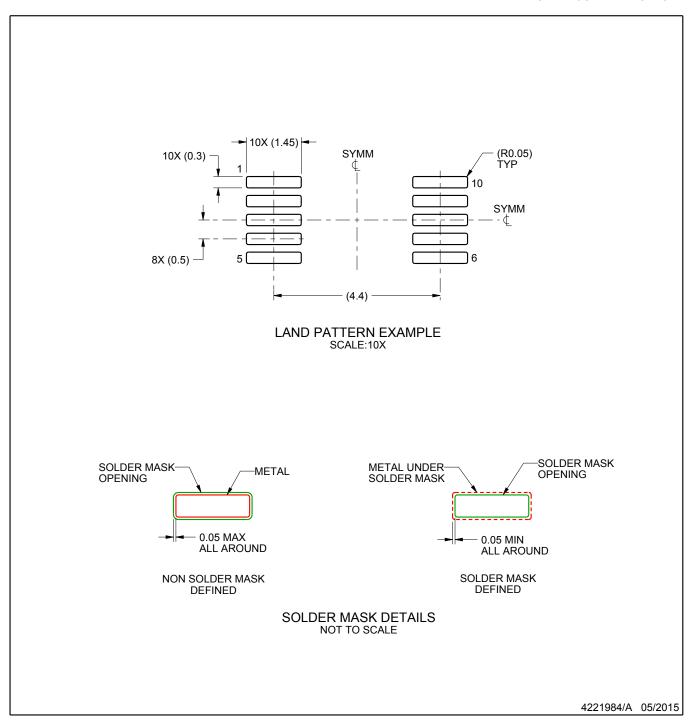

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

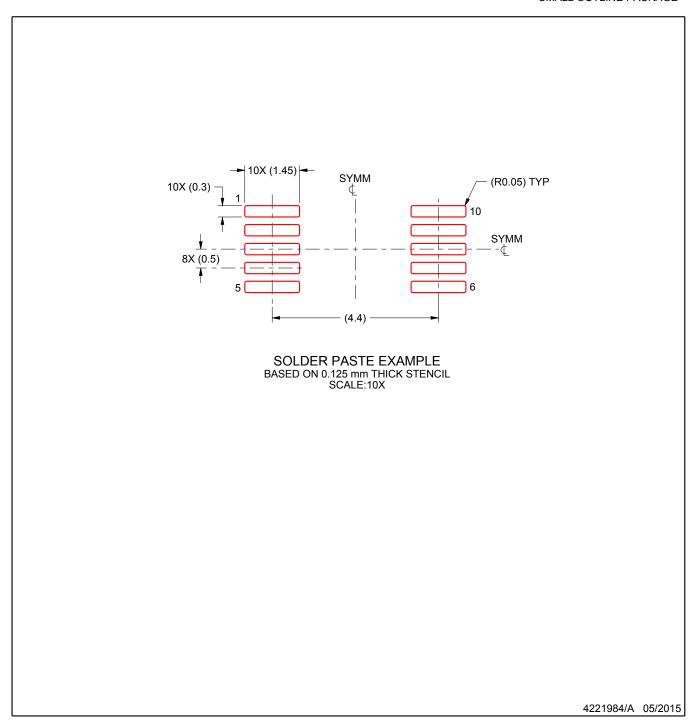

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司