bq76200

ZHCSED8 - NOVEMBER 2015

# bq76200 高压电池组前端充电/放电高侧 NFET 驱动器

# 特性

- CHG 和 DSG 高侧 N 沟道金属氧化物半导体 (NMOS) 场效应晶体管 (FET) 驱动器,可控制电池 保护快速 FET 导通和关断次数

- 预充电 P 沟道场效应晶体管 (PFET) 驱动器 (用于 为显著耗尽的电池组进行限流预充电)

- 独立的数字使能充/放电控制

- 所需外部组件最少

- 基于可扩展外部电容的电荷泵,适用于不同范围内 的并行 FET

- 耐受高压(绝对最高电压为 100V)

- 使能电池组电压感测的内部开关

- 支持通用和独立的充/放电路径配置

- 设计为直接与 bq76940、bq76930 和 bq76920 电 池监控器搭配使用

- 电流消耗:

- 正常模式: 40µA

- 关断模式: < 10µA (最大值)

#### 2 应用

- 电动自行车 (eBike)、电动踏板车 (eScooter) 和电 动摩托车 (eMotorcycles)

- 储能系统和不间断电源 (UPS)

- 便携式医疗系统

- 无线基站电池系统

- 铅酸 (PbA) 备用电池

- 12V 至 48V 电池组

# 3 说明

bq76200 器件是一款低功耗、高侧 N 沟道系统。 高侧 保护可防止系统的接地引脚断开连接,同时允许电池组 与主机系统之间进行持续通信。 该器件的附加 P 沟道 FET 控制功能支持对深度耗尽型电池进行低电流预充 电,其 PACK+ 电压监控控制功能支持主机感测 PACK+ 电压。

独立的使能输入允许单独导通和关断 CHG 与 DSG FET,从而提供灵活的电池系统实施方案。

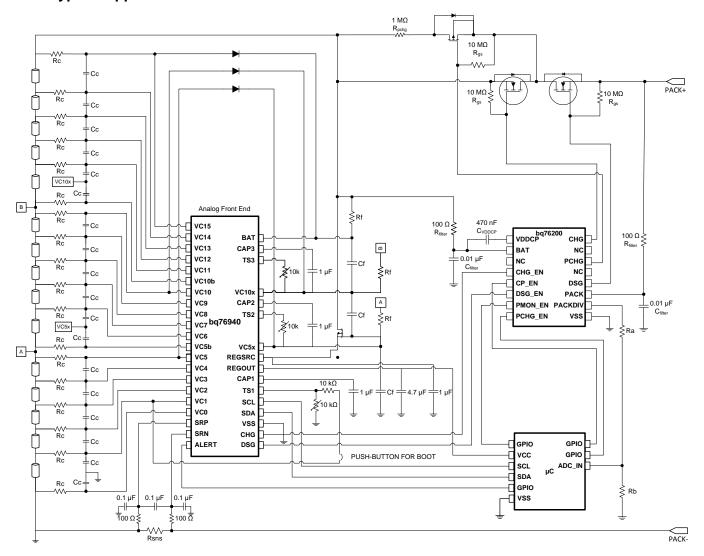

bq76200 器件可与配套的模拟前端器件搭配使用,例 如 bq76920/30/40 系列、3 节至 15 节电池模拟前端监 控以及主机微控制器或专用的充电状态 (SOC) 跟踪电 量监测计器件。

## 器件信息(1)

| 部件号     | 封装         | 封装尺寸 (标称值)               |

|---------|------------|--------------------------|

| bq76200 | TSSOP (16) | 5.00mm × 4.40mm × 1.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

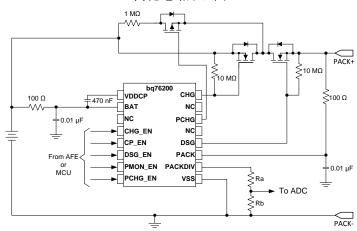

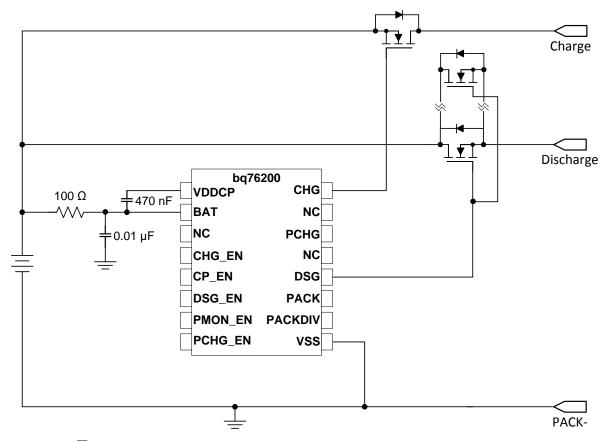

#### 简化电路原理图

#### www.ti.com.cn

# 目录

| 1 | 特性 1                                  |    | 7.3 Feature Description        | 9  |

|---|---------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                  |    | 7.4 Device Functional Modes    | 11 |

| 3 | ····································· | 8  | Application and Implementation | 12 |

| 4 | 修订历史记录 2                              |    | 8.1 Application Information    | 12 |

| 5 | Pin Configuration and Functions       |    | 8.2 Typical Applications       | 17 |

| 6 | Specifications4                       | 9  | Power Supply Recommendations   | 19 |

| • | 6.1 Absolute Maximum Ratings 4        | 10 | Layout                         | 19 |

|   | 6.2 ESD Ratings                       |    | 10.1 Layout Guidelines         | 19 |

|   | 6.3 Recommended Operating Conditions  |    | 10.2 Layout Example            | 19 |

|   | 6.4 Thermal Information               | 11 | 器件和文档支持                        | 21 |

|   | 6.5 Electrical Characteristics        |    | 11.1 文档支持                      | 21 |

|   | 6.6 Timing Requirements               |    | 11.2 社区资源                      | 21 |

|   | 6.7 Typical Characteristics           |    | 11.3 商标                        | 21 |

| 7 | Detailed Description 8                |    | 11.4 静电放电警告                    | 21 |

| • | 7.1 Overview 8                        |    | 11.5 Glossary                  | 21 |

|   | 7.2 Functional Block Diagram          | 12 | 机械、封装和可订购信息                    | 21 |

|   |                                       |    |                                |    |

# 4 修订历史记录

| 日期       | 修订版本 | 注释     |  |  |

|----------|------|--------|--|--|

| 2015年11月 | *    | 最初发布版本 |  |  |

ZHCSED8 - NOVEMBER 2015 www.ti.com.cn

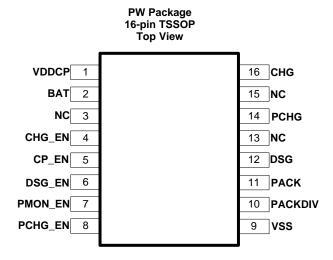

# 5 Pin Configuration and Functions

#### **Pin Functions**

|                        | PIN       |     | DESCRIPTION                                                                         |

|------------------------|-----------|-----|-------------------------------------------------------------------------------------|

| NAME                   | NO.       | I/O | DESCRIPTION                                                                         |

| BAT                    | 2         | Р   | Top of battery stack                                                                |

| CHG <sup>(2)</sup>     | 16        | 0   | Gate drive for charge FET                                                           |

| CHG_EN <sup>(3)</sup>  | 4         | I   | Charge FET enable                                                                   |

| CP_EN <sup>(3)</sup>   | 5         | I   | Charge pump enable (internally logic ORed with CHG_EN and DSG_EN signals)           |

| DSG <sup>(2)</sup>     | 12        | 0   | Gate drive for discharge FET                                                        |

| DSG_EN <sup>(3)</sup>  | 6         | 1   | Discharge FET enable                                                                |

| NC                     | 3, 13, 15 | _   | No connect. Leave the pin floating                                                  |

| PACK                   | 11        | Р   | Analog input from PACK+ terminal                                                    |

| PACKDIV <sup>(2)</sup> | 10        | 0   | PACK voltage after internal switch (connect to MCU ADC via resistor divider).       |

| PCHG <sup>(2)</sup>    | 14        | 0   | Gate drive for pre-charge FET                                                       |

| PCHG_EN <sup>(3)</sup> | 8         | 1   | Pre-charge FET enable                                                               |

| PMON_EN <sup>(3)</sup> | 7         | I   | Pack monitor enable (allows connection of internal switch between PACK and PACKDIV) |

| VDDCP                  | 1         | 0   | Charge pump output. Connect a capacitor to BAT pin. Do not load this pin.           |

| VSS                    | 9         | Р   | Ground reference                                                                    |

P = Power Connection, O = Digital Output, AI = Analog Input, I = Digital Input, I/OD = Digital Input/Output

Leave the pin float if function is not used.

Recommended to connect the pin to ground if function is not used.

# **STRUMENTS**

# **Specifications**

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                        | MIN             | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------|-----------------|-----|------|

| Input voltage range \/                | BAT, PACK (both under charge pump disabled condition)  | -0.3            | 100 | V    |

| Input voltage range, V <sub>IN</sub>  | CHG_EN, DSG_EN, PCHG_EN, PMON_EN, CP_EN <sup>(2)</sup> | -0.3            | 15  | V    |

| Output voltage range, V <sub>O</sub>  | CHG, DSG, PCHG, PACKDIV, VDDCP                         | -0.3            | 100 | V    |

| T <sub>FUNC</sub>                     | Functional Temperature                                 | -40             | 110 | °C   |

| Storage temperature, T <sub>stg</sub> |                                                        | <del>-</del> 65 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended* Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The enable inputs need to be current limited with max current not exceeding 5 mA.

6.2 ESD Ratings

|                    |                                                                     | VALUE | UNIT |

|--------------------|---------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | .,   |

| V <sub>(ESD)</sub> | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

Typical values stated where  $T_A = 25$ °C and VBAT = 48.8 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and BAT = 8 V to 75 V (unless otherwise noted)

|                    |                                  |                                         | MIN | NOM | MAX | UNIT |

|--------------------|----------------------------------|-----------------------------------------|-----|-----|-----|------|

| $V_{BAT}$          | Battery cell input sup           | oply voltage range                      | 8   |     | 75  | V    |

| $V_{PACK}$         | Charger/Load voltag              | e range                                 | 0   |     | 75  | V    |

| $V_{IN}$           | Input voltage range              | CHG_EN, DSG_EN, PCHG_EN, PMON_EN, CP_EN | 0   |     | 14  | V    |

| C <sub>VDDCP</sub> | Capacitor Between VDDCP and BAT  |                                         |     | 470 |     | nF   |

| T <sub>OPR</sub>   | Operating free-range temperature |                                         | -40 |     | 85  | °C   |

# 6.4 Thermal Information

|                           | THERMAL METRIC <sup>(1)</sup>                | TSSOP (PW) | LINUT |

|---------------------------|----------------------------------------------|------------|-------|

|                           | THERMAL METRIC**                             | 16 PINS    | UNIT  |

| R <sub>0</sub> JA, High K | Junction-to-ambient thermal resistance       | 106.8      | °C/W  |

| $R_{\theta JC(top)}$      | Junction-to-case(top) thermal resistance     | 41.5       | °C/W  |

| $R_{\theta JB}$           | Junction-to-board thermal resistance         | 51.8       | °C/W  |

| ΨЈΤ                       | Junction-to-top characterization parameter   | 3.8        | °C/W  |

| ΨЈВ                       | Junction-to-board characterization parameter | 51.3       | °C/W  |

| R <sub>0</sub> JC(bot)    | Junction-to-case(bottom) thermal resistance  | n/a        | °C/W  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

Typical values stated at  $T_A = 25$ °C and  $V_{(BAT)} = 48$  V. MIN/MAX values stated with  $T_A = -40$ °C to 85°C and  $V_{(BAT)} = 8$  to 75 V unless otherwise noted.

| PARAMETER                | DESCRIPTION                                                          | TEST CONDITION                                                                                                         | MIN | TYP | MAX | UNIT |

|--------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY AND L             | EAKAGE CURRENT                                                       |                                                                                                                        |     |     |     |      |

| I <sub>(BAT)</sub>       | NORMAL mode current <sup>(1)</sup>                                   | $C_{\text{(VDDCP)}} = 470 \text{ nF}, V_{\text{(BAT)}} = V_{\text{(PACK)}},$<br>$C_{\text{L}} = 10 \text{ nF}$         |     | 40  | 50  | μΑ   |

| Ishut                    | Sum of current into BAT and PACK pin                                 | Shutdown Mode, PACK = 0 V, BAT = 8 V                                                                                   |     | 6   | 9.5 | μΑ   |

| CHARGE PUMP              |                                                                      |                                                                                                                        |     |     |     |      |

| V <sub>(VDDCP)</sub>     | Charge pump voltage                                                  | No Load, $CP_EN = hi$ , $V_{(VDDCP)} - V_{(BAT)}$                                                                      | 9   |     | 14  | V    |

| t <sub>CPON</sub>        | Charge pump start up time from zero volt                             | $C_{(VDDCP)}$ = 470 nF, 10% to 90% of $V_{(VDDCP)}$                                                                    |     | 100 |     | ms   |

| INPUT ENABLE             | CONTROL SIGNALS                                                      |                                                                                                                        |     |     |     |      |

| $V_{IL}$                 | Digital low input level for CHG_EN, DSG_EN, PCHG_EN, CP_EN, PMON_EN  |                                                                                                                        |     |     | 0.6 | V    |

| V <sub>IH</sub>          | Digital high input level for CHG_EN, DSG_EN, PCHG_EN, CP_EN, PMON_EN |                                                                                                                        | 1.2 |     |     | V    |

| R <sub>PD</sub>          | Internal Pull down                                                   | VIN = 5 V                                                                                                              | 0.6 | 1   | 4   | МΩ   |

| CHARGE FET D             | RIVER                                                                |                                                                                                                        |     |     | ·   |      |

| V <sub>(CHGFETON)</sub>  | CHG gate drive voltage (on)                                          | $C_L$ = 10 nF, CHG_EN = Hi, $V_{(BAT)}$ = $V_{(PACK)}$ , $V_{(CHG)}$ - $V_{(BAT)}$                                     | 9   | 12  | 14  | V    |

| R <sub>(CHGFETON)</sub>  | CHG FET driver on resistance                                         | $V_{(VDDCP)} - V_{(BAT)} = 12 \text{ V, CHG\_EN} = \text{Hi,}$<br>$V_{(BAT)} = V_{(PACK)}$                             |     | 1.1 |     | kΩ   |

| R <sub>(CHGFETOFF)</sub> | CHG FET driver off resistance                                        | $V_{\text{(VDDCP)}} - V_{\text{(BAT)}} = 12 \text{ V, CHG\_EN} = \text{Lo,}$<br>$V_{\text{(BAT)}} = V_{\text{(PACK)}}$ |     | 0.3 |     | kΩ   |

| DISCHARGE FE             | T DRIVER                                                             |                                                                                                                        |     |     |     |      |

| V <sub>(DSGFETON)</sub>  | DSG gate drive voltage (on)                                          | $C_L$ = 10 nF, DSG_EN = Hi, $V_{(BAT)}$ = $V_{(PACK)}$ , $V_{(DSG)} - V_{(PACK)}$                                      | 9   | 12  | 14  | V    |

| R <sub>(DSGFETON)</sub>  | DSG FET driver on resistance                                         | $V_{(VDDCP)} - V_{(BAT)} = 12 \text{ V, DSG\_EN} = \text{Hi,}$<br>$V_{(BAT)} = V_{(PACK)}$                             |     | 3.5 |     | kΩ   |

| R <sub>(DSGFETOFF)</sub> | DSG FET driver off resistance                                        | $V_{(VDDCP)} - V_{(BAT)} = 12 \text{ V, DSG\_EN} = \text{Lo,}$<br>$V_{(BAT)} = V_{(PACK)}$                             |     | 1   |     | kΩ   |

| PRECHARGE F              | ET DRIVER                                                            |                                                                                                                        |     |     |     | -    |

| V <sub>(PCHGFETON)</sub> | PCHG gate drive voltage (on)                                         | $V_{(PACK)} > 17 \text{ V}, V_{(BAT)} < V_{(PACK)}, V_{(PACK)} - V_{(PCHG)}$                                           | 5   | 12  | 14  | V    |

| PACK MONITO              | R (PACK_DIV)                                                         | ·                                                                                                                      |     |     |     |      |

| R <sub>(PMONFET)</sub>   | On resistance of internal FET (R between PACK and PACKDIV)           | PMON_EN = hi                                                                                                           | 1.5 | 2.5 | 3.5 | kΩ   |

<sup>(1)</sup> NORMAL mode is defined as CHG\_EN = Hi, DSG\_EN = Hi, CP\_EN = Hi, PCHG\_EN = Lo, PMON\_EN = Lo. Current value is averaged out over time.

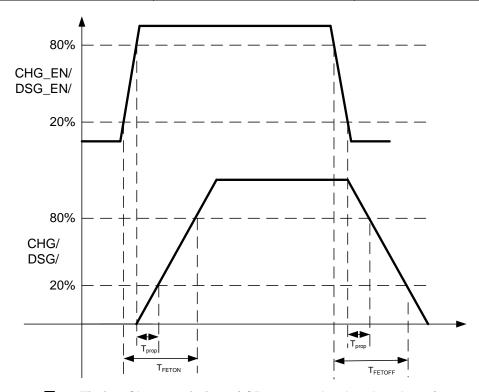

# 6.6 Timing Requirements

| Parameter              | Description                                  | TEST CONDITION                                                                                                    | MIN | TYP | MAX | UNIT |

|------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| tCHGFETON              | CHG on rise time + propagation delay         | $C_L$ = 10 nF, (20% of CHG_EN from Lo to Hi) to (80% of V <sub>(CHGFETON)</sub> ), CP_EN = Hi, (CP is already on) |     | 27  | 45  | μs   |

| tCHGFETOFF             | CHG off fall time + progation delay          | $C_L$ = 10 nF, (80% of CHG_EN from Hi to Lo) to (20% of $V_{(CHGFETON)}$ ) , CHG_EN = Hi to Lo                    |     | 7   | 20  | μs   |

| t <sub>PROP</sub> _CHG | CHG EN to CHG output                         | C <sub>L</sub> = 10 nF, CP_EN = Hi, (CP is already on), see timing diagram                                        |     | 0.5 |     | μs   |

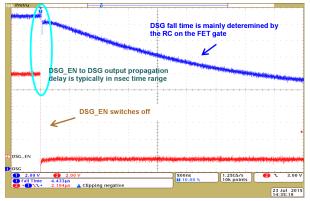

| t <sub>DSGFETON</sub>  | DSG on rise time + propagation delay         | $C_L$ = 10 nF, (20% of DSG_EN from Lo to Hi) to (80% of V <sub>(DSGFETON)</sub> ), CP_EN = Hi, (CP is already on) |     | 24  | 50  | μs   |

| t <sub>DSGFETOFF</sub> | DSG off fall time + propagation delay        | $C_L$ = 10 nF, (80% of DSG_EN from Hi to Lo) to (20% of V <sub>(DSGFETON)</sub> )                                 |     | 7   | 20  | μs   |

| t <sub>PROP_DSG</sub>  | DSG EN to DSG output propagation delay       | C <sub>L</sub> = 10 nF, CP_EN = Hi, (CP already on), see timing Diagram                                           |     | 0.5 |     | μs   |

| t <sub>PCHGOFF</sub>   | PCHG turn off time + propagation delay       | $C_L$ = 1 nF, (20% of PCHG_EN from Hi to Lo) to (80% of V <sub>(PCHGFETON)</sub> )                                |     | 30  | 55  | μs   |

| t <sub>PCHGON</sub>    | PCHG turn on time + propagation delay        | $C_L$ = 1 nF, (80% of PCHG_EN from Lo to Hi) to (20% of $V_{(PCHGFETON)}$ )                                       |     | 34  | 55  | μs   |

| t <sub>PROP_PCHG</sub> | PCH_EN to PCHG propagation delay             | C <sub>L</sub> = 1 nF                                                                                             |     | 0.5 |     | μs   |

| t <sub>PROP_PMON</sub> | PMON_EN and PACKDIV = PACK propagation delay |                                                                                                                   |     | 0.5 |     | μs   |

图 1. Timing Characteristics - ( CP assumed to be already On)

www.ti.com.cn

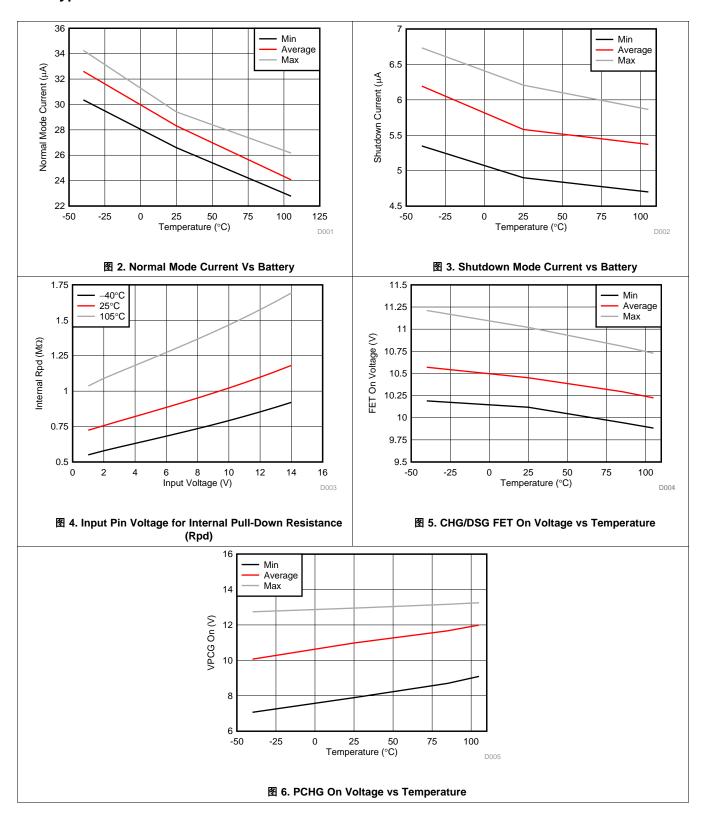

# 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

## 7 Detailed Description

#### 7.1 Overview

The bq76200 device is a low-power, high-side, N-Channel MOSFET driver for battery-pack protection systems, allowing a low-side battery-protection system to be implemented into a high-side protection system.

High-side charge/discharge FETs offer a huge advantage versus their low-side counterparts; with high-side implementation, a system-side processor can always communicate with the monitor or micro-controller (MCU) within the battery pack, regardless of whether the FETs are on or off — this is not easily supported in a low-side switching architecture due to the lack of a shared ground reference. One key benefit of an ever-present communication link is the ability to read out critical pack parameters despite safety faults, thereby enabling the system to assess pack conditions before determining if normal operation may resume.

The device allows independent control on charging and discharge via the digital enable pins. The device has integrated charge pump which is enabled by the CP\_EN pin. The enable inputs, CHG\_EN, DSG\_EN, and PCHG\_EN control the CHG, DSG, and PCHG FET gate drivers, respectively. The enable inputs can be connected to low-side FET driver outputs of an Analog Front End (AFE) such as Texas Instruments bq769x0 series, a general purpose microcontroller, or dedicated battery pack controller such as the bq783xx series.

In normal mode, the AFE or MCU enables the CHG\_EN and DSG\_EN, turning on the CHG and DSG FET drivers to connect the battery power to the PACK+ terminal. When a fault is detected by the AFE or the microcontroller, it can disable the CHG\_EN and/or DSG\_EN to open the charge or discharge path for protection. Note that when either the CHG\_EN or DSG\_EN is enabled, the charge pump will be automatically enabled even if the CP\_EN is in the disable state. It is recommended to enable the charge pump via CP\_EN pin during system start-up to avoid adding the  $t_{CPON}$  time into the FET switching time during normal operation.

A lower charging current is usually applied to a deeply depleted battery pack. The bq76200 PCHG\_EN input provides an option to implement a P-Channel MOSFET pre-charge path (current-limited path) in the battery pack.

An AFE usually provides individual cell voltages and/or battery stack voltage measurements, but it is not necessary to have PACK+ voltage measurement. The bq76200 PMON\_EN pin, when enabled, will connect the PACK+ voltage onto the PACKDIV pin, which is connected to an external resistor divider to scale down the PACK+ voltage. This scaled down PACK+ voltage can be connected to a microcontroller's ADC input for voltage measurement. The system can use this information for charger detection or to implement advanced charging control.

For safety purposes, all the enable inputs are internally pulled down. If the AFE or microcontroller is turned off, or if the PCB trace is damaged, the internal pull down of the enable inputs will keep CHG, DSG, PCHG in an off state and the PACK+ voltage does not switch onto the PACKDIV pin.

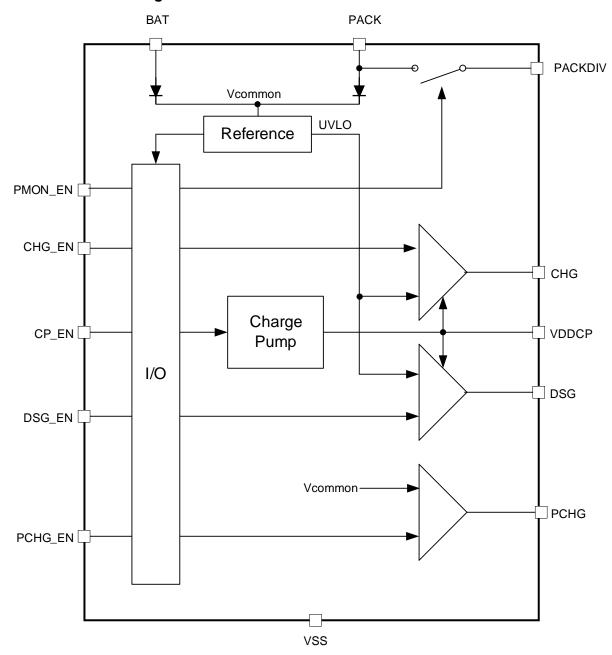

# 7.2 Functional Block Diagram

图 7. Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 Charge Pump Control

The bq76200 device has an integrated charge pump. A minimum of 470-nF capacitor is required on the  $V_{(VDDCP)}$  pin to the BAT pin to ensure proper function of the charge pump. If the  $V_{(VDDCP)}$  capacitor is disconnected, a residual voltage could reside at the CHG and/or DSG output if CHG\_EN and/or DSG\_EN are enabled. Such a fault condition can put the external FETs in high Rdson state and result in FET damage.

# Feature Description (接下页)

The  $V_{(VDDCP)}$  capacitor can be scaled up to support more FETs in parallel (such as high-total FET-gate capacitance) than the value specified in the electrical characteristics table. A higher VDDCP capacitance results in longer  $t_{CPON}$  time. See the *Application Information* section for more information. Note that probing the VDDCP pin may increase the loading on the charge pump and result in lower measurement value than the  $V_{(VDDCP)}$  specification. Using higher impedance probe can reduce such effect on the measurement.

The charge pump is controlled by CP\_EN and also OR'ed with the CHG\_EN and DSG\_EN inputs. This means by enabling CHG\_EN or DSG\_EN alone, the charge pump will automatically turn on even if the CP\_EN pin is disabled. The PCHG\_EN controls the PCHG pin, which is a P-channel FET driver and does not require the function of the charge pump. The charge pump is turned off by default. When CP\_EN is high, the charge pump turns on regardless of the status of the CHG\_EN and DSG\_EN inputs.

When CP\_EN is enabled, the charge pump voltage starts to ramp up. Once the voltage is above an internal UVLO level, about 9-V typical above  $V_{BAT}$ , the charge pump is considered on. The charge pump voltage should continuously ramp to the  $V_{(VDDCP)}$  level. If the CHG\_EN and/or DSG\_EN is enabled, the CHG and/or DSG voltage will starts to turn on after the charge pump voltage is above the UVLO level, and ramp up along the charge pump voltage to the  $V_{(VDDCP)}$  level. Otherwise, the CHG and DSG do not turn on if the charge pump voltage fails to ramp up above UVLO. For example, if the  $C_{(VDDCP)}$  is not scaled properly to support the number of FETs in parallel, the heavy loading would prevent the charge pump to ramp up above UVLO. CHG and DSG would not be turned on in this case.

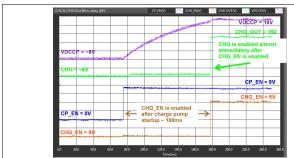

When CHG\_EN and/or DSG\_EN is enabled after the charge pump is fully turned on, the CHG\_EN-enable to CHG-on delay (or DSG\_EN-enable to DSG-on delay) is simply the sum of (tprop + FET rise time). A system configuration example for this scenario will be connecting the CP\_EN to the host MCU, enable CP\_EN at system start-up and keep the CP\_EN enabled during normal operation. This is the recommended configuration, because the charge pump ramp-up time,  $t_{CPON}$ , becomes part of the system start-up time and does not add onto the FET switch delay during normal operation.

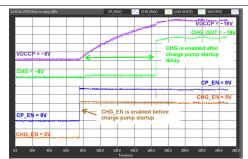

If CP\_EN is not used (it is highly recommended to connect the CP\_EN to ground), the charge pump on- and off-state is controlled by CHG\_EN or DSG\_EN. The CHG or DSG output will only be on after the charge-pump voltage is ramped up above UVLO. This means the CHG\_EN-enable to CHG-on delay (or DSG\_EN-enable to DSG-on delay) will be ( $t_{CPON}$  +  $t_{CPON}$

The charge pump is turned off when CP\_EN AND CHG\_EN AND DSG\_EN signals are all low. The charge pump is not actively driven low and the voltage on the  $V_{(VDDCP)}$  capacitor bleeds off passively. If any of the CP\_EN, CHG\_EN, or DSG\_EN signals is switched high again while the  $V_{(VDDCP)}$  capacitor is still bleeding off its charge, the charge pump start up time,  $t_{CPON}$ , will be shorter.

## 7.3.2 Pin Enable Controls

The bq76200 has four digital enable inputs that control the state of associated output signals as defined in the following table. The  $V_{IH}$  and VIL levels of these enable pins are low enough to work with most MCUs. At the same times, the pins have high enough tolerant to allow direct control from an AFE FET driver. This gives system maker a flexible option to architect the battery pack configuration.

| INPUT PIN | ASSOCIATED OUTPUT PIN | DESCRIPTION            |  |

|-----------|-----------------------|------------------------|--|

| CHG_EN    | CHG                   | Charge FET control     |  |

| DSG_EN    | DSG                   | Discharge FET control  |  |

| PCHG_EN   | PCHG                  | Pre-charge FET control |  |

| PMON_EN   | N PACKDIV Pa          |                        |  |

ON

Ηi

#### 7.3.2.1 External Control of CHG and DSG Output Drivers

The CHG\_EN and DSG\_EN pins provide direct control of the CHG and DSG FET driver. 表 1 summarizes the CHG and DSG statute with respect to the CP\_EN, CHG\_EN and DSG\_EN inputs.

|              | x 11 0110 and 200 mm Noopoot to 011, 01101, and 2001. |              |               |               |               |  |  |  |  |

|--------------|-------------------------------------------------------|--------------|---------------|---------------|---------------|--|--|--|--|

| CP_EN        | CHG_EN                                                | DSG_EN       | CHARGE PUMP   | CHG           | DSG           |  |  |  |  |

| Lo (default) | Lo (default)                                          | Lo (default) | OFF (default) | OFF (default) | OFF (default) |  |  |  |  |

| Lo           | Lo                                                    | Hi           | ON            | OFF           | ON            |  |  |  |  |

| Lo           | Hi                                                    | Lo           | ON            | ON            | OFF           |  |  |  |  |

| Lo           | Hi                                                    | Hi           | ON            | ON            | ON            |  |  |  |  |

| Hi           | Lo                                                    | Lo           | ON            | OFF           | OFF           |  |  |  |  |

| Hi           | Lo                                                    | Hi           | ON            | OFF           | ON            |  |  |  |  |

| Hi           | Hi                                                    | Lo           | ON            | ON            | OFF           |  |  |  |  |

|              |                                                       |              |               |               |               |  |  |  |  |

ON

ON

表 1, CHG and DSG with Respect to CP EN, CHG EN, and DSG EN

### 7.3.2.2 External Control of PCHG Output Driver

The PCHG output driver is designed to drive a P-channel FET and is controlled by the PCHG\_EN pin. The PCHG driver provides an option to implement a separate charging path with a P-channel FET to charge the battery when the cells are deeply depleted. A resistor should be added in series to the P-channel pre-charge FET to limit the charging current. A pre-charge current is usually at or less than 1/20 of the normal charge current if the charger does not support lower current pre-charge. Refer to the battery cell specification from the cell manufacturer charging for the appropriate current limit.

| PCHG_EN      | PCHG          |  |  |  |

|--------------|---------------|--|--|--|

| Lo (default) | OFF (default) |  |  |  |

| Hi           | ON            |  |  |  |

#### 7.3.2.3 Pack Monitor Enable

The bq76200 device provides an internal-switch control to post the PACK+ voltage on to the PACKDIV pin. A resistor divider can be connected to the PACKDIV pin externally to divide down the PACK+ voltage into a measurable range of an MCU. The PMON\_EN controls the internal switch between PACK pin and PACKDIV pin. The internal switch has an on resistance of  $R_{(PMONFET)}$ . The external resistor divider for PACKDIV pin should be selected to avoid exceeding the absolute maximum of the PACKDIV pin and should also keep the loading current < 500  $\mu$ A. If this function is not used, the PACKDIV pin should leave floating. To reduce power consumption, the PMON\_EN should be enabled only when PACK+ voltage measurement is needed.

| PMON_EN      | PACKDIV            |  |  |  |

|--------------|--------------------|--|--|--|

| Lo (default) | DISABLED (default) |  |  |  |

| Hi           | ENABLED            |  |  |  |

#### 7.4 Device Functional Modes

- In NORMAL mode, the bq76200 charge pump is turned on by enabling either CP\_EN, CHG\_EN, or DSG\_EN.

In this mode, typically the CHG and DSG outputs are driven to V<sub>(BAT)</sub> + V<sub>(VDDCP)</sub>.

- In SHUTDOWN mode, the bq76200 is completely powered down. When CHG\_EN, DSG\_EN, and CP\_EN are driven low, the device enters SHUTDOWN mode, and the outputs are driven low.

| DEVICE MODES | CONDITION                                                                        |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| NORMAL       | CHG_EN = Hi, DSG_EN = Hi, CP_EN = Hi, PCHG_EN = don't care, PMON_EN = don't care |  |  |  |  |  |

| SHUTDOWN     | CHG_EN = Lo, DSG_EN = Lo, CP_EN = Lo, PCHG_EN = Lo, PMON_EN = Lo                 |  |  |  |  |  |

# TEXAS INSTRUMENTS

## 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The bq76200 device is a high-side NMOS FET driver with integrated charge pump. The device can convert a low-side battery protection system into a high-side protection system, allowing the battery monitor device or battery MCU to always maintain communication to the host system regardless if the protection FETs are on or off. The device provides independent enables to control charge and discharge of a battery pack.

The following section highlights several recommended implementations when using this device. A detail bq76200 Application Note, SLVA729, is available at www.ti.com.

# 8.1.1 Recommended System Implementation

# 8.1.1.1 The bq76200 is a Slave Device

The bq76200 is a FET driver. It controls the output pins (CHG, DSG, PCHG, and PACKDIV) according to the input pin (CHG\_EN, DSG\_EN, PCHG\_EN, CP\_EN, and PMON\_EN) status. The device does not validate if the inputs should or should not be turned on or off. For example, if both CHG\_EN and PCHG\_EN are enabled, bq76200 will turn on both CHG and PCHG simultaneously, enabling two charging paths to the system. The system designer should avoid undesirable enable combination via schematic, AFE, or host MCU implementation.

#### 8.1.1.2 Flexible Control via AFE or via MCU

The bq76200 device has simple-logic input pins (CHG\_EN, DSG\_EN, PCHG\_EN, CP\_EN, and PMON\_EN) that can accept a control signal from any MCU I/O. At the same time, the input pins are designed to tolerate high voltage signal such as the FET driver output from an AFE. This flexibility allows a mix of control input driving from AFE and/or MCU to optimize the system design.

For example, it is recommended to control the CP\_EN pin via MCU which the system can turn on the charge pump at system start-up, excluding the extra FET delay due to charge pump voltage ramping. On the other hand, the CHG\_EN and DSG\_EN can be driven by the AFE FET driver output, especially if the AFE has hardware protection features (such as the bq76920/30/40 family), to optimize the FET reaction time.

All the input pins have internal pull-down resistor. The outputs are default to be off if any of the input pins are at high-Z state.

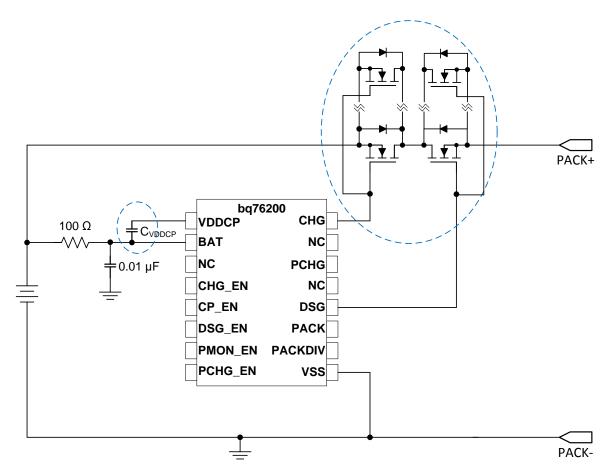

#### 8.1.1.3 Scalable VDDCP Capacitor to Support Multiple FETs in Parallel

The bq76200 requires a minimum 470-nF capacitor to be connected between the VDDCP pin and BAT pin in order to turn on the integrated charge pump. The Electrical Characteristics Specification of this document specified the device performance based on 10 nF loading with 470-nF VDDCP capacitor. The loading capacitance varies with FET choices, number of FETs in use, and in parallel and simultaneous switching versus sequential switching of CHG and DSG FET.

The more FETs that are in parallel, the higher the loading capacitance. Similarly, simultaneously switching of the CHG and DSG FET loads down the charge pump more than sequentially switching both FETs. Eventually, the loading capacitance can exceed the supported range of a 470-nF VDDCP capacitor. A > 470-nF VDDCP capacitor can be used to support higher-loading capacitance.

图 8. Scale C<sub>VDDCP</sub> to Support Multiple FETs in Parallel (Partial Schematic Shown)

Based on test results, 470-nF VDDCP capacitor can support up to approximately 30-nF loading capacitance. Using a 470-nF/20-nF ratio (to include some design margin), a 2.1- $\mu$ F VCCDP capacitor can support up to ~90 nF loading capacitance. Note that a larger VDDCP capacitor increases the charge pump start up time; a higher loading capacitance increases the FET on and off time. System designers should test across the operation range to ensure the design margin and system performance. Refer to the bq76200 Application note for more test results.

Also notice that any damage or disconnection of the VDDCP capacitor during operation can leave a residual voltage on the FET driver output if the inputs are enabled. This can result in putting the external FETs in a high-Rdson state and cause FET damage.

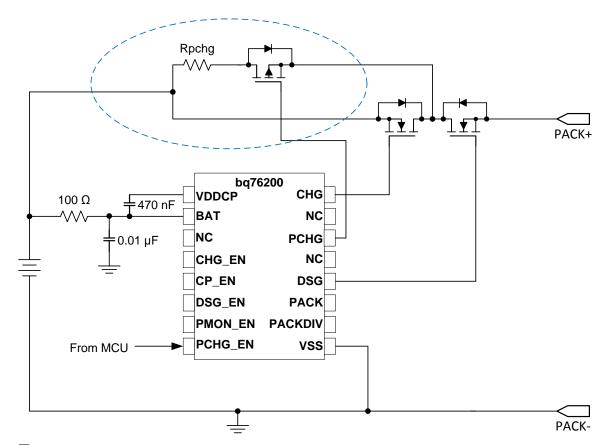

#### 8.1.1.4 Pre-Charge and Pre-Discharge Support

For a deeply depleted battery pack, a much lower charging current, for example, a C/10 rate, is usually used to pre-charge the battery cells. This allows the passivating layer of the cell to be recovered slowly (the passivating layer might be dissolved in the deep discharge state).

The bq76200 has a PCHG output to drive an external P-channel FET to support battery pre-charge. In this scenario, the external P-channel FET is placed in parallel with the CHG FET and a power resistor can be connected in series of the P-channel FET to limit the charging current during the pre-charge state. The MCU can be used to control the PCHG EN pin to determine the entry and exit of the pre-charge mode.

图 9. P-channel FET in Parallel With CHG FET for Pre-Charging (Partial Schematic Shown)

Alternatively, the CHG pin can also be used to pre-charge a battery pack given if the charging current is controlled by the system (i.e. does not require external component to limit the charging current such as a smart charger) and the battery stack voltage is higher than minimum operation voltage of the bq76200 (i.e. the charge pump can start to turn on the CHG FET). PCHG should leave floating if it is not used in the application.

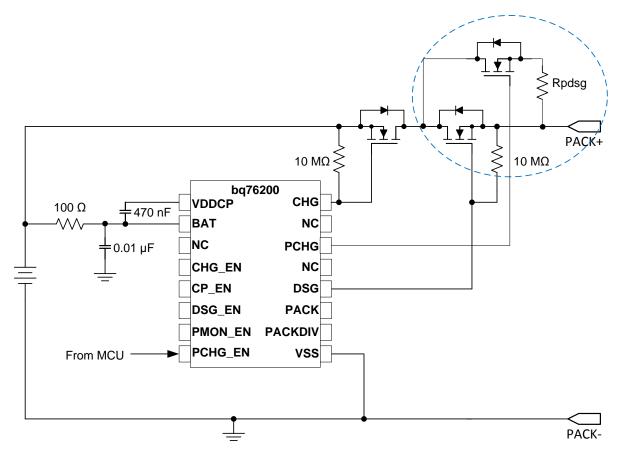

The PCHG output can be used to pre-discharge a high-capacitive system. For example, a load removal can be one of the recovery requirements after a discharge related fault has been detected. In a high-capacitive system, the residual voltage at the system side can take a significant time to bleed off. This results in an additional delay in fault recovery. The PCHG output can be used to control an external P-channel FET placed in parallel with the DSG FET to pre-discharge the residual voltage in order to speed up the fault recovery process.

图 10. P-channel FET in Parallel with DSG FET for Pre-Discharging (Partial Schematic Shown)

#### 8.1.1.5 Optional External Gate Resistor

The CHG and DSG have certain internal on and off resistance. However, an optional external gate resistor can be added to CHG and/or DSG FET to slow down the FET on and off timing.

#### 8.1.1.6 Separate Charge and Discharge paths

In some systems, the charging current might be significantly lower than the discharge current. In such systems, the system designer may prefer to implement a separate charge and discharge paths in which the number of FET in parallel for charge and discharge can be different to reduce to BOM cost.

图 11. Separate Charge and Discharge Paths (Partial Schematic Shown)

# 8.2 Typical Applications

# 8.2.1 Design Requirements

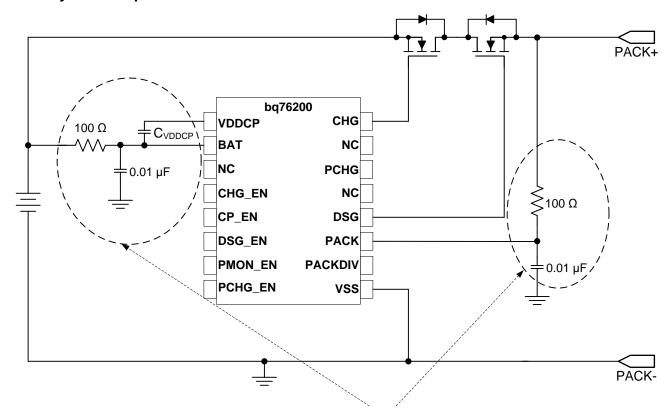

For this design example, use the parameters listed in 表 2.

# 表 2. Design Parameters

| PARAMETER EXTERNAL COMPONENT            |                     | NOTE                                                                                                                                                                                        |  |  |  |

|-----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BAT and PACK Filters                    | Rfilter and Cfilter | Recommended to use 100 $\Omega$ and 0.01 $\mu F.$                                                                                                                                           |  |  |  |

| VDDCP capacitor                         | $C_{VDDCP}$         | A minimum of 470 µF is required. A higher value can be used to support higher-loading capacitance. See Recommended Implementation and bq76200 Application Note () for details.              |  |  |  |

| PACKDIV resistor divider Ra and Rb      |                     | Based on the max PACK voltage of the application, calculate the total value of (Ra + Rb) that can keep the PACKDIV current below 500 $\mu$ A.                                               |  |  |  |

| CHG, DSG, PCHG gate-source resistor Rgs |                     | Recommended to use 10 $M\Omega$ . A different Rgs value may change the loading level of the charge pump. System designer should perform thorough system testing if a different Rgs is used. |  |  |  |

# TEXAS INSTRUMENTS

#### 8.2.2 Detailed Design Procedure

- 1. Determine if CP\_EN pin will be driven by MCU. It is highly recommended to use CP\_EN to turn on the charge pump at system start-up. However, it is not a must to operate the bq76200 to switch on CHG and DSG pins. System designer should ensure the FET's turn on time is acceptable during normal operation if CP\_EN is not enabled at system startup.

- Select the correct VDDCP capacitance. Scaling up the VDDCP capacitance allows support for a higher number of FETs in parallel. This test result of various parallel FETs versus VDDCP capacitance in the bq76200 application is for general reference only. System designer should always validate their design tolerant across operation temperature range.

- 3. If the PMON\_EN is used, the PACKDIV resistor divider, Ra and Rb, must be selected to satisfy (Ra+Rb) < 500uA, AND [Rb/(Ra + Rb)] < (max ADC input range)/(max PACK+ voltage). For example, In a 48V system, if the max charger voltage is 50.4V and a MCU's max ADC input is 3V. To meet both (Ra + Rb) < 500uA, AND [Rb/(Ra + Rb)] < (3V/50.4V) requirements, the Ra value might be  $100~k\Omega$  or less and Rb value might be  $6~K\Omega$  or less.

- 4. Follow the application schematic (see *Typical Applications*) to connect the device.

## 8.2.3 Application Curves

CHG output reacts to the CHG\_EN signal immediately. Similar behavior applies to DSG pin.

图 12. CHG\_EN Switched On After Charger Pump Turns On and is Stable

CHG output reacts to the CHG\_EN signal after charge pump startup delay. Similar behavior applies to DSG pin.

图 13. CHG\_EN Enabled Before Charge Pump is Turned On

With 10 nF loading and no Rgs on DSG output. Note the time scale was 800ns/div. Hence, the DSG waveform above was basically the DSG FET fall time

图 14. DSG\_EN to DSG Output Propagation Delay

# 9 Power Supply Recommendations

The maximum recommended operation voltage on the BAT and PACK pins is 75 V. The charge pump, when it turns on, will add 14 V maximum voltage on top of the BAT or PACK voltage to the device, pushing the total device voltage to approximately 89 V.

The bq76200 has high voltage (100 V) tolerant pins, but system designer should take into account the worse-case transient voltage and the maximum charge pump on voltage to determine the maximum voltage applying to BAT and PACK pins.

# 10 Layout

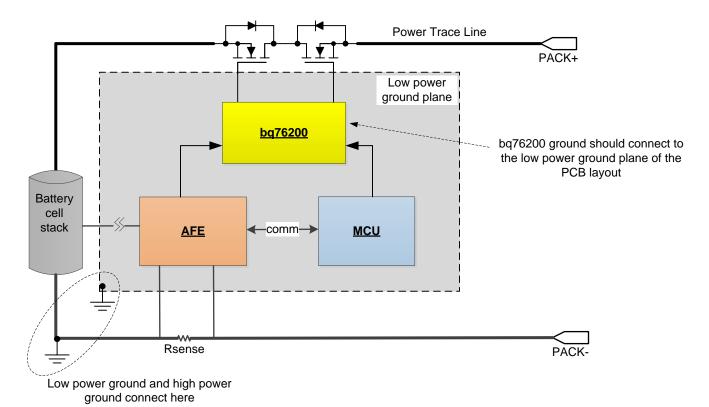

## 10.1 Layout Guidelines

For the following procedure, see \( \bar{2} \) 15 and \( \bar{2} \) 16.

- 1. Place C<sub>VDDCP</sub> capacitor close to the device.

- 2. Place BAT and PACK RC filters close to the device.

- 3. Generally, a typical system using an AFE, MCU, and bq76200 usually have a high-current ground trace/plane and low-current ground plane in the PCB layout. If so, the bq76200 ground should be connected to the low-current ground plane of the PCB layout to remove noise affecting the ENABLE signals.

#### 10.2 Layout Example

Place these components close to the device pins

图 15. Place C<sub>VDDCP</sub> and Filter Components Close to Device

# Layout Example (接下页)

图 16. Connect bq76200 to Low Power Ground Plane on PCB Layout

ZHCSED8 - NOVEMBER 2015 www.ti.com.cn

## 器件和文档支持

#### 11.1 文档支持

#### 11.1.1 相关文档

如需相关文档,请参见《ba76200 FET 配置测试结果》(文献编号: SLVA729)。

# 11.2 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 商标

E2E is a trademark of Texas Instruments.

#### 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可 能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可 能会导致器件与其发布的规格不相符。

#### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

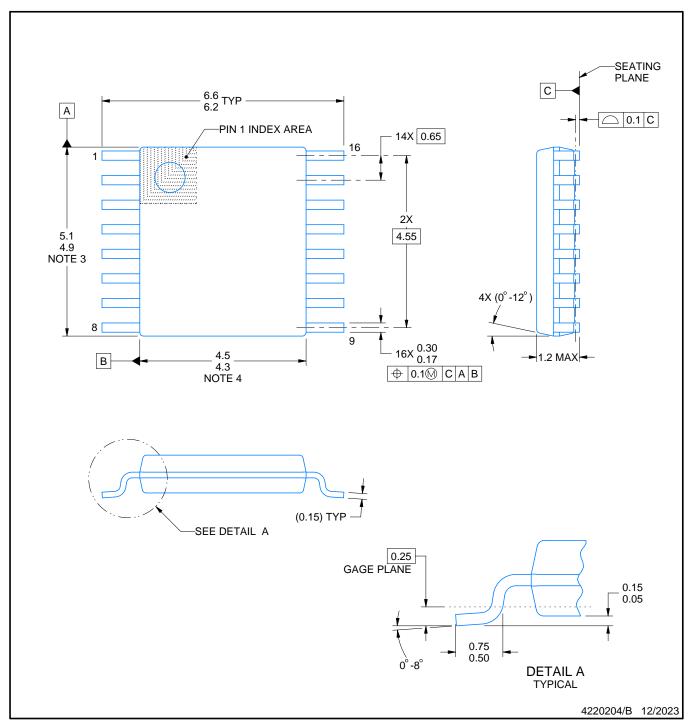

# 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不 对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 14-Jul-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| BQ76200PW             | Active | Production    | TSSOP (PW)   16 | 90   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | BQ7620B      |

| BQ76200PW.A           | Active | Production    | TSSOP (PW)   16 | 90   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | BQ7620B      |

| BQ76200PWR            | Active | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | BQ7620B      |

| BQ76200PWR.A          | Active | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | BQ7620B      |

| BQ76200PWRG4          | Active | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | BQ7620B      |

| BQ76200PWRG4.A        | Active | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | BQ7620B      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 14-Jul-2025

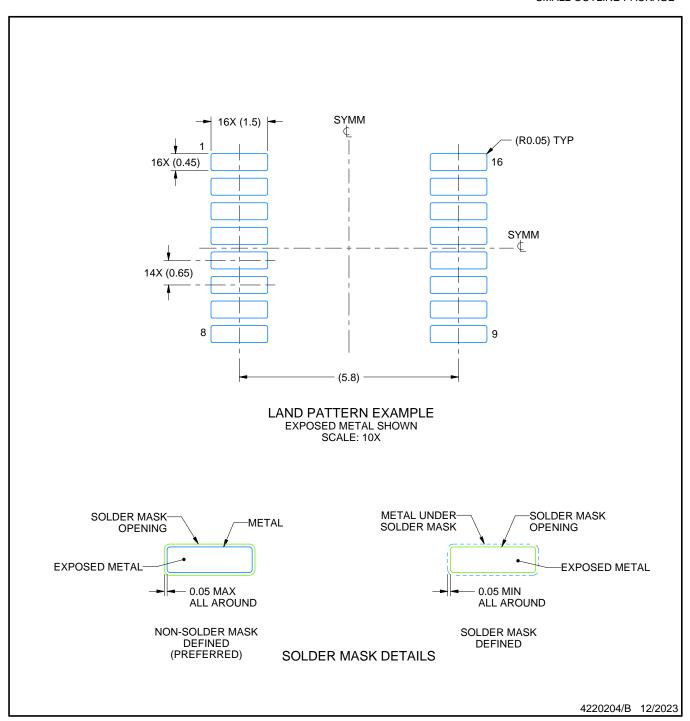

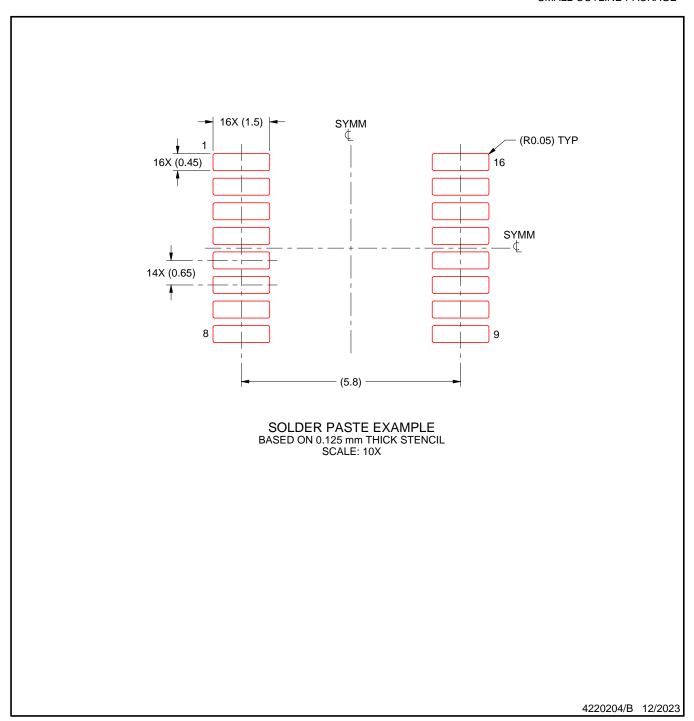

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司