AMC7834

ZHCSDL7B - NOVEMBER 2014 - REVISED MARCH 2016

# AMC7834 具有温度、电流和电压监控功能的 12 位集成功率放大器监视和控制系统

#### 1 特性

- 8 个具有可编程范围的单调性 12 位数模转换器 (DAC)

- 4 个双极 DAC:

- -4V 至 1V, -5V 至 0V 以及 0V 至 5V

- 4 个单极 DAC:0V 至 5V 以及 2.5V 至 7.5V

- 高电流驱动能力: 高达 ±10mA

- 可选钳位电压

- 多通道 12 位逐次逼近寄存器 (SAR) 模数转换器 (ADC)

- 4 个外部模拟输入: 0V 至 2.5V 范围

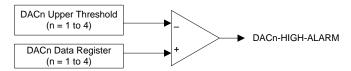

- 4个用于双极 DAC 监视的内部输入

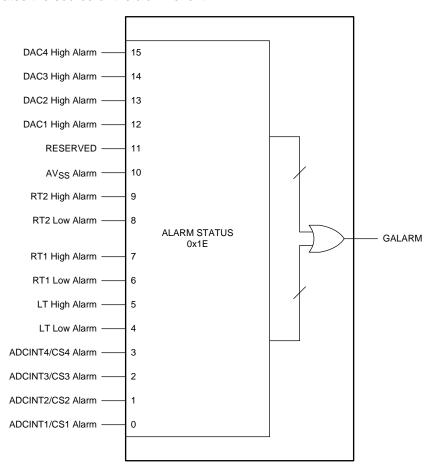

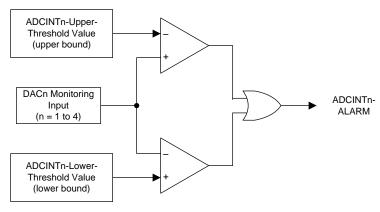

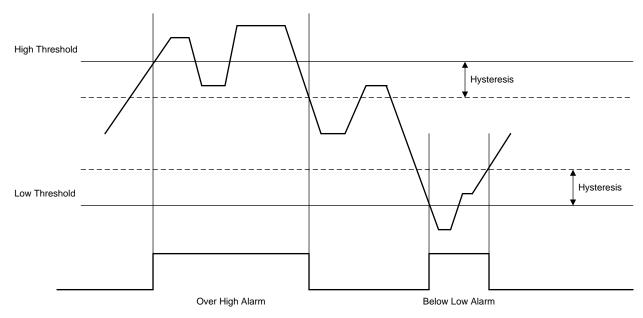

- 可编程超范围警报

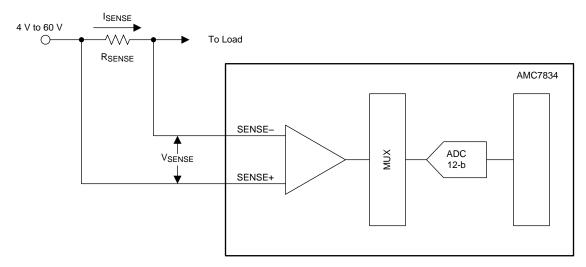

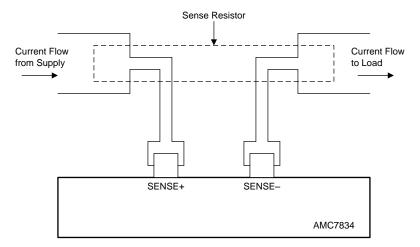

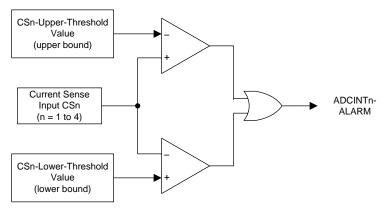

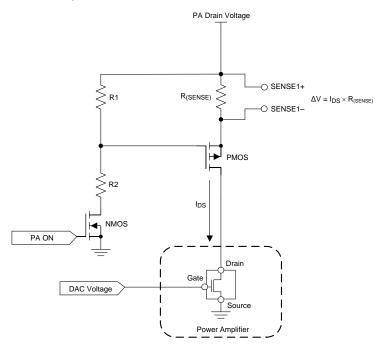

- 4 个高侧电流感测放大器

- 共模电压: 4V 至 60V

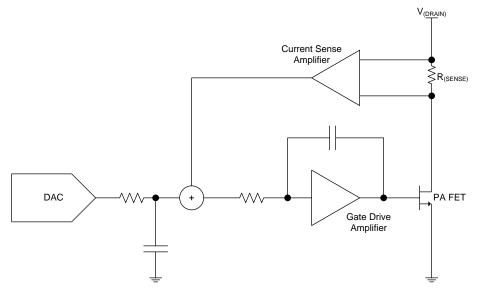

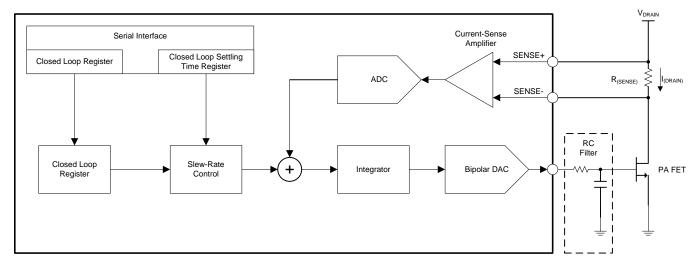

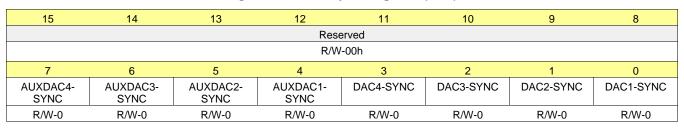

- 可选闭环漏极电流控制器操作

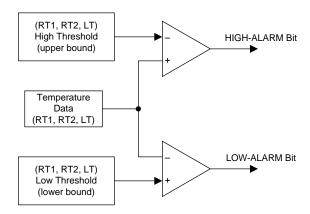

- 温度感测功能

- 内部温度传感器

- 2个远程温度二极管驱动器

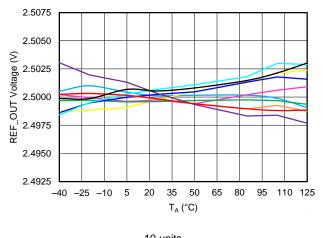

- 2.5V 内部基准电压

- 4 个通用 I/O 端口 (GPIO)

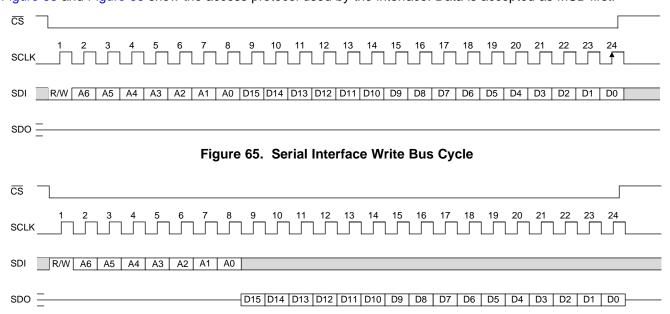

- 低功耗 SPI 兼容串行接口

- 4线模式, 1.7V至 3.6V工作电压

- 工作温度范围: -40°C 至 +125°C

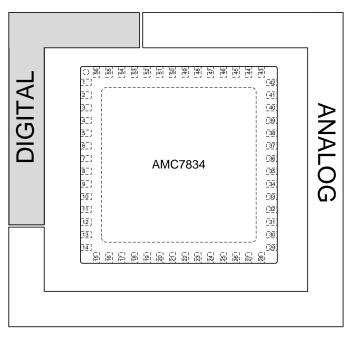

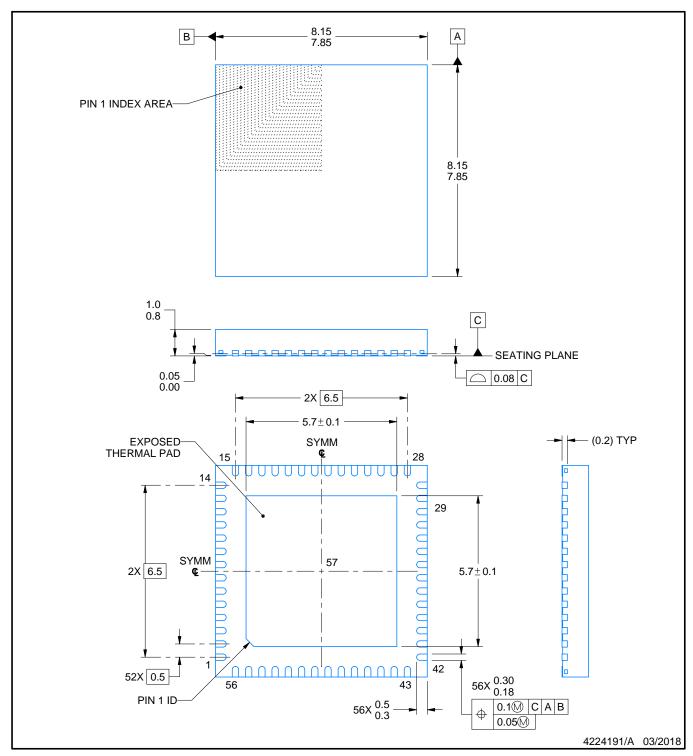

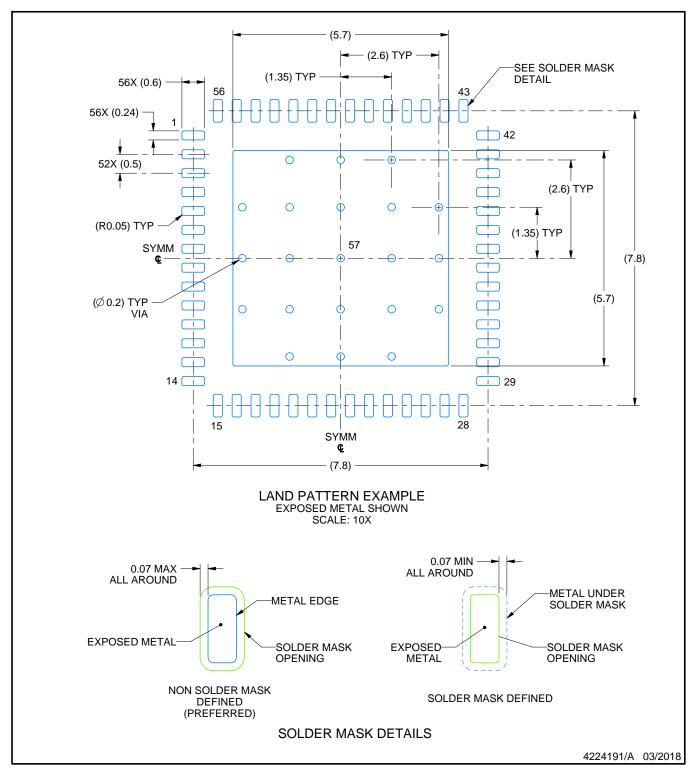

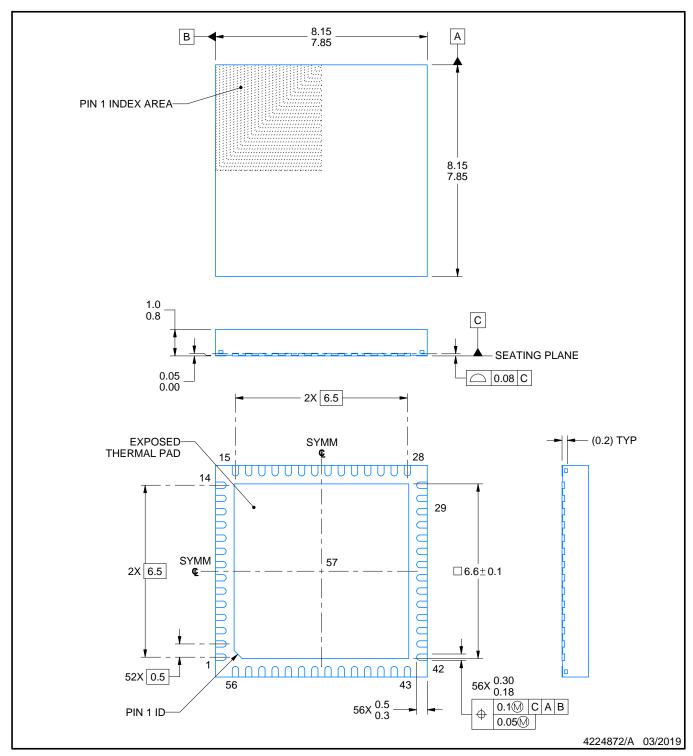

- 采用 56 引脚超薄型四方扁平无引线 (VQFN) 封装

#### 2 应用范围

- 通信基础设施:

- 蜂窝基站

- 微波回程

- 光纤网络

- 通用监视器和控制

- 数据采集系统

#### 3 说明

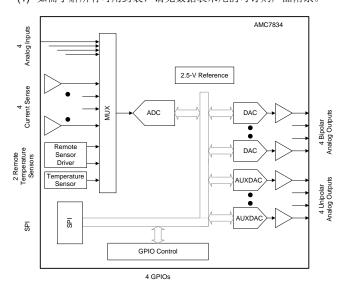

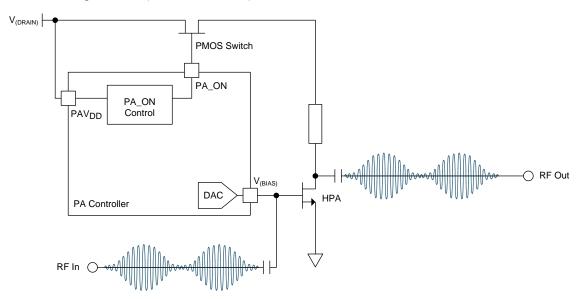

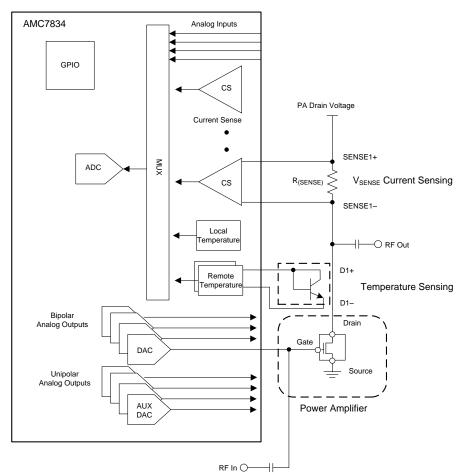

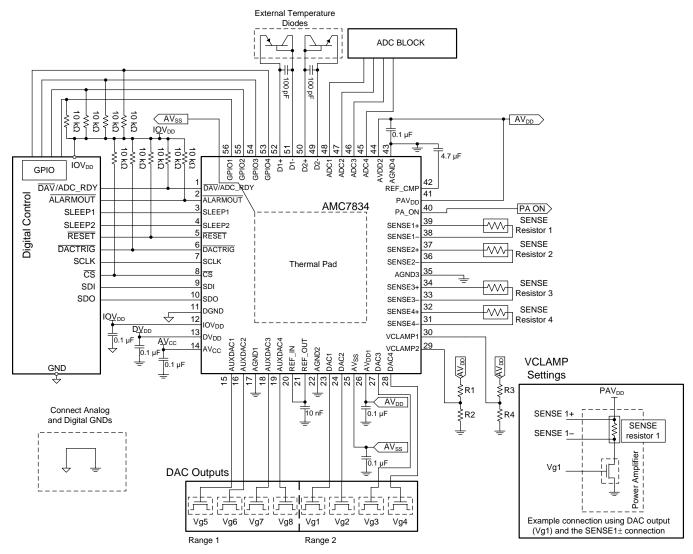

AMC7834 器件是一款针对功率放大器 (PA) 偏置的高度集成、低功耗、模拟监视和控制解决方案,能够对温度、电流和电压进行监控。

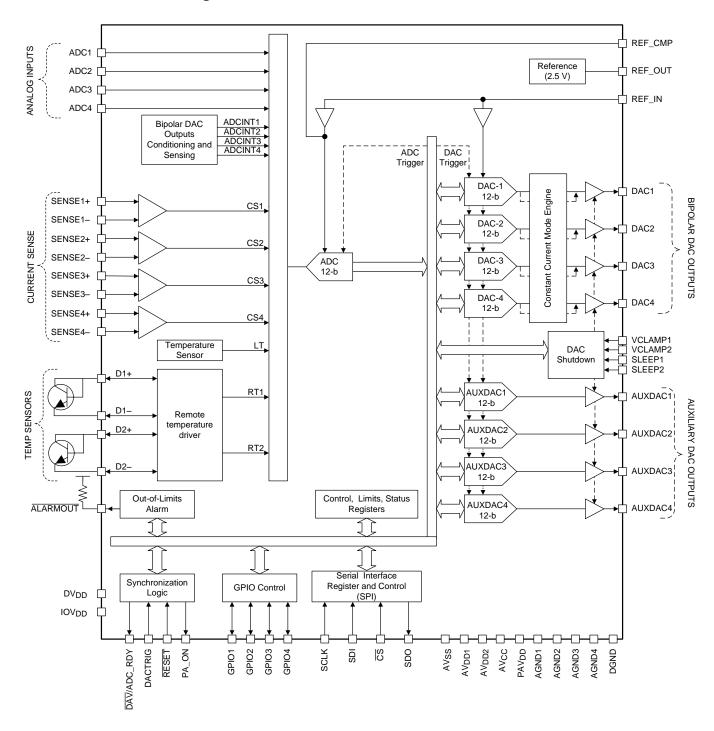

该器件集成了一个多通道 12 位模数转换器 (ADC); 八个 12 位数模转换器 (DAC); 四个高侧电流感测放大器,可以选择设置它们作为四个独立闭环漏极电流控制器的一部分;一个精确的片上温度传感器和两个远程温度二极管驱动器;四个可配置的通用 I/O 端口(GPIO);以及一个精确的内部基准。其高集成度极大地减少了组件数量,并且简化了 PA 偏置系统设计。

该器件具有功能集成和宽工作温度范围等诸多优势,因此适合用作多通道射频 (RF) 通信系统中 PA 的一体化、低成本偏置控制电路。凭借灵活的 DAC 输出范围和宽共模电压电流传感器,此器件可用作针对多种晶体管技术(例如 LDMOS、GaA 和 GaN)的偏置解决方案。AMC7834 功能集对通用监视器和控制系统而言同样有益。

德州仪器 (TI) 提供 了一个完备的模拟监视和控制 (AMC) 产品系列, 以满足各类应用不同的通道数、附 加特性或者转换器解决方案需求。更多信息,敬请访问 www.ti.com.cn/amc。

# 器件信息<sup>(1)</sup>

| 器件型号    | 封装        | 封装尺寸 (标称值)      |

|---------|-----------|-----------------|

| AMC7834 | VQFN (56) | 8.00mm x 8.00mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

|   | 目:                                                         | 录  |                                |                |

|---|------------------------------------------------------------|----|--------------------------------|----------------|

| 1 | 特性 1                                                       |    | 7.1 Overview                   | 24             |

| 2 | 应用范围1                                                      |    | 7.2 Functional Block Diagram   | 2              |

| 3 | 说明1                                                        |    | 7.3 Feature Description        | 20             |

| 4 | 修订历史记录 2                                                   |    | 7.4 Device Functional Modes    | 4              |

| 5 | Pin Configuration and Functions 4                          |    | 7.5 Programming                | 5              |

| 6 | Specifications                                             |    | 7.6 Register Maps              | 5              |

| ٠ | 6.1 Absolute Maximum Ratings                               | 8  | Application and Implementation | <mark>7</mark> |

|   | 6.2 ESD Ratings                                            |    | 8.1 Application Information    | <u>7</u>       |

|   | 6.3 Recommended Operating Conditions                       |    | 8.2 Typical Application        |                |

|   | 6.4 Thermal Information                                    |    | 8.3 Initialization Set Up      | 82             |

|   | 6.5 Electrical Characteristics—DAC Specifications 9        | 9  | Power Supply Recommendations   | 82             |

|   | 6.6 Electrical Characteristics—ADC, Current and            | 10 | Layout                         | 82             |

|   | Temperature Sensor Specifications                          |    | 10.1 Layout Guidelines         | 8              |

|   | 6.7 Electrical Characteristics—General Specifications . 12 |    | 10.2 Layout Example            | 8              |

|   | 6.8 Serial Interface Timing Requirements                   | 11 | 器件和文档支持                        | 8              |

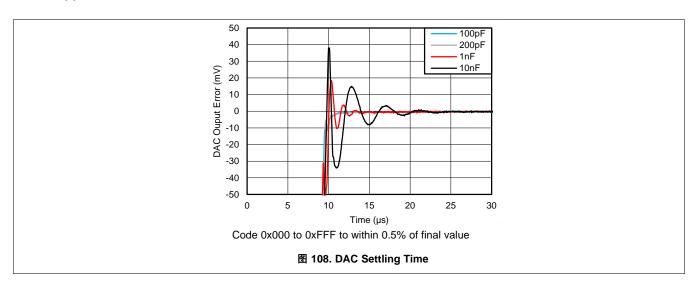

|   | 6.9 Switching Characteristics—DAC Specifications 14        |    | 11.1 文档支持                      | 8              |

|   | 6.10 Switching Characteristics—ADC, Current and            |    | 11.2 社区资源                      | 8              |

|   | Temperature Sensor Specifications14                        |    | 11.3 商标                        | 8              |

|   | 6.11 Switching Characteristics—General                     |    | 11.4 静电放电警告                    | 8              |

|   | Specifications                                             |    | 11.5 Glossary                  | 8              |

| - | 6.12 Typical Characteristics                               | 12 | . 机械、封装和可订购信息                  | 8              |

| 1 | Detailed Description24                                     |    |                                |                |

# 4 修订历史记录

| Cł | nanges from Revision A (April 2015) to Revision B                                                                                                                            | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | deleted text from the Description of pin 1 in the <i>Pin Functions</i> table " If unused the pin requires a 10 k $\Omega$ pullup resistor to the IOV <sub>DD</sub> pin."     | 5    |

| •  | Added: Bipolar DACs in AVSS clamp mode To the Clamp Output Mode section of <i>Electrical Characteristics—DAC Specifications</i>                                              | 10   |

| •  | Deleted text from the Accuracy Test Conditions: "32 Samples Average" in <i>Electrical Characteristics—ADC, Current and Temperature Sensor Specifications</i>                 | 11   |

| •  | Added: AV <sub>DD</sub> alarm threshold to <i>Electrical Characteristics—General Specifications</i>                                                                          | 12   |

| •  | Changed the I <sub>IOVDD</sub> (Power-Mode 10) TYP value From: 1 μA To 1.75 μA in <i>Electrical Characteristics—General Specifications</i>                                   | 13   |

| •  | Changed the I <sub>IOVDD</sub> (Power-Mode 00) TYP value From: 0.2 μA To 1.75 μA in <i>Electrical Characteristics—General Specifications</i>                                 | 13   |

| •  | Added Figure 29                                                                                                                                                              | 19   |

| •  | Changed Figure 45                                                                                                                                                            | 27   |

| •  | Added text to the itemized list in <i>DAC Clamp Operation</i> : "If the output buffer is inactive the clamp voltage is fixed to AV <sub>SS</sub> ."                          | 29   |

| •  | Added text to the end of DAC Clamp Operation: "Additionally, in the unique case"                                                                                             | 29   |

| •  | Changed text in paragraph 1 of <i>ADC Sequencing</i> From: "The AMC7834 supports autonomous ADC conversion" To: The AMC7834 supports autonomous and direct-mode conversions" |      |

| •  | Change the paragraph: "Once the conversion cycle starts" in ADC Sequencing                                                                                                   | 31   |

| •  | Deleted text from paragraph 3 of <i>ADC Sequencing</i> : "The first conversion sequence is reserved for calibration and the corresponding ADC results should be ignored."    | 31   |

| •  | Added text to the last paragraph of <i>ADC Sequencing</i> : "In direct-mode conversion the DAV/ADC_RDY pin for each channel group. "                                         | 33   |

| •  | Added text to paragraph 3 of <i>Drain Switch Control</i> : The PA_ON signal state is also triggered by the AVDD monitoring circuit                                           | 39   |

# 修订历史记录 (接下页)

| •        | 发布完整版量产数据数据表                                                                                                                                                                                                                     | 1    |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Cł       | nanges from Original (November 2014) to Revision A                                                                                                                                                                               | Page |

| <u>•</u> | Added text to item 2 of Initialization Procedure: A 250 µs POR delay occurs"                                                                                                                                                     | 82   |

| •        | Changed General Status Register (address = 0x1F) [reset = 0x0000]                                                                                                                                                                |      |

| •        | Changed Bit 1-0 of Table 18 From: 00: Invalid To: 00: 1                                                                                                                                                                          |      |

| •        | Changed Bit 3-2 of Table 18 From: 00: Invalid To: 00: 1                                                                                                                                                                          |      |

| •        | Changed Bit 5-4 of Table 18 From: 00: Invalid To: 00: 1                                                                                                                                                                          |      |

| •        | Changed Bit 10 of Table 18 From: 000: Invalid To: 000: 1                                                                                                                                                                         |      |

| •        | Changed Bit 12 of Table 15 From: Reserved To: CMODE                                                                                                                                                                              |      |

| •        | Changed the Reset value From: 0000h To: 0001h in Table 13                                                                                                                                                                        | 54   |

| •        | Changed R-00h To: R-01h in Bits 7:0 of Figure 69                                                                                                                                                                                 |      |

| •        | Changed 0x06 Default value From: 0000 To: 0001 in Table 9                                                                                                                                                                        | 52   |

| •        | Changed text in the second paragraph of <i>Open-Loop Mode</i> From: "The current-sense amplifier outputs are converted continuously by the device ADC" To: "The current-sense amplifier outputs are converted by the device ADC" | 47   |

| •        | Added section: AV <sub>DD</sub> Detection Alarm                                                                                                                                                                                  | 42   |

| •        | Added text to the last paragraph of <i>Drain Switch Control</i> : "The AV <sub>DD</sub> detection circuit is set to trigger the PA_ON signal to the OFF state in response to an out of range event."                             |      |

| •        | Changed text in two locations of paragraph 4 in <i>Drain Switch Control</i> : From: "AV <sub>SS</sub> " To: "AV <sub>DD</sub> and AV <sub>SS</sub> "                                                                             | 39   |

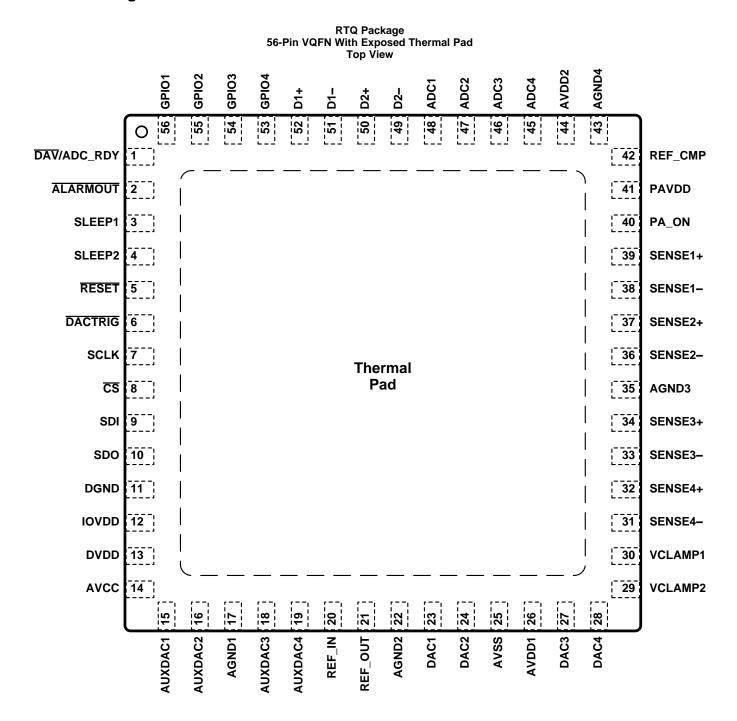

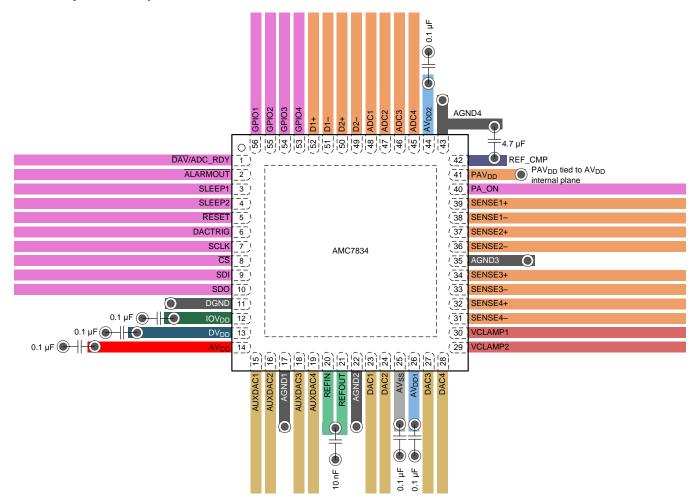

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN               |     |      | Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME              | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

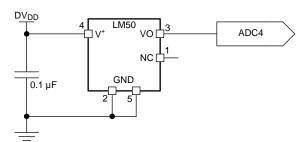

| ADC1              | 48  | I    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| ADC2              | 47  | ı    | Analog inputs channels. These channels are used for general manifering. The input range                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| ADC3              | 46  | ı    | Analog inputs channels. These channels are used for general monitoring. The input range of these pins is 0 to V <sub>ref</sub> .                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| ADC4              | 45  | ı    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| AGND1             | 17  | _    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| AGND2             | 22  | _    | Analog ground. These pins are the ground reference point for all analog circuitry on the device. Connect the AGND1, AGND2, AGND3, and AGND4 pins to the same potential                                                                                                                                                                                                                                                                                                                                                      |  |  |

| AGND3             | 35  | _    | (AGND). Ideally, the analog and digital grounds should be at the same potential (GND) and                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| AGND4             | 43  | _    | must not differ by more than ±0.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| ALARMOUT          | 2   | 0    | LARMOUT is an open drain global alarm ou <u>tput. An exte</u> rnal 10 k $\Omega$ pullup resistor to a oltage no higher than AV <sub>DD</sub> is required. The ALARMOUT output polarity is defined through ne ALARMOUT-POLARITY bit in register 0x1B. The default polarity is active low.                                                                                                                                                                                                                                    |  |  |

| AUXDAC1           | 15  | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| AUXDAC2           | 16  | 0    | Auxiliary DAC Outputs. The power-on-reset and clamp voltage for these DACs is always                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| AUXDAC3 18        |     | 0    | AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| AUXDAC4           | 19  | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| AV <sub>CC</sub>  | 14  | _    | Positive analog power supply for the auxiliary DACs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| AV <sub>DD1</sub> | 26  | _    | Analog supply voltage (4.5 V to 5.5 V). Connect the AV <sub>DD1</sub> and AV <sub>DD2</sub> pins to the same                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| AV <sub>DD2</sub> | 44  | _    | potential (AV <sub>DD</sub> ). These pins must have the same value as the DV <sub>DD</sub> pin.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| AV <sub>SS</sub>  | 25  | _    | Lowest potential in the system. This pin is typically tied to a negative supply voltage. If all the bipolar DACs are set to operate in positive output ranges can be connected to the analog ground.                                                                                                                                                                                                                                                                                                                        |  |  |

| <del>CS</del>     | 8   | I    | Active low serial data enable. This input is the frame synchronization signal for the serial data. When this signal goes low, it enables the serial interface input shift register.                                                                                                                                                                                                                                                                                                                                         |  |  |

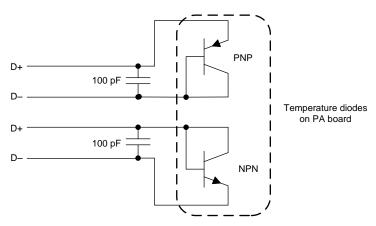

| D1+               | 52  | I    | Remote temperature sensor D1. This pin is a positive input when D1 is enabled. This pin can be left unconnected if unused.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| D1-               | 51  | 1    | Remote temperature sensor D1. This pin is a negative input when D1 is enabled. This pin can be left unconnected if unused. Pins D1– and D2– are internally shorted.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| D2+               | 50  | I    | Remote temperature sensor D2. This pin is a positive input when D2 is enabled. This pin can be left unconnected if unused.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| D2-               | 49  | I    | Remote temperature sensor D2. This pin is a negative input when D2 is enabled. This pin can be left unconnected if unused. Pins D1– and D2– are internally shorted.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| DAC1              | 23  | 0    | Bipolar DAC outputs 1 and 2. These DACs share the same range and clamp voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DAC2              | 24  | 0    | Dipolal DAC outputs 1 and 2. These DACs shale the same range and clamp voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DAC3              | 27  | 0    | Bipolar DAC outputs 3 and 4. These DACs share the same range and clamp voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DAC4              | 28  | 0    | Dipolar DAC outputs 3 and 4. These DACs share the same range and clamp voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

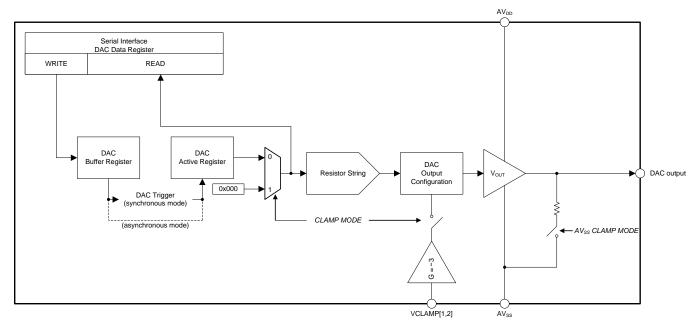

| DACTRIG           | 6   | 1    | DAC trigger active low control input. When the DACTRIG pin is low, the contents of the DAC data registers are transferred to the DAC active registers. The DAC outputs update only after the DAC active registers have been loaded. This pin is only operational in open loop current sensing mode.                                                                                                                                                                                                                         |  |  |

| DAV/ADC_RDY       | 1   | 0    | The DAV/ADC_RDY pin is in high-impedance mode by default and must be enabled through the DAVPIN-EN bit in register 0x11 to access the DAV or ADC_RDY functionality. DAV is an active low ADC synchronization signal. A 20 µs pulse (active low) on this pin is used to indicate the end of a conversion sequence. Alternatively the pin can be set to operate as ADC_RDY through the DAVPIN-SEL bit in register 0x11. ADC_RDY is an active high synchronization signal used to indicate when the ADC is in the READY state. |  |  |

| DGND              | 11  | _    | Digital ground. This pin is the ground reference point for all digital circuitry on the device. Ideally, the analog and digital grounds should be at the same potential (GND) and must not differ by more than ±0.3 V.                                                                                                                                                                                                                                                                                                      |  |  |

| $DV_DD$           | 13  |      | Digital supply voltage (4.5 V to 5.5 V). This pin must be the same value as the $AV_{DD}$ pins.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

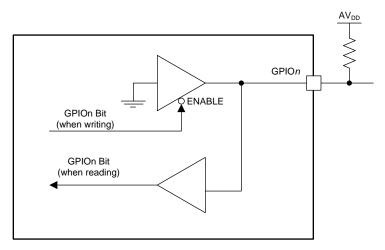

| GPIO1             | 56  | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| GPIO2             | 55  | I/O  | General-purpose digital I/Os. These pins are bidirectional open-drain, digital I/Os and                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GPIO3             | 54  | I/O  | requires an external 10 k $\Omega$ pullup resistor to a voltage no higher than $AV_{DD}$ . If unused, the GPIO pins should be connected to ground.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| GPIO4             | 53  | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

# Pin Functions (continued)

| PIN               |                                                                                                                                                                                           |      | First discussis (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME              | NO.                                                                                                                                                                                       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| IOV <sub>DD</sub> | 12                                                                                                                                                                                        | _    | IO supply voltage (1.7 V to 3.6 V). This pin sets the I/O operating voltage and threshold levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PAV <sub>DD</sub> | 41                                                                                                                                                                                        | _    | Power supply for the PA_ON control signal (4 V to 20 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PA_ON             | 40                                                                                                                                                                                        | 0    | PA_ON is a synchronization signal capable of driving an external PMOS switch and controlling the flow of drain current to a power amplifier (PA) transistor. The PA_ON pin has an internal 120 kΩ pull-up resistor to the PAV_DD pin. The maximum output voltage is set by the PAV_DD pin and limited to 20 V. For drain voltages higher than 20 V, tying the PAV_DD pin to the AV_DD pins and scaling the control signal externally is recommended. The PA_ON signal state can be set through a register write but it can also be configured to trigger automatically in the case of an ALARM event or when any of the SLEEP signals is activated. |  |  |

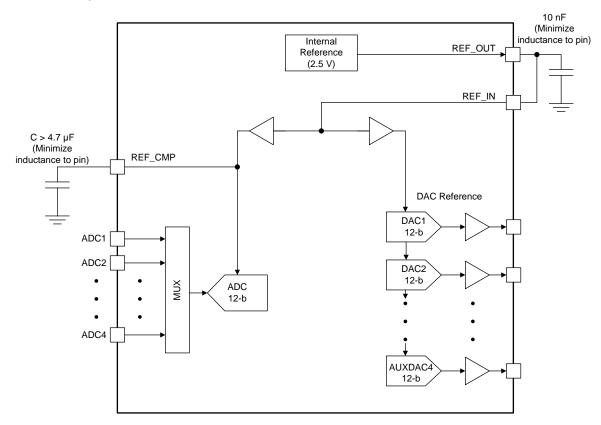

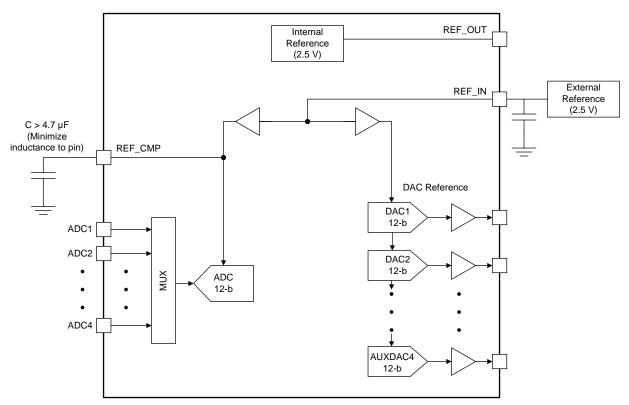

| REF_CMP           | 42                                                                                                                                                                                        | I/O  | Reference compensation capacitor connection. Connect a 4.7 $\mu F$ capacitor between this pin and the AGND4 pin for ADC reference compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| REF_IN            | 20                                                                                                                                                                                        | 1    | Reference input to the device. This pin can be connected to the REF_OUT pin to use the device internal reference or alternatively to an external voltage reference source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| REF_OUT           | 21                                                                                                                                                                                        | 0    | Internal voltage reference output. Connect this pin directly to the REF_IN pin to operate the device in internal reference mode. An external buffer amplifier with a high impedance input is required to drive an external load. This pin can be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RESET             | 5                                                                                                                                                                                         | I    | Active low reset input. Logic low on this pin causes the device to perform a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| SCLK              | 7                                                                                                                                                                                         | I    | Serial interface clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SDI               | 9                                                                                                                                                                                         | I    | Serial interface data input. Data is clocked into the input shift register on each rising edge of the SCLK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SDO               | 10                                                                                                                                                                                        | 0    | Serial interface data output. The SDO pin is in high impedance when the $\overline{\text{CS}}$ pin is high. Data is clocked out of the input shift register on each falling edge of the SCLK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SENSE1+           | 39                                                                                                                                                                                        | I    | Current sense 1 external sense resistor power connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SENSE1-           | 38                                                                                                                                                                                        | I    | Current sense 1 external sense resistor load connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SENSE2+           | 37                                                                                                                                                                                        | I    | Current sense 2 external sense resistor power connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SENSE2-           | 36                                                                                                                                                                                        | I    | Current sense 2 external sense resistor load connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SENSE3+           | 34                                                                                                                                                                                        | I    | Current sense 3 external sense resistor power connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SENSE3-           | 33                                                                                                                                                                                        | I    | Current sense 3 external sense resistor load connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SENSE4+           | 32                                                                                                                                                                                        | I    | Current sense 4 external sense resistor power connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SENSE4-           | 31                                                                                                                                                                                        | I    | Current sense 4 external sense resistor load connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SLEEP1            | 3                                                                                                                                                                                         | I    | Active high asynchronous power down digital input 1. The power down functions of this pin are register configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SLEEP2            | 4                                                                                                                                                                                         | I    | Active high asynchronous power down digital input 2. The power down functions of this pin are register configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VCLAMP1           | Power-on reset and clamp voltage control input for bipolar DACs 1 and 2. The resulting power-on reset (POR) and clamp voltage value is given by Equation 1.  CLAMP = -3 × VCLAMP[1:2] (1) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| VCLAMP2           | 29                                                                                                                                                                                        | I    | Power-on reset and clamp voltage control input for bipolar DACs 3 and 4. The resulting POR and clamp voltage value is given by Equation 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Thermal Pad       |                                                                                                                                                                                           | _    | The thermal pad is located on the bottom-side of the device package. The thermal pad should be tied to the same potential as the $AV_SS$ pin for optimal thermal dissipation. Alternatively, the thermal pad can be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                                                      | MIN                    | MAX                     | UNIT |  |

|---------------------------------------|----------------------------------------------------------------------|------------------------|-------------------------|------|--|

|                                       | AV <sub>DD</sub> to GND                                              | -0.3                   | 6                       |      |  |

|                                       | DV <sub>DD</sub> to GND                                              | -0.3                   | 6                       |      |  |

|                                       | IOV <sub>DD</sub> to GND                                             | -0.3                   | 6                       |      |  |

| Supply voltage                        | AV <sub>CC</sub> to GND                                              | -0.3                   | 13                      | V    |  |

|                                       | AV <sub>SS</sub> to GND                                              | -6                     | 0.3                     |      |  |

|                                       | PAV <sub>DD</sub> to AV <sub>SS</sub>                                | -0.3                   | 26                      |      |  |

|                                       | DGND to AGND                                                         | -0.3                   | 0.3                     |      |  |

|                                       | ADC analog input voltage to GND                                      | -0.3                   | $AV_{DD} + 0.3$         |      |  |

|                                       | Current sense input voltage to GND                                   | -0.3                   | 65                      |      |  |

|                                       | Bipolar DAC outputs to GND                                           | AV <sub>SS</sub> - 0.3 | $AV_{DD} + 0.3$         | İ    |  |

|                                       | Auxiliary DAC outputs to GND                                         | -0.3                   | AV <sub>CC</sub> + 0.3  |      |  |

|                                       | VCLAMP1, VCLAMP2 inputs to GND                                       | -0.3                   | AV <sub>DD</sub> + 0.3  |      |  |

|                                       | D1+, D1-, D2+ and D2- to GND                                         | -0.3                   | $AV_{DD} + 0.3$         |      |  |

| Pin voltage                           | REF_CMP, REF_IN to GND                                               | -0.3                   | $AV_{DD} + 0.3$         | V    |  |

|                                       | REF_OUT to GND                                                       | -0.3                   | AV <sub>DD</sub> + 0.3  |      |  |

|                                       | PA_ON to GND                                                         | -0.3                   | PAV <sub>DD</sub> + 0.3 |      |  |

|                                       | CS, SCLK, SDI, DACTRIG, RESET, SLEEP1, SLEEP2 and DAV/ADC_RDY to GND | -0.3                   | IOV <sub>DD</sub> + 0.3 |      |  |

|                                       | SDO to GND                                                           | -0.3                   | IOV <sub>DD</sub> + 0.3 |      |  |

|                                       | GPIOs, ALARMOUT to GND                                               | -0.3                   | 6                       |      |  |

|                                       | ADC analog input current                                             | -10                    | 10                      |      |  |

| Pin current                           | REF_OUT output current                                               | -0.3                   | 0.3                     | mA   |  |

|                                       | GPIOs, ALARMOUT sinking current                                      |                        | 5                       |      |  |

| Operating temperature range           |                                                                      | -40                    | 125                     | °C   |  |

| Junction temperature range, T         | -40                                                                  | 150                    | °C                      |      |  |

| Storage temperature, T <sub>stg</sub> |                                                                      | -40                    | 150                     | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±750  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                                   | MIN  | NOM        | MAX  | UNIT |

|---------------------|-----------------------------------|------|------------|------|------|

|                     | AV <sub>DD</sub> <sup>(1)</sup>   | 4.5  | 5          | 5.5  |      |

|                     | DV <sub>DD</sub> <sup>(1)</sup>   | 4.5  | 5          | 5.5  |      |

| Cumply voltage      | IOV <sub>DD</sub>                 | 1.7  | 3.3        | 3.6  | V    |

| Supply voltage      | AV <sub>CC</sub>                  | 4.5  | 5          | 12.5 |      |

|                     | AV <sub>SS</sub> <sup>(2)</sup>   | -5.5 | <b>-</b> 5 | 0    |      |

|                     | PAV <sub>DD</sub>                 | 4    | 5          | 20   |      |

| Specified performan | Specified performance temperature |      | 25         | 105  | °C   |

| Operating temperate | ıre                               | -40  | 25         | 125  | °C   |

#### 6.4 Thermal Information

|                       | THERMAL METRIC (1)(2)                        | RTQ (VQFN)<br>56 PINS | UNIT    |

|-----------------------|----------------------------------------------|-----------------------|---------|

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 24.7                  |         |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 7.9                   |         |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 2.7                   | °C // / |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2                   | °C/W    |

| ΨЈВ                   | Junction-to-board characterization parameter | 2.7                   |         |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.3                   |         |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) TI strongly recommends to solder the device thermal pad to a board plane connected to the AV<sub>SS</sub> pin.

The value of the  $DV_{DD}$  pin must be equal to that of the  $AV_{DD}$  pins. The value of the  $AV_{SS}$  pin is only equal to AGND when all bipolar DACs are set to operate in positive voltage ranges.

# 6.5 Electrical Characteristics—DAC Specifications

The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing it.  $AV_{DD} = DV_{DD} = 5 \text{ V}$ ,  $AV_{CC} = 5 \text{ V}$ ,  $AV_{SS} = -5 \text{ V}$ ,  $IOV_{DD} = 3.3 \text{ V}$ ,  $PAV_{DD} = 5 \text{ V}$ , AGND = DGND = 0 V, external 2.5 V reference, DAC output range = 0 to 5 V for all DACs, no load on the DACs, current sense inputs common mode at 48 V,  $T_A = -40 ^{\circ}\text{C}$  to  $+105 ^{\circ}\text{C}$

|       | PARAMETER                   | TEST CONDITIONS                                                                                                        | MIN | TYP   | MAX   | UNIT   |

|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|--------|

| BIPO  | LAR DAC DC ACCURACY         |                                                                                                                        |     |       |       |        |

|       | Resolution                  |                                                                                                                        | 12  |       |       | Bits   |

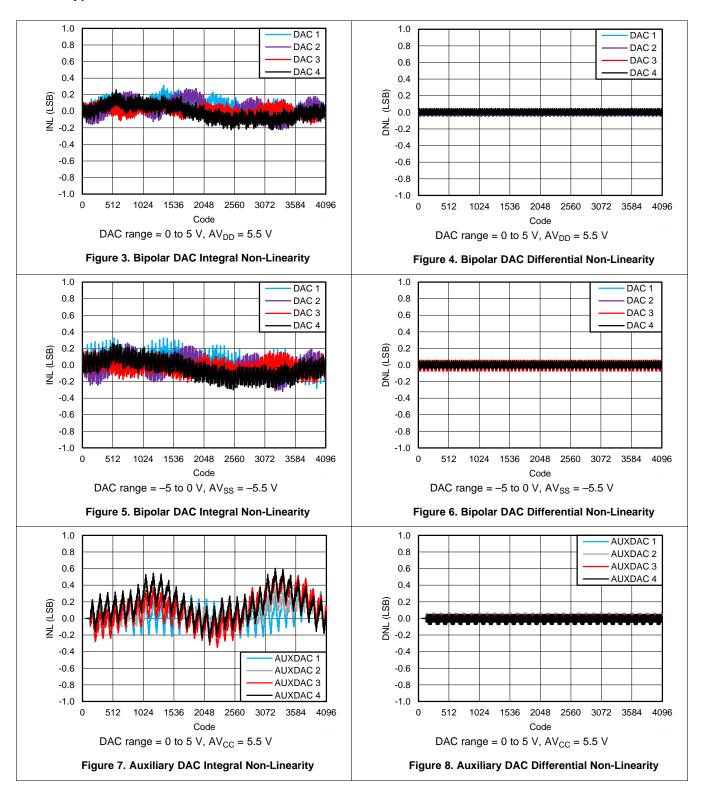

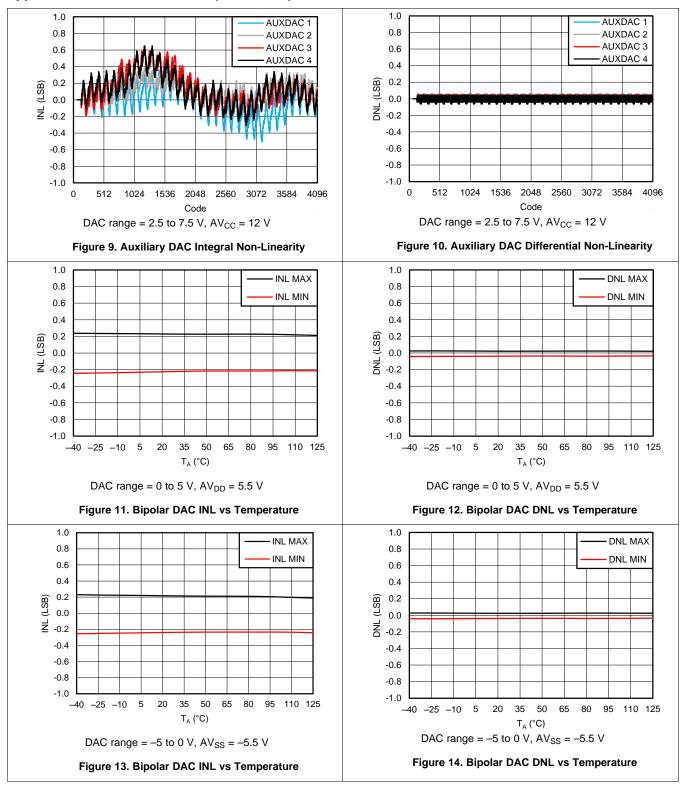

| INL   | Relative accuracy           | Measured by line passing through codes 040h and FC0h. 0 to 5 V range                                                   |     | ±0.3  | ±1    | LSB    |

| IINL  | Relative accuracy           | Measured by line passing through codes 040h and FC0h. –4 to 1 V and –5 to 0 V ranges                                   |     | ±0.3  | ±1    | LOD    |

| DNL   | Differential nonlinearity   | Specified monotonic. Measured by line passing through codes 040h and FC0h. 0 to 5 V range                              |     | ±0.05 | ±1    | LSB    |

| DINL  | Differential nonlinearity   | Specified monotonic. Measured by line passing through codes 040h and FC0h. –4 to 1 V and –5 to 0 V ranges              |     | ±0.05 | ±1    | LOD    |

| TUE   | Total unadjusted arror      | $T_A = 25$ °C, 0 to 5 V range                                                                                          |     | ±1    | ±15   | mV     |

| IUE   | Total unadjusted error      | $T_A = 25$ °C, -4 to 1 V and -5 to 0 V ranges                                                                          |     | ±2    | ±15   | IIIV   |

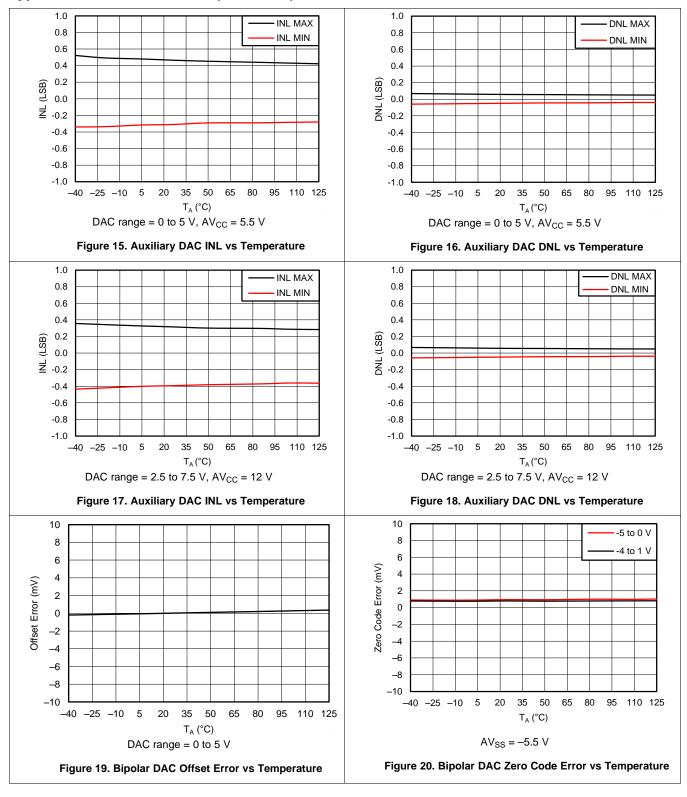

|       | Offset error                | T <sub>A</sub> = 25°C. Measured by line passing through codes 040h and FC0h. 0 to 5 V range                            |     | ±0.2  | ±10   | mV     |

|       | Zero-code error             | $T_A$ = 25°C. Code 000h4 to 1 V and -5 to 0 V ranges. $AV_{SS}$ = -5.5 V                                               |     | ±2    | ±10   | mV     |

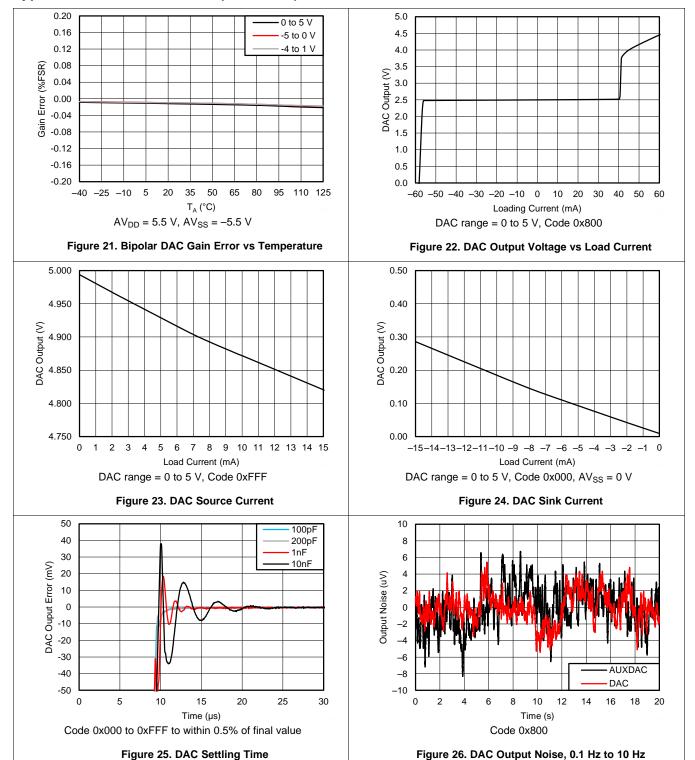

|       | Cain arrar                  | T <sub>A</sub> = 25°C. Measured by line passing through codes 040h and FC0h. 0 to 5 V range                            |     | ±0.02 | ±0.2  | 0/ FCD |

|       | Gain error                  | T <sub>A</sub> = 25°C. Measured by line passing through codes 040h and FC0h. –4 to 1 V and –5 to 0 V ranges            |     | ±0.02 | ±0.2  | %FSR   |

|       | Offset temperature drift    | 0 to 5 V range                                                                                                         |     | ±1    |       | ppm/°C |

|       | Zero-code temperature drift | -4 to 1 V and $-5$ to 0 V ranges. AV <sub>SS</sub> = $-5.5$ V                                                          |     | ±1.5  |       | ppm/°C |

|       | Gain temperature drift      | All output ranges                                                                                                      |     | ±1    |       | ppm/°C |

| AUXII | LIARY DAC DC ACCURAC        | Y .                                                                                                                    |     |       |       |        |

|       | Resolution                  |                                                                                                                        | 12  |       |       | Bits   |

| INL   | Integral nonlinearity       | Measured by line passing through codes 040h and FC0h. 0 to 5 V range                                                   |     | ±0.5  | ±1.25 | LSB    |

| IINL  |                             | Measured by line passing through codes 040h and FC0h. 2.5 to 7.5 V range. $AV_{CC}$ = 12 V                             |     | ±0.5  | ±1.25 | LOB    |

| DNL   | D''(anadial andianath       | Specified monotonic. Measured by line passing through codes 040h and FC0h. 0 to 5 V range                              |     | ±0.05 | ±1    | LSB    |

| DIVE  | Differential nonlinearity   | Specified monotonic. Measured by line passing through codes 040h and FC0h. 2.5 to 7.5 V range. AV <sub>CC</sub> = 12 V |     | ±0.05 | ±1    | LOD    |

| TUE   | Total unadjusted error      | T <sub>A</sub> = 25°C. 0 to 5 V range                                                                                  |     | ±2    | ±15   | mV     |

| TUE   | rotal unadjusted error      | $T_A = 25$ °C. 2.5 to 7.5 V range. $AV_{CC} = 12 \text{ V}$                                                            |     | ±2    | ±15   | IIIV   |

|       | Officet career              | T <sub>A</sub> = 25°C. Measured by line passing through codes 040h and FC0h. 0 to 5 V range                            |     | ±0.3  | ±10   | \/     |

|       | Offset error                | $T_A$ = 25°C. Measured by line passing through codes 040h and FC0h. 2.5 to 7.5 V range. AV <sub>CC</sub> = 12 V        |     | ±1    | ±10   | mV     |

|       | Gain error                  | T <sub>A</sub> = 25°C. Measured by line passing through codes 040h and FC0h. 0 to 5 V range                            |     | ±0.03 | ±0.2  | %FQD   |

|       | Gaill Elloi                 | $T_A$ = 25°C. Measured by line passing through codes 040h and FC0h. 2.5 to 7.5 V range. AV <sub>CC</sub> = 12 V        |     | ±0.03 | ±0.2  | %FSR   |

|       | Offset temperature drift    | All output ranges                                                                                                      |     | ±1    |       | ppm/°C |

|       | Gain temperature drift      | All output ranges                                                                                                      |     | ±1    |       | ppm/°C |

# **Electrical Characteristics—DAC Specifications (continued)**

The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing it.  $AV_{DD} = DV_{DD} = 5 \text{ V}$ ,  $AV_{CC} = 5 \text{ V}$ ,  $AV_{SS} = -5 \text{ V}$ ,  $IOV_{DD} = 3.3 \text{ V}$ ,  $PAV_{DD} = 5 \text{ V}$ , AGND = DGND = 0 V, external 2.5 V reference, DAC output range = 0 to 5 V for all DACs, no load on the DACs, current sense inputs common mode at 48 V,  $T_A = -40$ °C to +105°C

| PARAMETER                              | TEST CONDITIONS                                                                                                                                                                                       | MIN        | TYP MAX               | UNIT               |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|--------------------|

| DAC OUTPUT CHARACTERIST                | rics                                                                                                                                                                                                  |            |                       |                    |

|                                        | DACn_range set to 00                                                                                                                                                                                  | -4         | 1                     |                    |

| Dinalar DAC rease (1)                  | DACn_range set to 01                                                                                                                                                                                  | <b>-</b> 5 | 0                     | V                  |

| Bipolar DAC range <sup>(1)</sup>       | DAC <i>n</i> _range set to 10                                                                                                                                                                         | <b>-</b> 5 | 0                     | V                  |

|                                        | DAC <i>n</i> _range set to 11                                                                                                                                                                         | 0          | 5                     |                    |

| Auxiliary DAC range <sup>(2)</sup>     | AUXDAC <i>n</i> _range set to 0                                                                                                                                                                       | 0          | 5                     | V                  |

| Auxiliary DAC range                    | AUXDAC <i>n</i> _range set to 1                                                                                                                                                                       | 2.5        | 7.5                   | V                  |

| Short-circuit current                  | Bipolar DACs: Full-scale current shorted to $AV_{SS}$ or $AV_{DD}$ Auxiliary DACs: Full-scale current shorted to AGND or $AV_{CC}$                                                                    |            | 45                    | mA                 |

| Load current <sup>(3)</sup>            | Bipolar DACs: Source or sink with 300 mV headroom from $AV_{DD}$ or $AV_{SS}$ , voltage drop < 25 mV Auxiliary DACs: Source or sink with 300 mV headroom from $AV_{CC}$ or AGND, voltage drop < 25 mV | ±10        |                       | mA                 |

| Maximum capacitive load <sup>(4)</sup> | All DAC outputs. R <sub>L</sub> = ∞                                                                                                                                                                   | 0          | 10                    | nF                 |

| DC output impedance                    | All DAC outputs. Code set to 800h, ±10 mA                                                                                                                                                             |            | 1                     | Ω                  |

| Glitch energy                          | All DAC outputs. Transition: Code 7FFh to 800h; 800h to 7FFh                                                                                                                                          |            | 1                     | nV-s               |

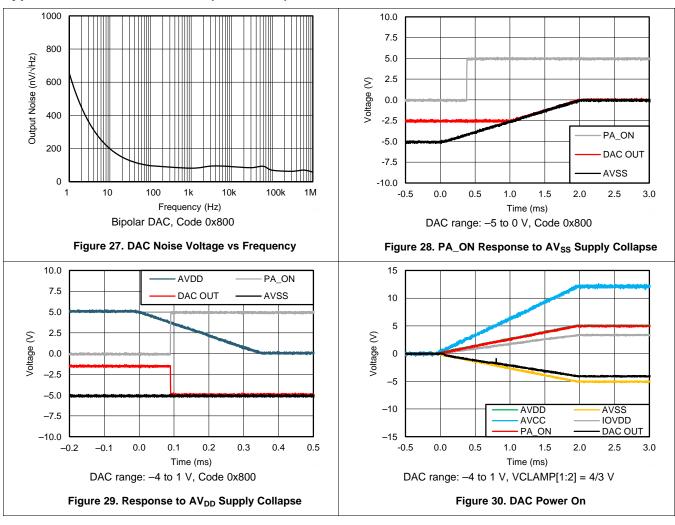

|                                        | Auxiliary DACs. 1 kHz, code 800h                                                                                                                                                                      |            | 200                   | nV/√ <del>Hz</del> |

|                                        | Bipolar DACs. 1 kHz, code 800h                                                                                                                                                                        |            | 100                   | IIV/VHZ            |

| Output noise                           | Auxiliary DACs. Integrated noise from 0.1 Hz to 10 Hz, code 800h                                                                                                                                      |            | 20                    | \/                 |

|                                        | Bipolar DACs. Integrated noise from 0.1 Hz to 10 Hz, code 800h                                                                                                                                        |            | 10                    | μV <sub>PP</sub>   |

| CLAMP OUTPUT MODE                      |                                                                                                                                                                                                       |            |                       | •                  |

| VCLAMP [1:2] voltage range             |                                                                                                                                                                                                       | 0          | -AV <sub>SS</sub> / 3 | V                  |

| VCLAMP [1:2] input current             |                                                                                                                                                                                                       |            | ±0.5                  | μΑ                 |

| Clamp output valtage                   | Bipolar DACs. Clamp voltage = $-3 \times VCLAMP[1:2]$                                                                                                                                                 | $AV_SS$    | 0                     | V                  |

| Clamp output voltage                   | Auxiliary DACs                                                                                                                                                                                        |            | AGND                  | V                  |

| Clamp output current                   | Bipolar DACs. Source, sink, or both with 300-mV headroom from AV $_{\rm SS}$ , voltage drop < 25 mV                                                                                                   | ±10        |                       | mA                 |

| Clamp pull-down                        | Auxiliary DACs. Measured to AGND                                                                                                                                                                      |            | 9                     | kΩ                 |

| resistance                             | Bipolar DACs. VCLAMP buffers inactive (AV $_{\rm SS}$ clamp mode). Measured to AV $_{\rm SS}$                                                                                                         |            | 550                   | Ω                  |

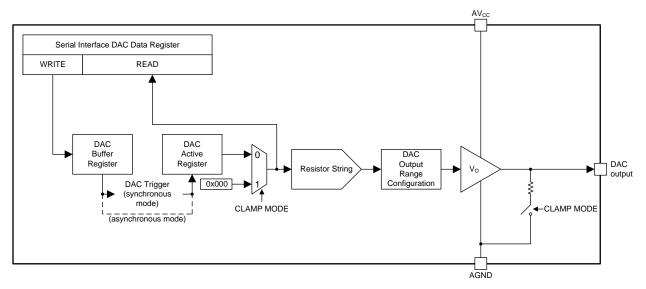

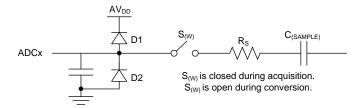

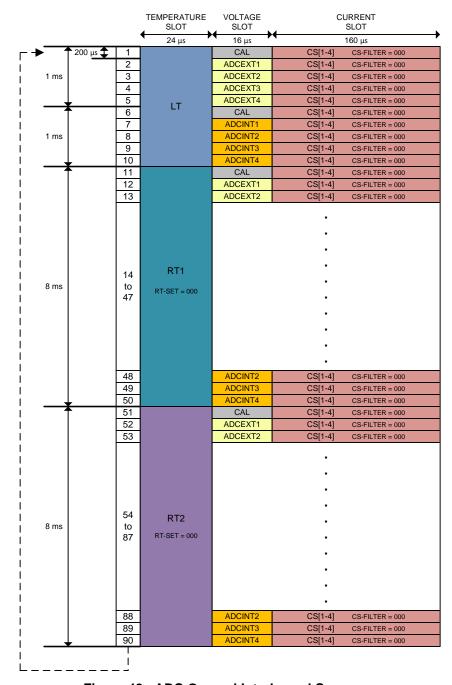

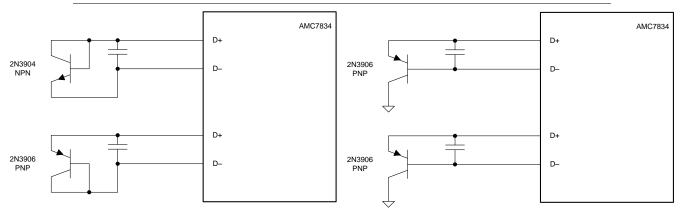

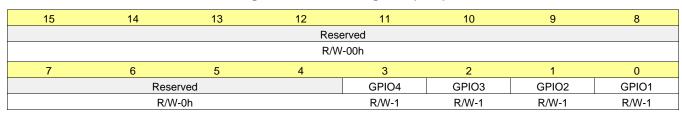

- The output voltage must not be greater than  $AV_{DD}$  or lower than  $AV_{SS}$ . A minimum of 100 mV headroom from  $AV_{DD}$  is required. The output voltage must not be greater than  $AV_{CC}$  or lower than AGND. A minimum of 100 mV headroom from  $AV_{CC}$  is required.