AFE78101, AFE88101 ZHCSP80 - DECEMBER 2022

# 具有电压基准和诊断 ADC 的 AFEx8101 16 位和 14 位低功耗 DAC, 适用于 4mA 至 20mA 环路供电应用

# 1 特性

- 提供功能安全

- 可帮助进行功能安全系统设计的文档: AFE88101、AFE78101

- 低静态电流:170 µA(典型值)

- 16 位或 14 位单调高性能 DAC

- 1.8V 电源: 0.15V 至 1.25V, 0.2V 至 1.0V

- 5V 电源: 0.3V 至 2.5V, 0.4V 至 2.0V

- 16 位时为 4-LSB INL

- 40°C 至 +125°C 范围内的 TUE 为 0.07% FSR (最大值)

- 可实现高级诊断的 12 位 3.84kSPS ADC

- 集成 1.25V 基准电压,温漂为 10ppm/°C

- 具有时钟输出的内部 1.2288MHz 振荡器

- 数字接口:

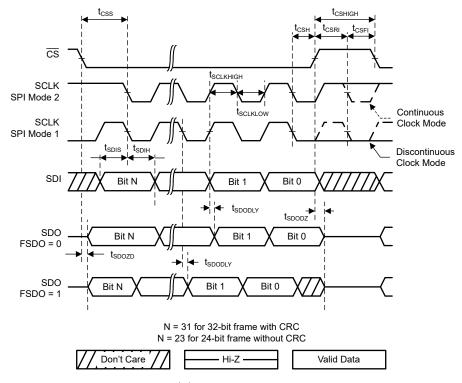

- 串行外设接口 (SPI)

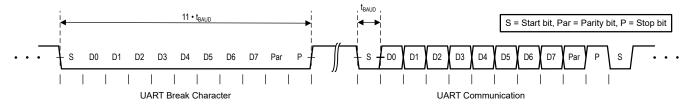

- 通用异步接收器/发送器 (UART)

- 故障检测:CRC 位错误检查、窗口式看门狗计时 器、诊断 ADC

- 宽工作温度范围: 55°C 至 +125°C

### 2 应用

- 2线变送器

- 4mA 至 20mA 环路供电应用

- 过程控制和工业自动化

- 智能发送器

- PLC 或 DCS I/O 模块

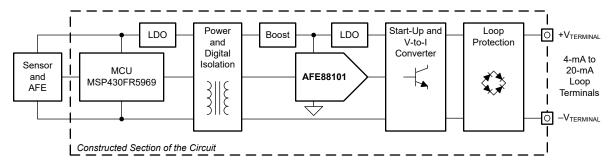

# 3 说明

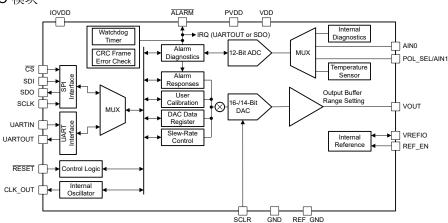

16 位 AFE88101 和 14 位 AFE78101 (AFEx8101) 是 具有电压输出的高度集成、高精度、极低功耗的数模转 换器 (DAC), 专为传感器变送器应用而设计。

AFEx8101 器件包含设计 4mA 至 20mA、2 线 (环路 供电)传感器变送器所需的大多数元件。除了高精度 DAC 之外,这些器件还包括一个 10ppm/°C 电压基准 和一个诊断模数转换器 (ADC)。为了适应内在和功能 安全问题,需要进行外部电压至电流转换和功率调节。

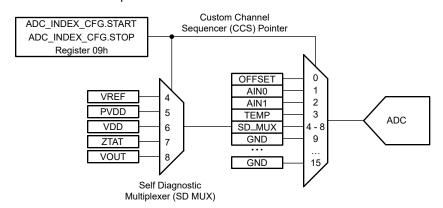

内部诊断 ADC 多路复用为多个内部节点,可实现自动 自我运行状况检查。此检查能够检测内部偏置源、电源 稳压器、电压基准、DAC 输出、芯片温度和可选外部 电压源的错误或故障。如果从诊断 ADC、CRC 帧错误 校验或窗口化看门狗计时器检测到任何故障,这些器件 可以选择发出中断,进入与标准 NAMUR 输出值和/或 用户指定的自定义值相对应的失效防护状态。

这些器件采用低至 1.71V 的电源供电,最大静态电流 为 210µA。这些器件的额定工作温度范围为 - 40°C 至 +125°C,但工作温度范围为 - 55°C 至 +125°C。

### 器件信息

| 器件型号     | 分辨率  | 封装 <sup>(1)</sup> |

|----------|------|-------------------|

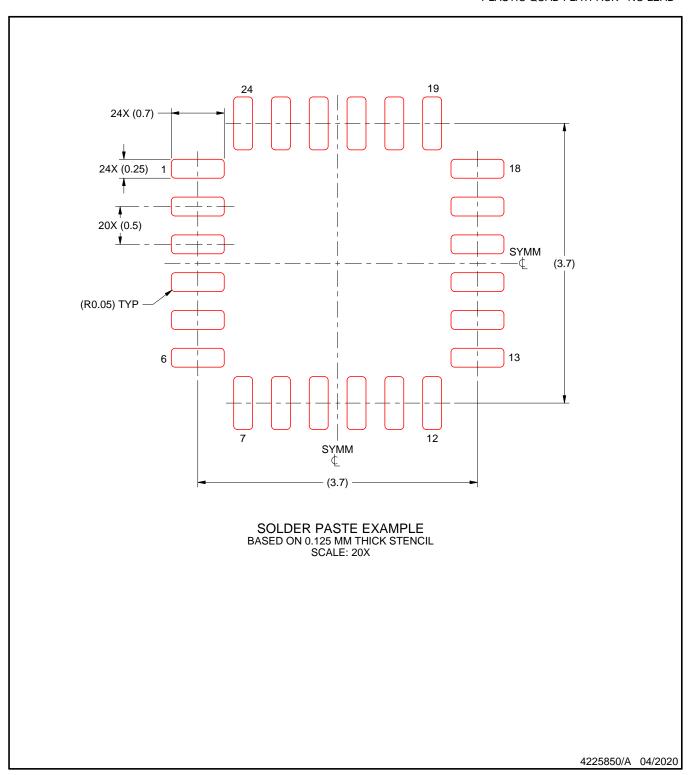

| AFE78101 | 14 位 | RRU (UQFN, 24)    |

| AFE88101 | 16 位 | 4.00mm × 4.00mm   |

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

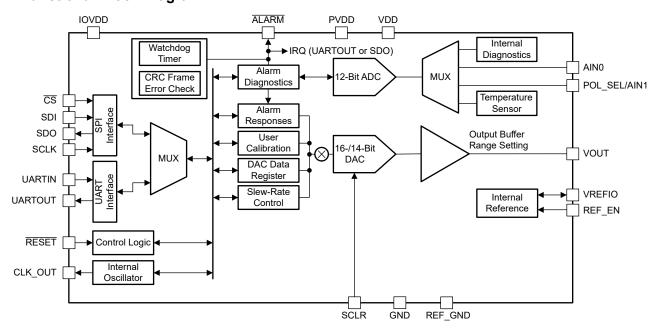

功能方框图

# **Table of Contents**

| 1 特性                                       | 1  | 7.3 Feature Description                 | 23 |

|--------------------------------------------|----|-----------------------------------------|----|

| 2 应用                                       |    | 7.4 Device Functional Modes             | 44 |

|                                            |    | 7.5 Programming                         | 46 |

| 4 Revision History                         |    | 7.6 Register Maps                       |    |

| 5 Pin Configuration and Functions          |    | 8 Application and Implementation        | 72 |

| 6 Specifications                           |    | 8.1 Application Information             | 72 |

| 6.1 Absolute Maximum Ratings               |    | 8.2 Typical Application                 |    |

| 6.2 ESD Ratings                            |    | 8.3 Initialization Set Up               | 79 |

| 6.3 Recommended Operating Conditions       |    | 8.4 Power Supply Recommendations        | 80 |

| 6.4 Thermal Information                    |    | 8.5 Layout                              |    |

| 6.5 Electrical Characteristics             |    | 9 Device and Documentation Support      |    |

| 6.6 Timing Requirements                    | 10 | 9.1 Documentation Support               |    |

| 6.7 Timing Diagrams                        |    | 9.2 接收文档更新通知                            | 82 |

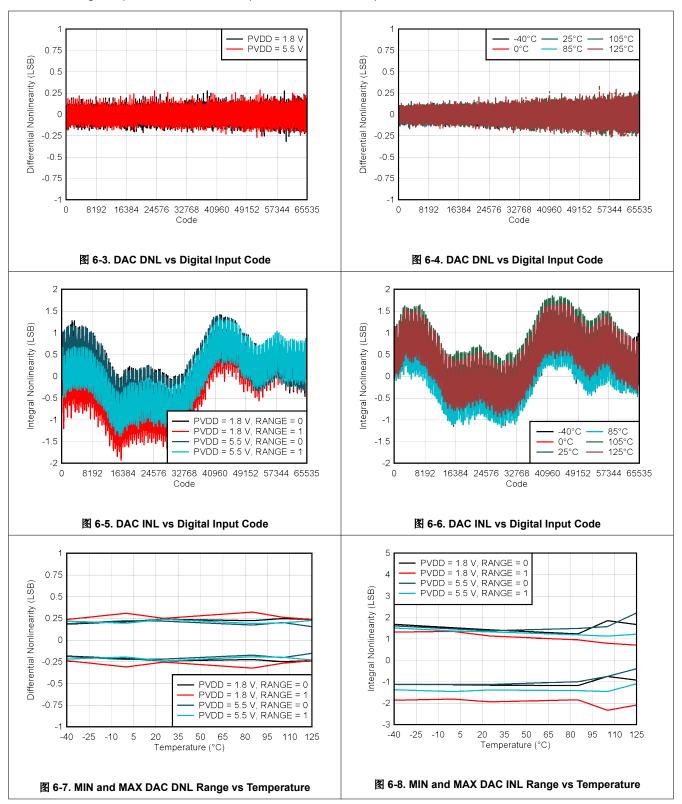

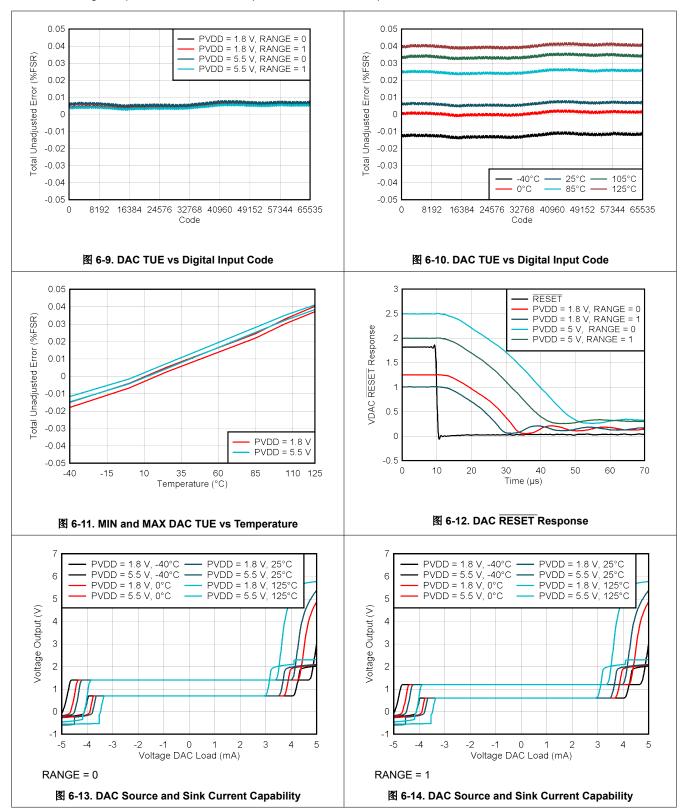

| 6.8 Typical Characteristics: VOUT DAC      |    | 9.3 支持资源                                | 82 |

| 6.9 Typical Characteristics: ADC           |    | 9.4 Trademarks                          | 82 |

| 6.10 Typical Characteristics: Reference    |    | 9.5 Electrostatic Discharge Caution     | 82 |

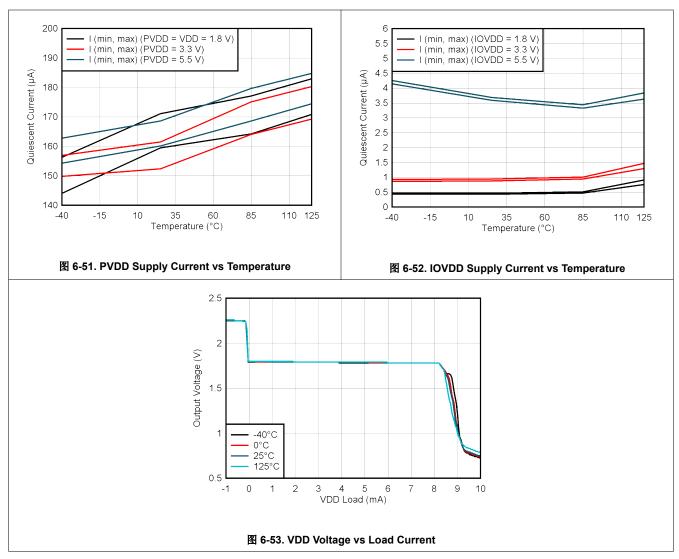

| 6.11 Typical Characteristics: Power Supply | 21 | 9.6 术语表                                 | 82 |

| 7 Detailed Description                     |    | 10 Mechanical, Packaging, and Orderable |    |

| 7.1 Overview                               |    | Information                             | 82 |

| 7.2 Functional Block Diagram               | 22 |                                         |    |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| DATE          | REVISION | NOTES            |  |  |

|---------------|----------|------------------|--|--|

| December 2022 | *        | Initial release. |  |  |

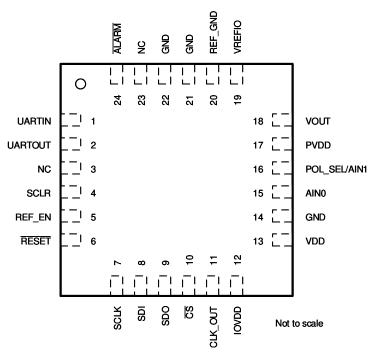

# **5 Pin Configuration and Functions**

图 5-1. RRU (24-pin UQFN) Package, Top View

表 5-1. Pin Functions

| PIN          |           | TYPE(1)                                                                                                                                                                                                                                       | DECORPORTION                                                                                                                                                                                                                                      |

|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.       | IYPE                                                                                                                                                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                       |

| AIN0         | 15        | Al                                                                                                                                                                                                                                            | ADC input voltage. The input range is 0 V to VREF if PVDD = VDD, or 0 V to 2 × VREF if PVDD > 2.7 V.                                                                                                                                              |

| ALARM        | 24        | DO                                                                                                                                                                                                                                            | Alarm notification. Open drain. When alarm condition is asserted, this pin is held to logic low; otherwise, this pin is in a high-impedance state (Hi-Z).                                                                                         |

| CLK_OUT      | 11        | DO                                                                                                                                                                                                                                            | Clock output. This pin can be configured as a clock output for the 1.2288-MHz internal clock.                                                                                                                                                     |

| CS           | 10        | SPI chip-select. Data bits are clocked into the serial shift register when $\overline{CS}$ is logic low. When $\overline{CS}$ is high, SDO is in a high-impedance state and data on SDI are ignored. Do not leave any digital input floating. |                                                                                                                                                                                                                                                   |

| GND          | 14        | P Digital and analog ground. Ground reference point for all circuitry on the device.                                                                                                                                                          |                                                                                                                                                                                                                                                   |

| GND          | 21,<br>22 | Р                                                                                                                                                                                                                                             | Digital and analog ground.                                                                                                                                                                                                                        |

| IOVDD        | 12        | Р                                                                                                                                                                                                                                             | Interface supply. Supply voltage for digital input and output circuitry. This voltage sets the logical thresholds for the digital interfaces.                                                                                                     |

| NC           | 3, 23     | -                                                                                                                                                                                                                                             | No connection. Leave floating.                                                                                                                                                                                                                    |

| POL_SEL/AIN1 | 16        | DI/AI                                                                                                                                                                                                                                         | ADC input voltage if SPECIAL_CFG.AIN1_ENB bit is set to 1. The input range is 0 V to VREF if PVDD = VDD, or 0 V to 2 × VREF if PVDD > 2.7 V. Otherwise, this pin acts as ALMV_POL, which sets the polarity of the VOUT alarm voltage.             |

| PVDD         | 17        | Р                                                                                                                                                                                                                                             | Power supply for the internal low-dropout regulator (LDO), ADC input, and VOUT DAC output. When 2.7 V to 5.5 V is provided, the internal LDO turns on and drives VDD internally. When 1.71 V to 1.89 V is provided, the internal LDO is disabled. |

| REF_EN       | 5         | DI                                                                                                                                                                                                                                            | Internal VREF enable input. A logic high on this pin enables the internal VREF and the VREFIO pin outputs 1.25 V. A logic low on this pin disables the internal VREF and the external 1.25-V reference is required at the VREFIO pin.             |

| REF_GND      | 20        | Р                                                                                                                                                                                                                                             | GND reference for VREFIO pin.                                                                                                                                                                                                                     |

| RESET        | 6         | DI                                                                                                                                                                                                                                            | Reset. Logic low on this pin places the device into power-down mode and resets the device. Logic high returns the device to normal operation. Do not leave any digital input pins floating.                                                       |

# 表 5-1. Pin Functions (continued)

| PIN     |         | <b>TYP</b> =(1)                                                                                                                                                                                                   | PEOCHIPTION                                                                                                                                                                                                                                                             |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | AME NO. |                                                                                                                                                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                             |

| SCLK    | 7       | DI                                                                                                                                                                                                                | SPI serial clock. Data can be transferred at rates up to 12.5 MHz. SCLK is a Schmitt-trigger logic input. Connect to GND or logic low if not used. Do not leave any digital input pins floating.                                                                        |

| SCLR    | 4       | DI                                                                                                                                                                                                                | DAC clear input pin in SPI mode. A logic high on this pin forces the DAC output into a CLEAR state. Connect to GND in UBM. Do not leave any digital input pins floating.                                                                                                |

| SDI     | 8       | SPI data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clinput. SDI is a Schmitt-Trigger logic input. Do not leave any digital input pins floating.              |                                                                                                                                                                                                                                                                         |

| SDO     | 9       | SPI data output. Data are output on the rising edge of SCLK when $\overline{CS}$ is logic low. Interrupt pin in the UART break mode (UBM). The output is in a Hi-Z state at power up and must be CONFIG register. |                                                                                                                                                                                                                                                                         |

| UARTIN  | 1       | DI                                                                                                                                                                                                                | UART data input. Connect to IOVDD or logic high if not used. Do not leave any digital input pins floating.                                                                                                                                                              |

| UARTOUT | 2       | DO                                                                                                                                                                                                                | UART data output. This pin can be configured to function as the IRQ pin in SPI only mode.                                                                                                                                                                               |

| VDD     | 13      | P/AO                                                                                                                                                                                                              | Power supply. When 2.7 V to 5.5 V is provided on PVDD pin, the internal LDO drives VDD internally. Connect a 1- $\mu$ F to 10- $\mu$ F capacitor to this pin. When 1.71 V to 1.89 V is provided on the PVDD pin, an external power supply must be provided on this pin. |

| VOUT    | 18      | AO                                                                                                                                                                                                                | DAC output voltage.                                                                                                                                                                                                                                                     |

| VREFIO  | 19      | AI/AO                                                                                                                                                                                                             | When the internal VREF is enabled by REF_EN pin, this pin outputs the internal VREF voltage. In this case, a load capacitance of 70-nF to 130-nF is required for stability. When disabled, this pin is the external 1.25-V reference input.                             |

<sup>(1)</sup> AI = analog input, AO = analog output, DI = digital input, DO = digital output, P = power.

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                      |                                 | MIN   | MAX         | UNIT |

|------------------|----------------------|---------------------------------|-------|-------------|------|

|                  |                      | PVDD, IOVDD to GND              | - 0.3 | 5.5         | V    |

|                  |                      | VDD to GND                      | - 0.3 | 1.98        | V    |

|                  | Voltage              | AIN0, POL_SEL/AIN1, VOUT to GND | - 0.3 | PVDD + 0.3  | V    |

|                  | Voltage              | Digital Input/Output to GND     | - 0.3 | IOVDD + 0.3 | V    |

|                  |                      | VREFIO to GND                   | - 0.3 | VDD + 0.3   | V    |

|                  |                      | REF_GND to GND                  | - 0.3 | 0.3         | V    |

|                  | Input current        | Current into any pin            | - 10  | 10          | mA   |

| TJ               | Junction temperature |                                 | - 55  | 150         | °C   |

| T <sub>stg</sub> | Storage temperature  |                                 | - 65  | 150         | C    |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |               |                                                                                 | VALUE | UNIT       |

|--------------------|---------------|---------------------------------------------------------------------------------|-------|------------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 |            |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | , <b>v</b> |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                     |                                        | MIN  | NOM  | MAX  | UNIT |

|----------------|---------------------|----------------------------------------|------|------|------|------|

|                | PVDD to GND         | PVDD > 2.7 V, VDD internally generated | 2.7  |      | 5.5  | V    |

|                | . 155 % 5.15        | PVDD = VDD                             | 1.71 |      | 1.89 | V    |

|                | VDD to GND          |                                        | 1.71 |      | 1.89 | V    |

|                | IOVDD to GND        |                                        | 1.71 |      | 5.5  | V    |

|                | VREFIO to GND       | External VREF                          | 1.2  | 1.25 | 1.3  | V    |

| _              | Ambient temperature | Specified                              | - 40 |      | 125  | °C   |

| T <sub>A</sub> |                     | Operating                              | - 55 |      | 125  | C    |

# **6.4 Thermal Information**

|                           |                                              | AFEx8101   |      |

|---------------------------|----------------------------------------------|------------|------|

|                           | THERMAL METRIC <sup>(1)</sup>                | RRU (UQFN) | UNIT |

|                           |                                              | 24 PINS    |      |

| R <sub> θ JA</sub>        | Junction-to-ambient thermal resistance       | 103.1      | °C/W |

| R <sub>θ JC(top)</sub>    | Junction-to-case (top) thermal resistance    | 84.4       | °C/W |

| R <sub>θ JC(bottom)</sub> | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

| R <sub> θ JB</sub>        | Junction-to-board thermal resistance         | 69.5       | °C/W |

| ΨJT                       | Junction-to-top characterization parameter   | 0.4        | °C/W |

| Ψ <sub>JB</sub>           | Junction-to-board characterization parameter | 68.4       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

all minimum and maximum values at  $T_A$  =  $-40^{\circ}$ C to +125°C and all typical values at  $T_A$  = 25°C, PVDD = VDD = IOVDD = 1.8 V, external or internal VREFIO = 1.25 V,  $R_{LOAD}$  = 50 k $\Omega$  to GND,  $C_{LOAD}$  = 100 pF to GND, and digital inputs at IOVDD or GND (unless otherwise noted)

|                | PARAMETER                                         | TEST CONDITIONS                                                                                  | MIN    | TYP  | MAX  | UNIT                |

|----------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|------|------|---------------------|

| VOUT D         | AC STATIC PERFORMANCE                             |                                                                                                  |        |      |      |                     |

|                | Dluff                                             | AFE88101                                                                                         | 16     |      |      | D:4-                |

|                | Resolution                                        | AFE78101                                                                                         | 14     |      |      | Bits                |

| 18.11          | 1 (1)                                             | AFE88101                                                                                         | - 4    |      | 4    | 1.00                |

| INL            | Integral nonlinearity <sup>(1)</sup>              | AFE78101                                                                                         | - 2    |      | 2    | LSB                 |

| DNL            | Differential nonlinearity <sup>(1)</sup>          |                                                                                                  | - 1    |      | 1    | LSB                 |

|                | ·                                                 | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                   | - 0.07 |      | 0.07 |                     |

| TUE            | Total unadjusted error <sup>(1)</sup>             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                              | - 0.05 |      | 0.05 | %FSR                |

|                |                                                   | T <sub>A</sub> = 25°C                                                                            | - 0.04 |      | 0.04 |                     |

|                |                                                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                   | - 0.07 |      | 0.07 |                     |

| ZCE            | Zero code error                                   | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                              | - 0.05 |      | 0.05 | %FSR                |

|                |                                                   | T <sub>A</sub> = 25°C                                                                            | - 0.03 |      | 0.03 |                     |

| ZCE-TC         | Zero code error temperature coefficient           | - A                                                                                              |        | ±3   |      | ppm/°C              |

|                |                                                   | T <sub>A</sub> = -40°C to +125°C                                                                 | - 0.07 |      | 0.07 | FF                  |

| OE             | Offset error <sup>(1)</sup>                       | T <sub>A</sub> = -40°C to +85°C                                                                  | - 0.05 |      | 0.05 | %FSR                |

| OL.            | Oliset error                                      | T <sub>A</sub> = 25°C                                                                            | - 0.03 |      | 0.03 | 701 011             |

| OE-TC          | Offset error temperature coefficient (1)          | 1 <sub>A</sub> - 20 0                                                                            | 0.00   | ±3   | 0.00 | ppm/°C              |

| OL-10          | Chacterior temperature occinicient                | T <sub>A</sub> = -40°C to +125°C                                                                 | - 0.04 |      | 0.04 | ррпіі О             |

| GE             | Gain error <sup>(1)</sup>                         | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                              | - 0.04 |      | 0.04 |                     |

| OL             |                                                   | T <sub>A</sub> = 25°C                                                                            |        |      | 0.04 | 701 OIX             |

| GE-TC          | Gain error temperature coefficient <sup>(1)</sup> | 1 <sub>A</sub> - 25 C                                                                            | - 0.03 | ±3   | 0.03 | ppm FSR/°C          |

| GE-10          | Gain error temperature coefficient                | T = 40°0 to 1405°0                                                                               | 0.07   |      | 0.07 | ppiii FSR/ C        |

| F0F            | Full scale sees                                   | T <sub>A</sub> = -40°C to +125°C                                                                 | - 0.07 |      | 0.07 | 0/ FCD              |

| FSE            | Full-scale error                                  | T <sub>A</sub> = -40°C to +85°C                                                                  | - 0.06 |      | 0.06 | %FSR                |

|                |                                                   | T <sub>A</sub> = 25°C                                                                            | - 0.04 |      | 0.04 |                     |

| FSE-TC         | '                                                 |                                                                                                  |        | ±3   |      | ppm FSR/°C          |

| VOUT DA        | AC DYNAMIC PERFORMANCE                            | 14/1 2/ 1 12/1 4/ 1 18/1 1 20 00                                                                 |        |      |      |                     |

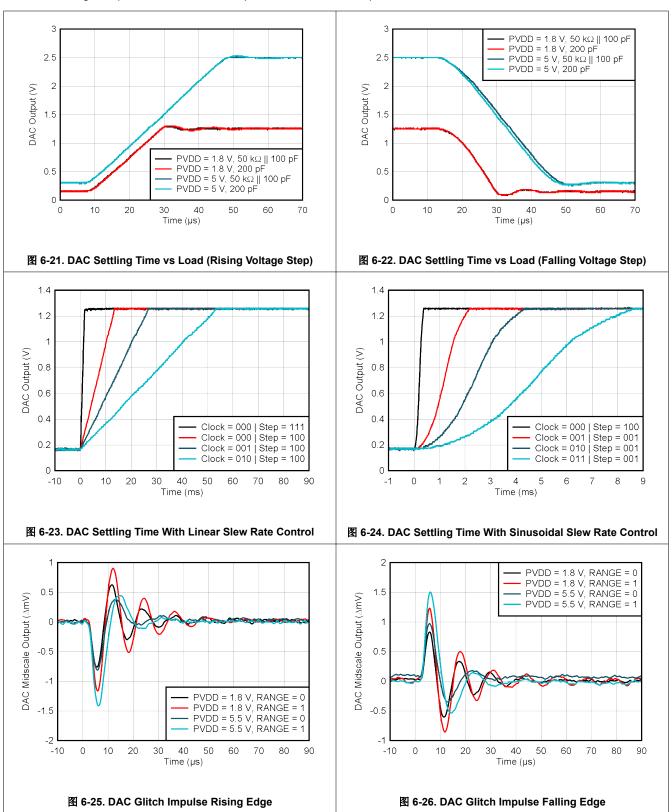

| t <sub>s</sub> | Output voltage settling time <sup>(4)</sup>       | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to ±2 LSB,<br>PVDD = VDD = 1.8 V, VREFIO = 1.25 V |        | 65   |      | μs                  |

|                |                                                   | 10-mV step settling to ±2 LSB,<br>PVDD = VDD = 1.8 V, VREFIO = 1.25 V                            |        | 30   |      |                     |

| SR             | Slew rate <sup>(4)</sup>                          | Fullscale transition measured from 10% to 90%                                                    |        | 2    |      | V/µs                |

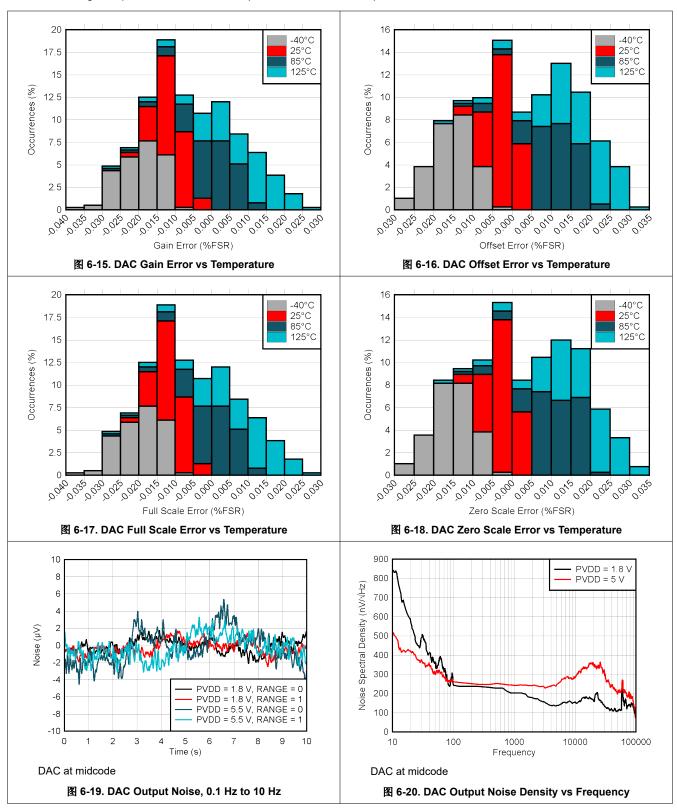

| V              | Output noise <sup>(4)</sup>                       | 0.1 Hz to 10 Hz, DAC at midscale,<br>PVDD = VDD = 1.8 V, VREFIO = 1.25 V                         |        | 0.25 |      | LSB <sub>PP</sub>   |

| V <sub>n</sub> | Output Hoise                                      | 100-kHz bandwidth, DAC at midscale,<br>PVDD = VDD = 1.8 V, VREFIO = 1.25 V                       |        | 32   |      | μVrms               |

| . ,            |                                                   | Measured at 1 kHz, DAC at midscale,<br>PVDD = VDD = 1.8 V, VREFIO = 1.25 V                       |        | 180  |      |                     |

| V <sub>n</sub> | Output noise density                              | Measured at 1 kHz, DAC at midscale,<br>PVDD = 5 V, VREFIO = 1.25 V                               |        | 260  |      | nV/ √ <del>Hz</del> |

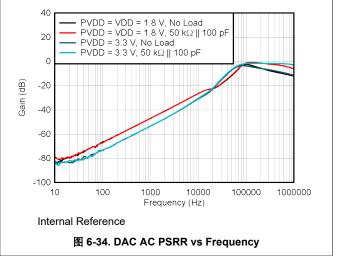

|                | Power supply rejection ratio (AC)                 | 200-mV 50-Hz to 60-Hz sine wave superimposed on power supply voltage, DAC at midscale.           |        | 85   |      | dB                  |

|                | Code change glitch impulse                        | Midcode ±1 LSB (including feedthrough) PVDD = VDD = 1.8 V, VREFIO = 1.25 V                       |        | 4.5  |      | nV-s                |

|                | Code change glitch magnitude                      | Midcode ±1 LSB (including feedthrough) PVDD = 5 V, VREFIO = 1.25 V                               |        | 1.5  |      | mV                  |

|                |                                                   |                                                                                                  |        |      |      |                     |

# **6.5 Electrical Characteristics (continued)**

all minimum and maximum values at  $T_A$  =  $-40^{\circ}$ C to +125°C and all typical values at  $T_A$  = 25°C, PVDD = VDD = IOVDD = 1.8 V, external or internal VREFIO = 1.25 V,  $R_{LOAD}$  = 50 k  $\Omega$  to GND,  $C_{LOAD}$  = 100 pF to GND, and digital inputs at IOVDD or GND (unless otherwise noted)

|                   | PARAMETER                                | TEST CONDITIONS                                      | MIN    | TYP    | MAX    | UNIT    |

|-------------------|------------------------------------------|------------------------------------------------------|--------|--------|--------|---------|

| VOUT E            | DAC OUTPUT CHARACTERISTICS               |                                                      |        |        |        |         |

|                   |                                          | RANGE = 0, PVDD = VDD                                | 0.15   |        | 1.25   |         |

|                   | Output wells are now as                  | RANGE = 1, PVDD = VDD                                | 0.2    |        | 1.0    |         |

|                   | Output voltage range                     | RANGE = 0, PVDD > 2.7 V, VDD generated               | 0.3    |        | 2.5    | V       |

|                   |                                          | RANGE = 1, PVDD > 2.7 V, VDD generated               | 0.4    |        | 2.0    |         |

|                   | VOLIT clares output high                 | PVDD > 2.7 V, VDD internally generated               | - 6%   | 2.5    | +6%    | V       |

|                   | VOUT alarm output high                   | PVDD = VDD                                           | - 6%   | 1.25   | +6%    | V       |

|                   | VOLIT                                    | PVDD > 2.7 V, VDD internally generated               | - 5%   | 0.3    | +5%    | .,      |

|                   | VOUT alarm output low                    | PVDD = VDD                                           | - 5%   | 0.15   | +5%    | V       |

| R <sub>LOAD</sub> | Resistive load <sup>(2)</sup>            |                                                      | 10     |        |        | kΩ      |

| C <sub>LOAD</sub> | Capacitive load <sup>(2)</sup>           |                                                      |        |        | 100    | pF      |

|                   | Load regulation                          | DAC at midscale, −1 mA ≤ I <sub>OUT</sub> ≤ +1 mA    |        | 10     |        | μV/mA   |

|                   | 0                                        | Full scale output shorted to GND                     |        | 5      |        |         |

|                   | Short-circuit current                    | Zero output shorted to VDD                           |        | 5      |        | mA      |

|                   | Output voltage headroom to PVDD          | DAC at full code, I <sub>OUT</sub> = 1 mA (sourcing) | 200    |        |        | mV      |

|                   | Output voltage footroom to GND           | DAC at zero code, I <sub>OUT</sub> = 1 mA (sinking)  | 200    |        |        | mV      |

| 7                 | DC small signal output impedance         | DAC at midscale                                      |        | 10     |        | mΩ      |

| Z <sub>O</sub>    |                                          | Output Hi-Z                                          |        | 500    |        | kΩ      |

|                   | Power supply rejection ratio (dc)        | DAC at midscale; PVDD = 1.8 V ± 10%                  |        | 0.1    |        | mV/V    |

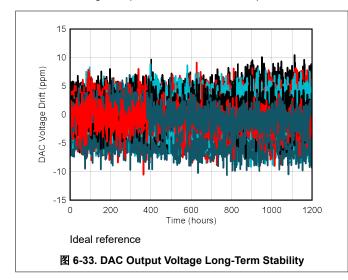

|                   | Output voltage drift vs time, 1000 hours | T <sub>A</sub> = 35°C, VOUT = midscale, ideal VREF   |        | ±5     |        | ppm FSR |

| DIAGNO            | OSTIC ADC                                | ·                                                    |        |        |        |         |

|                   | Input voltage range                      | PVDD = VDD                                           | 0      |        | 1.25   | V       |

|                   | input voltage range                      | PVDD > 2.7 V                                         | 0      |        | 2.5    | V       |

|                   | Resolution                               |                                                      |        | 12     |        | Bits    |

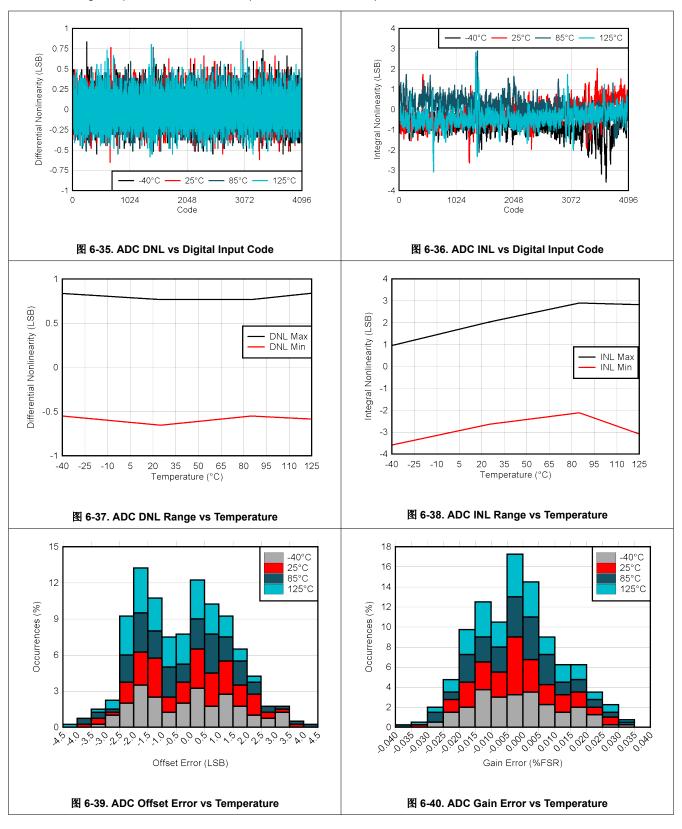

| DNL               | Differential nonlinearity                | Specified 12-bit monotonic                           | - 1    | ±0.2   | 1      | LSB     |

| INL               | Integral nonlinearity                    |                                                      | - 4    | ±1     | 4      | LSB     |

| OE                | Offset error                             | After calibration                                    | - 10   | ±1.6   | 10     | LSB     |

| GE                | Gain error                               |                                                      | - 0.8  | ±0.13  | 0.8    | %FSR    |

|                   | Noise                                    |                                                      |        | ±4     |        | LSB     |

|                   | Input capacitance                        |                                                      |        | 6      |        | pF      |

|                   | Input bias current                       | ADC not converting                                   | - 50   |        | 50     | nA      |

|                   | Acquisition time                         |                                                      |        | 52     |        | μs      |

|                   | Conversion time                          |                                                      |        | 210    |        | μs      |

|                   | Conversion rate                          |                                                      |        |        | 3.84   | kSPS    |

|                   | Temperature sensor accuracy              |                                                      |        | 5      |        | °C      |

| INTERN            | IAL OSCILLATOR                           |                                                      |        |        |        |         |

|                   | Frequency                                | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       | 1.2165 | 1.2288 | 1.2411 | MHz     |

# **6.5 Electrical Characteristics (continued)**

all minimum and maximum values at  $T_A = -40^{\circ}\text{C}$  to +125°C and all typical values at  $T_A = 25^{\circ}\text{C}$ , PVDD = VDD = IOVDD = 1.8 V, external or internal VREFIO = 1.25 V,  $R_{LOAD} = 50 \text{ k}\Omega$  to GND,  $C_{LOAD} = 100 \text{ pF}$  to GND, and digital inputs at IOVDD or GND (unless otherwise noted)

| GND (u              | nless otherwise noted)                      |                                                      |       |      |       |                     |

|---------------------|---------------------------------------------|------------------------------------------------------|-------|------|-------|---------------------|

|                     | PARAMETER                                   | TEST CONDITIONS                                      | MIN   | TYP  | MAX   | UNIT                |

| VOLTAG              | E REFERENCE INPUT                           |                                                      |       |      |       |                     |

| Z <sub>VREFIO</sub> | Reference input impedance (VREFIO)          | RANGE = 0                                            |       | 125  |       | kΩ                  |

| ∠VREFIO             | Treference input impedance (VIVLI 10)       | RANGE = 1                                            |       | 180  |       | K 22                |

| C <sub>VREFIO</sub> | Reference input capacitance (VREFIO)        |                                                      |       | 100  |       | pF                  |

| VOLTAG              | E REFERENCE OUTPUT                          |                                                      |       |      |       |                     |

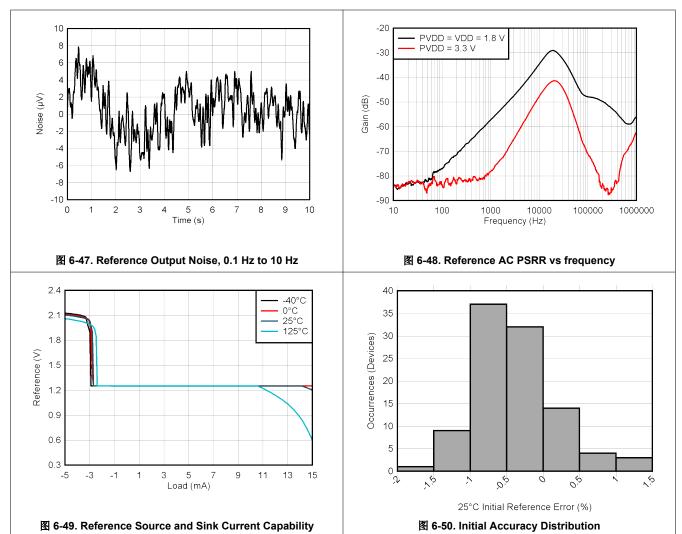

|                     | Output (initial accuracy)(3)                | T <sub>A</sub> = 25°C                                | 1.248 | 1.25 | 1.252 | V                   |

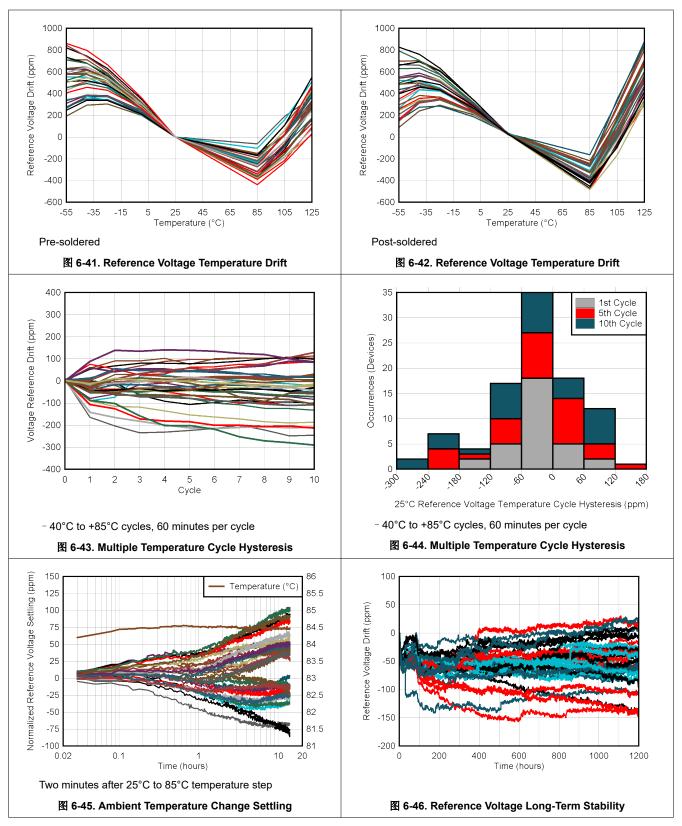

|                     | Output drift <sup>(3)</sup>                 | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |       |      | 10    | ppm/℃               |

|                     | Output impedance <sup>(3)</sup>             |                                                      |       | 0.1  |       | Ω                   |

|                     | Output noise <sup>(3)</sup>                 | 0.1 Hz to 10 Hz                                      |       | 7.5  |       | $\mu V_{PP}$        |

|                     | Output noise density <sup>(3)</sup>         | Measured at 10 kHz, reference load = 100 nF          |       | 200  |       | nV/ √ <del>Hz</del> |

|                     |                                             | Sourcing, 0.1% VREF change from nominal              |       | 2.5  |       |                     |

|                     | Load current <sup>(3)</sup>                 | Sinking, 0.1% VREF change from nominal               |       |      | 0.3   | mA                  |

|                     | Load regulation <sup>(3)</sup>              | Sourcing, 0 mA to 2.5 mA                             |       | 4    |       | μV/mA               |

| C <sub>OUT</sub>    | Stable output capacitance                   | $T_A$ = -40°C to +125°C,<br>ESR from 10 mΩ to 400 mΩ | 70    | 100  | 130   | nF                  |

|                     | Line regulation <sup>(3)</sup>              |                                                      |       | 80   |       | μV/V                |

|                     | Output voltage drift vs time <sup>(3)</sup> | T <sub>A</sub> = 35°C, 1000 hours                    |       | ±100 |       | ppm                 |

|                     | Thermal hysteresis <sup>(3)</sup>           | 1st cycle                                            |       | 500  |       | μV                  |

|                     |                                             | Additional cycles                                    |       | 25   |       | μV                  |

| VDD VO              | LTAGE REGULATOR OUTPUT                      | ,                                                    |       |      |       |                     |

|                     | Output voltage                              |                                                      | 1.71  | 1.8  | 1.89  | V                   |

|                     | Output impedance <sup>(3)</sup>             | PVDD = 3.3 V, sourcing, 0.5 mA to 2.5 mA             |       | 3    |       | Ω                   |

|                     | Load current <sup>(3)</sup>                 | PVDD = 3.3 V, sourcing, 1% VDD change from nominal   |       | 4    |       | mA                  |

| THERMA              | AL ALARM                                    |                                                      |       | ,    |       |                     |

|                     | Alarm trip point                            |                                                      |       | 130  |       | °C                  |

|                     | Warning trip point                          |                                                      |       | 85   |       | °C                  |

|                     | Hysteresis                                  |                                                      |       | 12   |       | °C                  |

|                     | Trip point absolute accuracy                |                                                      |       | 5    |       | °C                  |

|                     | Trip point relative accuracy                |                                                      |       | 2    |       | °C                  |

| DIGITAL             | INPUT CHARACTERISTICS                       |                                                      |       |      |       |                     |

| V <sub>IH</sub>     | High-level input voltage                    |                                                      | 0.7   |      |       | V/IOVDD             |

| V <sub>IL</sub>     | Low-level input voltage                     |                                                      |       | ,    | 0.3   | V/IOVDD             |

|                     | Hysteresis voltage                          |                                                      | 0.05  | ,    |       | V/IOVDD             |

|                     | Input current                               |                                                      | - 400 |      | 400   | nA                  |

|                     | Pin capacitance                             | Per pin                                              |       | 10   |       | pF                  |

| DIGITAL             | OUTPUT CHARACTERISTICS                      |                                                      |       |      |       |                     |

| V <sub>OH</sub>     | High-level output voltage                   | I <sub>SOURCE</sub> = 1 mA                           | 0.8   |      |       | V/IOVDD             |

| V <sub>OL</sub>     | Low-level output voltage                    | I <sub>SINK</sub> = 1 mA                             |       |      | 0.2   | V/IOVDD             |

| V <sub>OL</sub>     | Open-drain low-level output voltage         | I <sub>SINK</sub> = 2 mA                             |       |      | 0.3   | V                   |

|                     | Output pin capacitance                      |                                                      | +     | 10   |       | pF                  |

# **6.5 Electrical Characteristics (continued)**

all minimum and maximum values at  $T_A = -40^{\circ}\text{C}$  to +125°C and all typical values at  $T_A = 25^{\circ}\text{C}$ , PVDD = VDD = IOVDD = 1.8 V, external or internal VREFIO = 1.25 V,  $R_{LOAD} = 50 \text{ k}\,\Omega$  to GND,  $C_{LOAD} = 100 \text{ pF}$  to GND, and digital inputs at IOVDD or GND (unless otherwise noted)

| PARAMETER                                   | TEST CONDITIONS                                                                                                                                                                                                     | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQUIREMENTS                                |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Current flowing into DVDD                   | PVDD only, VDD internally generated, DAC at zero-<br>scale, ADC and SPI static, internal reference                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sub>PVDD</sub> Current flowing into PVDD | Shared PVDD and VDD connection, DAC at zero-scale, ADC and SPI static                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | μА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDD LDO quiescent current                   | From PVDD                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Current flowing into VDD                    | Shared PVDD and VDD connection, DAC at zero-<br>scale, ADC and SPI static, internal reference                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Internal reference current consumption      | From external or internally generated VDD                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADC current consumption                     | From PVDD, ADC converting at 3.84 kSPS                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Recommended VDD decoupling capacitance      |                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

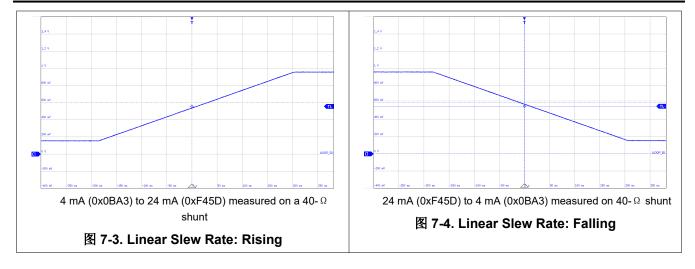

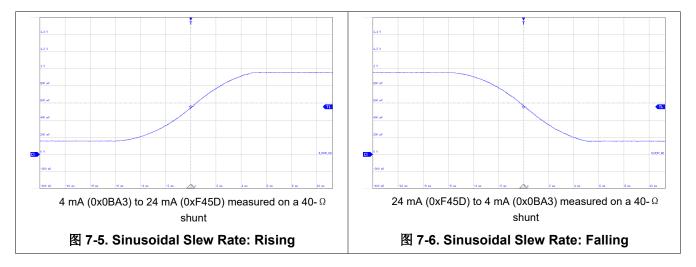

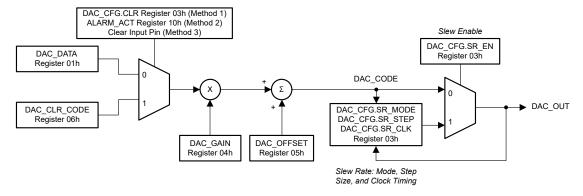

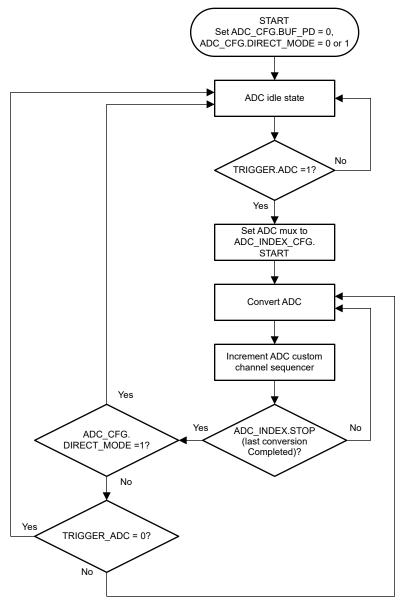

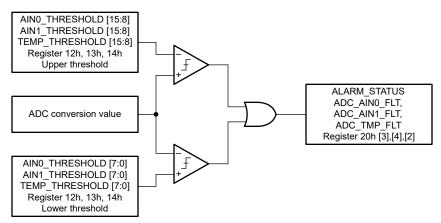

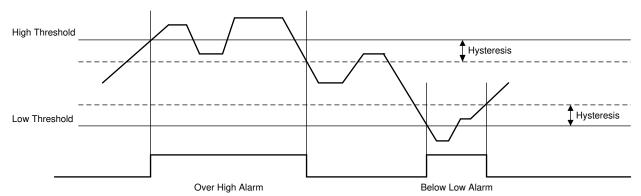

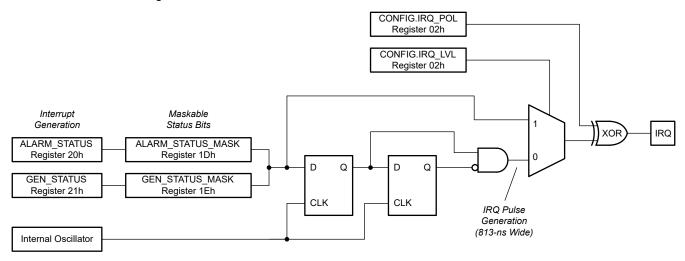

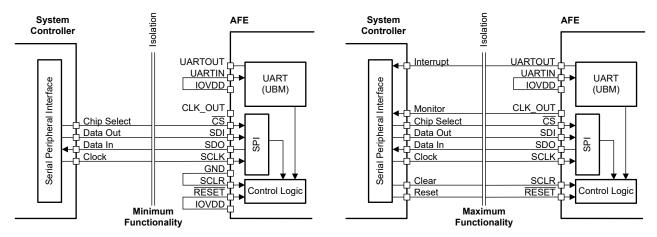

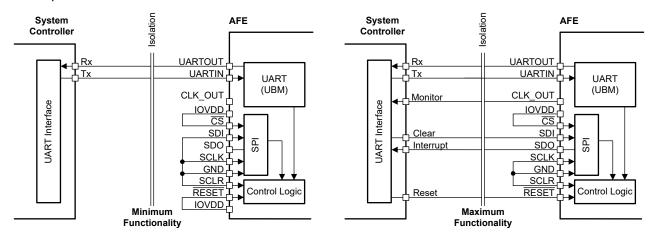

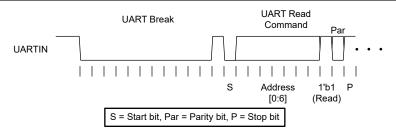

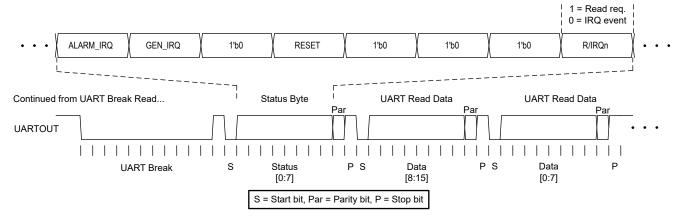

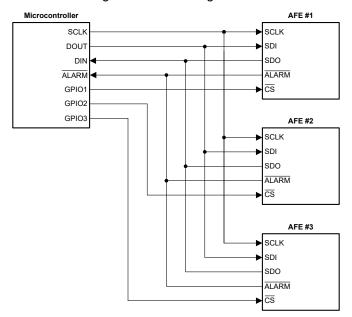

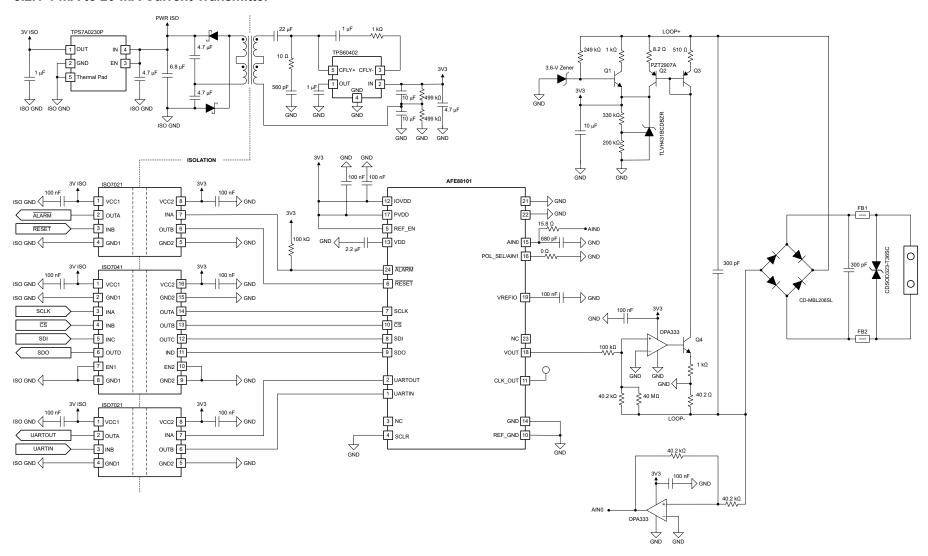

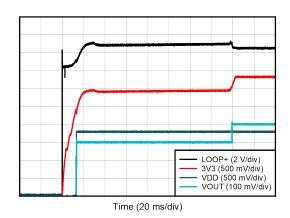

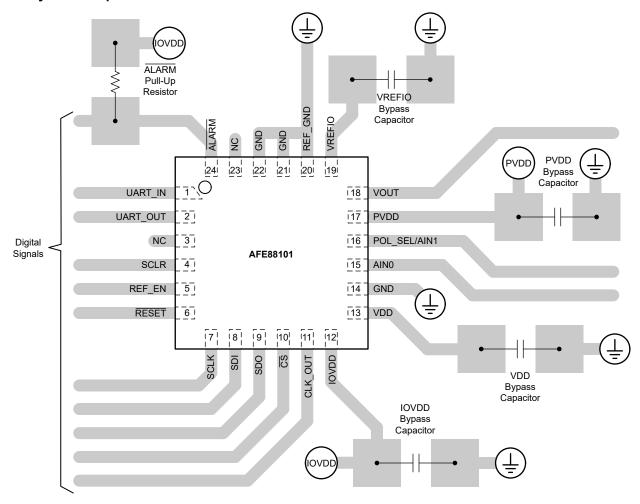

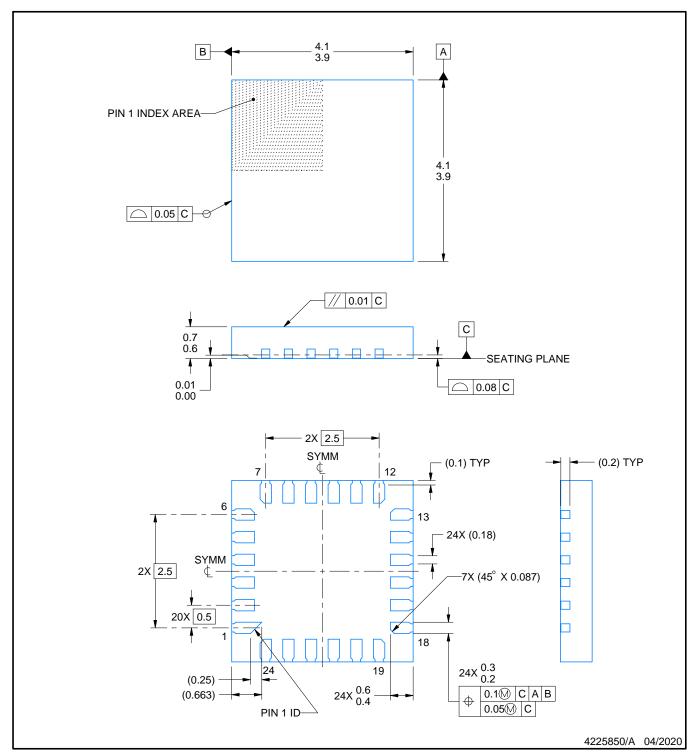

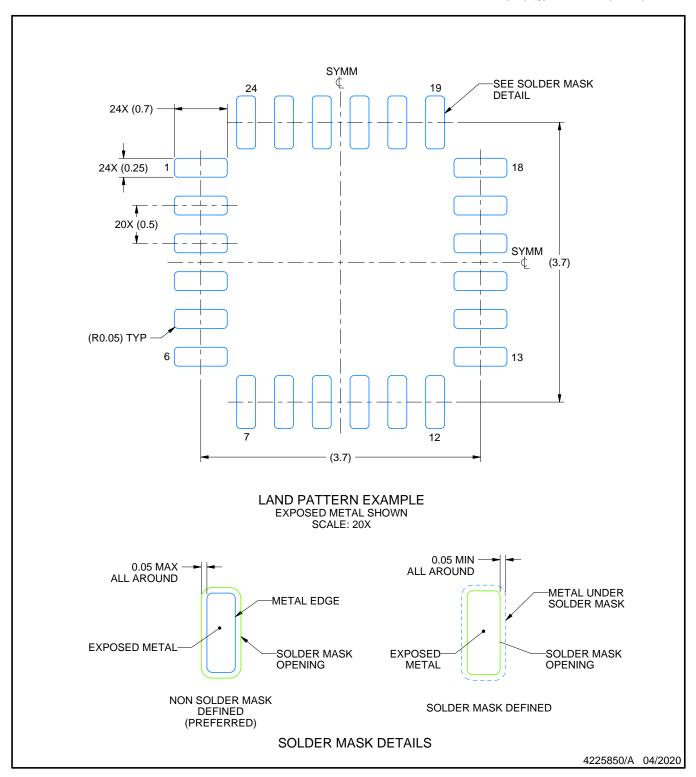

| Current flowing into IOVDD                  | SPI static                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |