ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

# 四通道, 250 每秒百万次采样 (MSPS) 接收器和反馈模数转换器 (ADC)

### 查询样品: ADS58H40

# 特性

- 四通道 .

- 三个不同的运行模式:

- 11 位: 250MSPS

- 11 位 SNRBoost<sup>3G+</sup>: 250MSPS

- 14 位: 250MSPS (突发模式)

- 最大采样数据速率: 250MSPS

- 功率耗散:

- 11 位模式: 每通道 365mW

- SNRBoost<sup>3G+</sup> 带宽: 2x 45MHz 或者 90MHz

- **170MHz IF** 上的频谱性能(典型值):

- 信噪比 (SNR): 在 SNRBoost<sup>3G+</sup> 的 90MHz 波 段下为 70.5dBFS

- 无杂散动态范围 (SFDR): 85dBc

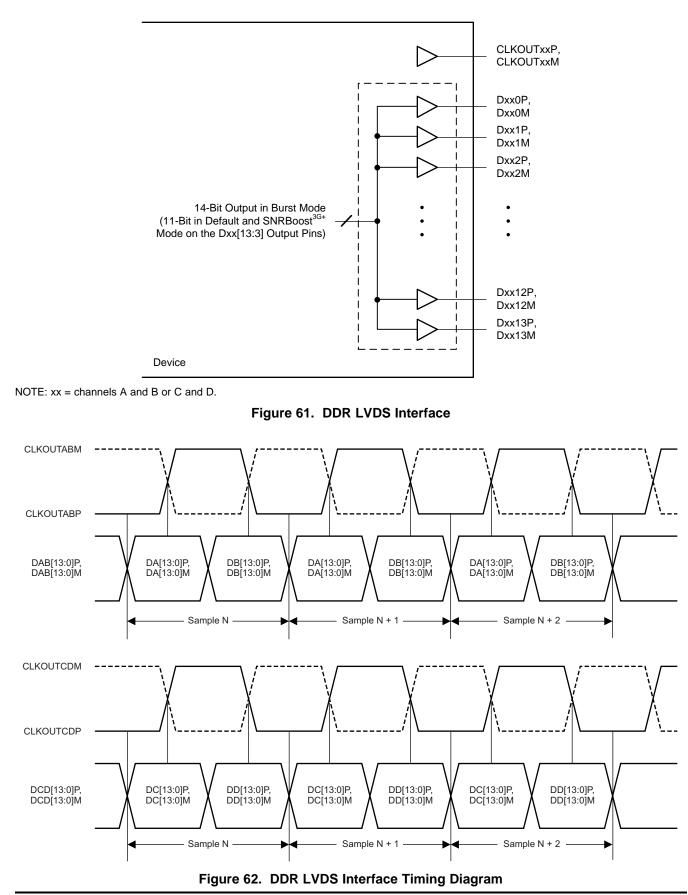

- DDR 低压差分信令 (LVDS) 数字输出接口

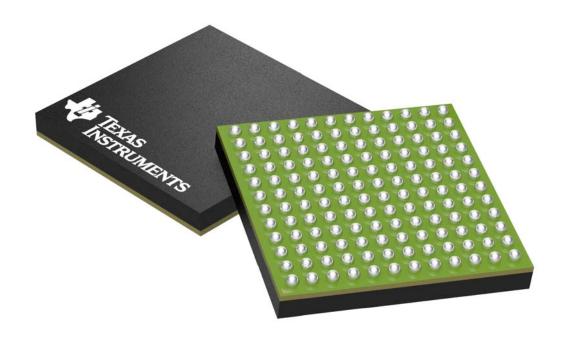

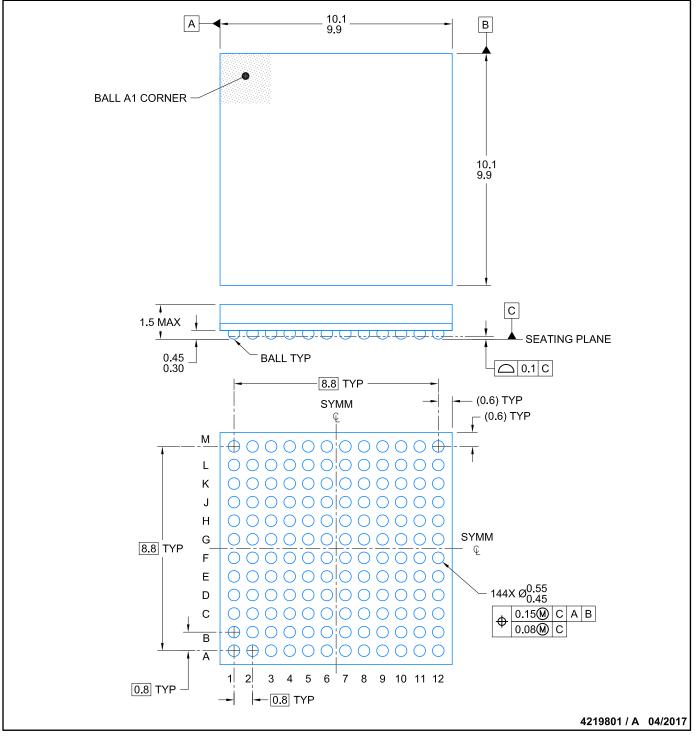

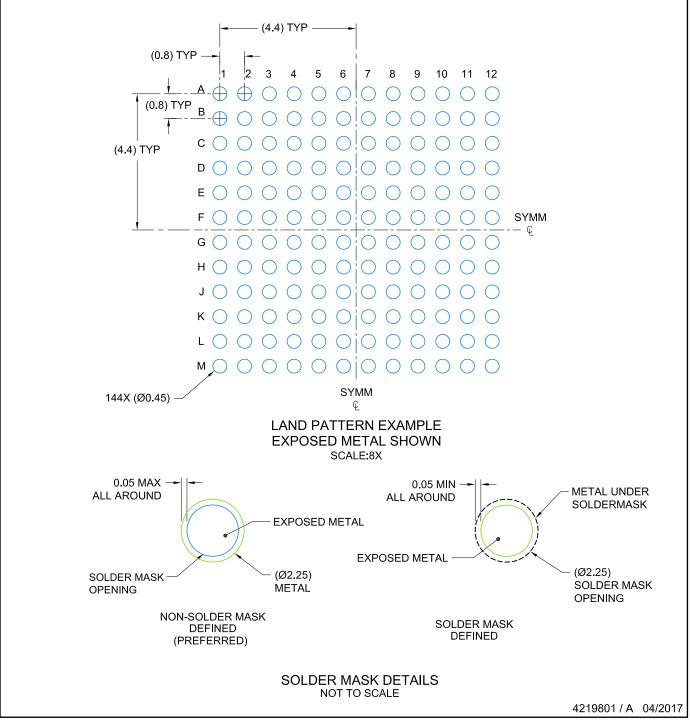

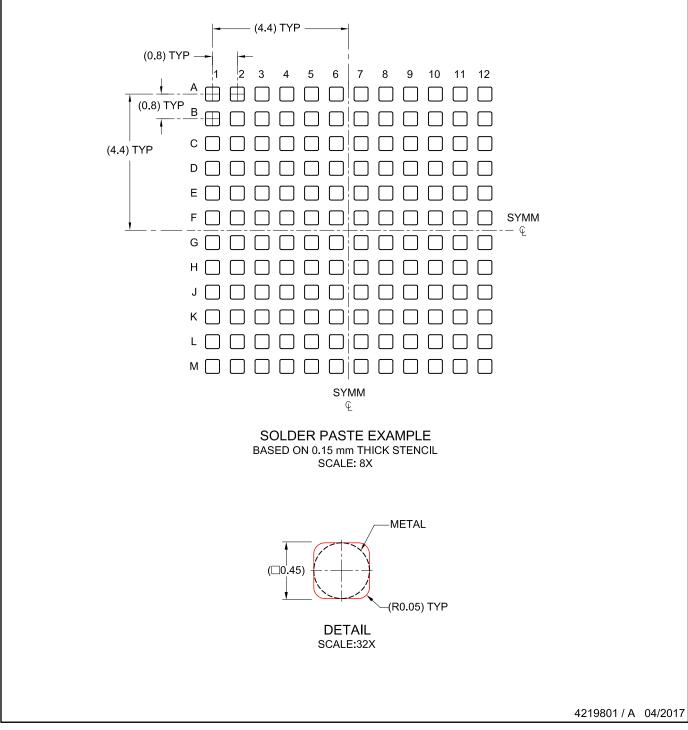

- 144 热层球状引脚栅格阵列封装 (BGA) (10mm x • 10mm)

# 应用范围

- 多载波 GSM 蜂窝基础设施基站

- 多载波多模式蜂窝基础设施基站

- 针对无线基础设施有源天线阵列

- 通信测试设备

### 说明

ADS58H40 是一款高线性, 四通道, 14 位,250MSPS 模数转换器 (ADC)。 四个 ADC 通道被 分成两块,每块有两个 ADC。 每个块可被独立配置成 为三个不同的运行模式。一个运行模式包括 SNRBoost<sup>3G+</sup> 信号处理技术的实现来在只使用 11 位 分辨率的情况下在高达

90MHz 带宽内提供高信噪比 (SNR)。 针对低功耗和高 无杂散动态范围 (SFDR) 而设计,此 ADC 具有低噪声 性能以及在宽输入频率范围内出色的 SFDR。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

#### ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

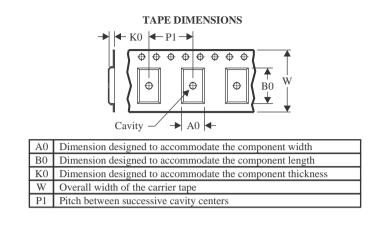

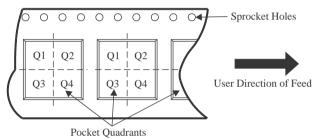

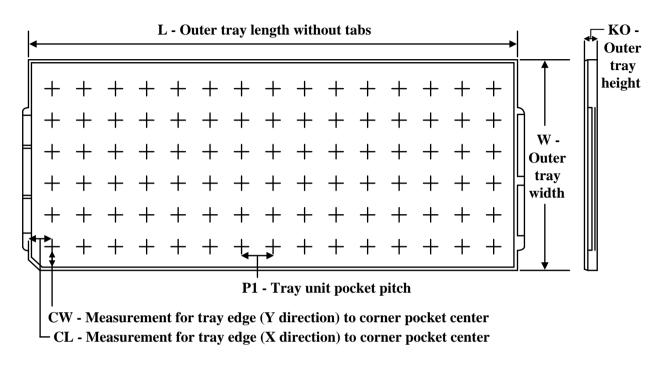

| PRODUCT  | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR                          | IEMPERATURE    |                                      | LEAD AND<br>BALL<br>FINISH | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA |  |  |  |

|----------|------------------|------------------------------------------------|----------------|--------------------------------------|----------------------------|--------------------|--------------------|--------------------|--|--|--|

|          | BGA-144          | A-144 ZCR -40°C to +85°C GREEN (RoHS, CuNiPdAu |                | 40%C to USERC GREEN (RoHS, CUNIDIAL) |                            | ADS58H40I          | ADS58H40IZCR       | Tray               |  |  |  |

| ADS58H40 | DGA-144          | ZCR                                            | -40°C 10 +65°C | no SB or BR)                         | CUNIPGAU                   | AD556H40I          | ADS58H40IZCRR      | Tape and Reel      |  |  |  |

# PACKAGE AND ORDERING INFORMATION<sup>(1)</sup>

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

(2) These packages conform to Lead (Pb)-free and green manufacturing specifications. Additional details including specific material content can be accessed at www.ti.com/leadfree.

GREEN: TI defines Green to mean Lead (Pb)-Free and in addition, uses less package materials that do not contain halogens, including bromine (Br), or antimony (Sb) above 0.1% of total product weight.

N/A: Not yet available Lead (Pb)-Free; for estimated conversion dates, go to www.ti.com/leadfree.

Pb-FREE: TI defines Lead (Pb)-Free to mean RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and, if designed to be soldered, suitable for use in specified lead-free soldering processes.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                                       |                                             | VALUE                             | UNIT |

|---------------------------------------|---------------------------------------------|-----------------------------------|------|

|                                       | AVDD33                                      | -0.3 to +3.6                      | V    |

| Supply voltage range                  | AVDD                                        | -0.3 to +2.1                      | V    |

|                                       | DRVDD                                       | -0.3 to +2.1                      | V    |

|                                       | AVSS and DRVSS                              | -0.3 to +0.3                      | V    |

| Valtage between                       | AVDD and DRVDD                              | -2.4 to +2.4                      | V    |

| Voltage between                       | AVDD33 and DRVDD                            | -2.4 to +3.9                      | V    |

|                                       | AVDD33 and AVDD                             | -2.4 to +3.9                      | V    |

|                                       | XINP, XINM                                  | -0.3 to minimum (1.9, AVDD + 0.3) | V    |

| Voltage applied to input pins         | CLKP, CLKM <sup>(2)</sup>                   | -0.3 to minimum (1.9, AVDD + 0.3) | V    |

|                                       | RESET, SCLK, SDATA, SEN, SNRB, TRIG_EN, PDN | -0.3 to +3.9                      | V    |

|                                       | Operating free-air, T <sub>A</sub>          | -40 to +85                        | °C   |

| Temperature                           | Operating junction, T <sub>J</sub>          | +150                              | °C   |

|                                       | Storage, T <sub>stg</sub>                   | -65 to +150                       | °C   |

| Electrostatic discharge (ESD) ratings | Human body model (HBM)                      | 2                                 | kV   |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) When AVDD is turned off, TI recommends switching off the input clock (or ensuring the voltage on CLKP and CLKM is less than | 0.3 V |). This recommendation prevents the ESD protection diodes at the clock input pins from turning on.

ZHCSA63B - AUGUST 2012 - REVISED NOVEMBER 2012

# THERMAL INFORMATION

|                    |                                              | ADS58H40  |       |

|--------------------|----------------------------------------------|-----------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                | ZCR (BGA) | UNITS |

|                    |                                              | 144 PINS  |       |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance       | 35.9      |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 5.1       |       |

| θ <sub>JB</sub>    | Junction-to-board thermal resistance         | 12.6      | °C04/ |

| ΨJT                | Junction-to-top characterization parameter   | 0.1       | °C/W  |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter | 12.4      |       |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | N/A       |       |

(1) 有关传统和新的热度量的更多信息,请参阅/C 封装热度量应用报告, SPRA953。

# **RECOMMENDED OPERATING CONDITIONS**

|                   |                                                      |                                                  | MIN                | NOM                  | MAX  | UNIT            |

|-------------------|------------------------------------------------------|--------------------------------------------------|--------------------|----------------------|------|-----------------|

| SUPPLIE           | S                                                    |                                                  |                    |                      |      |                 |

| AVDD33            |                                                      |                                                  | 3.15               | 3.3                  | 3.45 | V               |

| AVDD              | Supply voltage                                       |                                                  | 1.8                | 1.9                  | 2.0  | V               |

| DRVDD             |                                                      |                                                  | 1.7                | 1.8                  | 2.0  | V               |

| ANALOG            | INPUTS                                               |                                                  |                    |                      |      |                 |

|                   | Differential input voltage range                     |                                                  |                    | 2                    |      | V <sub>PP</sub> |

|                   | Input common-mode voltage                            |                                                  | V <sub>CI</sub>    | <sub>M</sub> ± 0.025 |      | V               |

|                   | Analog input common-mode current                     | t (per input pin of each channel)                |                    | 1.5                  |      | µA/MSPS         |

|                   | VCM current capability                               |                                                  |                    | 5                    |      | mA              |

|                   |                                                      | 2-V <sub>PP</sub> input amplitude <sup>(1)</sup> |                    | 400                  |      | MHz             |

|                   | Maximum analog input frequency                       | 1.4-V <sub>PP</sub> input amplitude              |                    | 500                  |      | MHz             |

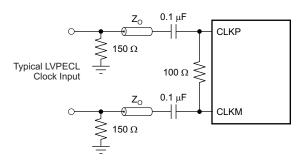

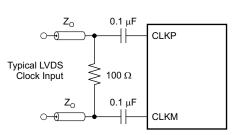

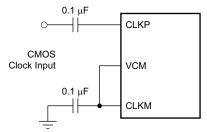

| CLOCK I           | NPUTS                                                |                                                  |                    |                      |      |                 |

|                   | Input clock sample rate                              |                                                  | 184 <sup>(2)</sup> |                      | 250  | MSPS            |

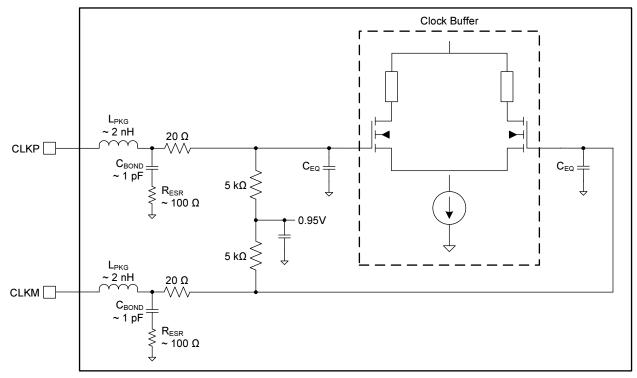

|                   |                                                      | Sine wave, ac-coupled                            | 0.2                | 1.5                  |      | V <sub>PP</sub> |

|                   | Input clock amplitude differential                   | LVPECL, ac-coupled                               |                    | 1.6                  |      | V <sub>PP</sub> |

|                   | $(V_{CLKP} - V_{CLKM})$                              | LVDS, ac-coupled                                 |                    | 0.7                  |      | V <sub>PP</sub> |

|                   |                                                      | LVCMOS, single-ended, ac-coupled                 |                    | 1.8                  |      | V <sub>PP</sub> |

|                   | Input clock duty cycle                               |                                                  | 40%                | 50%                  | 60%  |                 |

| DIGITAL           | OUTPUTS                                              |                                                  |                    |                      |      |                 |

| C <sub>LOAD</sub> | Maximum external load capacitance (default strength) | e from each output pin to DRVSS                  |                    | 3.3                  |      | pF              |

| R <sub>LOAD</sub> | Differential load resistance between                 | the LVDS output pairs (LVDS mode)                |                    | 100                  |      | Ω               |

| TEMPER            | ATURE RANGE                                          |                                                  |                    |                      |      |                 |

| T <sub>A</sub>    | Operating free-air temperature                       | -40                                              |                    | +85                  | °C   |                 |

| -                 |                                                      | Recommended                                      |                    |                      | +105 | °C              |

| TJ                | Operating junction temperature                       | Maximum rated <sup>(3)</sup>                     |                    |                      | +125 | °C              |

(1) See the *Theory of Operation* section.

(2) The minimum *functional clock speed* can be 10 MSPS after writing the following special modes: address 4Ah, value 01h; address 62h, value 01h; address 92h, value 01h; and address 7Ah, value 01h. See the SPECIAL MODE[17:14] bits in Table 4 of the Serial Interface Registers section.

(3) Prolonged use at this junction temperature may increase the device failure-in-time (FIT) rate.

www.ti.com.cn

```

Table 1. High-Performance Modes Summary<sup>(1)(2)</sup>

```

|                  |            |                                 | f <sub>S</sub> = 245.            | f <sub>S</sub> = 184.           | 32 MSPS                          |                                 |                                  |

|------------------|------------|---------------------------------|----------------------------------|---------------------------------|----------------------------------|---------------------------------|----------------------------------|

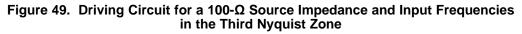

| ADDRESS<br>(Hex) | DATA (Hex) | R <sub>S</sub> = 50<br>ZONE = 2 | R <sub>S</sub> = 100<br>ZONE = 2 | R <sub>S</sub> = 50<br>ZONE = 3 | R <sub>S</sub> = 100<br>ZONE = 3 | R <sub>S</sub> = 50<br>ZONE = 2 | R <sub>S</sub> = 100<br>ZONE = 2 |

| D4               | 80         |                                 |                                  |                                 | $\checkmark$                     |                                 |                                  |

| D5               | 80         |                                 |                                  |                                 | $\checkmark$                     |                                 |                                  |

| D6               | 80         | $\checkmark$                    | $\checkmark$                     | $\checkmark$                    | $\checkmark$                     | $\checkmark$                    |                                  |

| D7               | 0C         | $\checkmark$                    | $\checkmark$                     | $\checkmark$                    |                                  | $\checkmark$                    | $\checkmark$                     |

| DB               | 30         |                                 |                                  |                                 | $\checkmark$                     |                                 |                                  |

| F0               | 38         |                                 |                                  |                                 |                                  | √                               | $\checkmark$                     |

| F1               | 20         | $\checkmark$                    |                                  | √                               |                                  | √                               |                                  |

| F5               | 42         |                                 |                                  |                                 | $\checkmark$                     |                                 |                                  |

(1) R<sub>S</sub> refers to the source impedance. Zone refers to the Nyquist zone in which the signal band lies. Zone = 2 corresponds to the signal

band that lies between  $f_S / 2$  and  $f_S$ . Zone = 3 corresponds to the signal band that lies between  $f_S$  and  $3 \times f_S / 2$ . (2) Best performance can be achieved by writing these modes depending upon source impedance, band of operation, and sampling speed.

# **ELECTRICAL CHARACTERISTICS**

Typical values are at  $T_A = +25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = +85^{\circ}$ C, ADC clock frequency = 250 MHz, 50% clock duty cycle, AVDD33V = 3.3 V, AVDD = 1.9 V, DRVDD = 1.8 V, and -1-dBFS differential input, unless otherwise noted.

|                          | PARAME                     | TER                                                | TEST CONDITIONS                                          | MIN | TYP   | MAX | UNITS           |

|--------------------------|----------------------------|----------------------------------------------------|----------------------------------------------------------|-----|-------|-----|-----------------|

| RESOLUT                  | TION                       |                                                    | •                                                        |     |       |     |                 |

|                          | Default resolution         |                                                    |                                                          |     | 11    |     | Bits            |

| ANALOG                   | INPUTS                     |                                                    |                                                          |     |       |     |                 |

|                          | Differential input full-sc | ale                                                |                                                          |     | 2     |     | V <sub>PP</sub> |

| VCM                      | Common mode input v        | oltage                                             |                                                          |     | 1.15  |     | V               |

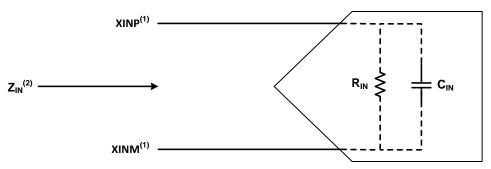

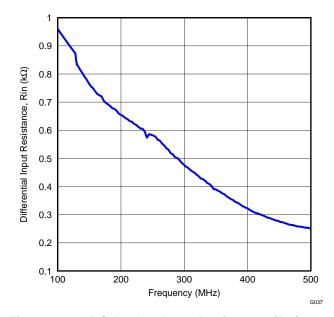

| R <sub>IN</sub>          | Input resistance, differe  | ential                                             | At 170-MHz input frequency                               |     | 700   |     | Ω               |

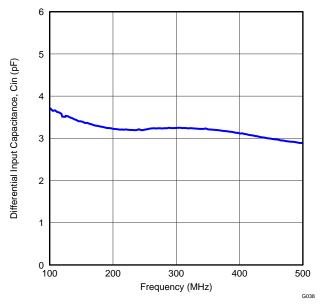

| C <sub>IN</sub>          | Input capacitance, diffe   | erential                                           | At 170-MHz input frequency                               |     | 3.3   |     | pF              |

|                          | Analog input bandwidth     | n, 3 dB                                            | With a 50- $\Omega$ source driving the ADC analog inputs | 500 |       |     | MHz             |

| DYNAMIC                  | CACCURACY                  |                                                    |                                                          |     |       |     |                 |

| Eo                       | Offset error               |                                                    | Specified across devices and channels                    | -15 |       | 15  | mV              |

| E <sub>G</sub>           | Gain error <sup>(1)</sup>  | As a result of internal reference inaccuracy alone | Specified across devices and channels                    | -5  |       | 5   | %FS             |

|                          |                            | Of channel alone                                   | Specified across channels within a device                |     | ±0.2  |     | %FS             |

|                          | Channel gain error tem     | perature coefficient <sup>(1)</sup>                |                                                          |     | 0.001 |     | ∆%/°C           |

| POWER S                  | SUPPLY <sup>(2)</sup>      |                                                    | •                                                        |     |       |     |                 |

| I <sub>AVDD33</sub>      |                            | 3.3-V analog supply                                |                                                          |     | 51    |     | mA              |

| I <sub>AVDD</sub>        |                            | 1.9-V analog supply                                |                                                          |     | 350   |     | mA              |

|                          | Supply current             |                                                    | 11-bit operation                                         |     | 340   |     | mA              |

| I <sub>DRVDD</sub>       |                            | 1.8-V digital supply                               | SNRBoost <sup>3G+</sup> enabled (90 MHz)                 |     | 400   |     | mA              |

|                          |                            |                                                    | 14-bit burst mode                                        |     | 355   |     | mA              |

|                          |                            |                                                    | 11-bit operation                                         |     | 1.45  | 1.6 | W               |

| P <sub>TOTAL</sub>       |                            | Total                                              | SNRBoost <sup>3G+</sup> enabled                          |     | 1.55  | 1.8 | W               |

|                          | Power dissipation          |                                                    | 14-bit burst mode                                        |     | 1.47  |     | W               |

| P <sub>DISS(stand</sub>  | by)                        | Standby                                            |                                                          |     | 400   |     | mW              |

| P <sub>DISS(global</sub> |                            | Global power-down                                  |                                                          |     | 6     | 52  | mW              |

There are two sources of gain error: internal reference inaccuracy and channel gain error. (1)

A 185-MHz, full-scale, sine-wave input signal is applied to all four channels. (2)

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS (continued)**

Typical values are at  $T_A = +25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = +85^{\circ}$ C, ADC clock frequency = 250 MHz, 50% clock duty cycle, AVDD33V = 3.3 V, AVDD = 1.9 V, DRVDD = 1.8 V, and -1-dBFS differential input, unless otherwise noted.

|       | PARAMET                                 | ER                                            | TEST CONDITIONS                                                                              | MIN   | TYP  | MAX   | UNITS          |

|-------|-----------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|----------------|

|       | AC CHARACTERISTICS <sup>(3)</sup>       | (4)                                           |                                                                                              |       |      |       |                |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         |       | 71   |       | dBFS           |

|       |                                         | 11-bit SNRBoost <sup>3G+</sup> ,<br>90-MHz BW | $f_{IN} = 170 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 | 69    | 70.5 |       | dBFS           |

| SNR   | Signal-to-noise ratio                   |                                               | $f_{IN} = 220 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         |       | 70   |       | dBFS           |

|       |                                         | 11-bit SNRBoost <sup>3G+</sup> ,              | $f_{IN} = 307 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$                                         |       | 71.7 |       | dBFS           |

|       |                                         | 60-MHz BW                                     | $f_{IN} = 350 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 71.5 |       | dBFS           |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         |       | 70.6 |       | dBFS           |

|       |                                         | 11-bit SNRBoost <sup>3G+</sup> ,<br>90-MHz BW | $f_{IN} = 170 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 | 68    | 70.1 |       | dBFS           |

| SINAD | Signal-to-noise and<br>distortion ratio |                                               | $f_{IN} = 220 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 69.5 |       | dBFS           |

|       |                                         | 11-bit SNRBoost <sup>3G+</sup> ,              | $f_{IN} = 307 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 69.7 |       | dBFS           |

|       |                                         | 60-MHz BW                                     | $f_{IN} = 350 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 69.2 |       | dBFS           |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 85   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 170 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 | 80    | 85   |       | dBc            |

| SFDR  | Spurious-free dynamic ra                | ange                                          | $f_{IN} = 220 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 82   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 307 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 78   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 350 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 77   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         |       | 82   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 170 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 | 77    | 82   |       | dBc            |

| THD   | Total harmonic distortion               | ı                                             | $f_{IN} = 220 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 80   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 307 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 77   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 350 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 76   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         |       | 86   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         | 80    | 85   |       | dBc            |

| HD2   | Second-order harmonic                   | distortion <sup>(5)</sup>                     | $f_{IN} = 220 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 82   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 307 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 78   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 350 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 77   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 85   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 170 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 | 82    | 85   |       | dBc            |

| HD3   | Third-order harmonic dis                | stortion                                      | $f_{IN} = 220 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 85   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 307 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 85   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 350 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 83   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                         |       | 95   |       | dBc            |

|       |                                         |                                               | $f_{IN} = 170 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 | 87    | 95   |       | dBc            |

|       | Worst spur<br>(non HD2, HD3)            |                                               | $f_{IN} = 220 \text{ MHz}, \text{ A}_{IN} = -1 \text{ dBFS}$                                 |       | 95   |       | dBc            |

|       | (1011102, 1100)                         |                                               | $f_{IN} = 307 \text{ MHz}, \text{ A}_{IN} = -3 \text{ dBFS}$                                 |       | 95   |       | dBc            |

|       |                                         |                                               | $f_{IN}$ = 350 MHz, $A_{IN}$ = -3 dBFS                                                       |       | 95   |       | dBc            |

| DNL   | Differential nonlinearity               |                                               |                                                                                              | -0.95 | ±0.5 | 1.6   | LSBs           |

| INL   | Integral nonlinearity                   |                                               |                                                                                              |       | ±1.5 | ±5.25 | LSBs           |

|       | Input overload recovery                 |                                               | Recovery to within 1% (of final value) for<br>6-dB output overload with sine-wave input      |       | 1    |       | Clock<br>cycle |

|       | Crosstalk                               |                                               | With a full-scale, 220-MHz signal on<br>aggressor channel and no signal on victim<br>channel |       | 90   |       | dB             |

| PSRR  | AC power-supply rejection               | on ratio                                      | For 50-mV <sub>PP</sub> signal on AVDD supply                                                |       | < 30 |       | dB             |

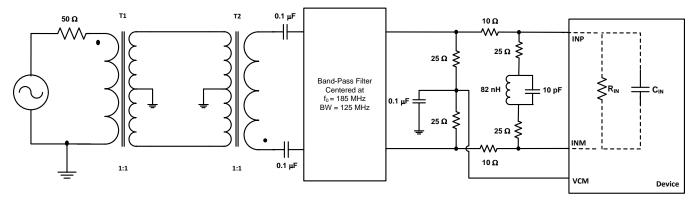

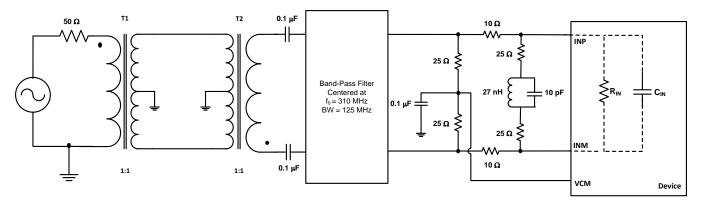

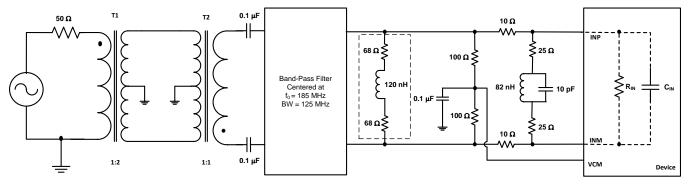

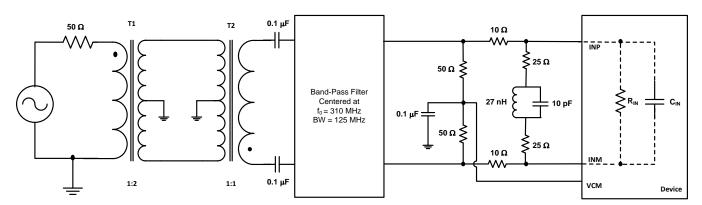

(3) Phase and amplitude imbalances onboard must be minimized to obtain good performance.

(4) Dynamic ac characteristics are taken with respect to the 14-bit burst mode, unless otherwise noted.

(5) The minimum value across temperature is ensured by bench characterization.

www.ti.com.cn

# **DIGITAL CHARACTERISTICS**

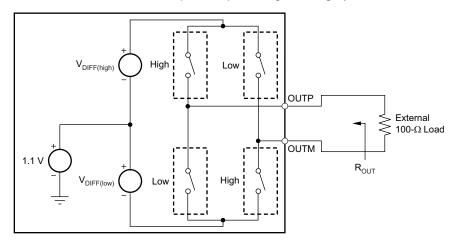

The dc specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level '0' or '1'. AVDD33 = 3.3 V, AVDD = 1.9 V, and DRVDD = 1.8 V, unless otherwise noted.

|                  | PARA                                      | METER                                   | TEST CONDITIONS                                                                 | MIN            | TYP   | MAX      | UNIT |

|------------------|-------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|----------------|-------|----------|------|

| DIGITA           | L INPUTS <sup>(1)</sup> (RESET            | , SCLK, SDATA, SEN, PDN                 | , SNRB, TRIG_EN)                                                                |                |       |          |      |

| VIH              | High-level input vo                       | bltage                                  | All digital inputs support 1.8-V logic levels. SPI supports 3.3-V logic levels. | 1.25           |       |          | V    |

| VIL              | Low-level input vo                        | Itage                                   | All digital inputs support 1.8-V logic levels. SPI supports 3.3-V logic levels. |                |       | 0.45     | V    |

| IIH              | High-level input                          | RESET, SCLK, PDN,<br>SNRB, TRIG_EN pins | V <sub>HIGH</sub> = 1.8 V                                                       |                | 10    |          | μΑ   |

|                  | current                                   | SEN <sup>(2)</sup> pin                  | V <sub>HIGH</sub> = 1.8 V                                                       |                | 0     |          | μA   |

| IIL              | Low-level input                           | RESET, SCLK, PDN,<br>SNRB, TRIG_EN pins | V <sub>LOW</sub> = 0 V                                                          |                | 0     |          | μΑ   |

|                  | current                                   | SEN pin                                 | V <sub>LOW</sub> = 0 V                                                          |                | 10    |          | μΑ   |

| DIGITA           | L OUTPUTS (SDOUT                          | , HIRES, TRIG_RDY)                      |                                                                                 |                |       |          |      |

| V <sub>OH</sub>  | High-level output                         | voltage                                 |                                                                                 | DRVDD -<br>0.1 | DRVDD |          | V    |

| V <sub>OL</sub>  | Low-level output v                        | oltage                                  |                                                                                 |                | 0     | 0.1      | V    |

|                  | L OUTPUTS, LVDS  <br>3:0]P, DAB[13:0]M, [ |                                         | LKOUTABP, CLKOUTABM, CLKOUTCDP,                                                 | CLKOUTCDM)     |       | <b>i</b> |      |

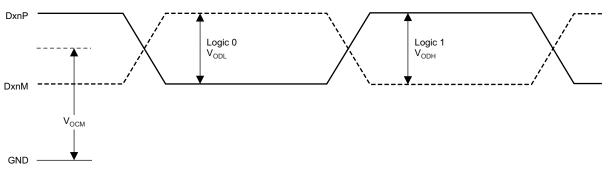

| V <sub>ODH</sub> | Output differential                       | High <sup>(3)</sup>                     | Standard-swing LVDS                                                             | 270            | 350   | 465      | mV   |

| V <sub>ODL</sub> | voltage Low                               |                                         | Standard-swing LVDS                                                             | -465           | -350  | -270     | mV   |

| V <sub>OCM</sub> | Output common-m                           | node voltage                            |                                                                                 |                | 1.05  |          | V    |

(1) RESET, SDATA, SCLK, TRIG\_EN, and SNRB have an internal 150-kΩ pull-down resistor.

SEN has an internal  $150-k\Omega$  pull-up resistor to DRVDD. With an external  $100-\Omega$  termination. (2)

(3)

# TIMING REQUIREMENTS<sup>(1)</sup>

Typical values are at +25°C, AVDD33 = 3.3 V, AVDD = 1.9 V, DRVDD = 1.8 V, sine-wave input clock, C<sub>LOAD</sub> = 3.3 pF<sup>(2)</sup>, and  $R_{LOAD} = 100 \ \Omega^{(3)}$ , unless otherwise noted.

Minimum and maximum values are across the full temperature range of  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = +85^{\circ}$ C.

|                                                | PARAMETER                              | TEST CONDITIONS                                                                                                             | MIN                             | TYP  | MAX  | UNIT                |

|------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|---------------------|

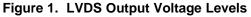

| t <sub>A</sub>                                 | Aperture delay                         |                                                                                                                             | 0.7                             | 1.2  | 1.6  | ns                  |

|                                                | Aperture delay matching                | Between any two channels of the same device                                                                                 |                                 | ±70  |      | ps                  |

|                                                | Variation of aperture delay            | Between two devices at the same temperature and DRVDD supply                                                                |                                 | ±150 |      | ps                  |

| tj                                             | Aperture jitter                        |                                                                                                                             |                                 | 140  |      | fs rms              |

|                                                | M/-1                                   | Time to valid data after coming out of global power down                                                                    |                                 | 100  |      | μs                  |

|                                                | Wake up time                           | Time to valid data after coming out of channel power down                                                                   | 10                              |      |      | μs                  |

|                                                |                                        | Default latency in 11-bit mode                                                                                              | 10                              |      |      | Output clock cycles |

|                                                |                                        | Digital gain enabled                                                                                                        |                                 | 13   |      | Output clock cycles |

|                                                | ADC latency <sup>(4)(5)</sup>          | Digital gain and offset correction enabled                                                                                  | 14                              |      |      | Output clock cycles |

|                                                |                                        | SNRBoost <sup>3G+</sup> (90-MHz BW) enabled alone                                                                           |                                 | 13   |      | Output clock cycles |

|                                                |                                        | SNRBoost <sup>3G+</sup> (90-MHz BW), digital gain, and offset correction enabled                                            |                                 | 17   |      | Output clock cycles |

|                                                |                                        | SNRBoost <sup>3G+</sup> (45-MHz BW) enabled alone                                                                           | 15                              |      |      | Output clock cycles |

|                                                |                                        | SNRBoost <sup>3G+</sup> (45-MHz BW), digital gain, and offset correction enabled                                            | 19                              |      |      | Output clock cycles |

| OUTPUT                                         | TIMING <sup>(6)</sup>                  | · · · · · · · · · · · · · · · · · · ·                                                                                       |                                 |      | L    |                     |

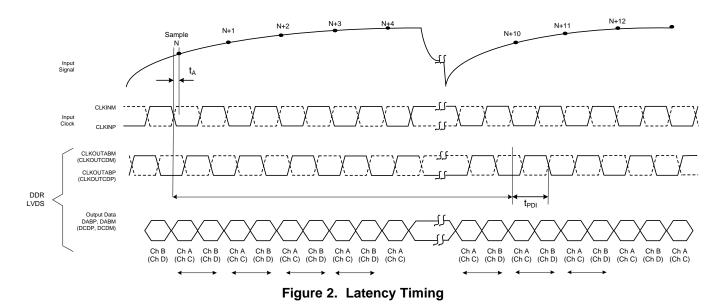

| t <sub>SU</sub>                                | Data setup time <sup>(7)(8)(9)</sup>   | Data valid to CLKOUTxxP zero-crossing                                                                                       | 0.6                             | 0.85 |      | ns                  |

| t <sub>H</sub>                                 | Data hold time <sup>(7)(8)(9)</sup>    | CLKOUTxxP zero-crossing to data becoming invalid                                                                            | 0.6                             | 0.84 |      | ns                  |

|                                                | LVDS bit clock duty cycle              | Differential clock duty cycle (CLKOUTxxP –<br>CLKOUTxxM)                                                                    |                                 | 50%  |      |                     |

| t <sub>PDI</sub>                               | Clock propagation delay <sup>(5)</sup> | Input clock falling edge cross-over to output clock<br>falling edge cross-over, 184 MSPS ≤ sampling<br>frequency ≤ 250 MSPS | $0.25 \times t_{S} + t_{delay}$ |      | ns   |                     |

| t <sub>delay</sub>                             | Delay time                             | Input clock falling edge cross-over to output clock<br>falling edge cross-over, 184 MSPS ≤ sampling<br>frequency ≤ 250 MSPS | 6.9                             | 8.65 | 10.5 | ns                  |

| t <sub>RISE</sub> ,<br>t <sub>FALL</sub>       | Data rise and fall time                | Rise time measured from -100 mV to +100 mV                                                                                  |                                 | 0.1  |      | ns                  |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise and fall time        | Rise time measured from -100 mV to +100 mV                                                                                  |                                 | 0.1  |      | ns                  |

Timing parameters are ensured by design and characterization and are not tested in production. (1)

(2) CLOAD is the effective external single-ended load capacitance between each output pin and ground.

(3)

R<sub>LOAD</sub> is the differential load resistance between the LVDS output pair. ADC latency is given for channels B and D. For channels A and C, latency reduces by half of the output clock cycles. (4)

(5) Overall latency = ADC latency + t<sub>PDI</sub>.

Measurements are done with a transmission line of 100-Ω characteristic impedance between the device and load. Setup and hold time (6) specifications take into account the effect of jitter on the output data and clock.

(7)Data valid refers to a logic high of +100 mV and a logic low of -100 mV.

Note that these numbers are taken with delayed output clocks by writing the following registers: address A9h, value 02h; and address (8) ACh, value 60h. Refer to the Serial Interface Registers section. By default after reset, minimum setup time and minimum hold times are 520 ps each.

The setup and hold times of a channel are measured with respect to the same channel output clock. (9)

| Table 2. LVDS Timings Across Lower Samp | ling Frequencies |

|-----------------------------------------|------------------|

|-----------------------------------------|------------------|

| SAMPLING FREQUENCY | SETU | P TIME (ns) |     | HOLD TIME (ns) |      |     |  |

|--------------------|------|-------------|-----|----------------|------|-----|--|

| (MSPS)             | MIN  | TYP         | MAX | MIN            | ТҮР  | MAX |  |

| 210                | 0.89 | 1.03        |     | 0.82           | 1.01 |     |  |

| 185                | 1.06 | 1.21        |     | 0.95           | 1.15 |     |  |

# PARAMETRIC MEASUREMENT INFORMATION

# LVDS OUTPUT TIMING

Figure 1 shows a timing diagram of the LVDS output voltage levels. Figure 2 shows the latency described in the Timing Requirements table.

#### ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

### **PARAMETRIC MEASUREMENT INFORMATION (continued)**

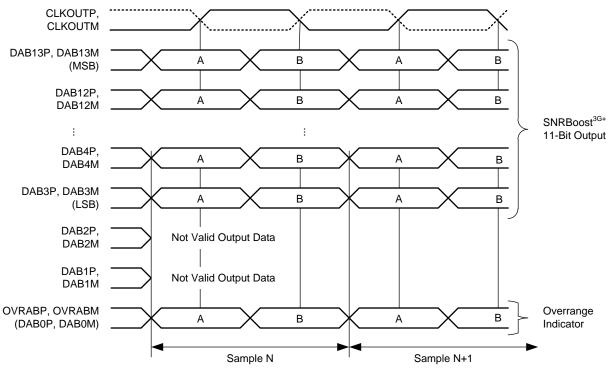

All 14 data bits of one channel (11 data bits in default SNRBoost<sup>3G+</sup> mode) are included in the digital output interface at the same time, as shown in Figure 3. Channel A and C data are output on the rising edge of the output clock while channels B and D are output on the falling edge of the output clock.

Figure 3. LVDS Output Interface Timing

TEXAS INSTRUMENTS

ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

www.ti.com.cn

# **PIN CONFIGURATION**

|   | ZCR PACKAGE<br>BGA-144<br>(TOP VIEW) |        |               |               |                  |                  |                  |                  |               |               |        |        |

|---|--------------------------------------|--------|---------------|---------------|------------------|------------------|------------------|------------------|---------------|---------------|--------|--------|

|   | 1                                    | 2      | 3             | 4             | 5                | 6                | 7                | 8                | 9             | 10            | 11     | 12     |

| Α | AVDD                                 | AVDD   | CINM          | CINP          | AVDD             | VCM              | VCM              | AVDD             | BINM          | BINP          | AVDD   | AVDD   |

| в | DINP                                 | AVSS   | AVDD          | AVDD          | AVSS             | AVDD33           | AVDD33           | AVSS             | AVDD          | AVDD          | AVSS   | AINM   |

| с | DINM                                 | AVSS   | AVSS          | AVSS          | AVSS             | CLKINM           | CLKINP           | AVSS             | AVSS          | AVSS          | AVSS   | AINP   |

| D | AVDD                                 | AVDD   | VCM           | AVSS          | AVSS             | AVSS             | AVSS             | AVSS             | AVSS          | VCM           | AVDD   | AVDD   |

| Е | AVDD33                               | AVDD33 | SNRB          | DRVSS         | DRVSS            | DRVSS            | DRVSS            | DRVSS            | DRVSS         | PDN           | AVDD33 | AVDD33 |

| F | DCD13M                               | DCD13P | DRVDD         | DRVSS         | DRVSS            | DRVSS            | DRVSS            | DRVSS            | DRVSS         | DRVDD         | DAB13P | DAB13M |

| G | DCD12M                               | DCD12P | TRIG_EN       | TRIG_RDY      | HIRES            | RESET            | SCLK             | SDATA            | SEN           | SDOUT         | DAB12P | DAB12M |

| н | DCD11M                               | DCD11P | DCD6P         | DCD6M         | DRVDD            | DRVDD            | DRVDD            | DRVDD            | DAB6M         | DAB6P         | DAB11P | DAB11M |

| J | DCD10M                               | DCD10P | DCD5P         | DCD5M         | DCD2P            | DRVDD            | DRVDD            | DAB2M            | DAB5M         | DAB5P         | DAB10P | DAB10M |

| к | DCD9M                                | DCD9P  | DCD4P         | DCD4M         | DCD2M            | DRVDD            | DRVDD            | DAB2P            | DAB4M         | DAB4P         | DAB9P  | DAB9M  |

| L | DCD8M                                | DCD8P  | DCD3P         | DCD3M         | DCD1P            | DCD1M            | DAB1M            | DAB1P            | DAB3M         | DAB3P         | DAB8P  | DAB8M  |

| М | DCD7M                                | DCD7P  | CLKOUT<br>CDP | CLKOUT<br>CDM | DCD0P/<br>OVRCDP | DCD0M/<br>OVRCDM | DAB0M/<br>OVRABM | DAB0P/<br>OVRABP | CLKOUT<br>ABM | CLKOUT<br>ABP | DAB7P  | DAB7M  |

ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

#### www.ti.com.cn

### PIN FUNCTIONS

| PIN                                                         |                                                                            |     |                                                                                                                                                                                                                                        |

|-------------------------------------------------------------|----------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                        | NUMBER                                                                     | I/O | DESCRIPTION                                                                                                                                                                                                                            |

| AINM                                                        | B12                                                                        | Ι   | Negative differential analog input for channel A                                                                                                                                                                                       |

| AINP                                                        | C12                                                                        | Ι   | Positive differential analog input for channel A                                                                                                                                                                                       |

| AVDD33                                                      | B6, B7, E1, E2, E11, E12                                                   | Ι   | Analog 3.3-V power supply                                                                                                                                                                                                              |

| AVDD                                                        | A1, A2, A5, A8, A11, A12,<br>B3, B4, B9, B10, D1, D2,<br>D11, D12          | Ι   | Analog 1.9-V power supply                                                                                                                                                                                                              |

| AVSS                                                        | B2, B5, B8, B11, C2-C5,<br>C8-C11, D4-D9                                   | Ι   | Analog ground                                                                                                                                                                                                                          |

| BINM                                                        | A9                                                                         | Ι   | Negative differential analog input for channel B                                                                                                                                                                                       |

| BINP                                                        | A10                                                                        | Ι   | Positive differential analog input for channel B                                                                                                                                                                                       |

| CINM                                                        | A3                                                                         | Ι   | Negative differential analog input for channel C                                                                                                                                                                                       |

| CINP                                                        | A4                                                                         | Ι   | Positive differential analog input for channel C                                                                                                                                                                                       |

| CLKINM                                                      | C6                                                                         | Ι   | Negative differential clock input                                                                                                                                                                                                      |

| CLKINP                                                      | C7                                                                         | Ι   | Positive differential clock input                                                                                                                                                                                                      |

| CLKOUTABM                                                   | M9                                                                         | 0   | Negative differential LVDS clock output for channel A and B                                                                                                                                                                            |

| CLKOUTABP                                                   | M10                                                                        | 0   | Positive differential LVDS clock output for channel A and B                                                                                                                                                                            |

| CLKOUTCDM                                                   | M4                                                                         | 0   | Negative differential LVDS clock output for channels C and D                                                                                                                                                                           |

| CLKOUTCDP                                                   | M3                                                                         | 0   | Positive differential LVDS clock output for channels C and D                                                                                                                                                                           |

| DAB[13:1]P,<br>DAB0P/OVRABP,<br>DAB[13:1]M,<br>DAB0M/OVRABM | F11, F12, G11, G12,<br>H9-H12, J8-J12, K8-K12,<br>L7-L12, M7, M8, M11, M12 | 0   | DDR LVDS outputs for channels A and B.<br>In 11-bit mode, DAB13 is the MSB, DAB3 is the LSB, and DAB0 is the over-range (OVR) bit.<br>In 14-bit burst mode, DAB13 is the MSB and DAB0 is the LSB. There is no OVR bit in this<br>mode. |

| DCD[13:1]P,<br>DCD0P/OVRCDP,<br>DCD[13:1]M,<br>DCD0M/OVRCDM | F1, F2, G1, G2, H1-H4,<br>J1-J5, K1-K5, L1-L6, M1,<br>M2, M5, M6           | 0   | DDR LVDS outputs for channels C and D.<br>In 11-bit mode, DCD13 is the MSB, DCD3 is the LSB, and DCD0 is the OVR bit.<br>In 14-bit burst mode, DCD13 is the MSB and DCD0 is the LSB. There is no OVR bit in this<br>mode.              |

| DINM                                                        | C1                                                                         | Ι   | Negative differential analog input for channel D                                                                                                                                                                                       |

| DINP                                                        | B1                                                                         | Ι   | Positive differential analog input for channel D                                                                                                                                                                                       |

| DRVDD                                                       | F3, F10, H5-H8, J6, J7, K6,<br>K7                                          | Ι   | Digital 1.8-V power supply                                                                                                                                                                                                             |

| DRVSS                                                       | E4-E9, F4-F9                                                               | Ι   | Digital ground                                                                                                                                                                                                                         |

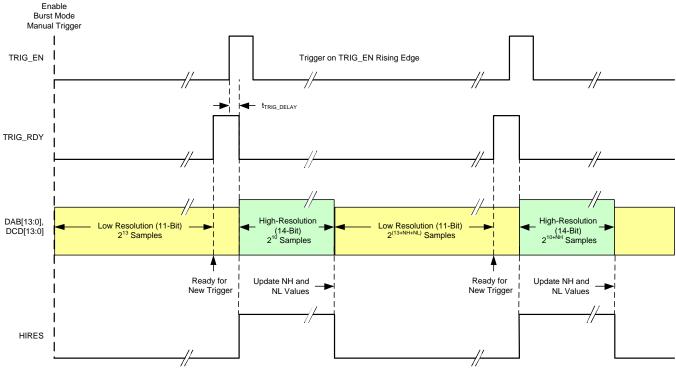

| HIRES                                                       | G5                                                                         | 0   | Indication in burst mode if output data is high or low resolution                                                                                                                                                                      |

| PDN                                                         | E10                                                                        | Ι   | Power-down control; active high. Logic high is power down.                                                                                                                                                                             |

| RESET                                                       | G6                                                                         | Ι   | Hardware reset; active high                                                                                                                                                                                                            |

| SCLK                                                        | G7                                                                         | Ι   | Serial interface clock input                                                                                                                                                                                                           |

| SDATA                                                       | G8                                                                         | Ι   | Serial interface data input                                                                                                                                                                                                            |

| SDOUT                                                       | G10                                                                        | 0   | Serial interface data output                                                                                                                                                                                                           |

| SEN                                                         | G9                                                                         | Ι   | Serial interface enable                                                                                                                                                                                                                |

| SNRB                                                        | E3                                                                         | Ι   | SNRB enable; active high                                                                                                                                                                                                               |

| TRIG_EN                                                     | G3                                                                         | Ι   | Trigger burst mode; active high                                                                                                                                                                                                        |

| TRIG_RDY                                                    | G4                                                                         | 0   | Indication if ADC is ready for another high-resolution burst mode                                                                                                                                                                      |

| VCM                                                         | A6, A7, D3, D10                                                            | 0   | Common-mode voltage for analog inputs. All VCM pins are internally connected together.                                                                                                                                                 |

www.ti.com.cn

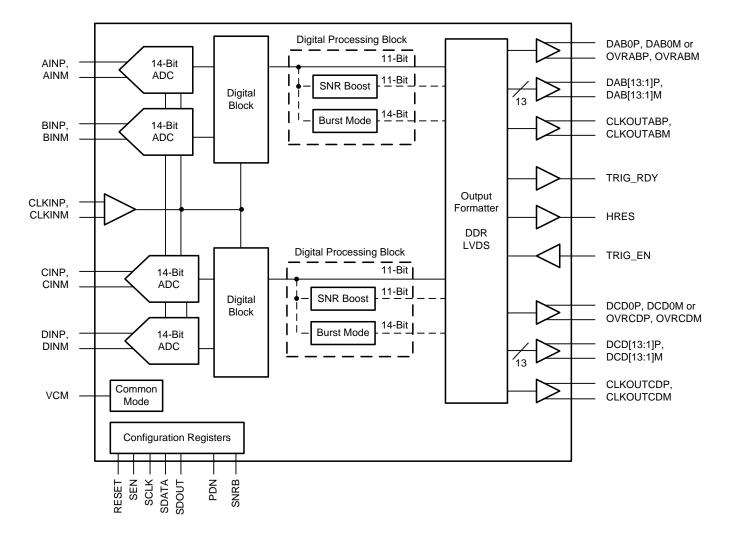

# FUNCTIONAL BLOCK DIAGRAM

TEXAS INSTRUMENTS

www.ti.com.cn

#### ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

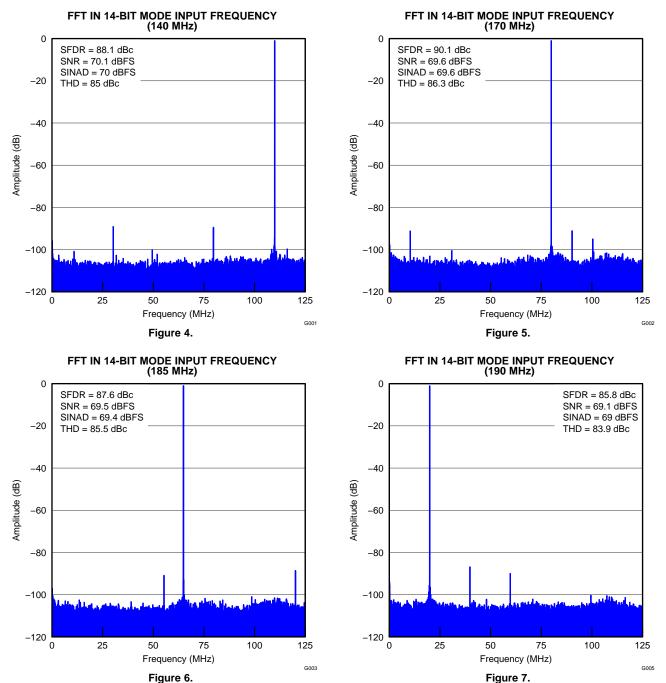

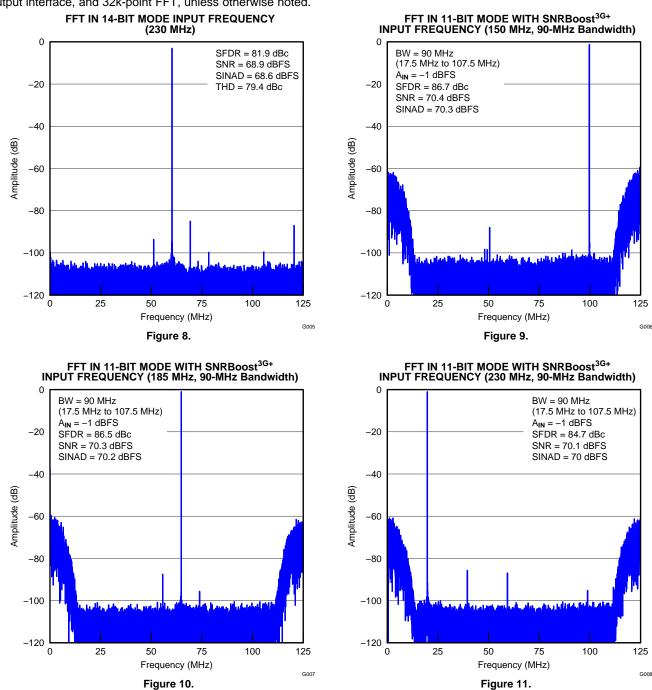

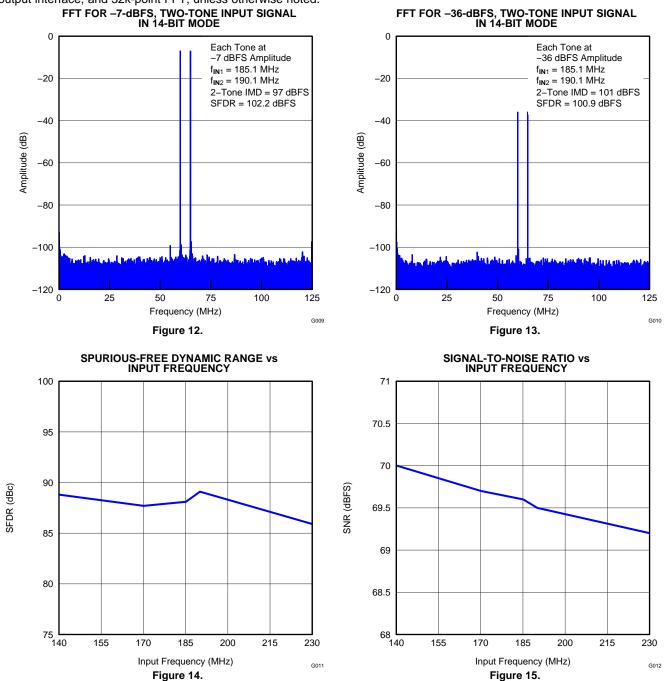

### **TYPICAL CHARACTERISTICS**

www.ti.com.cn

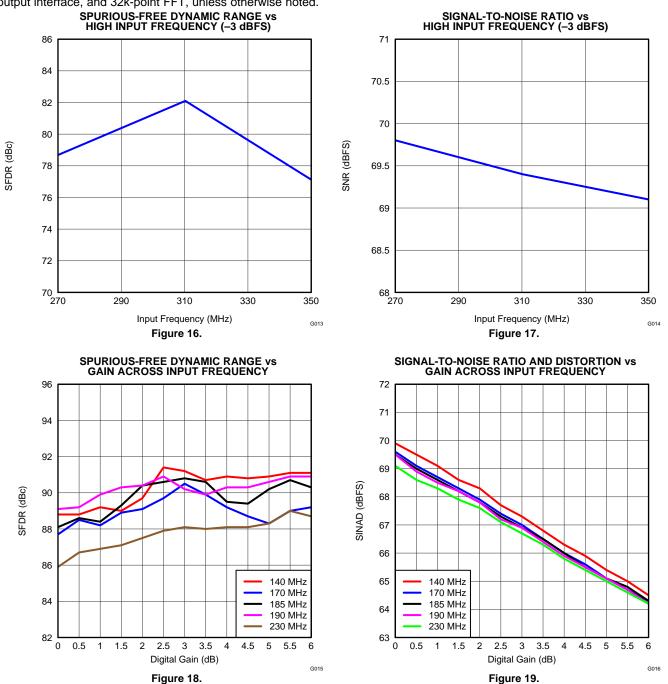

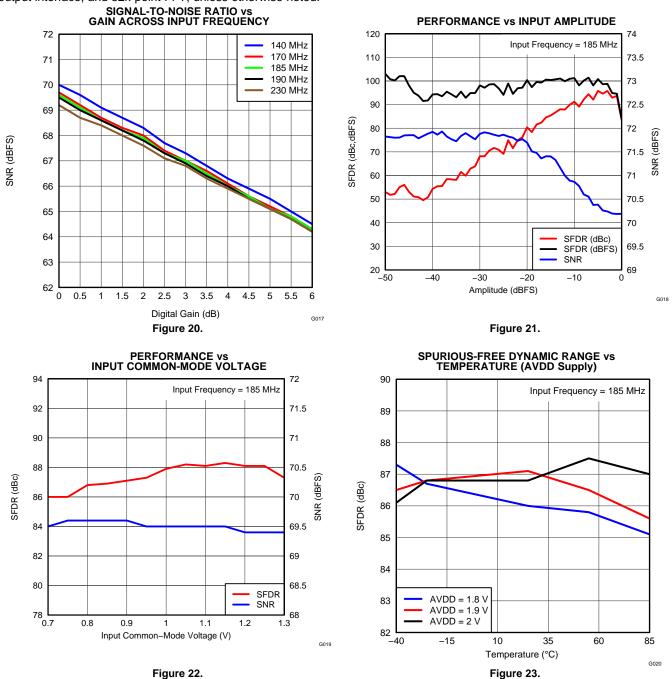

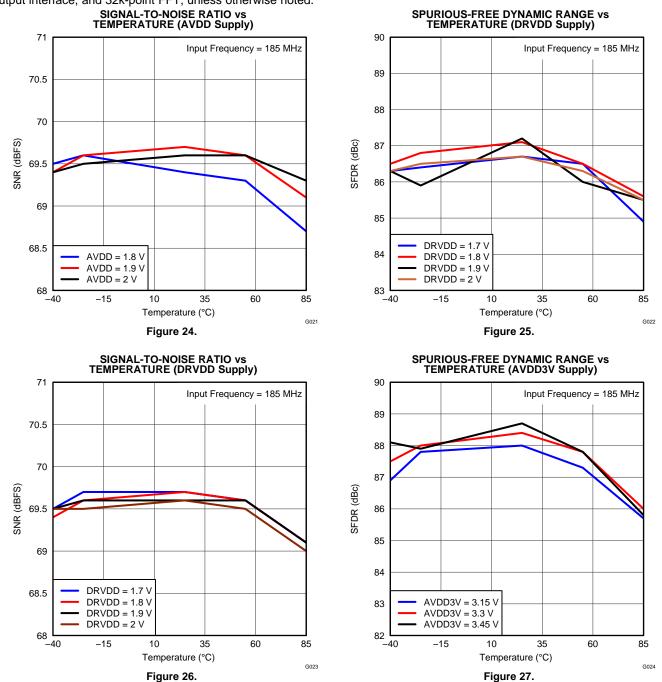

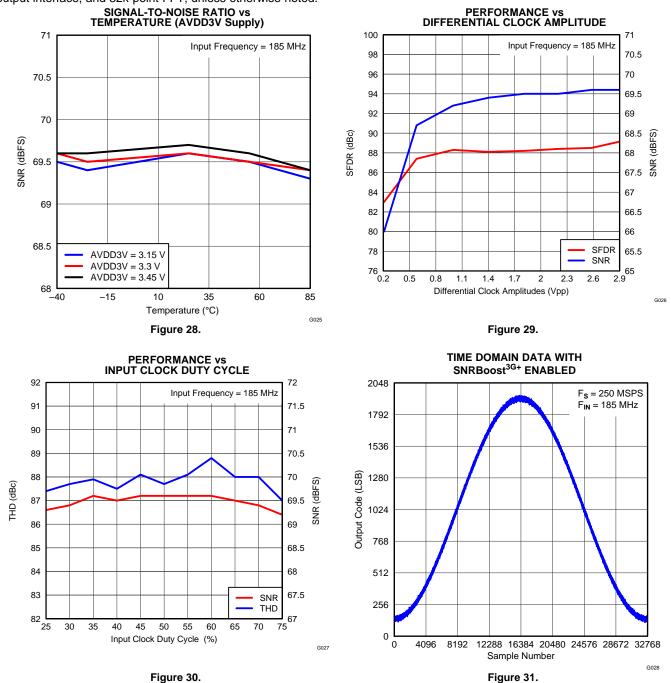

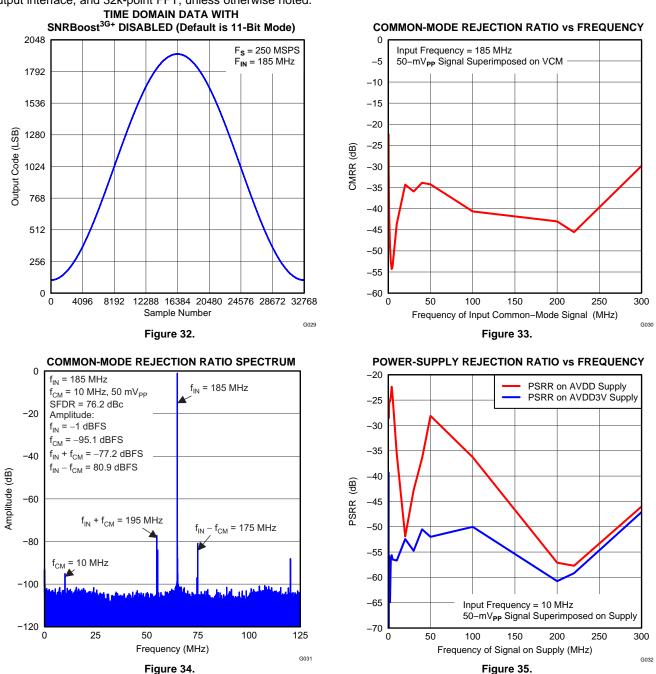

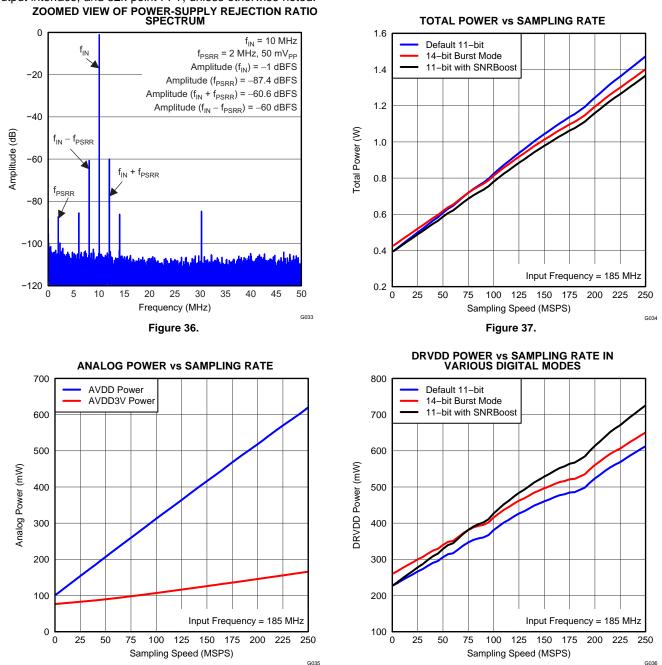

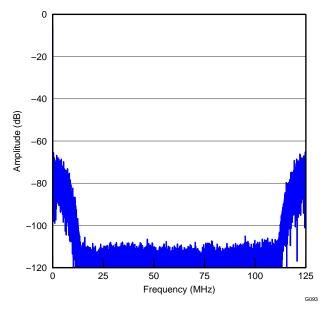

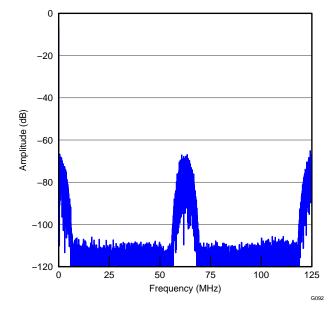

# **TYPICAL CHARACTERISTICS (continued)**

At +25°C, AVDD = 1.9 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, rated sampling frequency, 0-dB gain, 14-bit burst mode, sine wave input clock, 1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, DDR LVDS output interface, and 32k-point FFT, unless otherwise noted.

Figure 11.

#### ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

www.ti.com.cn

### **TYPICAL CHARACTERISTICS (continued)**

www.ti.com.cn

# **TYPICAL CHARACTERISTICS (continued)**

#### www.ti.com.cn

### **TYPICAL CHARACTERISTICS (continued)**

www.ti.com.cn

# **TYPICAL CHARACTERISTICS (continued)**

#### ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

www.ti.com.cn

### **TYPICAL CHARACTERISTICS (continued)**

www.ti.com.cn

# **TYPICAL CHARACTERISTICS (continued)**

#### ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

www.ti.com.cn

#### **TYPICAL CHARACTERISTICS (continued)**

At +25°C, AVDD = 1.9 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, rated sampling frequency, 0-dB gain, 14-bit burst mode, sine wave input clock, 1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, DDR LVDS output interface, and 32k-point FFT, unless otherwise noted.

# Figure 39.

Figure 38.

# DEVICE CONFIGURATION

The ADS58H40 can be configured with a serial programming interface (SPI), as described in the Serial Interface section. In addition, the device has control pins that control power-down and SNRBoost<sup>3G+</sup> operation.

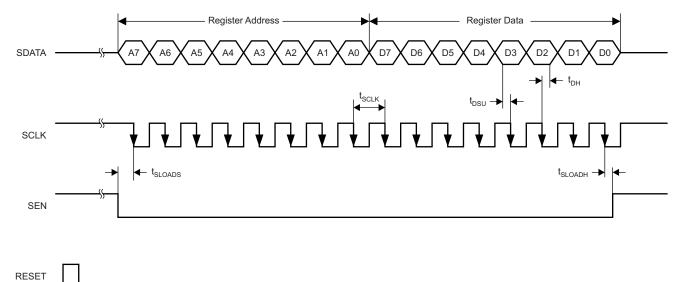

### SERIAL INTERFACE

The ADC has a set of internal registers that can be accessed by the serial interface formed by the SEN (serial interface enable), SCLK (serial interface clock), SDATA (serial interface input data), and SDOUT (serial interface read back data) pins. The serial shift of bits into the device is enabled when SEN is low. Serial data (SDATA) are latched at every SCLK falling edge when SEN is active (low). The serial data are loaded into the register at every 16th SCLK falling edge when SEN is low. When the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data can be loaded in multiples of 16-bit words within a single active SEN pulse. The first eight bits form the register address and the remaining eight bits are the register data. The interface can function with SCLK frequencies from 20 MHz down to very low speeds (of a few hertz) and also with a non-50% SCLK duty cycle.

### **Register Initialization**

After power-up, the internal registers must be initialized to the default values. This initialization can be accomplished in one of two ways:

- 1. Either through a hardware reset by applying a high pulse on the RESET pin (of widths greater than 10 ns), as shown in Figure 40; or

- By applying a software reset. When using the serial interface, set the RESET bit (D1 in register 00h) high. This setting initializes the internal registers to the default values and then self-resets the RESET bit low. In this case, the RESET pin is kept low.

### Figure 40. Serial Interface Timing

|                     | PARAMETER                                        | MIN  | TYP | MAX | UNIT |

|---------------------|--------------------------------------------------|------|-----|-----|------|

| f <sub>SCLK</sub>   | SCLK frequency (equal to 1 / t <sub>SCLK</sub> ) | > dc |     | 20  | MHz  |

| t <sub>SLOADS</sub> | SEN to SCLK setup time                           | 25   |     |     | ns   |

| t <sub>SLOADH</sub> | SCLK to SEN hold time                            | 25   |     |     | ns   |

| t <sub>DSU</sub>    | SDI setup time                                   | 25   |     |     | ns   |

| t <sub>DH</sub>     | SDI hold time                                    | 25   |     |     | ns   |

### Table 3. Timing Characteristics for Figure 40

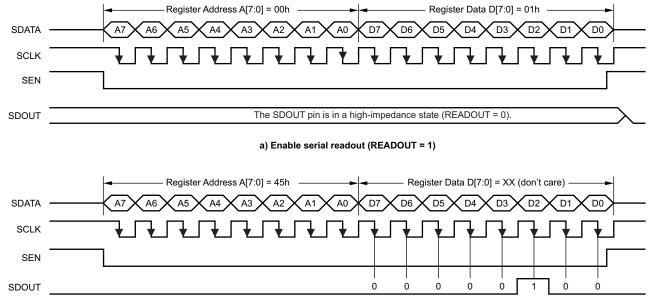

#### Serial Register Readout

The device includes a mode where the contents of the internal registers can be read back, as shown in Figure 41. This read-back mode can be useful as a diagnostic check to verify the serial interface communication between the external controller and ADC.

- 1. Set the READOUT register bit to '1'. This setting disables any further writes to the registers except register address 00h.

- 2. Initiate a serial interface cycle specifying the address of the register (A[7:0]) whose content must be read.

- 3. The device outputs the contents (D[7:0]) of the selected register on the SDOUT pin (pin G10).

- 4. The external controller can latch the contents at the SCLK falling edge.

- 5. To enable register writes, reset the READOUT register bit to '0'.

Note that the contents of register 00h cannot be read back because the register contains RESET and READOUT bits. When the READOUT bit is disabled, the SDOUT pin is in a high-impedance state. If serial readout is not used, the SDOUT pin must not be connected (must float).

The SDOUT pin functions as a serial readout (READOUT = 1).

b) Read contents of Register 45h. This register is initialized with 04h.

Figure 41. Serial Readout Timing Diagram

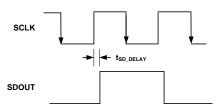

SDOUT comes out at the SCLK rising edge with an approximate delay (t<sub>SD DELAY</sub>) of 8 ns, as shown in Figure 42.

Figure 42. SDOUT Delay Timing

ZHCSA63B-AUGUST 2012-REVISED NOVEMBER 2012

# SERIAL INTERFACE REGISTERS

Table 4 summarizes the ADS58H40 registers.

|                     | 1                             |                    | 1.451              | e 4. Registe      |                             |                      |                    |                      |

|---------------------|-------------------------------|--------------------|--------------------|-------------------|-----------------------------|----------------------|--------------------|----------------------|

| REGISTER<br>ADDRESS |                               | 1                  |                    | REGIST            | ER DATA                     | I                    | I                  | I                    |

| A[7:0] (Hex)        | D7                            | D6                 | D5                 | D4                | D3                          | D2                   | D1                 | D0                   |

| 00                  | 0                             | 0                  | 0                  | 0                 | 0                           | 0                    | RESET              | READOUT              |

| 01                  |                               |                    | LVDS               | SWING             | Т                           | T.                   | 0                  | 0                    |

| 25                  |                               | DIGITAL G          | GAIN CH B          |                   | DIGITAL GAIN<br>BYPASS CH B | г                    | EST PATTERN CH     | В                    |

| 2B                  |                               | DIGITAL G          | GAIN CH A          |                   | DIGITAL GAIN<br>BYPASS CH A | Т                    | EST PATTERN CH     | A                    |

| 31                  |                               | DIGITAL G          | GAIN CH D          |                   | DIGITAL GAIN<br>BYPASS CH D | Т                    | EST PATTERN CH     | D                    |

| 37                  |                               | DIGITAL G          | GAIN CH C          |                   | DIGITAL GAIN<br>BYPASS CH C | Т                    | EST PATTERN CH     | С                    |

| 3D                  | 0                             | 0                  | SEL OFFSET<br>CORR | 0                 | 0                           | 0                    | 0                  | 0                    |

| ЗF                  | 0                             | 0                  |                    | L                 | CUSTOM PA                   | TTERN[13:8]          | L                  |                      |

| 40                  |                               |                    |                    | CUSTOM P          | ATTERN[7:0]                 |                      |                    |                      |

| 41                  | 0                             | 0                  | 0                  |                   | HIGH RESOLUTIO              | ON SAMPLES, NH       |                    | AUTO BURST<br>ENABLE |

| 42                  | 0                             | 0                  | 0                  | 0                 | DIGITAL ENABLE              | SNRB 45/95MHz        | LOW RESOLUTI       | ON SAMPLES, NL       |

| 44                  | BMODE EN<br>CH CD             | BMODE EN CH<br>AB  | 0                  | 0                 | 0                           | BMODE OVR<br>ENABLE  | 0                  | DIS SNRB             |

| 45                  | 0                             | 0                  | 0                  | 0                 | SEL OVR                     | GLOBAL POWER<br>DOWN | 0                  | CONFIG PDN PI        |

| A9                  | 0                             | 0                  | 0                  | 0                 |                             | CLOCKOUT DEL         | AY PROG CH AB      | ł                    |

| AC                  | 0 CLOCKOUT DELAY PROG CH CD 0 |                    |                    |                   |                             | 0                    | 0                  | 0                    |

| C3                  |                               |                    |                    | FAST OVR T        | HRESH PROG                  |                      | L                  | 1                    |

| C4                  | EN FAST OVR<br>THRESH         | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | 0                    |

| CF                  | 0                             | 0                  | 0                  | 0                 | SPECIAL<br>MODE 0           | 0                    | 0                  | 0                    |

| D4                  | SPECIAL<br>MODE 1             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | 0                    |

| D5                  | SPECIAL<br>MODE 2             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | 0                    |

| D6                  | SPECIAL<br>MODE 3             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | 0                    |

| D7                  | 0                             | 0                  | 0                  | 0                 | SPECIAL<br>MODE 5           | SPECIAL<br>MODE 4    | 0                  | 0                    |

| DB                  | 0                             | 0                  | SPECIAL<br>MODE 7  | SPECIAL<br>MODE 6 | 0                           | 0                    | 0                  | 0                    |

| F0                  | 0                             | 0                  | SPECIAL<br>MODE 10 | SPECIAL<br>MODE 9 | SPECIAL<br>MODE 8           | 0                    | 0                  | 0                    |

| F1                  | 0                             | 0                  | SPECIAL<br>MODE 11 | 0                 | 0                           | ENA                  | BLE LVDS SWING F   | PROG                 |

| F5                  | 0                             | SPECIAL<br>MODE 13 | 0                  | 0                 | 0                           | 0                    | SPECIAL<br>MODE 12 | 0                    |

| 4A                  | 0                             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | SPECIAL<br>MODE 14   |

| 62                  | 0                             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | SPECIAL<br>MODE 15   |

| 92                  | 0                             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | SPECIAL<br>MODE 16   |

| 7A                  | 0                             | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | SPECIAL<br>MODE 17   |

| EA                  | SNRB PIN OVRD                 | 0                  | 0                  | 0                 | 0                           | 0                    | 0                  | 0                    |

| FE                  | 0                             | 0                  | 0                  | 0                 | PDN CH D                    | PDN CH C             | PDN CH A           | PDN CH B             |

### Table 4. Register Map

**DESCRIPTION OF SERIAL REGISTERS**

www.ti.com.cn

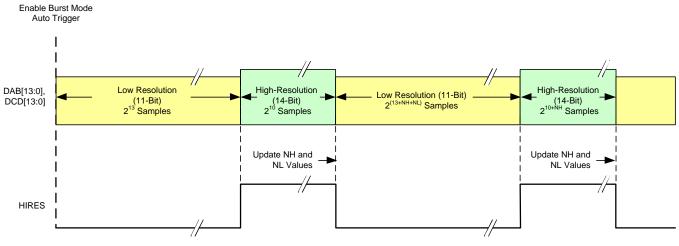

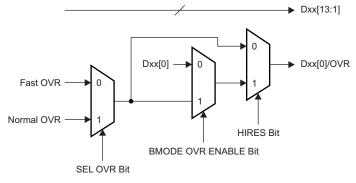

|             |                                                                                      | Regis                                                                                                                                                                                           | ster Address                                                                  | 00h (Default =                                                                             | = 00h)                                                               |                                              |         |  |  |