ADS54J69

ZHCSEJ4C -MAY 2015-REVISED JANUARY 2017

# ADS54J69 双通道、16 位、500MSPS 模数转换器

# 1 特性

- 16 位分辨率、双通道、500 MSPS 模数转换器 (DAC)

- 空闲通道噪底: -159dBFS/Hz

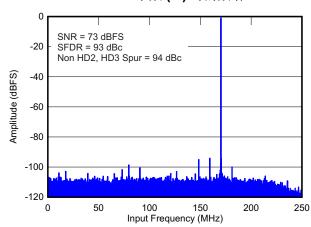

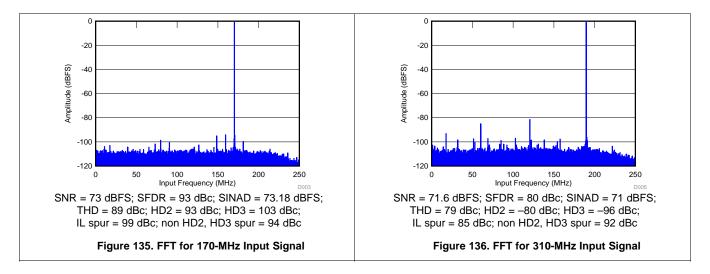

- 频谱性能(-1dBFS 时的 f<sub>IN</sub> = 170MHz):

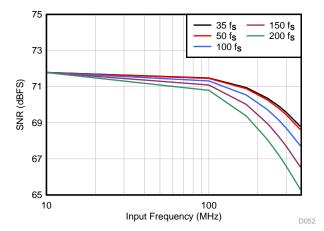

- 信噪比 (SNR): 73dBFS

- 噪声频谱密度 (NSD): -157dBFS/Hz

- 无杂散动态范围 (SFDR): 93dBc

- SFDR: 94dBc(不包括 HD2、HD3 和交错音调)

- 频谱性能(-1dBFS 时的 f<sub>IN</sub> = 310MHz):

- SNR: 71.7dBFS

- NSD: -155.7dBFS/Hz

- SFDR: 81dBc

- SFDR: 94dBc(不包括 HD2、HD3 和交错音调)

- 通道隔离: f<sub>IN</sub> = 170MHz 时为 100dBc

- 输入满量程: 1.9 V<sub>PP</sub>

- 输入带宽 (3dB): 1.2GHz

- 片上抖动

- 集成 2 倍抽取率滤波器

- 支持 JESD204B 子类 1 接口:

- 10.0Gbps 时每个 ADC 1 条通道

- 5.0Gbps 时每个 ADC 2 条通道

- 支持多芯片同步

- 功耗: 500MSPS 时为 1.35W/通道

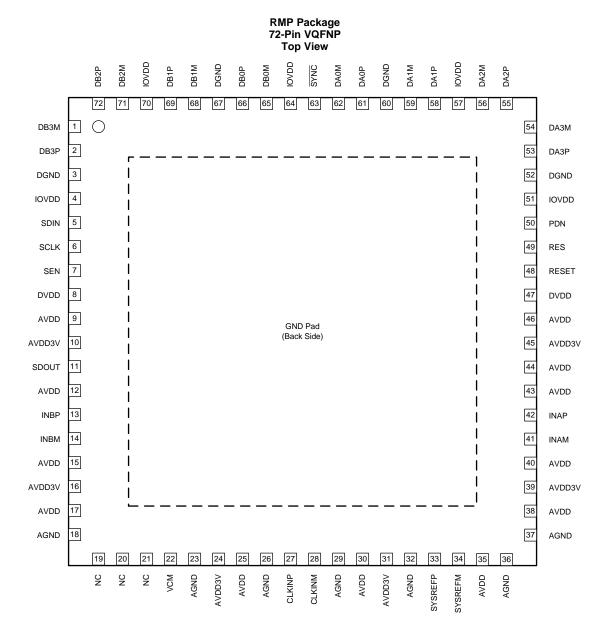

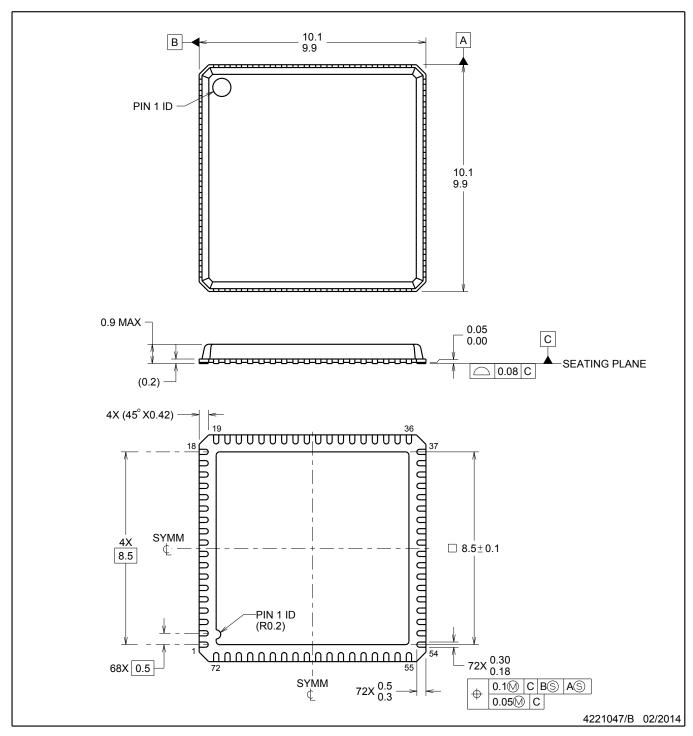

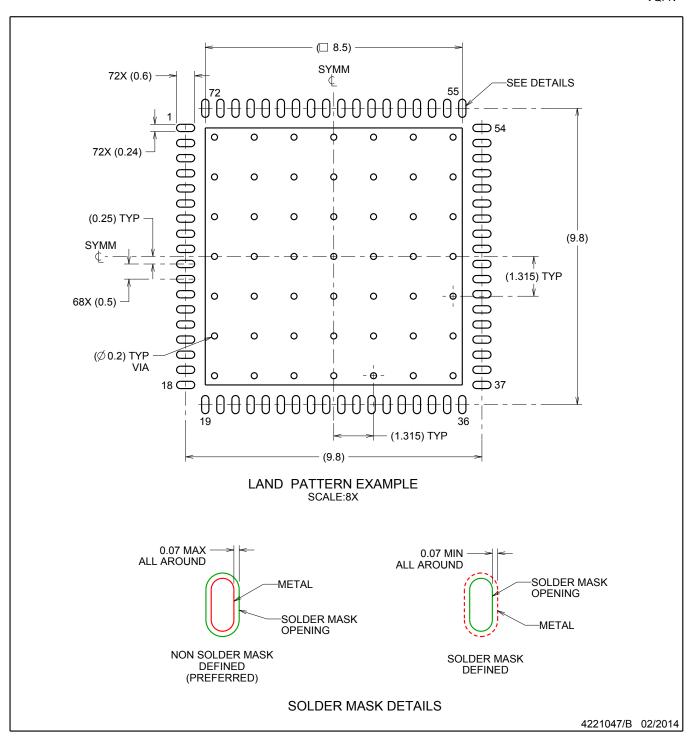

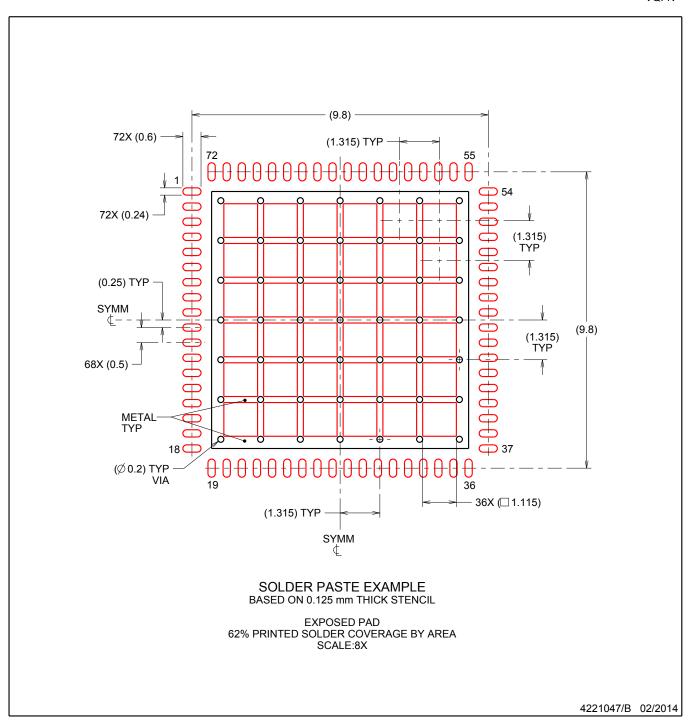

- 72 引脚超薄型四方扁平无引线 (VQFN) 封装 (10mm × 10mm)

## 2 应用

- 雷达和天线阵列

- 无线宽带

- 电缆 CMTS、DOCSIS 3.1 接收器

- 通信测试设备

- 微波接收器

- 软件定义无线电 (SDR)

- 数字转换器

- 医疗成像和诊断功能

# 3 说明

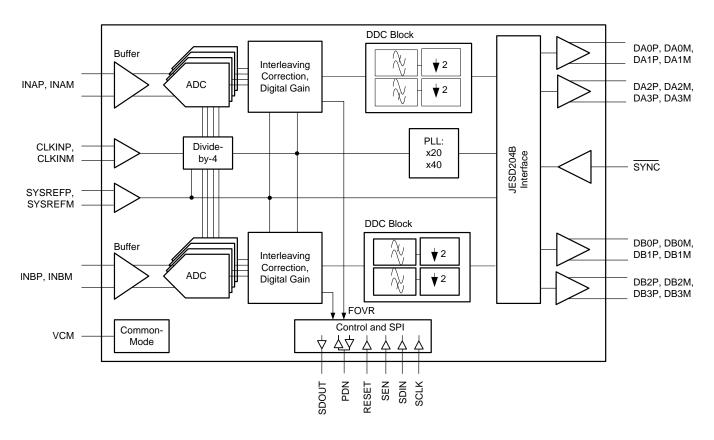

ADS54J69 是一款低功耗、高带宽 16 位、500MSPS 双通道模数转换器 (ADC)。该器件经设计具有高信噪比 (SNR),可提供 -159dBFS/Hz 的噪底,从而 协助应用在宽瞬时带宽内 实现最高动态范围。该器件支持JESD204B 串行接口,数据传输速率高达 10Gbps,每个 ADC 可支持 1 或 2 条通道。经缓冲的模拟输入可在较宽频率范围内提供统一输入阻抗并最大程度地降低采样和保持毛刺脉冲能量。可选择将每条 ADC 通道直接与宽带数字下变频器 (DDC) 模块相连。ADS54J69以超低功耗在宽输入频率范围内提供出色的无杂散动态范围 (SFDR)。

JESD204B 接口减少了接口线路数,从而实现高系统集成度。内部锁相环 (PLL) 会将 ADC 采样时钟加倍,以获得串行化各通道的 16 位数据时所使用的位时钟。

### 器件信息

| 器件编号     | 封装         | 封装尺寸 (标称值)        |

|----------|------------|-------------------|

| ADS54J69 | VQFNP (72) | 10.00mm x 10.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

#### 170MHz 中频 (IF) 时的频谱

| 1 | 特性 1                                 |    | 8.3 Feature Description                  | 25               |

|---|--------------------------------------|----|------------------------------------------|------------------|

| 2 | 应用1                                  |    | 8.4 Device Functional Modes              | 30               |

| 3 | <br>说明 1                             |    | 8.5 Register Maps                        | 39               |

| 4 | 修订历史记录                               | 9  | Application and Implementation           | 63               |

| 5 | Device Comparison Table 4            |    | 9.1 Application Information              | 63               |

| 6 | Pin Configuration and Functions      |    | 9.2 Typical Application                  | 68               |

| 7 | Specifications                       | 10 | Power Supply Recommendations             | 70               |

| • | 7.1 Absolute Maximum Ratings         |    | 10.1 Power Sequencing and Initialization | <mark>7</mark> 1 |

|   | 7.2 ESD Ratings                      | 11 | Layout                                   | 72               |

|   | 7.3 Recommended Operating Conditions |    | 11.1 Layout Guidelines                   | 72               |

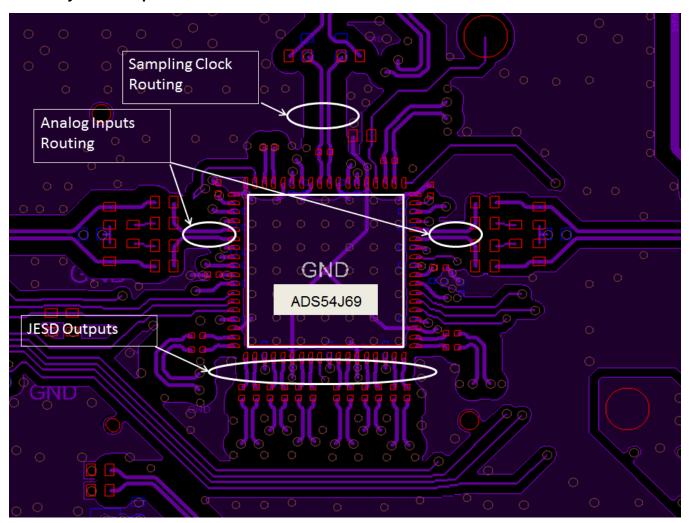

|   | 7.4 Thermal Information              |    | 11.2 Layout Example                      | <mark>7</mark> 3 |

|   | 7.5 Electrical Characteristics       | 12 | 器件和文档支持                                  | <b>7</b> 4       |

|   | 7.6 AC Characteristics               |    | 12.1 文档支持                                | 74               |

|   | 7.7 Digital Characteristics          |    | 12.2 接收文档更新通知                            | 74               |

|   | 7.8 Timing Characteristics           |    | 12.3 社区资源                                | 74               |

|   | 7.9 Typical Characteristics          |    | 12.4 商标                                  |                  |

| 8 | Detailed Description 24              |    | 12.5 静电放电警告                              |                  |

| - | 8.1 Overview                         |    | 12.6 Glossary                            |                  |

|   | 8.2 Functional Block Diagram         | 13 | 机械、封装和可订购信息                              | <b>7</b> 4       |

|   | ŭ                                    |    |                                          |                  |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Changes from Revision B (February 2016) to Revision C                       | Page       |

|-----------------------------------------------------------------------------|------------|

| Added Device Comparison Table                                               | 5          |

| Added the FOVR latency parameter to the <i>Timing Characteristics</i> table | 12         |

| Added SYSREF Not Present (Subclass 0, 2) section                            | 27         |

| Changed the number of clock cycles in the Fast OVR section                  | 28         |

| Changed the Register Map                                                    | 40         |

| Deleted register 39h, 3Ah, and 56h                                          | 40         |

| Changed the SNR versus Input Frequency and External Clock Jitter figure     | 67         |

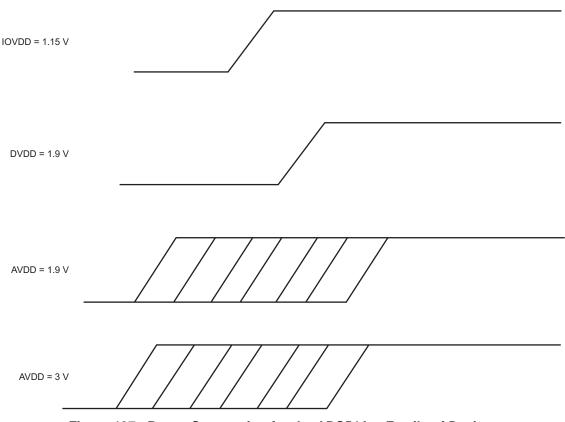

| Changed Power Supply Recommendations section                                | 70         |

| Added the Power Sequencing and Initialization section                       | 71         |

| • 己添加 文档支持和接收文档更新通知部分                                                       | <b>7</b> 4 |

| • 己添加 接收文档更新通知部分                                                            | 74         |

| CI | hanges from Revision A (January 2016) to Revision B                                   | Page |

|----|---------------------------------------------------------------------------------------|------|

| •  | Changed Sample Timing, Aperture jitter parameter in Timing Characteristics table      | 12   |

| •  | Changed Table 35                                                                      | 5    |

| •  | Changed Table 42                                                                      | 54   |

| •  | Changed Table 44                                                                      | 55   |

| •  | Changed SNR and Clock Jitter section: changed Figure 130 and last sentence of section | 67   |

| •  | Changed Application Curves section                                                    | 70   |

| Changes from Original (May 2015) to Revision A |   |  |

|------------------------------------------------|---|--|

| • 已发布为"量产数据"                                   | 1 |  |

# 5 Device Comparison Table

| PART NUMBER | SPEED GRADE (MSPS) | RESOLUTION (Bits) | CHANNEL |

|-------------|--------------------|-------------------|---------|

| ADS54J20    | 1000               | 12                | 2       |

| ADS54J42    | 625                | 14                | 2       |

| ADS54J40    | 1000               | 14                | 2       |

| ADS54J60    | 1000               | 16                | 2       |

| ADS54J66    | 500                | 14                | 4       |

| ADS54J69    | 500                | 16                | 2       |

# 6 Pin Configuration and Functions

## **Pin Functions**

|            | PIN                                              |     |                                                                                                                                                                                                      |  |

|------------|--------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO.                                              | 1/0 | DESCRIPTION                                                                                                                                                                                          |  |

| CLOCK, SYS | REF                                              |     |                                                                                                                                                                                                      |  |

| CLKINM     | 28                                               | I   | Negative differential clock input for the ADC                                                                                                                                                        |  |

| CLKINP     | 27                                               | 1   | Positive differential clock input for the ADC                                                                                                                                                        |  |

| SYSREFM    | 34                                               | I   | Negative external SYSREF input                                                                                                                                                                       |  |

| SYSREFP    | 33                                               | I   | Positive external SYSREF input                                                                                                                                                                       |  |

| CONTROL, S | ERIAL INTERFACE                                  |     |                                                                                                                                                                                                      |  |

| PDN        | 50                                               | I/O | Power-down. Can be configured via an SPI register setting. Can be configured to fast overrange output for channel A via the SPI.                                                                     |  |

| RESET      | 48                                               | I   | Hardware reset; active high. This pin has an internal 20-kΩ pulldown resistor.                                                                                                                       |  |

| SCLK       | 6                                                | I   | Serial interface clock input                                                                                                                                                                         |  |

| SDIN       | 5                                                | I   | Serial interface data input                                                                                                                                                                          |  |

| SDOUT      | 11                                               | 0   | Serial interface data output. Can be configured to fast overrange output for channel B via the SPI.                                                                                                  |  |

| SEN        | 7                                                | I   | Serial interface enable                                                                                                                                                                              |  |

| DATA INTER | FACE                                             |     |                                                                                                                                                                                                      |  |

| DA0M       | 62                                               |     |                                                                                                                                                                                                      |  |

| DA1M       | 59                                               | 0   | IECD204P parial data pagative autouts for channel A                                                                                                                                                  |  |

| DA2M       | 56                                               | U   | JESD204B serial data negative outputs for channel A                                                                                                                                                  |  |

| DA3M       | 54                                               |     |                                                                                                                                                                                                      |  |

| DA0P       | 61                                               |     |                                                                                                                                                                                                      |  |

| DA1P       | 58                                               | 0   | JESD204B serial data positive outputs for channel A                                                                                                                                                  |  |

| DA2P       | 55                                               | O   | 3ESD204B Serial data positive outputs for charmer A                                                                                                                                                  |  |

| DA3P       | 53                                               |     |                                                                                                                                                                                                      |  |

| DB0M       | 65                                               |     |                                                                                                                                                                                                      |  |

| DB1M       | 68                                               | 0   | IECD204P parial data pagative autouts for channel P                                                                                                                                                  |  |

| DB2M       | 71                                               | O   | JESD204B serial data negative outputs for channel B                                                                                                                                                  |  |

| DB3M       | 1                                                |     |                                                                                                                                                                                                      |  |

| DB0P       | 66                                               |     |                                                                                                                                                                                                      |  |

| DB1P       | 69                                               | 0   | JESD204B serial data positive outputs for channel B                                                                                                                                                  |  |

| DB2P       | 72                                               | O   | 3E3D204B Serial data positive outputs for charmer B                                                                                                                                                  |  |

| DB3P       | 2                                                |     |                                                                                                                                                                                                      |  |

| SYNC       | 63                                               | I   | Synchronization input for JESD204B port                                                                                                                                                              |  |

| INPUT, COM | MON MODE                                         |     |                                                                                                                                                                                                      |  |

| INAM       | 41                                               | I   | Differential analog negative input for channel A                                                                                                                                                     |  |

| INAP       | 42                                               | I   | Differential analog positive input for channel A                                                                                                                                                     |  |

| INBM       | 14                                               | I   | Differential analog negative input for channel B                                                                                                                                                     |  |

| INBP       | 13                                               | ı   | Differential analog positive input for channel B                                                                                                                                                     |  |

| VCM        | 22                                               | 0   | Common-mode voltage, 2.1 V. Note that analog inputs are internally biased to this pin through 600 $\Omega$ (effective), no external connection from the VCM pin to the INxP or INxM pin is required. |  |

| POWER SUP  | PLY                                              |     |                                                                                                                                                                                                      |  |

| AGND       | 18, 23, 26, 29, 32, 36, 37                       | ı   | Analog ground                                                                                                                                                                                        |  |

| AVDD       | 9, 12, 15, 17, 25, 30, 35, 38,<br>40, 43, 44, 46 | 1   | Analog 1.9-V power supply                                                                                                                                                                            |  |

| AVDD3V     | 10, 16, 24, 31, 39, 45                           | I   | Analog 3.0-V power supply for the analog buffer                                                                                                                                                      |  |

| DGND       | 3, 52, 60, 67                                    | I   | Digital ground                                                                                                                                                                                       |  |

| DVDD       | 8, 47                                            | I   | Digital 1.9-V power supply                                                                                                                                                                           |  |

| IOVDD      | 4, 51, 57, 64, 70                                | I   | I Digital 1.15-V power supply for the JESD204B transmitter                                                                                                                                           |  |

| NC, RES    |                                                  |     |                                                                                                                                                                                                      |  |

| NC         | 19, 20, 21                                       |     | Unused pins, do not connect                                                                                                                                                                          |  |

| RES        | 49                                               | I   | Reserved pin. Connect to DGND.                                                                                                                                                                       |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                                                                                                                                                                                               | MIN  | MAX        | UNIT |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------|--|

|                                       | AVDD3V                                                                                                                                                                                                                        | -0.3 | 3.6        |      |  |

| Supply voltage range                  | AVDD                                                                                                                                                                                                                          | -0.3 | 2.1        | V    |  |

| Supply voltage range                  | DVDD                                                                                                                                                                                                                          | -0.3 | 2.1        | V    |  |

|                                       | AVDD3V -0.3 3.6  AVDD -0.3 2.1  DVDD -0.3 2.1  IOVDD -0.2 1.4  and DGND -0.3 0.3  INAP, INBP, INAM, INBM -0.3 3  CLKINP, CLKINM -0.3 AVDD + 0.3  SYSREFP, SYSREFM -0.3 AVDD + 0.3  SCLK, SEN, SDIN, RESET, SYNC, PDN -0.2 2.1 |      |            |      |  |

| Voltage between AGND and D            | OGND                                                                                                                                                                                                                          | -0.3 | 0.3        | V    |  |

|                                       | INAP, INBP, INAM, INBM                                                                                                                                                                                                        | -0.3 | 3          |      |  |

| Valtage applied to input pine         | CLKINP, CLKINM                                                                                                                                                                                                                | -0.3 | AVDD + 0.3 | V    |  |

| Voltage applied to input pins         | SYSREFP, SYSREFM                                                                                                                                                                                                              | -0.3 | AVDD + 0.3 | V    |  |

|                                       | SCLK, SEN, SDIN, RESET, SYNC, PDN                                                                                                                                                                                             | -0.2 | 2.1        |      |  |

| Storage temperature, T <sub>stg</sub> |                                                                                                                                                                                                                               | -65  | 150        | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Floatroctatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)(2)

|                           |                                                                                          |                       | MIN  | NOM                | MAX  | UNIT     |

|---------------------------|------------------------------------------------------------------------------------------|-----------------------|------|--------------------|------|----------|

|                           | AVDD3V                                                                                   |                       | 2.85 | 3.0                | 3.6  |          |

| Complement and an arrange | AVDD                                                                                     |                       | 1.8  | 1.9                | 2.0  | V        |

| Supply voltage range      | DVDD                                                                                     |                       | 1.7  | 1.9                | 2.0  |          |

|                           | IOVDD                                                                                    | 1.1                   | 1.15 | 1.2                |      |          |

|                           | Differential input voltage range                                                         |                       |      | 1.9                |      | $V_{PP}$ |

| Analog inputs             | Input common-mode voltage                                                                |                       |      | 2.0                |      | V        |

|                           | Maximum analog input frequency for 1.9-V <sub>PP</sub> input amplitude <sup>(3)(4)</sup> |                       |      | 400                |      | MHz      |

|                           | Input clock frequency, device clock frequency                                            |                       | 500  |                    | 1000 | MHz      |

|                           | Input clock amplitude differential (VCLKP - VCLKM)                                       | Sine wave, ac-coupled | 0.75 | 1.5                |      |          |

| Clock inputs              |                                                                                          | LVPECL, ac-coupled    | 0.8  | 1.6                |      | $V_{PP}$ |

|                           | (*CLRP *CLRM)                                                                            | LVDS, ac-coupled      |      | 0.7                |      |          |

|                           | Input device clock duty cycle                                                            |                       | 45%  | 50%                | 55%  |          |

| Tomporoturo               | Operating free-air, T <sub>A</sub>                                                       |                       | -40  |                    | 85   | °C       |

| Temperature               | Operating junction, T <sub>J</sub>                                                       |                       |      | 105 <sup>(5)</sup> | 125  | -0       |

<sup>1)</sup> SYSREF must be applied for the device to initialize; see the SYSREF Signal section for details.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V HBM allows safe manufacturing with a standard ESD control process.

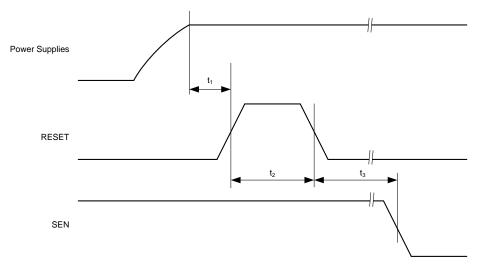

<sup>(2)</sup> After power-up, always use a hardware reset to reset the device for the first time; see Table 60 for details.

<sup>(3)</sup> Operating 0.5 dB below the maximum-supported amplitude is recommended to accommodate gain mismatch in interleaving ADCs.

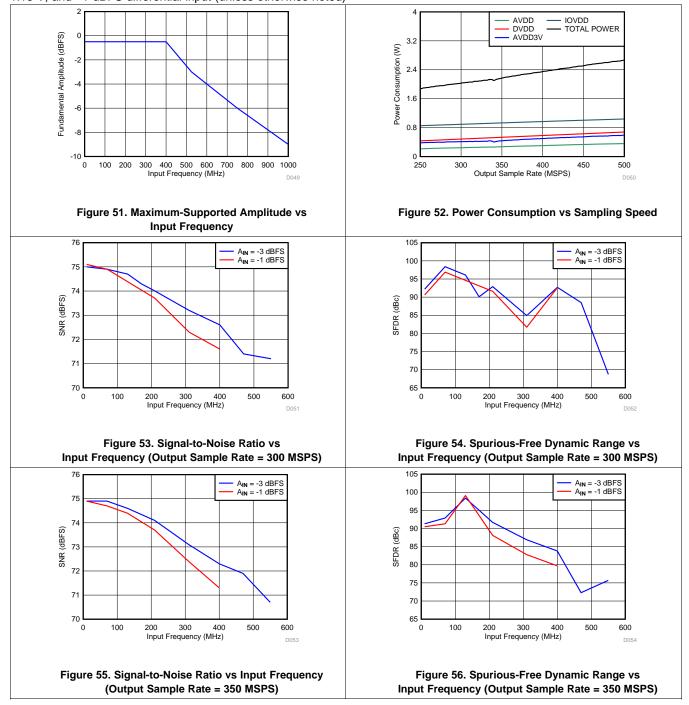

<sup>(4)</sup> At high frequencies, the maximum supported input amplitude reduces; see Figure 51 for details.

<sup>(5)</sup> Prolonged use above the nominal junction temperature can increase the device failure-in-time (FIT) rate.

### 7.4 Thermal Information

|                      |                                              | ADS54J69 |      |

|----------------------|----------------------------------------------|----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                |          | UNIT |

|                      |                                              | 72 PINS  |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 22.3     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 5.1      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 2.4      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1      | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 2.3      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.4      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

|                     | PARAMETER                           | TEST CONDITIONS                                      | MIN  | TYP  | MAX  | UNIT |

|---------------------|-------------------------------------|------------------------------------------------------|------|------|------|------|

| GENERAL             |                                     |                                                      |      |      |      |      |

|                     | Device clock frequency              |                                                      |      |      | 1000 | MSPS |

|                     | Output sample rate                  |                                                      |      |      | 500  | MSPS |

|                     | Resolution                          |                                                      | 16   |      |      | Bits |

| POWER SUPP          | LIES                                |                                                      |      |      |      |      |

| AVDD3V              | 3.0-V analog supply                 |                                                      | 2.85 | 3.0  | 3.6  | V    |

| AVDD                | 1.9-V analog supply                 |                                                      | 1.8  | 1.9  | 2.0  | V    |

| DVDD                | 1.9-V digital supply                |                                                      | 1.7  | 1.9  | 2.0  | V    |

| IOVDD               | 1.15-V SERDES supply                |                                                      | 1.1  | 1.15 | 1.2  | V    |

| I <sub>AVDD3V</sub> | 3.0-V analog supply current         | V <sub>IN</sub> = full-scale on both channels        |      | 293  | 360  | mA   |

| I <sub>AVDD</sub>   | 1.9-V analog supply current         | V <sub>IN</sub> = full-scale on both channels        |      | 354  | 510  | mA   |

| I <sub>DVDD</sub>   | 1.9-V digital supply current        |                                                      |      | 188  | 260  | mA   |

| I <sub>IOVDD</sub>  | 1.15-V SERDES supply current        | Four-lane output mode (default after reset)          |      | 512  | 920  | mA   |

| P <sub>dis</sub>    | Total power dissipation             | (deladit ditel reset)                                |      | 2.66 | 3.1  | W    |

| I <sub>DVDD</sub>   | 1.9-V digital supply current        |                                                      |      | 195  |      | mA   |

| I <sub>IOVDD</sub>  | 1.15-V SERDES supply current        | Two-lane output mode                                 |      | 559  |      | mA   |

| P <sub>dis</sub>    | Total power dissipation             |                                                      |      | 2.73 |      | W    |

|                     | Global power-down power dissipation | Using the GLOBAL PDN register bit in the master page |      | 204  | 315  | mW   |

# 7.6 AC Characteristics

|       | PARAMETER                                           | TEST CONDITIONS                                      | MIN   | TYP   | MAX | UNIT    |

|-------|-----------------------------------------------------|------------------------------------------------------|-------|-------|-----|---------|

|       |                                                     | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |       | 74.2  |     |         |

|       |                                                     | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 73.4  |     |         |

|       |                                                     | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 71.3  | 73    |     |         |

| SNR   | Signal-to-noise ratio                               | $f_{IN} = 210 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 72.7  |     | dBFS    |

|       |                                                     | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 71.7  |     |         |

|       |                                                     | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 70.3  |     |         |

|       |                                                     | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$ |       | 70.5  |     |         |

|       |                                                     | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |       | 158.2 |     |         |

|       |                                                     | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 157.4 |     |         |

|       |                                                     | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 155.3 | 157.0 |     |         |

| NSD   | Noise spectral density                              | $f_{IN} = 210 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 156.7 |     | dBFS/Hz |

|       |                                                     | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 155.7 |     |         |

|       |                                                     | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 154.3 |     |         |

|       |                                                     | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$ |       | 154.5 |     |         |

|       |                                                     | f <sub>IN</sub> = 10 MHz, A <sub>IN</sub> = -1 dBFS  |       | 73.8  |     |         |

|       |                                                     | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 73.3  |     |         |

|       | Signal-to-noise and distortion ratio                | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 69.8  | 72.9  |     | dBFS    |

| SINAD |                                                     | $f_{IN} = 210 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 72.5  |     |         |

|       |                                                     | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 71.2  |     |         |

|       |                                                     | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 70.2  |     |         |

|       |                                                     | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$ |       | 69.4  |     |         |

|       |                                                     | f <sub>IN</sub> = 10 MHz, A <sub>IN</sub> = -1 dBFS  |       | 86    |     |         |

|       |                                                     | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 95    |     |         |

|       |                                                     | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 79    | 94    |     |         |

| SFDR  | Spurious free dynamic range<br>(excluding IL spurs) | $f_{IN} = 210 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 89    |     | dBc     |

|       | (excluding it spars)                                | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 81    |     |         |

|       |                                                     | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 87    |     |         |

|       |                                                     | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$ |       | 73    |     |         |

|       |                                                     | f <sub>IN</sub> = 10 MHz, A <sub>IN</sub> = -1 dBFS  |       | 86    |     |         |

|       |                                                     | f <sub>IN</sub> = 140 MHz, A <sub>IN</sub> = -1 dBFS |       | 104   |     |         |

|       |                                                     | f <sub>IN</sub> = 170 MHz, A <sub>IN</sub> = -1 dBFS | 85    | 102   |     |         |

| HD2   | Second-order harmonic distortion                    | f <sub>IN</sub> = 210 MHz, A <sub>IN</sub> = -1 dBFS |       | 95    |     | dBc     |

|       |                                                     | f <sub>IN</sub> = 310 MHz, A <sub>IN</sub> = -1 dBFS |       | 81    |     |         |

|       |                                                     | f <sub>IN</sub> = 370 MHz, A <sub>IN</sub> = -1 dBFS |       | 87    |     |         |

|       |                                                     | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$ |       | 96    |     |         |

|       |                                                     | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |       | 89    |     |         |

|       |                                                     | f <sub>IN</sub> = 140 MHz, A <sub>IN</sub> = -1 dBFS |       | 103   |     |         |

|       |                                                     | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 86    | 101   |     |         |

| HD3   | Third-order harmonic distortion                     | $f_{IN} = 210 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 100   |     | dBc     |

|       |                                                     | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 98    |     |         |

|       |                                                     | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 95    |     | -       |

|       |                                                     | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$ |       | 73    |     |         |

# **AC Characteristics (continued)**

|                 | PARAMETER                                                     | TEST CONDITIONS                                                                      | MIN  | TYP  | MAX | UNIT |

|-----------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|-----|------|

|                 |                                                               | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                  |      | 98   |     |      |

|                 |                                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 95   |     |      |

|                 |                                                               | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 | 84   | 94   |     |      |

| Non<br>HD2, HD3 | Spurious-free dynamic range (excluding HD2, HD3, and IL spur) | $f_{IN} = 210 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 89   |     | dBc  |

| 1102, 1100      | (excidenting Fib2, Fibo, and it spar)                         | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 92   |     |      |

|                 |                                                               | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 97   |     |      |

|                 |                                                               | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$                                 |      | 92   |     |      |

|                 |                                                               | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                  |      | 12   |     |      |

|                 |                                                               | f <sub>IN</sub> = 140 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 11.9 |     |      |

|                 |                                                               | f <sub>IN</sub> = 170 MHz, A <sub>IN</sub> = -1 dBFS                                 | 11.3 | 11.9 |     |      |

| ENOB            | Effective number of bits                                      | f <sub>IN</sub> = 210 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 11.8 |     | Bits |

|                 |                                                               | f <sub>IN</sub> = 310 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 11.5 |     |      |

|                 |                                                               | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 11.4 |     |      |

|                 |                                                               | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$                                 |      | 11.2 |     |      |

|                 | Total harmonic distortion                                     | f <sub>IN</sub> = 10 MHz, A <sub>IN</sub> = -1 dBFS                                  |      | 84   |     | dBc  |

|                 |                                                               | $f_{IN} = 140 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 95   |     |      |

|                 |                                                               | f <sub>IN</sub> = 170 MHz, A <sub>IN</sub> = -1 dBFS                                 | 79   | 89   |     |      |

| THD             |                                                               | f <sub>IN</sub> = 210 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 85   |     |      |

|                 |                                                               | $f_{IN} = 310 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 80   |     |      |

|                 |                                                               | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 85   |     |      |

|                 |                                                               | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$                                 |      | 72   |     |      |

|                 |                                                               | f <sub>IN</sub> = 10 MHz, A <sub>IN</sub> = -1 dBFS                                  |      | 90   |     |      |

|                 |                                                               | f <sub>IN</sub> = 140 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 90   |     |      |

|                 |                                                               | f <sub>IN</sub> = 170 MHz, A <sub>IN</sub> = -1 dBFS                                 | 75   | 87   |     |      |

| SFDR_IL         | Interleaving spur                                             | f <sub>IN</sub> = 210 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 85   |     | dBc  |

|                 |                                                               | f <sub>IN</sub> = 310 MHz, A <sub>IN</sub> = -1 dBFS                                 |      | 85   |     |      |

|                 |                                                               | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                 |      | 86   |     |      |

|                 |                                                               | $f_{IN} = 470 \text{ MHz}, A_{IN} = -3 \text{ dBFS}$                                 |      | 82   |     |      |

|                 |                                                               | $f_{IN1} = 185 \text{ MHz}, f_{IN2} = 190 \text{ MHz}, A_{IN} = -7 \text{ dBFS}$     |      | 86   |     |      |

| IMD3            | Two-tone, third-order intermodulation distortion              | $f_{IN1} = 365 \text{ MHz}, f_{IN2} = 370 \text{ MHz}, A_{IN} = -7 \text{ dBFS}$     |      | 79   |     | dBFS |

|                 |                                                               | $f_{IN1} = 465 \text{ MHz}, f_{IN2} = 470 \text{ MHz}, \\ A_{IN} = -10 \text{ dBFS}$ |      | 78   |     |      |

# 7.7 Digital Characteristics

|                       | PARAMETER                                     | TEST CONDITIONS                                                    | MIN           | TYP  | MAX | UNITS               |

|-----------------------|-----------------------------------------------|--------------------------------------------------------------------|---------------|------|-----|---------------------|

| DIGITAL IN            | NPUTS (RESET, SCLK, SEN, SDIN, SYN            | C, PDN) <sup>(1)</sup>                                             |               |      |     |                     |

| V <sub>IH</sub>       | High-level input voltage                      | All digital inputs support 1.2-V and 1.8-V logic levels            | 0.8           |      |     | V                   |

| V <sub>IL</sub>       | Low-level input voltage                       | All digital inputs support 1.2-V and 1.8-V logic levels            |               |      | 0.4 | V                   |

|                       | High level input gurrant                      | SEN                                                                |               | 0    |     |                     |

| IH                    | High-level input current                      | RESET, SCLK, SDIN, PDN, SYNC                                       |               | 50   |     | μΑ                  |

|                       | Lavalara Linavitaria                          | SEN                                                                |               | 50   |     |                     |

| I <sub>IL</sub>       | Low-level input current                       | RESET, SCLK, SDIN, PDN, SYNC                                       |               | 0    |     | μA                  |

| DIGITAL IN            | NPUTS (SYSREFP, SYSREFM)                      |                                                                    |               |      |     |                     |

| V <sub>D</sub>        | Differential input voltage                    |                                                                    | 0.35          | 0.45 | 1.4 | V                   |

| V <sub>(CM_DIG)</sub> | Common-mode voltage for SYSREF <sup>(2)</sup> |                                                                    |               | 1.3  |     | V                   |

|                       | OUTPUTS (SDOUT, PDN <sup>(3)</sup> )          |                                                                    |               |      |     |                     |

| V <sub>OH</sub>       | High-level output voltage                     |                                                                    | DVDD -<br>0.1 | DVDD |     | V                   |

| V <sub>OL</sub>       | Low-level output voltage                      |                                                                    |               |      | 0.1 | V                   |

| DIGITAL O             | UTPUTS (JESD204B Interface: DxP, Dx           | M) <sup>(4)</sup>                                                  |               |      |     |                     |

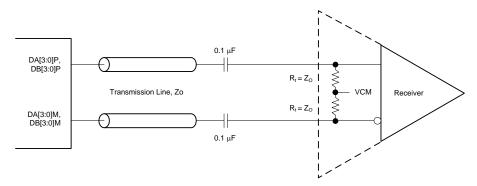

| V <sub>OD</sub>       | Output differential voltage                   | With default swing setting                                         |               | 700  |     | ${\rm mV}_{\rm PP}$ |

| V <sub>oc</sub>       | Output common-mode voltage                    |                                                                    |               | 450  |     | mV                  |

|                       | Transmitter short-circuit current             | Transmitter pins shorted to any voltage between –0.25 V and 1.45 V | -100          |      | 100 | mA                  |

| Z <sub>os</sub>       | Single-ended output impedance                 |                                                                    |               | 50   |     | Ω                   |

|                       | Output capacitance                            | Output capacitance inside the device, from either output to ground |               | 2    |     | pF                  |

<sup>(1)</sup> The RESET, SCLK, SDIN, and PDN pins have a 20-kΩ (typical) internal pulldown resistor to ground, and the SEN pin has a 20-kΩ (typical) pullup resistor to IOVDD.

<sup>(2)</sup> The SYSREFP and SYSREFM pins are internally biased to the 1.3-V common-mode voltage through a 5-kΩ resistor.

<sup>(3)</sup> When functioning as an OVR pin for channel B.

<sup>(4)</sup>  $100-\Omega$  differential termination.

## 7.8 Timing Characteristics

|                                 |                                        |                                                                                           | MIN  | TYP                | MAX                      | UNITS                    |

|---------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------|------|--------------------|--------------------------|--------------------------|

| SAMPLE T                        | IMING                                  |                                                                                           |      |                    | '                        |                          |

|                                 | Aperture delay                         |                                                                                           | 0.75 |                    | 1.6                      | ns                       |

|                                 | Aperture delay matching be             | etween two channels on the same device                                                    |      | ±70                |                          | ps                       |

|                                 | Aperture delay matching be             | etween two devices at the same temperature and supply voltage                             |      | ±270               |                          | ps                       |

|                                 | A : : : : : : : : : : : : : :          | Actual jitter of sampling clock buffer                                                    | 145  |                    |                          | 4                        |

|                                 | Aperture jitter                        | Effective jitter after decimation filtering                                               |      | 102                |                          | f <sub>S</sub> rms       |

| WAKE-UP                         | TIMING                                 |                                                                                           |      |                    |                          |                          |

|                                 | Wake-up time to valid data             | after coming out of global power-down                                                     |      | 150                |                          | μs                       |

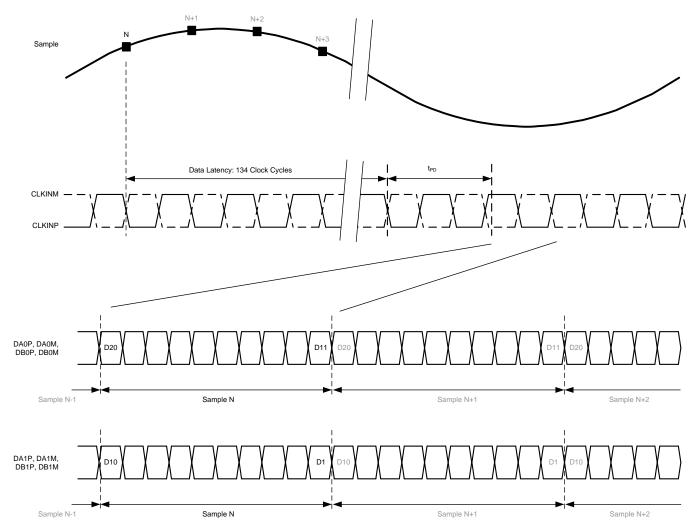

| LATENCY                         |                                        |                                                                                           |      |                    |                          |                          |

|                                 | Data latency <sup>(1)</sup> : ADC samp | ole to digital output                                                                     |      | 134 <sup>(2)</sup> |                          | Input<br>clock<br>cycles |

|                                 | OVR latency: ADC sample                |                                                                                           | 62   |                    | Input<br>clock<br>cycles |                          |

|                                 | FOVR latency: ADC sample               | le to FOVR signal on pin                                                                  | 1    | 8 + 4 ns           |                          | Input<br>clock<br>cycles |

| t <sub>PD</sub>                 | Propagation delay: logic ga            | ates and output buffers delay (does not change with f <sub>S</sub> )                      |      | 4                  |                          | ns                       |

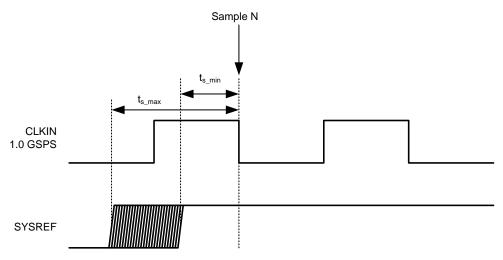

| SYSREF T                        | IMING                                  |                                                                                           |      |                    |                          |                          |

| t <sub>SU_SYSREF</sub>          | Setup time for SYSREF, re              | eferenced to the input clock falling edge                                                 | 300  |                    | 900                      | ps                       |

| t <sub>H_SYSREF</sub>           | Hold time for SYSREF, ref              | erenced to the input clock falling edge                                                   | 100  |                    |                          | ps                       |

| JESD OUT                        | PUT INTERFACE TIMING (                 | CHARACTERISTICS                                                                           |      |                    |                          |                          |

|                                 | Unit interval                          |                                                                                           | 100  |                    | 400                      | ps                       |

|                                 | Serial output data rate                |                                                                                           | 2.5  |                    | 10                       | Gbps                     |

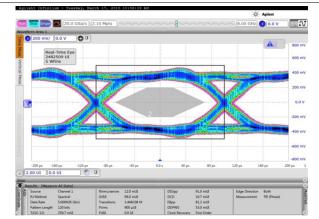

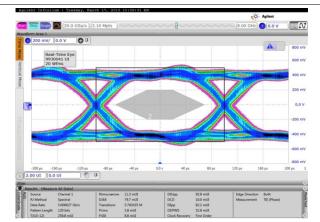

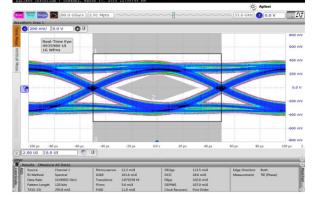

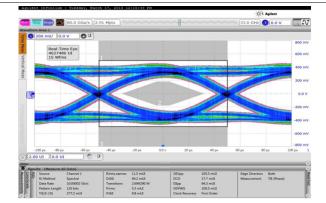

|                                 | Total jitter for BER of 1E-1           | 5 and lane rate = 10 Gbps                                                                 |      | 26                 |                          | ps                       |

|                                 | Random jitter for BER of 1             | E-15 and lane rate = 10 Gbps                                                              |      | 0.75               |                          | ps rms                   |

|                                 | Deterministic jitter for BER           | of 1E-15 and lane rate = 10 Gbps                                                          |      | 12                 |                          | ps, pk-pk                |

| t <sub>R</sub> , t <sub>F</sub> |                                        | ne: rise and fall times are measured from 20% to 80%,<br>n, 2.5 Gbps ≤ bit rate ≤ 10 Gbps |      | 35                 |                          | ps                       |

- (1) Overall latency = data latency + decimation filter delay + t<sub>PDI</sub>.

- (2) Decimation filter latency is not included in this specification.

Figure 1. SYSREF Timing

Figure 2. Sample Timing Requirements

### 7.9 Typical Characteristics

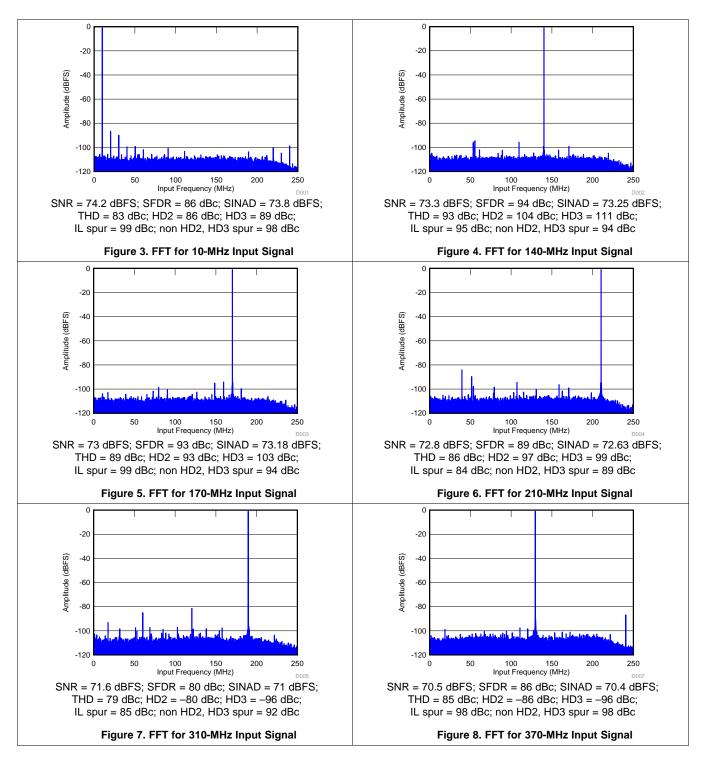

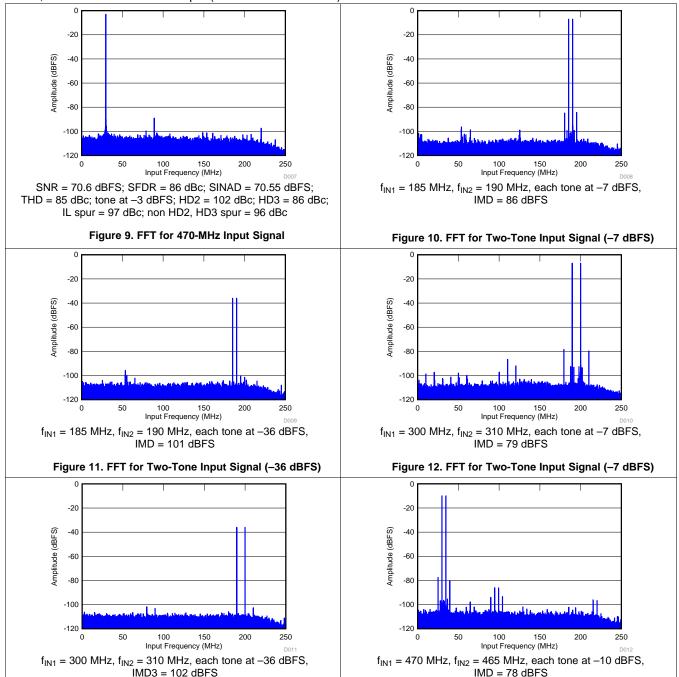

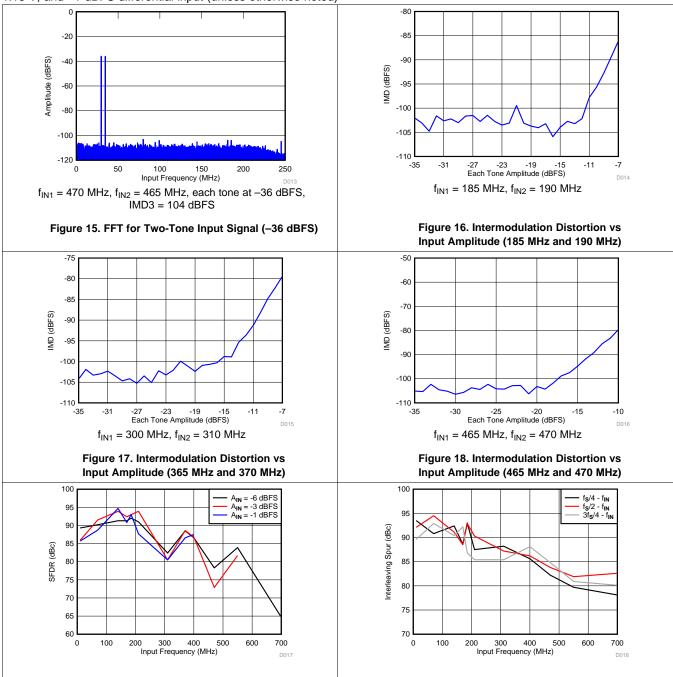

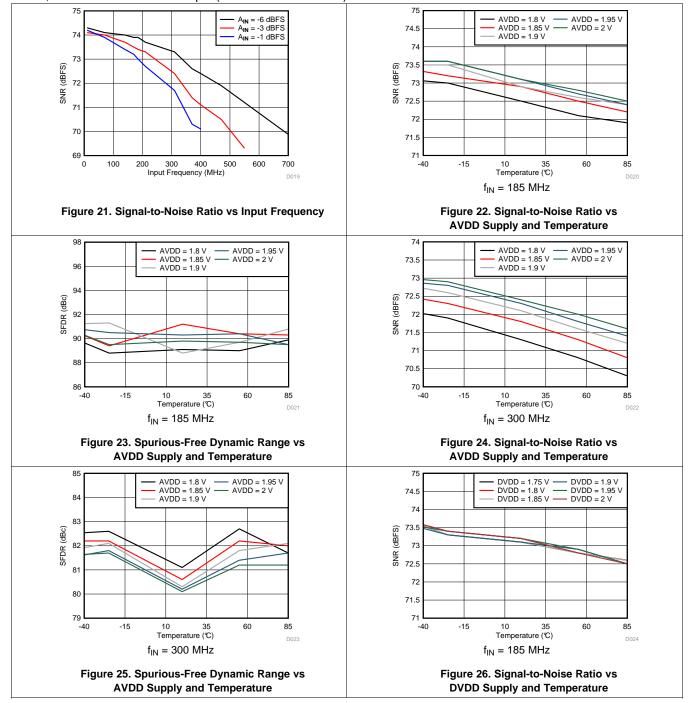

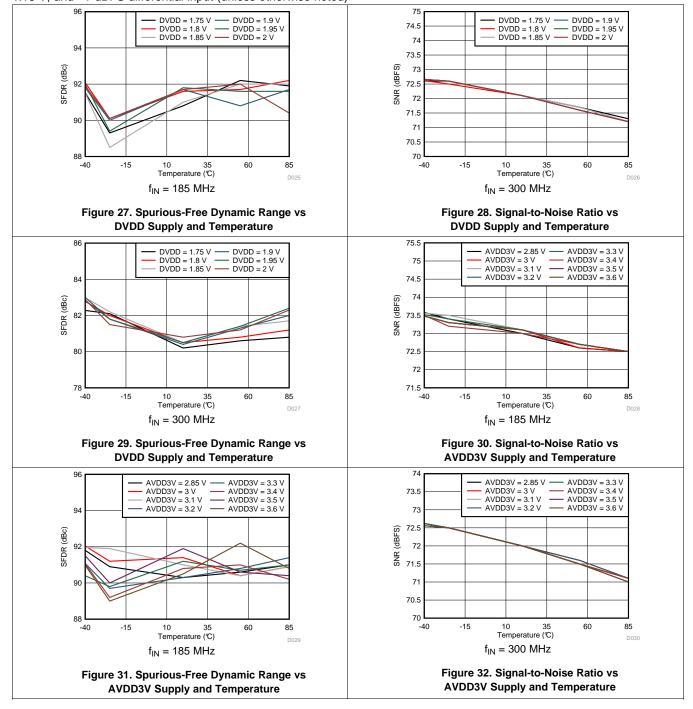

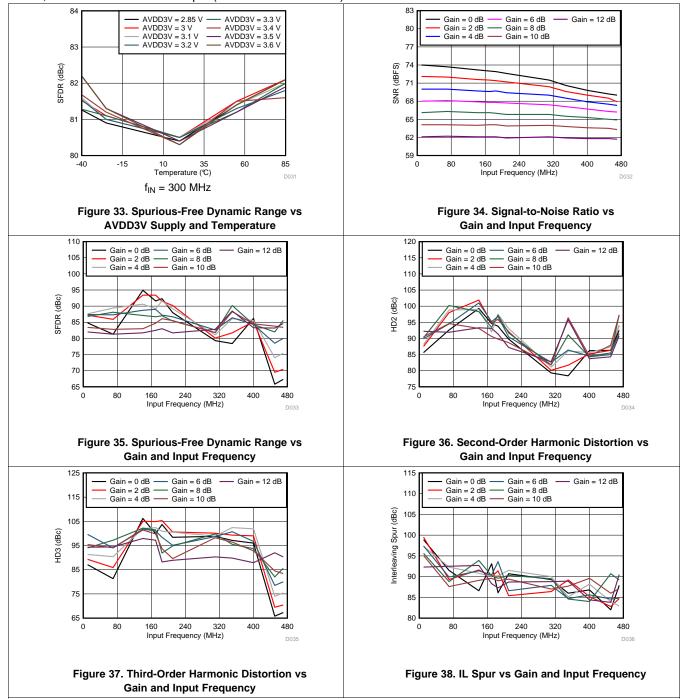

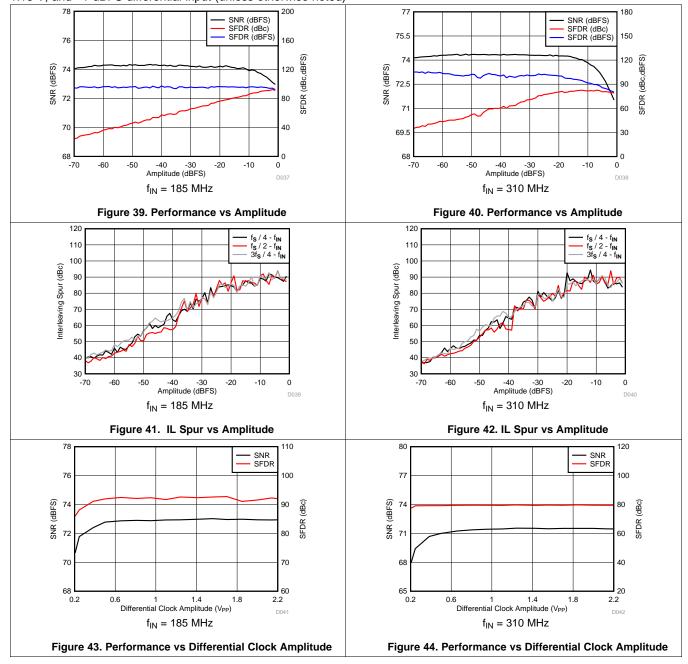

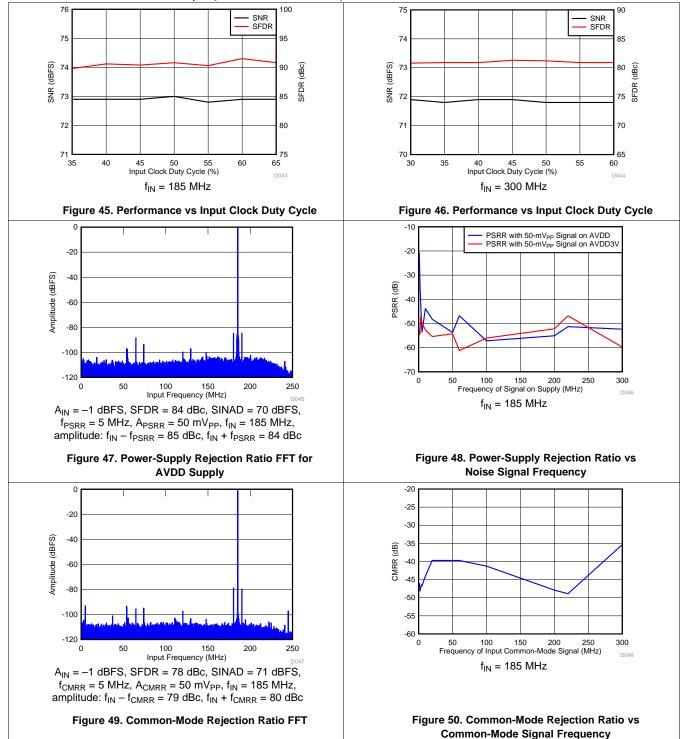

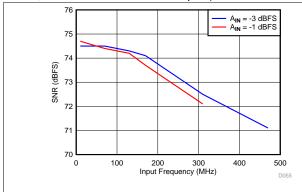

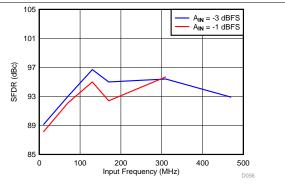

typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, device clock frequency = 1 GSPS, output sampling rate = 500 MSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input (unless otherwise noted)

Figure 13. FFT for Two-Tone Input Signal (-36 dBFS)

Figure 14. FFT for Two-Tone Input Signal (-10 dBFS)

typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, device clock frequency = 1 GSPS, output sampling rate = 500 MSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input (unless otherwise noted)

Figure 19. Spurious-Free Dynamic Range vs

Input Frequency

Figure 20. IL Spur vs Input Frequency

Figure 57. Signal-to-Noise Ratio vs Input Frequency (Output Sample Rate = 400 MSPS)

Figure 58. Spurious-Free Dynamic Range vs Input Frequency (Output Sample Rate = 400 MSPS)

# 8 Detailed Description

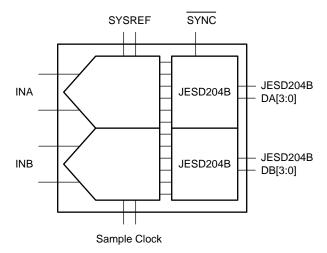

#### 8.1 Overview

The ADS54J69 is a low-power, wide-bandwidth, 16-bit, 500-MSPS, dual-channel, analog-to-digital converter (ADC). The ADS54J69 employs four interleaving ADCs for each channel to achieve a noise floor of –159 dBFS/Hz.

The ADS54J69 uses TI's proprietary interleaving and dither algorithms to achieve a clean spectrum with high spurious-free dynamic range (SFDR). Built-in, half-band, decimate-by-2 filters further enhance the capability of the ADS54J69 to deliver excellent signal-to-noise ratio (SNR) and SFDR over a wide range of frequencies. Analog input buffers isolate the ADC driver from glitch energy generated from sampling process, thereby simplify the driving network on-board.

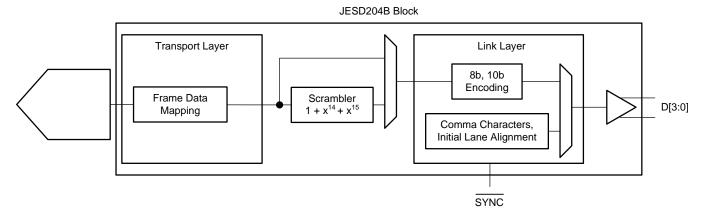

The JESD204B interface reduces the number of interface lines with two-lane and four-lane options, allowing a high system integration density. The JESD204B interface operates in subclass-1, enabling multi-chip synchronization with the SYSREF input.

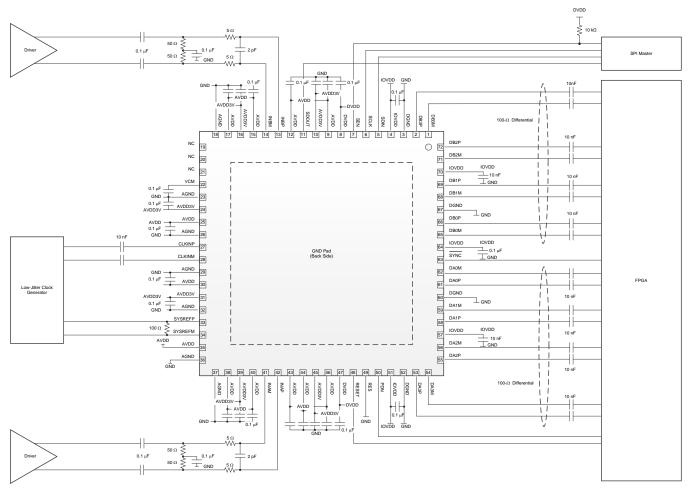

### 8.2 Functional Block Diagram

### 8.3 Feature Description

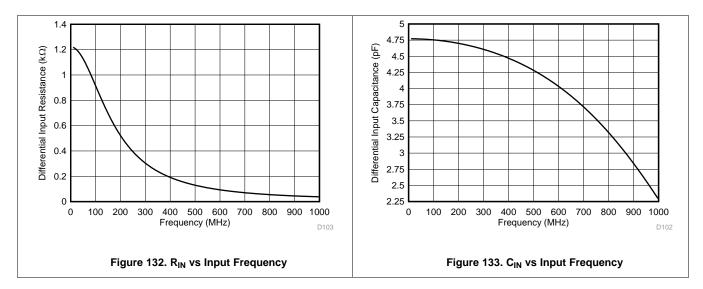

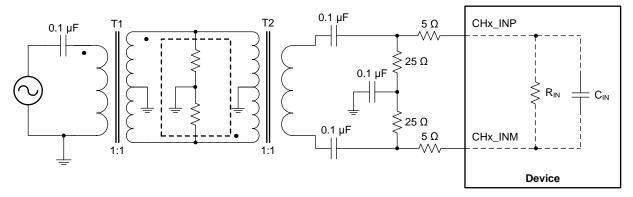

### 8.3.1 Analog Inputs

The ADS54J69 analog signal inputs are designed to be driven differentially. The analog input pins have internal analog buffers that drive the sampling circuit. As a result of the analog buffer, the input pins present a high impedance input across a very wide frequency range to the external driving source that enables great flexibility in the external analog filter design as well as excellent  $50-\Omega$  matching for RF applications. The buffer also helps isolate the external driving circuit from the internal switching currents of the sampling circuit, resulting in a more constant SFDR performance across input frequencies.

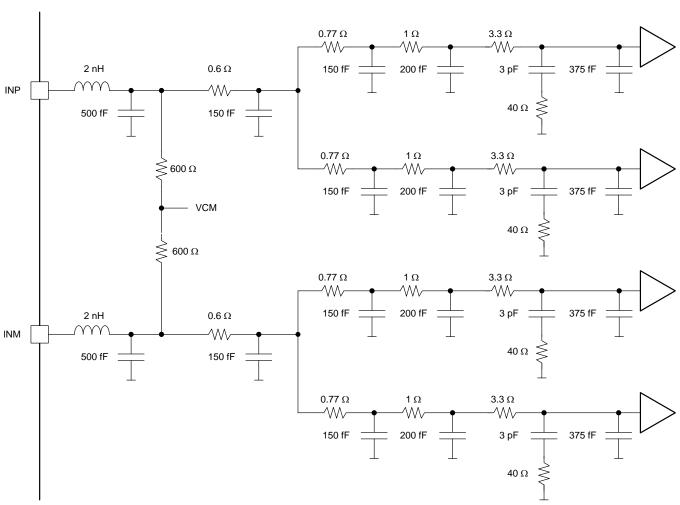

The common-mode voltage of the signal inputs is internally biased to VCM using  $600-\Omega$  resistors, allowing for accoupling of the input drive network. Each input pin (INP, INM) must swing symmetrically between (VCM + 0.475 V) and (VCM - 0.475 V), resulting in a 1.9-V<sub>PP</sub> (default) differential input swing. The input sampling circuit has a 3-dB bandwidth that extends up to 1.2 GHz. An equivalent analog input network diagram is shown in Figure 59.

Figure 59. Analog Input Network

### **Feature Description (continued)**

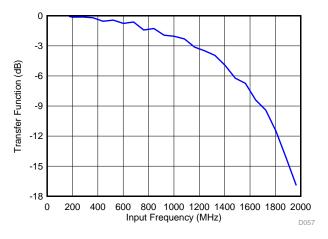

The input bandwidth shown in Figure 60 is measured with respect to a  $50-\Omega$  differential input termination at the ADC input pins.

Figure 60. Transfer Function versus Frequency

#### 8.3.2 DDC Block

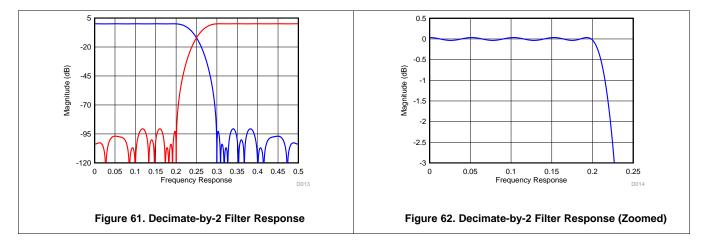

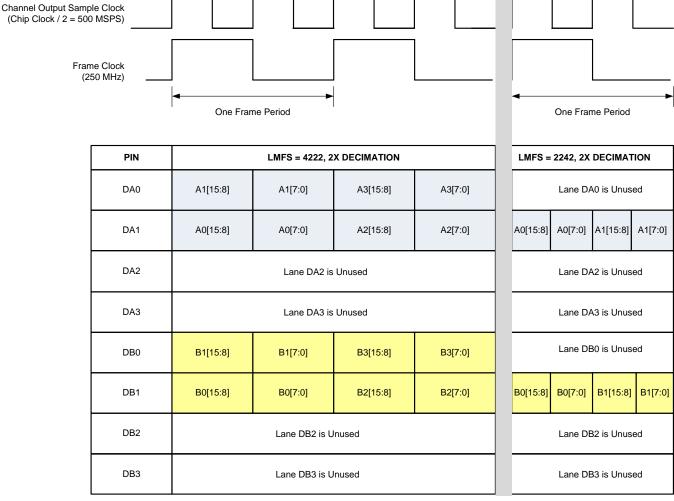

The ADS54J69 has an optional DDC block that can be enabled via an SPI register write. Each ADC channel is followed by a DDC block consisting of a decimate-by-2, half-band, finite impulse response (FIR) filter with low-pass and high-pass options programmable via the SPI interface.

### 8.3.2.1 Decimate-by-2 Filter

This decimation filter has 41 taps. The stop-band attenuation is approximately 90 dB and the pass-band flatness is  $\pm 0.05$  dB. Table 1 shows corner frequencies for the low-pass and high-pass filter options.

Table 1. Corner Frequencies for the Decimate-by-2 Filter

| CORNERS (dB) | LOW PASS                      | HIGH PASS                     |

|--------------|-------------------------------|-------------------------------|

| -0.1         | 0.202 <b>x</b> f <sub>S</sub> | 0.298 <b>x</b> f <sub>S</sub> |

| -0.5         | 0.210 <b>x</b> f <sub>S</sub> | 0.290 <b>x</b> f <sub>S</sub> |

| -1           | 0.215 × f <sub>S</sub>        | 0.285 × f <sub>S</sub>        |

| -3           | 0.227 × f <sub>S</sub>        | 0.273 × f <sub>S</sub>        |

Figure 61 and Figure 62 show the frequency response of the decimate-by-2 filter from dc to f<sub>S</sub> / 2.

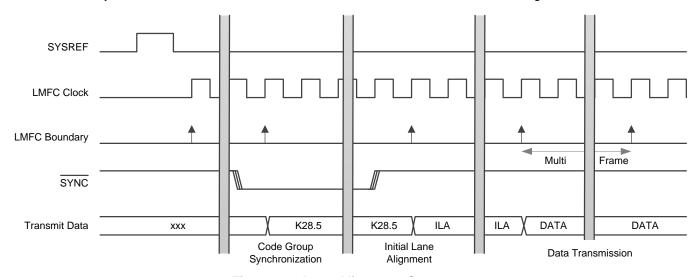

#### 8.3.3 SYSREF Signal

The SYSREF signal is a periodic signal that is sampled by the ADS54J69 device clock and used to align the boundary of the local multi-frame clock inside the data converter. SYSREF is required to be a sub-harmonic of the local multi-frame clock (LMFC) internal timing. To meet this requirement, the timing of SYSREF is dependent on the device clock frequency and the LMFC frequency, as determined by the selected DDC decimation and frames per multi-frame settings. The SYSREF signal is recommended be a low-frequency signal in the range of 1 MHz to 5 MHz in order to reduce coupling to the signal path both on the printed circuit board (PCB) as well as internal in the device.

The external SYSREF signal must be a sub-harmonic of the internal LMFC clock, as shown in Equation 1 and Table 2.

SYSREF = LMFC / 2N

where

(1)

**Table 2. LMFC Clock Frequency**

| LMFS CONFIGURATION | DECIMATION | LMFC CLOCK <sup>(1)(2)</sup> |

|--------------------|------------|------------------------------|

| 4222               | 2X         | (f <sub>S</sub> / 4) / k     |

| 2242               | 2X         | (f <sub>S</sub> / 4) / k     |

- (1) K = Number of frames per multi-frame (JESD digital page 6900h, address 06h, bits 4-0).

- (2)  $f_S = \text{sampling (device) clock frequency.}$

#### 8.3.3.1 SYSREF Not Present (Subclass 0, 2)

A SYSREF pulse is required by the ADS54J69 to reset internal counters. If SYSREF is not present, as can be the case in subclass 0 or 2, this pulse can be done by doing the following register writes shown in Table 3.

Table 3. Internally Pulsing SYSREF Twice Using Register Writes

| ADDRESS (Hex) | DATA (Hex) | COMMENT              |

|---------------|------------|----------------------|

| 0-011h        | 80h        | Set the master page  |

| 0-054h        | 80h        | Enable manual SYSREF |

| 0-053h        | 01h        | Set SYSREF high      |

| 0-053h        | 00h        | Set SYSREF low       |

| 0-053h        | 01h        | Set SYSREF high      |

| 0-053h        | 00h        | Set SYSREF low       |

### 8.3.4 Overrange Indication

The ADS54J69 provides a fast overrange indication that can be presented in the digital output data stream via an SPI configuration. Alternatively, if not used, the SDOUT (pin 11) and PDN (pin 50) pins can be configured via the SPI to output the fast overrange (FOVR) indicator.

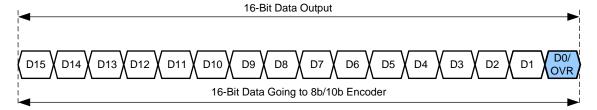

When the FOVR indication is embedded in the output data stream, the FOVR replaces the LSB of the 16-bit data stream going to the 8b/10b encoder, as shown in Figure 63.

Figure 63. Overrange Indication in a Data Stream

#### 8.3.4.1 Fast OVR

The fast OVR is triggered if the input voltage exceeds the programmable overrange threshold and is presented after only 18 clock cycles +  $t_{PD}$  ( $t_{PD}$  of the gates and buffers is approximately 4 ns), thus enabling a quicker reaction to an overrange event.

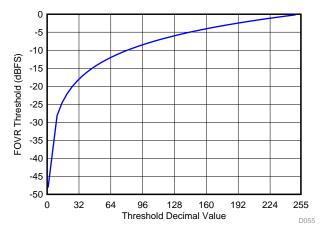

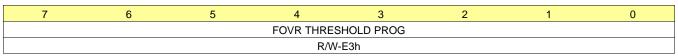

The input voltage level at which the overload is detected is referred to as the *threshold*. The threshold is programmable using the FOVR THRESHOLD bits, as shown in Figure 64. The FOVR is triggered 18 clock cycles + t<sub>PD</sub> (t<sub>PD</sub> of the gates and buffers is approximately 4 ns) after the overload condition occurs.

Figure 64. Programming Fast OVR Thresholds

The input voltage level at which the fast OVR is triggered is defined by Equation 2: Full-Scale × [Decimal Value of the FOVR Threshold Bits] / 255)

(2)

The default threshold is E3h (227d), corresponding to a threshold of -1 dBFS.

In terms of full-scale input, the fast OVR threshold can be calculated as Equation 3: 20log (FOVR Threshold / 255)

(3)

#### 8.3.5 Power-Down Mode

The ADS54J69 provides a highly-configurable power-down mode. Power-down can be enabled by using the PDN pin or via SPI register writes.

A power-down mask can be configured that allows a trade-off between wake-up time and power consumption in power-down mode. Two independent power-down masks can be configured: MASK 1 and MASK 2, as shown in Table 4. See the master page registers in Table 10 for further details.

Table 4. Register Address for Power-Down Modes

| REGISTER<br>ADDRESS | COMMENT |               | REGISTER DATA       |                 |          |             |        |        |   |

|---------------------|---------|---------------|---------------------|-----------------|----------|-------------|--------|--------|---|

| A[7:0] (Hex)        |         | 7             | 6                   | 5               | 4        | 3           | 2      | 1      | 0 |

| MASTER PAG          | E (80h) |               |                     |                 |          |             |        |        |   |

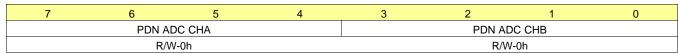

| 20                  | MACKA   |               | PDN ADC CHA         |                 |          |             | PDN AI | OC CHB |   |

| 21                  | MASK 1  | PDN BUF       | FER CHB             | PDN BUFFER CHA  |          | 0           | 0      | 0      | 0 |

| 23                  | MASK 2  |               | PDN AI              | DC CHA          |          | PDN ADC CHB |        |        |   |

| 24                  | WASK 2  | PDN BUF       | FER CHB             | PDN BUF         | FER CHA  | 0           | 0      | 0      | 0 |

| 26                  | CONFIG  | GLOBAL<br>PDN | OVERRIDE<br>PDN PIN | PDN MASK<br>SEL | 0        | 0           | 0      | 0      | 0 |

| 53                  |         | 0             | MASK<br>SYSREF      | 0               | 0        | 0           | 0      | 0      | 0 |

| 55                  |         | 0             | 0                   | 0               | PDN MASK | 0           | 0      | 0      | 0 |

To save power, the device can be put in complete power-down by using the GLOBAL PDN register bit. However, when the JESD link is required to be active during power-down, the ADC and analog buffer can be selectively powered down by using the PDN ADC CHx and PDN BUFFER CHx register bits after enabling the PDN MASK register bit. The PDN MASK SEL register bit can be used to select between MASK 1 or MASK 2. Table 5 shows power consumption for different combinations of the GLOBAL PDN, PDN ADC CHx, and PDN BUFF CHx register bits.

Table 5. Power Consumption in Different Power-Down Settings

| REGISTER BIT                                                          | COMMENT                                                      | I <sub>AVDD3V</sub><br>(mA) | I <sub>AVDD</sub><br>(mA) | I <sub>DVDD</sub><br>(mA) | I <sub>IOVDD</sub><br>(mA) | TOTAL<br>POWER<br>(W) |

|-----------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------|---------------------------|---------------------------|----------------------------|-----------------------|

| Default                                                               | After reset, with a full-scale input signal to both channels | 346                         | 354                       | 188                       | 512                        | 2.66                  |

| GBL PDN = 1                                                           | The device is in a complete power-down state                 | 3                           | 6                         | 21                        | 127                        | 0.2                   |

| GBL PDN = 0,<br>PDN ADC CHx = 1<br>(x = A or B)                       | The ADC of one channel is powered down                       | 284                         | 221                       | 130                       | 461                        | 2.05                  |

| GBL PDN = 0,<br>PDN BUFF CHx = 1<br>(x = A or B)                      | The input buffer of one channel is powered down              | 270                         | 352                       | 188                       | 516                        | 2.43                  |

| GBL PDN = 0,<br>PDN ADC CHx = 1,<br>PDN BUFF CHx = 1<br>(x = A or B)  | The ADC and input buffer of one channel are powered down     | 206                         | 220                       | 129                       | 465                        | 1.82                  |

| GBL PDN = 0,<br>PDN ADC CHx = 1,<br>PDN BUFF CHx = 1<br>(x = A and B) | The ADC and input buffer of both channels are powered down   | 64                          | 84                        | 67                        | 389                        | 0.93                  |

#### 8.4 Device Functional Modes

### 8.4.1 Device Configuration

The ADS54J69 can be configured by using a serial programming interface, as described in the *Serial Interface* section. In addition, the device has one dedicated parallel pin (PDN) for controlling the power-down mode.

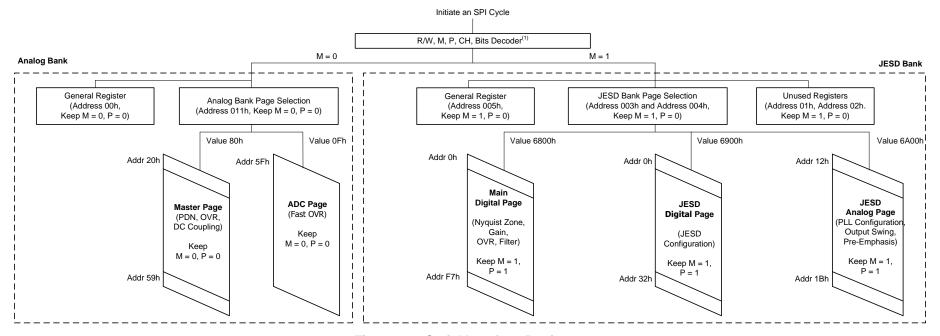

The ADS54J69 supports a 24-bit (16-bit address, 8-bit data) SPI operation and uses paging (see the *Register Maps* section) to access all register bits.

#### 8.4.1.1 Serial Interface

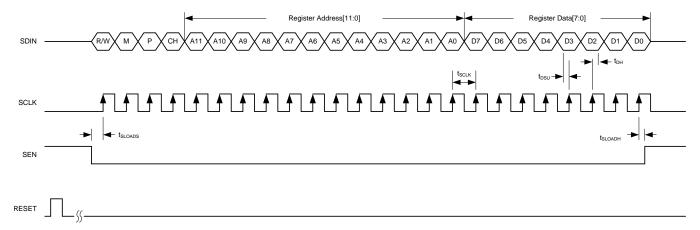

The ADC has a set of internal registers that can be accessed by the serial interface formed by the SEN (serial interface enable), SCLK (serial interface clock), and SDIN (serial interface data) pins, as shown in Figure 65. Legends used in Figure 65 are explained in Table 6. Serially shifting bits into the device is enabled when SEN is low. Serial data on SDIN are latched at every SCLK rising edge when SEN is active (low). The interface can function with SCLK frequencies from 2 MHz down to very low speeds (of a few Hertz) and also with a non-50% SCLK duty cycle.

Figure 65. SPI Timing Diagram

**Table 6. SPI Timing Diagram Legend**

| SPI BITS | DESCRIPTION                                            | BIT SETTINGS                                                                                                     |

|----------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| R/W      | Read/write bit                                         | 0 = SPI write<br>1 = SPI read back                                                                               |

| М        | SPI bank access                                        | 0 = Analog SPI bank (master and ADC pages) 1 = JESD SPI bank (main digital, analog JESD, and digital JESD pages) |

| Р        | JESD page selection bit                                | 0 = Page access<br>1 = Register access                                                                           |

| СН       | SPI access for a specific channel of the JESD SPI bank | 0 = Channel A 1 = Channel B By default, both channels are being addressed.                                       |

| A[11:0]  | SPI address bits                                       | _                                                                                                                |

| D[7:0]   | SPI data bits                                          | _                                                                                                                |

Table 7 shows the timing requirements for the serial interface signals in Figure 65.

**Table 7. SPI Timing Requirements**

|                     |                                                  | MIN  | TYP | MAX | UNIT |

|---------------------|--------------------------------------------------|------|-----|-----|------|

| f <sub>SCLK</sub>   | SCLK frequency (equal to 1 / t <sub>SCLK</sub> ) | > dc |     | 2   | MHz  |

| t <sub>SLOADS</sub> | SEN to SCLK setup time                           | 100  |     |     | ns   |

| t <sub>SLOADH</sub> | SCLK to SEN hold time                            | 100  |     |     | ns   |

| t <sub>DSU</sub>    | SDIN setup time                                  | 100  |     |     | ns   |

| t <sub>DH</sub>     | SDIN hold time                                   | 100  |     |     | ns   |

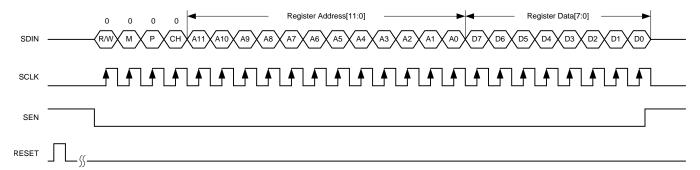

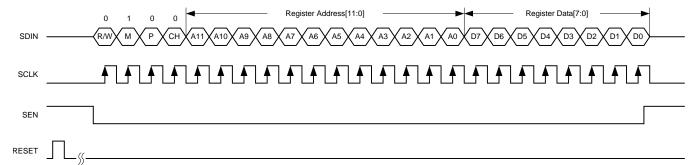

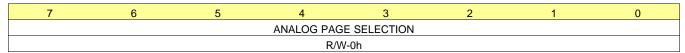

## 8.4.1.2 Serial Register Write: Analog Bank

The analog SPI bank contains two pages (the master and ADC page). The internal register of the ADS54J69 analog SPI bank can be programmed by:

- 1. Driving the SEN pin low.

- 2. Initiating a serial interface cycle specifying the page address of the register whose content must be written.

- Master page: write address 0011h with 80h.

- ADC page: write address 0011h with 0Fh.

- 3. Writing the register content, as shown in Figure 66. When a page is selected, multiple writes into the same page can be done.

Figure 66. Serial Register Write Timing Diagram

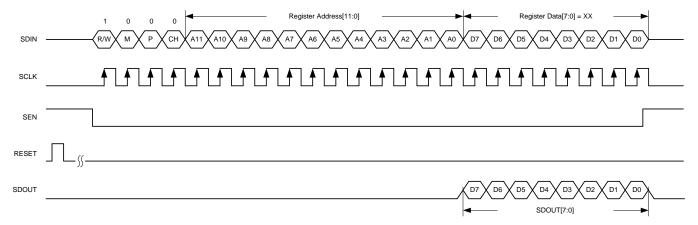

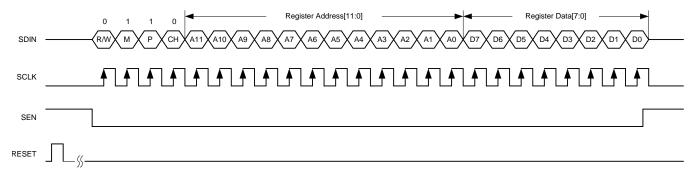

### 8.4.1.3 Serial Register Readout: Analog Bank

The content from one of the two analog banks can be read out by:

- 1. Driving the SEN pin low.

- 2. Selecting the page address of the register whose content must be read.

- Master page: write address 0011h with 80h.

- ADC page: write address 0011h with 0Fh.

- 3. Setting the R/W bit to 1 and writing the address to be read back.

- 4. Reading back the register content on the SDOUT pin, as shown in Figure 67. When a page is selected, multiple read backs from the same page can be done.

Figure 67. Serial Register Read Timing Diagram

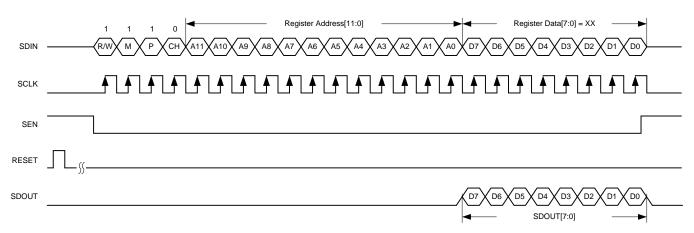

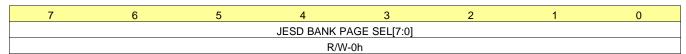

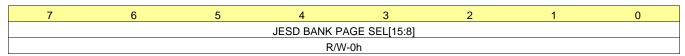

#### 8.4.1.4 JESD Bank SPI Page Selection

The JESD SPI bank contains four pages (main digital, digital, and analog JESD pages). The individual pages can be selected by:

- 1. Driving the SEN pin low.

- 2. Setting the M bit to 1 and specifying the page with two register writes. Note that the P bit must be set to 0, as shown in Figure 68.

- Write address 4003h with 00h (LSB byte of page address).

- Write address 4004h with the MSB byte of the page address.

- For the main digital page: write address 4004h with 68h.

- For the digital JESD page: write address 4004h with 69h.

- For the analog JESD page: write address 4004h with 6Ah.

Figure 68. SPI Page Selection

### 8.4.1.5 Serial Register Write: JESD Bank

The ADS54J69 is a dual-channel device and the JESD204B portion is configured individually for each channel by using the CH bit. Note that the P bit must be set to 1 for register writes.

- 1. Drive the SEN pin low.

- 2. Select the JESD bank page. Note that the M bit = 1 and the P bit = 0.

- Write address 4003h with 00h.

- If separate control for both channels is desired, write address 4005h with 01h.

- For the main digital page: write address 4004h with 68h.

- For the digital JESD page: write address 4004h with 69h.

- For the analog JESD page: write address 4004h with 6Ah.

- 3. Set the M and P bits to 1, select channel A (CH = 0) or channel B (CH = 1), and write the register content as shown in Figure 69. When a page is selected, multiple writes into the same page can be done.

Figure 69. JESD Serial Register Write Timing Diagram

#### 8.4.1.5.1 Individual Channel Programming

By default, register writes are applied to both channels. To enable individual channel writes, write address 4005h with 01h (default is 00h).

#### 8.4.1.6 Serial Register Readout: JESD Bank

The content from one of the pages of the JESD bank can be read out by:

- 1. Driving the SEN pin low.

- 2. Select the JESD bank page. Note that the M bit = 1 and the P bit = 0.

- Write address 4003h with 00h.

- If separate control for both channels is desired, write address 4005h with 01h.

- For the main digital page: write address 4004h with 68h.

- For the digital JESD page: write address 4004h with 69h.

- For the analog JESD page: write address 4004h with 6Ah.