www.ti.com.cn

# 12 位,100 每秒百万次采样 (MSPS), 8 通道模数转换器

查询样品: ADS5295

### 特性

- 最大采样率: 100MSPS

- 针对低功耗而设计:

- 100MSPS 时,每通道功耗为 80mW

- 信噪比 (SNR): 70.6dBFS

- 无杂散动态范围 (SFDR): 10MHz, 100MSP 时为 85dBc

- 串行低压差分信令 (LVDS) 模数转换器 (ADC) 数据 输出:

- 每个通道有一线制或两线制串行 LVDS 输出

- 一线制接口: 高达 80MSPS 采样率

- 两线制接口: 高达 100MSPS 采样率

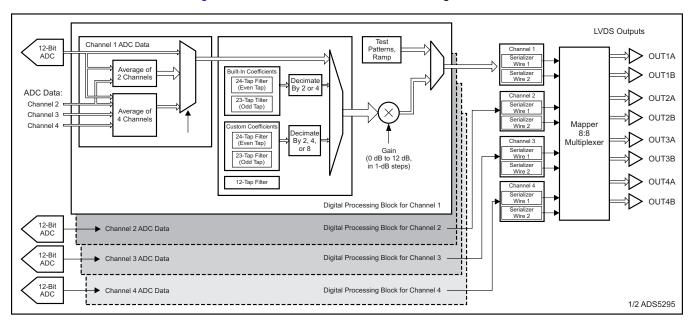

- 数字处理块:

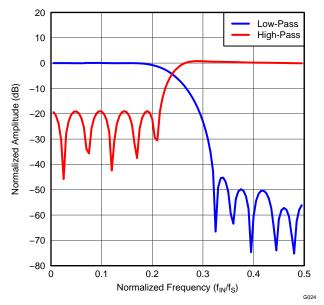

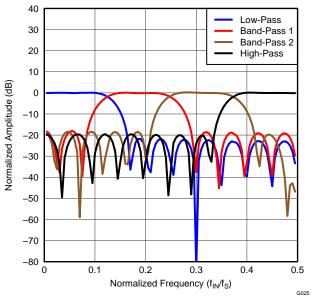

- 可编程有限脉冲响应 (FIR) 抽取滤波器和过采样 以大大减少谐波干扰

- 可编程无限脉冲响应 (IIR) 高通滤波器以大大减 少直流 (DC) 偏移

- 可编程数字增益: 0dB 至 12dB

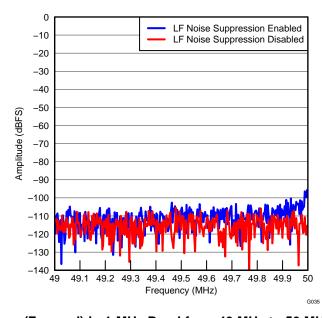

- 低频噪声抑制模式

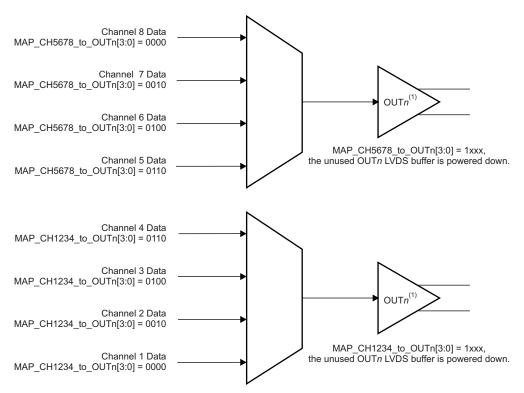

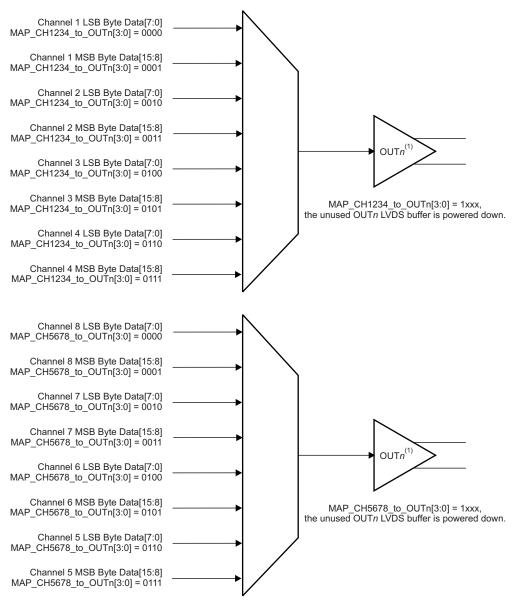

- ADC 输入通道与 LVDS 输出引脚间的可编程映射

- 通道均衡模式

- 多种 LVDS 测试模式以验证 现场可编程栅极阵列 (FPGA) 或接收器的数据捕捉

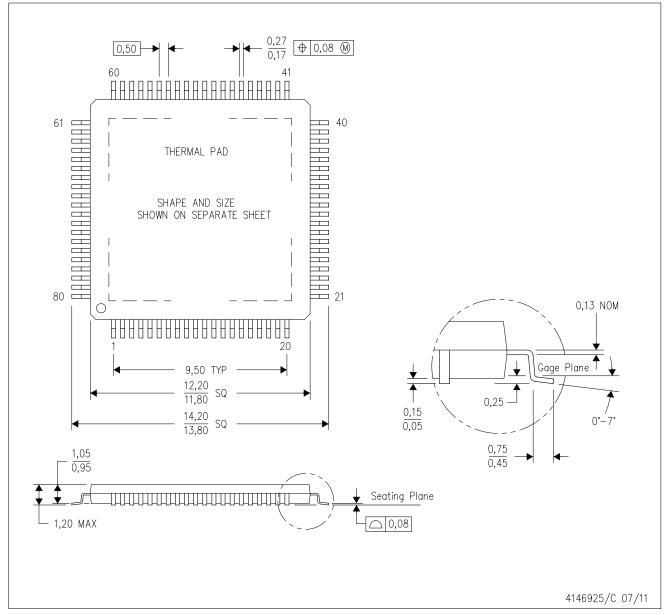

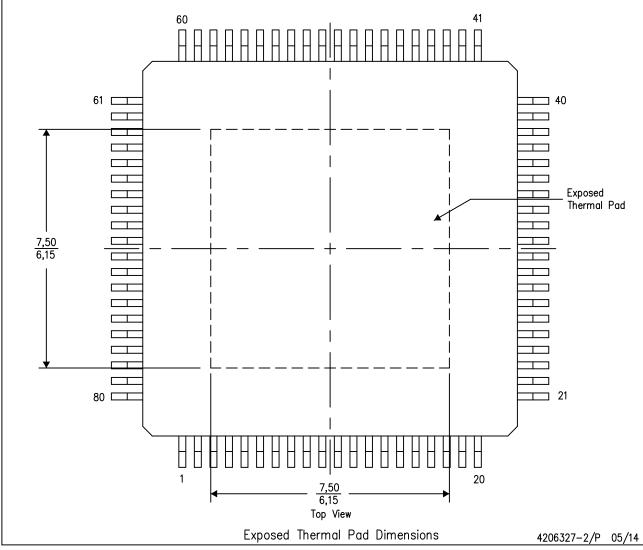

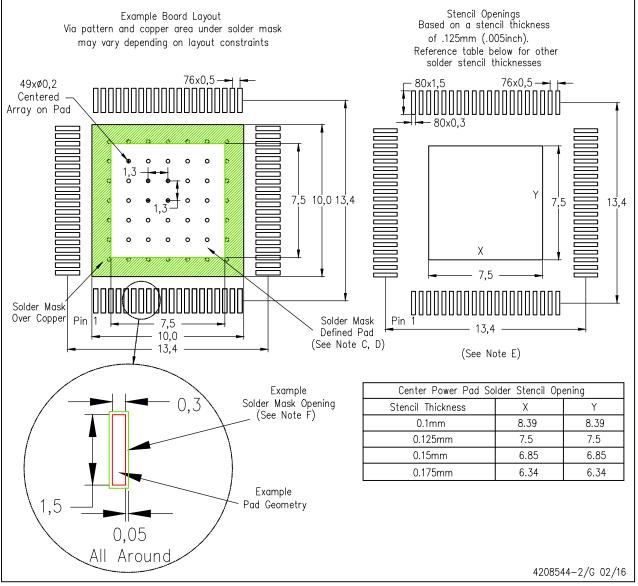

- 封装: 12mm x 12mm 四方扁平封装 (QFP)-80

### 应用范围

- 超声波成像

- 通信应用

- 多通道输出采集

### 说明

ADS5295 是一款低功耗, 12 位, 100MSPS, 8 通道 模数转换器 (ADC)。 低功耗和紧凑封装内集成的多通 道使得此器件适用于极高通道数量数据采集系统。

串行低压差分信令 (LVDS) 输出减少了接口线路的数量 并实现高系统集成。 ADC 数字数据可从每个通道 LVDS 引脚的一线制或两线制接口上输出。 采样高采 样率时,两线制接口有助于保持低串行数据速率,从而 实现基于低成本现场可编程栅极阵列 (FPGA) 的接收器 的使用。

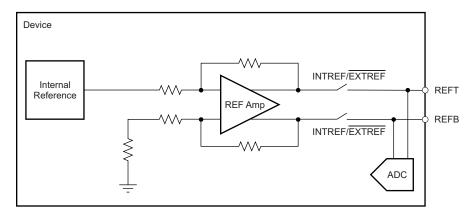

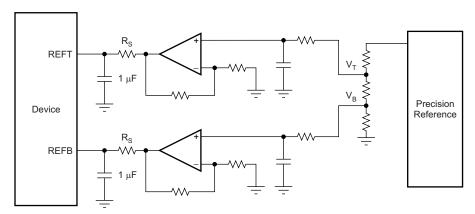

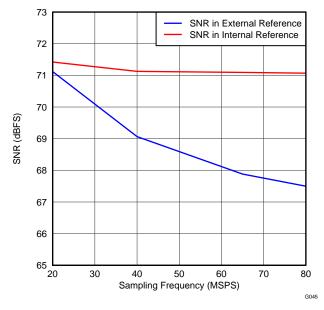

此器件集成了一个已调整的且可与其它器件精确匹配的 内部基准。 最佳性能可在内部基准模式中实现。 然 而, 此器件也可由外部基准驱动。

系统中常用的几种数字功能也包含在器件中。 这些功 能包括一个低频抑制模式、数字滤波选项和可编程映

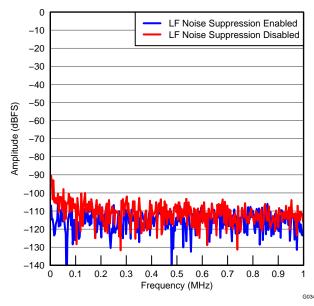

对于低输入频率应用,低频噪声抑制模式可实现低频状 态下的噪声抑制并将 dc 附近 1MHz 波段内的信噪比 (SNR) 提升 3dB。 数字滤波选项包括低通、高通和带 通数字滤波器,以及 dc 偏移消除滤波器。 此器件还提 供 LVDS 输出引脚和模拟输入通道的可编程映射。 对 于无需 12 位 ADC SNR 的应用, ADS5295 可被配置 为具有 10 倍 LVDS 串行的 8 通道, 10 位 ADC 以减 少输出数据速率。

此器件采用 12mm x 12mm QFP-80 封装。 ADS5295 额定运行温度范围为 -40°C 至 +85°C。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE DESIGNATOR | SPECIFIED TEMPERATURE<br>RANGE | PACKAGE MARKING | ORDERING NUMBER |

|---------|--------------|--------------------|--------------------------------|-----------------|-----------------|

| ADS5295 | TQFP-80      | PFP                | -40°C to +85°C                 | ADS5295         | ADS5295IPFP     |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

### ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range, unless otherwise noted.

| P.                                   | ARAMETER                                                                         | VALUE                         | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------|-------------------------------|------|

| Complementary reserve                | AVDD                                                                             | D                             | V    |

| Supply voltage range                 | LVDD                                                                             |                               | V    |

|                                      | AVDD                                                                             | V                             |      |

| Voltage between                      | AVDD to LVDD (when AVDD leads LVDD)                                              | 0 to 2.2                      | V    |

|                                      | LVDD to AVDD (when LVDD leads AVDD)                                              | 0 to 2.2                      | V    |

|                                      | INP, INN                                                                         | -0.3 to min (2.2, AVDD + 0.3) | V    |

| Voltage applied to                   | RESET, SCLK, SDATA, $\overline{\text{CS}}$ , PD, SYNC, CLKP, CLKN <sup>(2)</sup> | -0.3 to min (2.2, AVDD + 0.3) | V    |

|                                      | Digital outputs                                                                  | -0.3 to min (2.2, LVDD + 0.3) | V    |

|                                      | Operating free-air, T <sub>A</sub>                                               | -40 to +85                    | °C   |

| Temperature range                    | Operating junction, T <sub>J</sub>                                               | +105                          | °C   |

|                                      | Storage, T <sub>stg</sub>                                                        | -55 to +150                   | °C   |

| Electrostatic discharge (ESD) rating | Human body model (HBM)                                                           | 2000                          | V    |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### THERMAL INFORMATION

|                  |                                              | ADS5295    |       |

|------------------|----------------------------------------------|------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | PFP (TQFP) | UNITS |

|                  |                                              | 80 PINS    |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 30.8       |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 6.3        |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 8.3        | 9000  |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.2        | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter | 8.2        |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.3        |       |

(1) 有关传统和新的热 度量的更多信息,请参阅IC 封装热度量应用报告, SPRA953。

<sup>(2)</sup> When AVDD is turned off, TI recommends switching off the input clock (or ensuring the voltage on CLKP and CLKN is less than |0.3 V|. This setting prevents the ESD protection diodes at the clock input pins from turning on.

# **RECOMMENDED OPERATING CONDITIONS**

|                 |                                                                                                                   |                         | MIN         | NOM                                                                       | MAX                                   | UNIT     |

|-----------------|-------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|---------------------------------------------------------------------------|---------------------------------------|----------|

| SUPPLIES        |                                                                                                                   |                         | <del></del> |                                                                           | · · · · · · · · · · · · · · · · · · · |          |

| AVDD            | Analog supply voltage                                                                                             |                         | 1.7         | 1.8                                                                       | 1.9                                   | V        |

| LVDD            | Digital supply voltage                                                                                            |                         | 1.7         | 1.8                                                                       | 1.9                                   | V        |

| ANALOG INF      | PUTS                                                                                                              |                         |             |                                                                           |                                       |          |

| V <sub>ID</sub> | Differential input voltage range                                                                                  |                         |             | 2                                                                         |                                       | $V_{PP}$ |

|                 | Input common-mode voltage                                                                                         |                         | VC          | M ± 0.05                                                                  |                                       | V        |

| REFT            | External reference mode                                                                                           |                         |             | 1.45                                                                      |                                       |          |

| REFB            | External reference mode                                                                                           |                         |             | 0.45                                                                      |                                       | V        |

| VCM             | Common-mode voltage output                                                                                        |                         |             | 0.95                                                                      |                                       | V        |

| CLOCK INPU      | ITS (ADCLK Input Sample Rate)                                                                                     |                         |             |                                                                           |                                       |          |

|                 | ADOLK input comple set (4.4.1.)                                                                                   | One-wire LVDS interface | 10          |                                                                           | 80                                    | MSPS     |

|                 | ADCLK input sample rate (1 / t <sub>C</sub> )                                                                     | Two-wire LVDS interface | 10          |                                                                           | 100                                   | MSPS     |

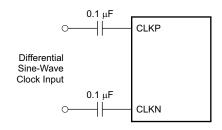

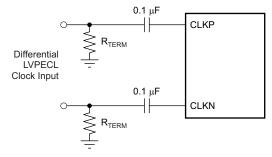

|                 |                                                                                                                   | Sine-wave, ac-coupled   |             | 1.5                                                                       |                                       | $V_{PP}$ |

|                 | Input clock amplitude differential (VCLKP – VCLKN)  Input clock CMOS single-ended (VCLKP)  Input clock duty cycle | LVPECL, ac-coupled      |             | 1.6                                                                       |                                       | $V_{PP}$ |

|                 | (VOLITI VOLITIV)                                                                                                  | LVDS, ac-coupled        |             | 0.7                                                                       |                                       | $V_{PP}$ |

|                 | Input clock CMOS single-ended                                                                                     | V <sub>IL</sub>         |             | < 0.3                                                                     |                                       | V        |

|                 |                                                                                                                   | V <sub>IH</sub>         |             | > 1.5                                                                     |                                       | V        |

|                 | Input clock duty cycle                                                                                            |                         | 35          | 50                                                                        | 65                                    | %        |

| DIGITAL OUT     | TPUTS                                                                                                             |                         | •           |                                                                           | '                                     |          |

|                 | ADCLKP and ADCLKN outputs (L'                                                                                     | VDS), one-wire          | (sampl      | 1x<br>e rate in<br>MSPS)                                                  |                                       | MHz      |

|                 | ADCLKP and ADCLKN outputs (L'                                                                                     | VDS), two-wire          | (sampl      | 0.5x<br>e rate in<br>MSPS)                                                |                                       | MHz      |

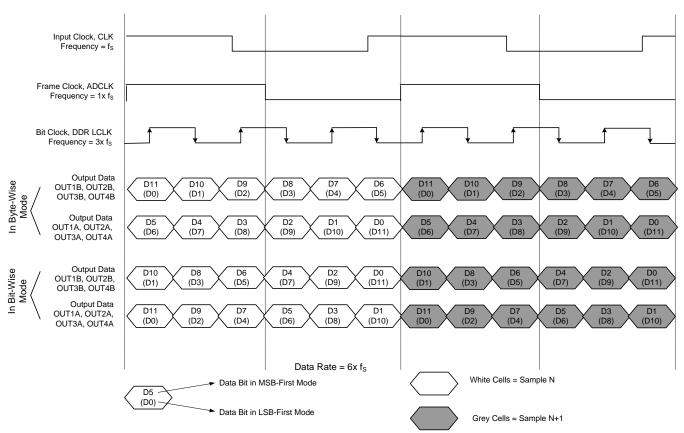

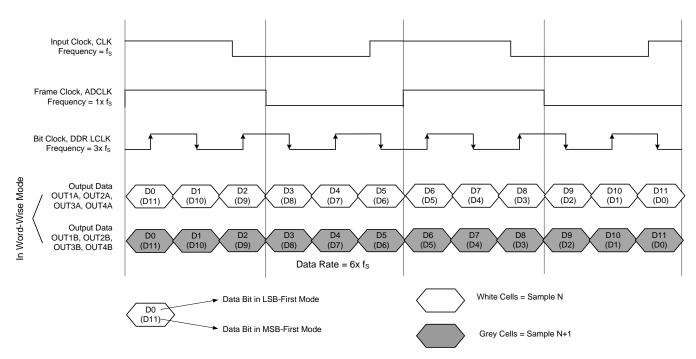

|                 | LCLKP and LCLKN outputs                                                                                           | 12x serialization       | (sampl      | 6x<br>e rate in<br>MSPS)                                                  |                                       | MHz      |

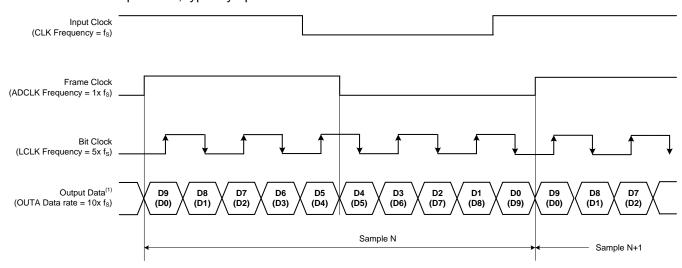

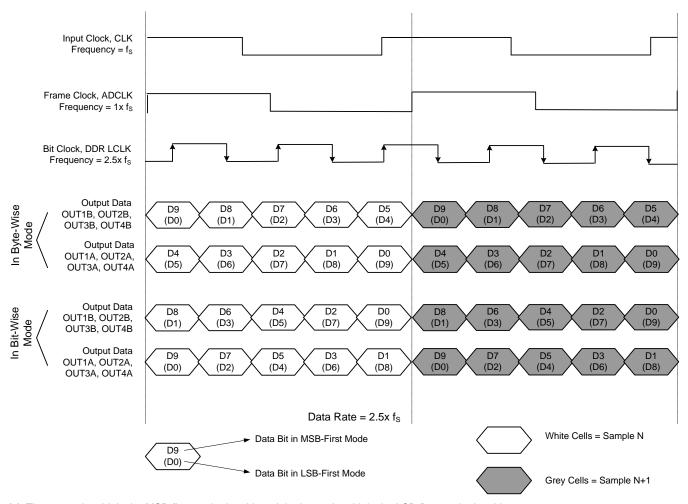

|                 | (LVDS), one-wire                                                                                                  | 10x serialization       | (sampl      | (sample rate in MSPS)  6x (sample rate in MSPS)  5x (sample rate in MSPS) |                                       | MHz      |

|                 | LCLKP and LCLKN outputs                                                                                           | 12x serialization       | (sampl      | 3x<br>e rate in<br>MSPS)                                                  |                                       | MHz      |

|                 | (LVDS), two-wire                                                                                                  | 10x serialization       | (sampl      | 2.5x<br>e rate in<br>MSPS)                                                | 80 100                                | MHz      |

# **ELECTRICAL CHARACTERISTICS: General**

Typical values are at  $T_A$  = +25°C, AVDD = 1.8 V, LVDD = 1.8 V, 50% clock duty cycle, 100 MSPS, two-wire LVDS interface, and -1-dBFS differential analog input, unless otherwise noted.

Minimum and maximum values are across the full temperature range of  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, AVDD = 1.8 V, and LVDD = 1.8 V.

|                    | PARAI                            | METER                                              | TEST CONDITIONS                                                                 | MIN  | TYP    | MAX | UNIT     |

|--------------------|----------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------|------|--------|-----|----------|

| RESOLU             | ITION                            |                                                    |                                                                                 |      |        |     |          |

|                    | Resolution                       |                                                    |                                                                                 |      |        | 12  | Bits     |

| ANALOG             | S INPUTS                         |                                                    |                                                                                 |      |        |     |          |

|                    | Differential input               | voltage range                                      |                                                                                 |      | 2.0    |     | $V_{PP}$ |

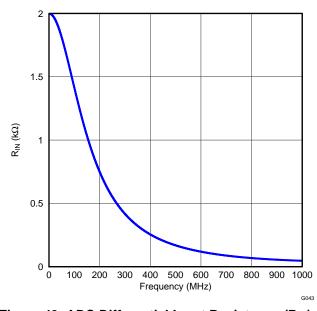

|                    | Differential input               | resistance                                         | At dc                                                                           |      | 2      |     | kΩ       |

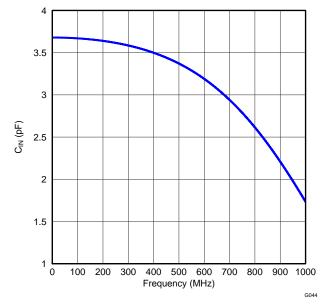

|                    | Differential input               | capacitance                                        | At dc                                                                           |      | 3.7    |     | pF       |

|                    | Analog input ban                 | dwidth                                             |                                                                                 |      | 500    |     | MHz      |

|                    | Analog input com (per input pin) | nmon-mode current                                  |                                                                                 |      | 1      |     | μA/MSPS  |

| VCM                | Common-mode output voltage       |                                                    |                                                                                 |      | 0.95   |     | V        |

|                    | VCM output curre                 | ent capability                                     |                                                                                 |      | 5      |     | mA       |

| DYNAMI             | C ACCURACY                       |                                                    |                                                                                 |      |        |     |          |

| Eo                 | Offset error                     |                                                    |                                                                                 | -20  |        | 20  | mV       |

| E <sub>GREF</sub>  | Gain error                       | Resulting from internal reference inaccuracy alone |                                                                                 | -1.5 |        | 1.5 | %FS      |

| E <sub>GCHAN</sub> |                                  | Of channel itself                                  |                                                                                 |      | 0.5    |     | %FS      |

|                    | E <sub>GCHAN</sub> temperat      | ure coefficient                                    |                                                                                 |      | < 0.01 |     | Δ%FS/°C  |

| POWER              | SUPPLY                           |                                                    |                                                                                 |      |        |     |          |

| IAVDD              | Analog supply cu                 | rrent                                              | 100 MSPS                                                                        |      | 206    | 225 | mA       |

| ILVDD              | Output buffer sup                | oply current                                       | 100 MSPS, two-wire LVDS interface, 350-mV swing with 100-Ω external termination |      | 150    | 163 | mA       |

| AVDD               | Analog power                     |                                                    | 100 MSPS                                                                        |      | 370.8  |     | mW       |

| LVDD               | Digital power                    |                                                    | 100 MSPS, two-wire LVDS interface, 350-mV swing with 100-Ω external termination |      | 270    |     | mW       |

|                    | Total power                      |                                                    | 100 MSPS, two-wire LVDS interface, 350-mV swing with 100-Ω external termination |      | 640.8  |     | mW       |

|                    | Global power-dov                 | wn                                                 |                                                                                 |      |        | 45  | mW       |

|                    | Standby power                    |                                                    |                                                                                 |      | 192    |     | mW       |

# **ELECTRICAL CHARACTERISTICS: Dynamic Performance**

Typical values are at  $T_A$  = +25°C, AVDD = 1.8 V, LVDD = 1.8 V, maximum rated sampling frequency, 50% clock duty cycle, 100 MSPS, two-wire LVDS interface, and -1-dBFS differential analog input, unless otherwise noted. Minimum and maximum values are across the full temperature range of  $T_{MIN}$  = -40°C to  $T_{MAX}$  = +85°C, AVDD = 1.8 V, and

| /D |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

|       | PARAMETER                                          | TEST CONDITIONS                                                                                       | MIN   | TYP   | MAX  | UNIT           |

|-------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|------|----------------|

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 67.5  | 70.6  |      | dBFS           |

| SNR   | Signal-to-noise ratio                              | f <sub>IN</sub> = 30 MHz                                                                              |       | 70.4  |      | dBFS           |

|       |                                                    | f <sub>IN</sub> = 70 MHz                                                                              |       | 69.7  |      | dBFS           |

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 66    | 70.4  |      | dBFS           |

| SINAD | Signal-to-noise and distortion ratio               | f <sub>IN</sub> = 30 MHz                                                                              |       | 70    |      | dBFS           |

|       |                                                    | f <sub>IN</sub> = 70 MHz                                                                              |       | 68.9  |      | dBFS           |

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 72.5  | 86    |      | dBc            |

| SFDR  | Spurious-free dynamic range                        | f <sub>IN</sub> = 30 MHz                                                                              |       | 79    |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 70 MHz                                                                              |       | 76.3  |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 71    | 85    |      | dBc            |

| THD   | Total harmonic distortion                          | f <sub>IN</sub> = 30 MHz                                                                              |       | 78.4  |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 70 MHz                                                                              |       | 75.8  |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 72.5  | 89.5  |      | dBc            |

| HD2   | Second-harmonic distortion                         | f <sub>IN</sub> = 30 MHz                                                                              |       | 89.5  |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 70 MHz                                                                              |       | 89.5  |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 72.5  | 86    |      | dBc            |

| HD3   | Third-harmonic distortion                          | f <sub>IN</sub> = 30 MHz                                                                              |       | 79    |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 70 MHz                                                                              |       | 76.4  |      | dBc            |

|       |                                                    | f <sub>IN</sub> = 5 MHz                                                                               | 75    | 95    |      | dBc            |

|       | Worst spur (other than second and third harmonics) | f <sub>IN</sub> = 30 MHz                                                                              |       | 93    |      | dBc            |

|       | (other than second and time namionies)             | f <sub>IN</sub> = 70 MHz                                                                              |       | 82.3  |      | dBc            |

| IMD   | Two-tone intermodulation distortion                | f <sub>1</sub> = 8 MHz, f <sub>2</sub> = 10 MHz,<br>each tone at –7 dBFS                              |       | 86    |      | dBc            |

|       | Crosstalk                                          | 10-MHz full-scale signal on aggressor channel;<br>5-MHz input signal applied on victim channel        |       | 86    |      | dB             |

|       | Input overload recovery                            | Recovery to within 1% (of full-scale) for 6-dB overload with sine-wave input                          |       | 1     |      | Clock<br>cycle |

| PSRR  | AC power-supply rejection ratio                    | For 50-mV <sub>PP</sub> signal on AVDD supply,<br>up to 10 MHz, no signal applied to analog<br>inputs |       | 60    |      | dB             |

| ENOB  | Effective number of bits                           | f <sub>IN</sub> = 5 MHz                                                                               |       | 11.4  |      | LSBs           |

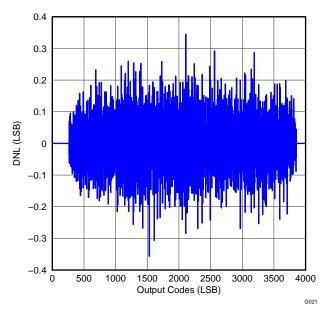

| DNL   | Differential nonlinearity                          | f <sub>IN</sub> = 5 MHz                                                                               | -0.82 | ±0.05 | 0.82 | LSBs           |

| INL   | Integrated nonlinearity                            | f <sub>IN</sub> = 5 MHz                                                                               |       | 0.4   | 1.1  | LSBs           |

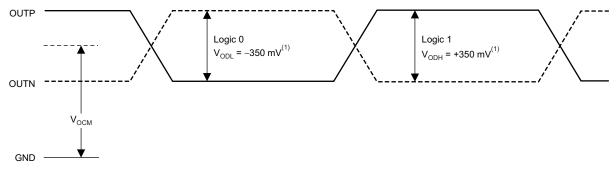

### **DIGITAL CHARACTERISTICS**

The dc specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level '0' or '1'. AVDD = 1.8 V and DRVDD = 1.8 V.

|                  | PARAMET                       | ER                             | TEST CONDITIONS                                    | MIN 7                | YP MA           | X UNIT |  |  |

|------------------|-------------------------------|--------------------------------|----------------------------------------------------|----------------------|-----------------|--------|--|--|

| DIGITA           | AL INPUTS (RESET, SCLK, S     | SDATA, CS, SYNC, PDN)          |                                                    | ,                    | 0.4<br>6<br>0.1 |        |  |  |

| V <sub>IH</sub>  | High-level input voltage      |                                | All pins support 1.8-V and 3.3-V CMOS logic levels | 1.3                  |                 | V      |  |  |

| $V_{IL}$         | Low-level input voltage       |                                | All pins support 1.8-V and 3.3-V CMOS logic levels |                      | 0.              | 4 V    |  |  |

| I <sub>IH</sub>  | High-level input current      | CS, SDATA, SCLK <sup>(1)</sup> | V <sub>HIGH</sub> = 1.8 V                          |                      | 6               | μA     |  |  |

| I <sub>IL</sub>  | Low-level input current       | CS, SDATA, SCLK <sup>(1)</sup> | V <sub>LOW</sub> = 0 V                             |                      | 0.1             | μA     |  |  |

| DIGITA           | AL OUTPUTS (CMOS INTERI       | FACE: SDOUT)                   |                                                    |                      |                 |        |  |  |

| V <sub>OH</sub>  | High-level output voltage     |                                |                                                    | AVDD - 0.1           |                 | V      |  |  |

| V <sub>OL</sub>  | Low-level output voltage      |                                |                                                    |                      | 0.              | 1 V    |  |  |

| DIGITA           | AL OUTPUTS (LVDS INTERF       | ACE: OUT1A_P, OUT1A_N          | to OUT8A_P, OUT8A_N and OUT1B_P, OU                | T1B_N to OUT8B_P, OI | JT8B_N)         |        |  |  |

| V <sub>ODH</sub> | High-level output differentia | al voltage <sup>(2)</sup>      |                                                    | 300                  | 48              | 5 mV   |  |  |

| V <sub>ODL</sub> | Low-level output differentia  | l voltage <sup>(2)</sup>       |                                                    | -485                 | -30             | 0 mV   |  |  |

| V <sub>OCM</sub> | Output common-mode volta      | age                            |                                                    | 0.95                 | 1.3             | 5 V    |  |  |

<sup>(1)</sup>  $\overline{\text{CS}}$ , SDATA, and SCLK have an internal 220-k $\Omega$  pull-down resistor.

<sup>(2)</sup> With an external 100-Ω termination.

# TIMING REQUIREMENTS(1)

Typical values are at +25°C, AVDD = 1.8 V, LVDD = 1.8 V, sampling frequency = 100 MSPS, sine-wave input clock,  $C_{LOAD}$  = 5 pF, and  $R_{LOAD}$  = 100  $\Omega$ , unless otherwise noted.

Minimum and maximum values are across the full temperature range of  $T_{MIN} = -40^{\circ}C$  to  $T_{MAX} = +85^{\circ}C$ , AVDD = 1.8 V, and LVDD = 1.7 V to 1.9 V.

|                      | PARAMETER                   | TEST CONDITIONS                                                                        | MIN  | TYP                                                                    | MAX  | UNIT         |

|----------------------|-----------------------------|----------------------------------------------------------------------------------------|------|------------------------------------------------------------------------|------|--------------|

| t <sub>A</sub>       | Aperture delay              |                                                                                        |      | 4                                                                      |      | ns           |

|                      | Aperture delay matching     | Between any two channels of the same device                                            |      | ±200                                                                   |      | ps           |

|                      | Variation of aperture delay | Between two devices at the same temperature and LVDD supply                            |      | ±1                                                                     |      | ns           |

| tJ                   | Aperture jitter             | Sample uncertainty                                                                     |      | 320                                                                    |      | fs rms       |

|                      |                             | Time to valid data after coming out of standby                                         |      | 5                                                                      |      | μs           |

|                      | Wake-up time                | Time to valid data after coming out of global power-down mode                          | 100  |                                                                        |      | μs           |

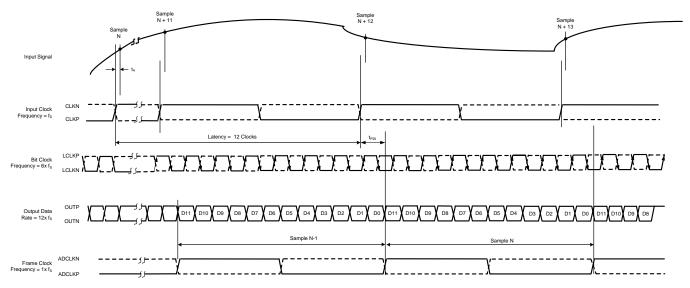

|                      | ADC latency <sup>(2)</sup>  | One-wire LVDS Output interface                                                         |      | 12                                                                     |      | Clock cycles |

|                      | ADC laterity -              | Two-wire LVDS Output interface                                                         |      | 16                                                                     |      | Clock cycles |

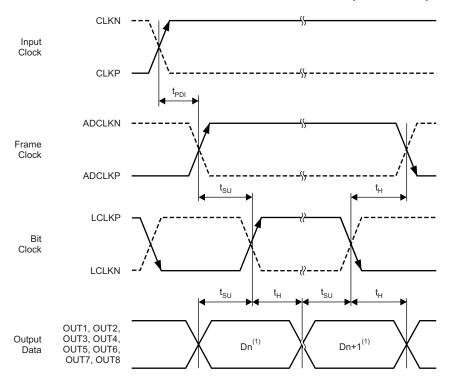

| TWO-WI               | RE, 12x SERIALIZATION       |                                                                                        |      |                                                                        |      |              |

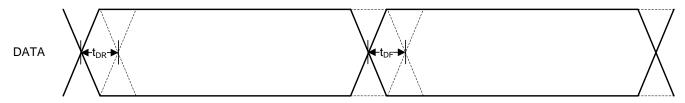

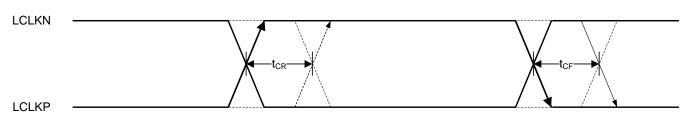

| t <sub>SU</sub>      | Data setup time             | Data valid to zero-crossing of LCLKP                                                   | 0.52 |                                                                        |      | ns           |

| t <sub>H</sub>       | Data hold time              | Zero-crossing of LCLKP to data becoming invalid                                        | 0.62 |                                                                        |      | ns           |

| t <sub>PDI</sub>     | Clock propagation delay     | Input clock rising edge crossover to output clock rising edge crossover                |      | t <sub>PDI</sub> = (11/12)<br>× t <sub>S</sub> +<br>t <sub>DELAY</sub> |      | ns           |

| t <sub>DELAY</sub>   | Delay time                  |                                                                                        | 8.5  | 11                                                                     | 13.5 | ns           |

|                      | LVDS bit clock duty cycle   | Duty cycle of differential clock<br>(LCLKP – LCLKN)                                    |      | 50                                                                     |      | %            |

| ACROSS               | S ALL SERIALIZATION MODES   |                                                                                        |      |                                                                        |      |              |

| t <sub>FALL</sub>    | Data fall time              | Rise time measured from −100 mV to +100 mV,<br>10 MSPS ≤ sampling frequency ≤ 100 MSPS |      | 0.11                                                                   |      | ns           |

| t <sub>RISE</sub>    | Data rise time              | Rise time measured from −100 mV to +100 mV,<br>10 MSPS ≤ sampling frequency ≤ 100 MSPS |      | 0.11                                                                   |      | ns           |

| t <sub>CLKRISE</sub> | Output clock rise time      | Rise time measured from −100 mV to +100 mV,<br>10 MSPS ≤ sampling frequency ≤ 100 MSPS |      | 0.11                                                                   |      | ns           |

| t <sub>CLKFALL</sub> | Output clock fall time      | Rise time measured from −100 mV to +100 mV,<br>10 MSPS ≤ sampling frequency ≤ 100 MSPS |      | 0.11                                                                   |      | ns           |

<sup>(1)</sup> Timing parameters are ensured by design and characterization, but are not tested in production.

<sup>(2)</sup> At higher frequencies, t<sub>PDI</sub> is greater than one clock period and the overall latency = ADC latency + 1.

# Table 1. Two-Wire, 12x Serialization (1)(2)

| SAMPLING         | SETU | P TIME (ns) |     | HOL  | D TIME (ns) |     | Where t <sub>DEL</sub> | 12) × t <sub>S</sub> + t <sub>D</sub><br><sub>AY</sub> is specifi<br>elow, ns | ELAY<br>ed as |

|------------------|------|-------------|-----|------|-------------|-----|------------------------|-------------------------------------------------------------------------------|---------------|

| FREQUENCY (MSPS) | MIN  | TYP         | MAX | MIN  | TYP         | MAX | MIN                    | TYP                                                                           | MAX           |

| 10               | 7.80 |             |     | 8.00 |             |     | 8.5                    | 11                                                                            | 13.5          |

| 30               | 2.40 |             |     | 2.50 |             |     | 8.5                    | 11                                                                            | 13.5          |

| 50               | 1.10 |             |     | 1.60 |             |     | 8.5                    | 11                                                                            | 13.5          |

| 65               | 0.83 |             |     | 1.25 |             |     | 8.5                    | 11                                                                            | 13.5          |

| 80               | 0.60 |             |     | 1.00 |             |     | 8.5                    | 11                                                                            | 13.5          |

| 100              | 0.52 |             |     | 0.62 |             |     | 8.5                    | 11                                                                            | 13.5          |

(1) All the timing specifications are taken with default output clock and data delay settings (0 ps).

# Table 2. One-Wire, 12x Serialization (1)(2)

| SAMPLING         | SETUP TIME (ns) |     |     | HOLD TIME (ns) |     |     | $t_{PDI}$ = (9/12) × $t_{S}$ + $t_{DELAY}$<br>Where $t_{DELAY}$ is specified as below, ns |     |     |

|------------------|-----------------|-----|-----|----------------|-----|-----|-------------------------------------------------------------------------------------------|-----|-----|

| FREQUENCY (MSPS) | MIN             | TYP | MAX | MIN            | TYP | MAX | MIN                                                                                       | TYP | MAX |

| 10               | 3.90            |     |     | 4.00           |     |     | 8                                                                                         | 10  | 12  |

| 30               | 1.00            |     |     | 1.30           |     |     | 8                                                                                         | 10  | 12  |

| 50               | 0.60            |     |     | 0.57           |     |     | 8                                                                                         | 10  | 12  |

| 65               | 0.40            |     |     | 0.34           |     |     | 8                                                                                         | 10  | 12  |

| 80               | 0.22            |     |     | 0.24           |     |     | 8                                                                                         | 10  | 12  |

(1) All the timing specifications are taken with default output clock and data delay settings (0 ps).

# Table 3. Two-Wire, 10x Serialization (1)(2)

| SAMPLING FREQUENCY<br>(MSPS) | SETU | SETUP TIME (ns) |     |      | HOLD TIME (ns) |     |  |  |

|------------------------------|------|-----------------|-----|------|----------------|-----|--|--|

|                              | MIN  | TYP             | MAX | MIN  | TYP            | MAX |  |  |

| 65                           | 1.00 |                 |     | 1.50 |                |     |  |  |

| 80                           | 0.74 |                 |     | 1.20 |                |     |  |  |

| 100                          | 0.44 | ·               |     | 1.00 | ·              |     |  |  |

(1) All the timing specifications are taken with default output clock and data delay settings (0 ps).

### Table 4. One-Wire, 10x Serialization (1)(2)

| SAMPLING FREQUENCY | SETU | P TIME (ns) | HOLI | O TIME (ns) |     |     |

|--------------------|------|-------------|------|-------------|-----|-----|

| (MSPS)             | MIN  | TYP         | MAX  | MIN         | TYP | MAX |

| 65                 | 0.51 |             |      | 0.60        |     |     |

| 80                 | 0.33 |             |      | 0.36        |     |     |

| 100                | 0.17 |             |      | 0.31        |     |     |

(1) All the timing specifications are taken with default output clock and data delay settings (0 ps).

<sup>(2)</sup> Refer to the *Programmable LVDS Output Clock and Data Edges* section in the Application Information for output clock and data delay options.

<sup>(2)</sup> Refer to the Programmable LVDS Output Clock and Data Edges section in the Application Information for output clock and data delay options.

<sup>(2)</sup> Refer to the Programmable LVDS Output Clock and Data Edges section in the Application Information for output clock and data delay options.

<sup>(2)</sup> Refer to the Programmable LVDS Output Clock and Data Edges section in the Application Information for output clock and data delay options.

### PARAMETRIC MEASUREMENT INFORMATION

### **LATENCY TIMING**

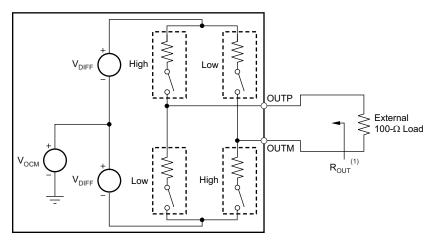

Figure 1 shows a timing diagram of the LVDS output voltage levels.

(1) With an external  $100-\Omega$  termination.

Figure 1. LVDS Output Voltage Levels

Figure 2 shows a latency timing diagram.

Figure 2. Latency Timing Diagram

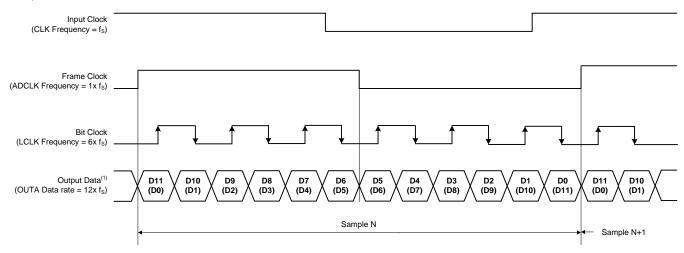

### LVDS OUTPUT TIMING

Figure 3 shows the output timing described in the Timing Requirements table.

# PARAMETRIC MEASUREMENT INFORMATION (continued)

(1) n = 0 to 11.

Figure 3. LVDS Output Timing

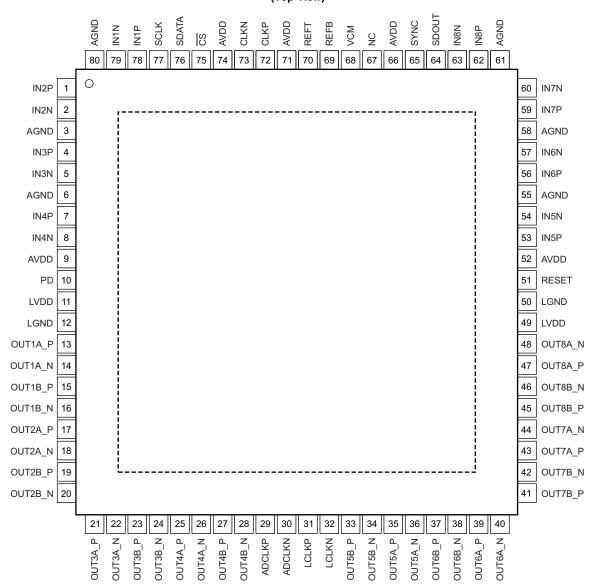

### **PIN DESCRIPTION**

#### PFP PACKAGE TQFP-80 (Top View)

### **PIN DESCRIPTIONS**

| NAME    | NO.                  | FUNCTION <sup>(1)</sup> | DESCRIPTION                                                |

|---------|----------------------|-------------------------|------------------------------------------------------------|

| ADCLKN  | 30                   | DO                      | Differential LVDS frame clock (1x), negative               |

| ADCLKP  | 29                   | DO                      | Differential LVDS frame clock (1x), positive               |

| AGND    | 3, 6, 55, 58, 61, 80 | G                       | Analog ground pin                                          |

| AVDD    | 9, 52, 66, 71, 74    | S                       | Analog supply pin, 1.8 V                                   |

| CLKN    | 73                   | Al                      | Differential clock input, negative                         |

| CLKP    | 72                   | Al                      | For a single-ended clock, tie CLKN to 0 V                  |

| CS      | 75                   |                         | Differential clock input, positive                         |

|         | +                    | DI                      | Serial enable chip select; active low digital input        |

| IN1N    | 79                   | Al                      | Differential analog input for channel 1, negative          |

| IN1P    | 78                   | Al                      | Differential analog input for channel 1, positive          |

| IN2N    | 2                    | Al                      | Differential analog input for channel 2, negative          |

| IN2P    | 1                    | Al                      | Differential analog input for channel 2, positive          |

| IN3N    | 5                    | Al                      | Differential analog input for channel 3, negative          |

| IN3P    | 4                    | Al                      | Differential analog input for channel 3, positive          |

| IN4N    | 8                    | Al                      | Differential analog input for channel 4, negative          |

| IN4P    | 7                    | Al                      | Differential analog input for channel 4, positive          |

| IN5N    | 54                   | Al                      | Differential analog input for channel 5, negative          |

| IN5P    | 53                   | Al                      | Differential analog input for channel 5, positive          |

| IN6N    | 57                   | Al                      | Differential analog input for channel 6, negative          |

| IN6P    | 56                   | Al                      | Differential analog input for channel 6, positive          |

| IN7N    | 60                   | AI                      | Differential analog input for channel 7, negative          |

| IN7P    | 59                   | Al                      | Differential analog input for channel 7, positive          |

| IN8N    | 63                   | Al                      | Differential analog input for channel 8, negative          |

| IN8P    | 62                   | Al                      | Differential analog input for channel 8, positive          |

| LCLKN   | 32                   | DO                      | LVDS differential bit clock output pins (6x), negative     |

| LCLKP   | 31                   | DO                      | LVDS differential bit clock output pins (6x), positive     |

| LGND    | 12, 50               | G                       | Digital ground pin                                         |

| LVDD    | 11, 49               | S                       | Digital and I/O power supply, 1.8 V                        |

| NC      | 67                   | _                       | Do not connect                                             |

| OUT1A_N | 14                   | DO                      | Channel 1 differential LVDS negative data output, one-wire |

| OUT1A_P | 13                   | DO                      | Channel 1 differential LVDS positive data output, one-wire |

| OUT1B_N | 16                   | DO                      | Channel 1 differential LVDS negative data output, two-wire |

| OUT1B_P | 15                   | DO                      | Channel 1 differential LVDS positive data output, two-wire |

| OUT2A_N | 18                   | DO                      | Channel 2 differential LVDS negative data output, one-wire |

| OUT2A_P | 17                   | DO                      | Channel 2 differential LVDS positive data output, one-wire |

| OUT2B_N | 20                   | DO                      | Channel 2 differential LVDS negative data output, two-wire |

| OUT2B_P | 19                   | DO                      | Channel 2 differential LVDS positive data output, two-wire |

| OUT3A_N | 22                   | DO                      | Channel 3 differential LVDS negative data output, one-wire |

| OUT3A_P | 21                   | DO                      | Channel 3 differential LVDS positive data output, one-wire |

| OUT3B_N | 24                   | DO                      | Channel 3 differential LVDS negative data output, two-wire |

| OUT3B_P | 23                   | DO                      | Channel 3 differential LVDS positive data output, two-wire |

| OUT4A_N | 26                   | DO                      | Channel 4 differential LVDS negative data output, one-wire |

| OUT4A_P | 25                   | DO                      | Channel 4 differential LVDS positive data output, one-wire |

| OUT4B_N | 28                   | DO                      | Channel 4 differential LVDS negative data output, two-wire |

| OUT4B_P | 27                   | DO                      | Channel 4 differential LVDS positive data output, two-wire |

| 2014D_I | ۷.                   |                         | J. a for a mororitar Expo positivo data output, two wife   |

<sup>(1)</sup> Pin functionality: AI = analog input; DI = digital input; DO = digital output; G = ground; and S = supply.

# PIN DESCRIPTIONS (continued)

| NAME      | NO. | FUNCTION <sup>(1)</sup> | DESCRIPTION                                                |  |  |  |  |

|-----------|-----|-------------------------|------------------------------------------------------------|--|--|--|--|

| OUT5B_N   | 34  | DO                      | Channel 5 differential LVDS negative data output, two-wire |  |  |  |  |

| OUT5B_P   | 33  | DO                      | Channel 5 differential LVDS positive data output, two-wire |  |  |  |  |

| OUT5A_N   | 36  | DO                      | Channel 5 differential LVDS negative data output, one-wire |  |  |  |  |

| OUT5A_P   | 35  | DO                      | Channel 5 differential LVDS positive data output, one-wire |  |  |  |  |

| OUT6B_N   | 38  | DO                      | Channel 6 differential LVDS negative data output, two-wire |  |  |  |  |

| OUT6B_P   | 37  | DO                      | Channel 6 differential LVDS positive data output, two-wire |  |  |  |  |

| OUT6A_N   | 40  | DO                      | Channel 6 differential LVDS negative data output, one-wire |  |  |  |  |

| OUT6A_P   | 39  | DO                      | Channel 6 differential LVDS positive data output, one-wire |  |  |  |  |

| OUT7B_N   | 42  | DO                      | Channel 7 differential LVDS negative data output, two-wire |  |  |  |  |

| OUT7B_P   | 41  | DO                      | Channel 7 differential LVDS positive data output, two-wire |  |  |  |  |

| OUT7A_N   | 44  | DO                      | Channel 7 differential LVDS negative data output, one-wire |  |  |  |  |

| OUT7A_P   | 43  | DO                      | Channel 7 differential LVDS positive data output, one-wire |  |  |  |  |

| OUT8B_N   | 46  | DO                      | Channel 8 differential LVDS negative data output, two-wire |  |  |  |  |

| OUT8B_P   | 45  | DO                      | Channel 8 differential LVDS positive data output, two-wire |  |  |  |  |

| OUT8A_N   | 48  | DO                      | Channel 8 differential LVDS negative data output, one-wire |  |  |  |  |

| OUT8A_P   | 47  | DO                      | Channel 8 differential LVDS positive data output, one-wire |  |  |  |  |

| PD        | 10  | DI                      | Power-down control input pin                               |  |  |  |  |

| REFB      | 69  | Al                      | Negative reference input/output                            |  |  |  |  |

| REFT      | 70  | Al                      | Positive reference input/output                            |  |  |  |  |

| RESET     | 51  | DI                      | Active high RESET input                                    |  |  |  |  |

| SCLK      | 77  | DI                      | Serial clock input                                         |  |  |  |  |

| SDATA     | 76  | DI                      | Serial data input                                          |  |  |  |  |

| SDOUT     | 64  | DO                      | Serial data output                                         |  |  |  |  |

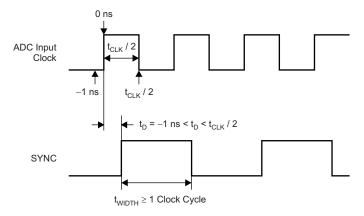

| SYNC      | 65  | DI                      | Synchronization input for reduced output data rate         |  |  |  |  |

| VCM 68 AI |     |                         | Common-mode output pin, 0.95-V output                      |  |  |  |  |

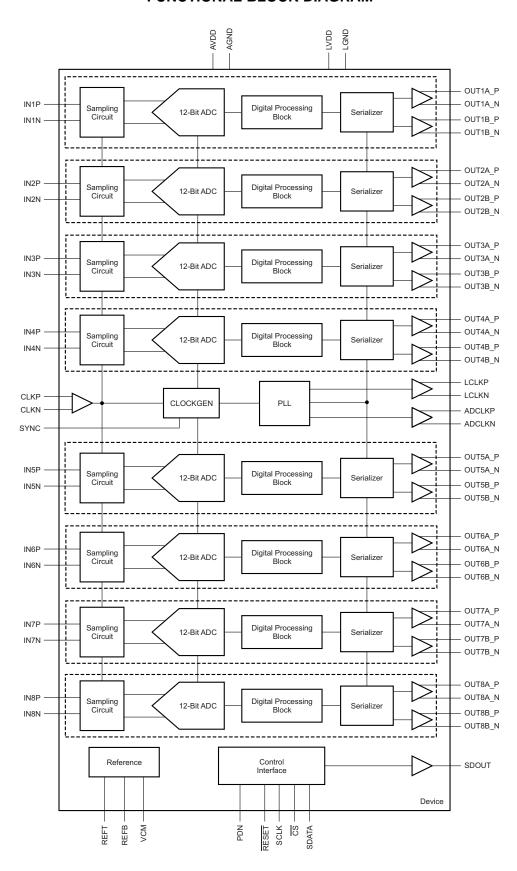

### **FUNCTIONAL BLOCK DIAGRAM**

#### TYPICAL CHARACTERISTICS: General

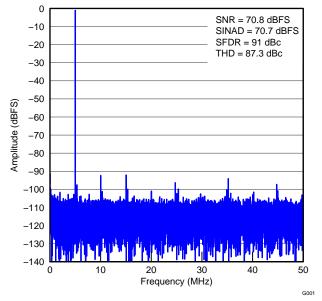

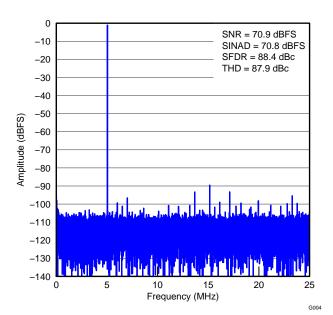

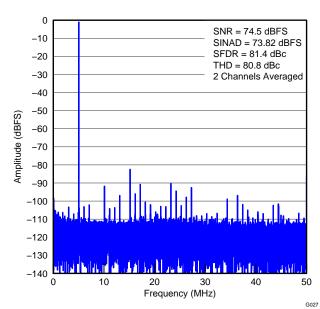

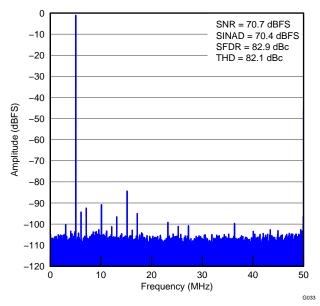

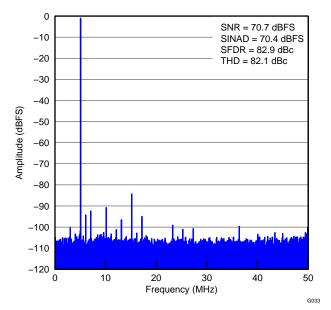

Figure 4. FFT FOR 5-MHz INPUT SIGNAL (Sample Rate = 100 MSPS)

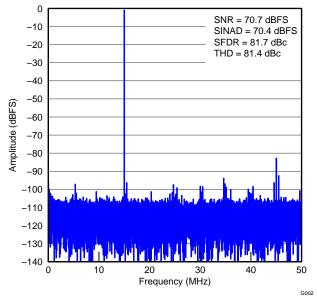

Figure 6. FFT FOR 70-MHz INPUT SIGNAL (Sample Rate = 100 MSPS)

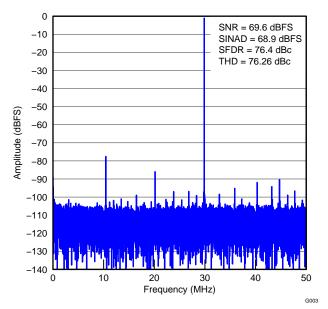

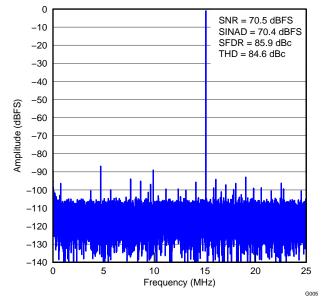

Figure 5. FFT FOR 15-MHz INPUT SIGNAL (Sample Rate = 100 MSPS)

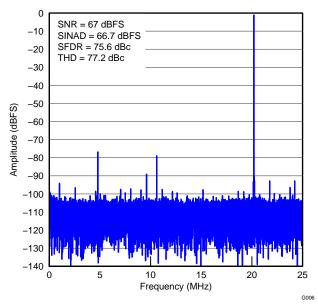

Figure 7. FFT FOR 5-MHz INPUT SIGNAL (Sample Rate = 50 MSPS)

# TEXAS INSTRUMENTS

# **TYPICAL CHARACTERISTICS: General (continued)**

Figure 8. FFT FOR 15-MHz INPUT SIGNAL (Sample Rate = 50 MSPS)

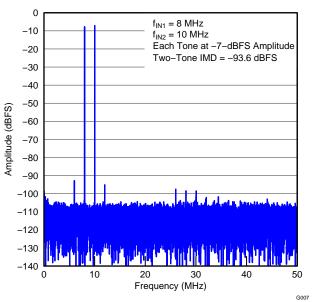

Figure 10. FFT WITH TWO-TONE SIGNAL

Figure 9. FFT FOR 70-MHz INPUT SIGNAL (Sample Rate = 50 MSPS)

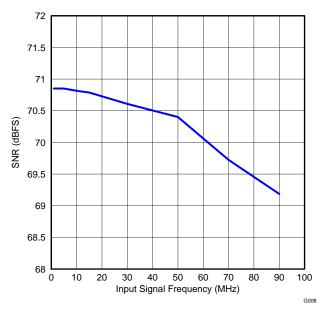

Figure 11. SIGNAL-TO-NOISE RATIO vs INPUT SIGNAL FREQUENCY

# **TYPICAL CHARACTERISTICS: General (continued)**

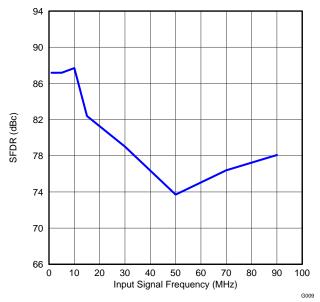

Figure 12. SPURIOUS-FREE DYNAMIC RANGE vs INPUT SIGNAL FREQUENCY

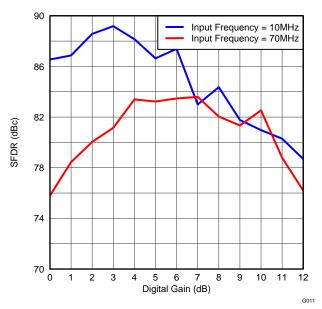

Figure 14. SPURIOUS-FREE DYNAMIC RANGE vs DIGITAL GAIN

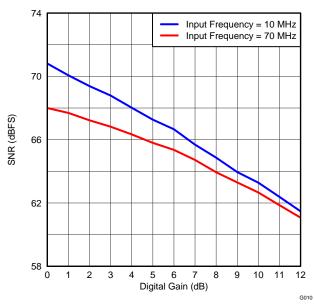

Figure 13. SIGNAL-TO-NOISE RATIO vs DIGITAL GAIN

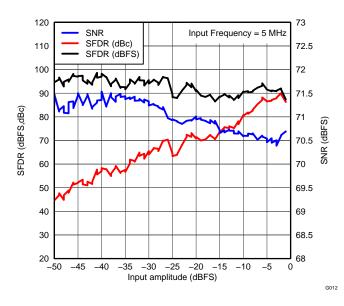

Figure 15. PERFORMANCE vs INPUT AMPLITUDE

AVDD = 1.7 V

NSTRUMENTS

ZHCSAL4 – DECEMBER 2012 www.ti.com.cn

# **TYPICAL CHARACTERISTICS: General (continued)**

Typical values are at  $T_A = +25$ °C, AVDD = 1.8 V, LVDD = 1.8 V, 50% clock duty cycle, 100 MSPS, two-wire LVDS interface, and -1-dBFS differential analog input, unless otherwise noted.

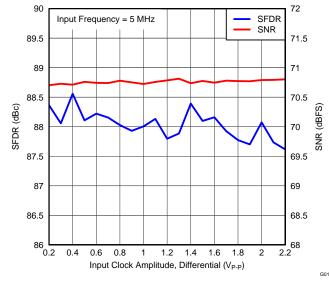

Figure 16. PERFORMANCE vs INPUT CLOCK AMPLITUDE

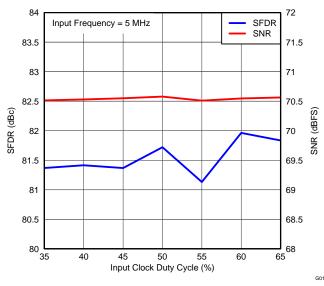

Figure 17. PERFORMANCE vs INPUT CLOCK DUTY CYCLE

Input Frequency = 5 MHz

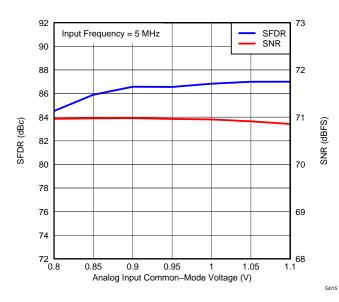

Figure 18. PERFORMANCE vs INPUT COMMON-MODE VOLTAGE

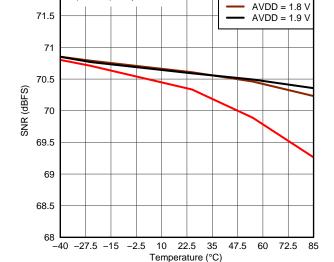

Figure 19. SIGNAL-TO-NOISE RATIO vs AVDD AND TEMPERATURE

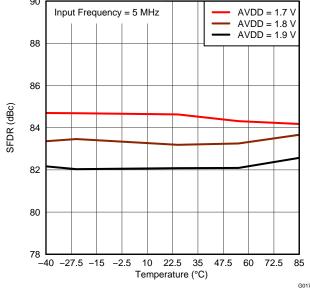

# **TYPICAL CHARACTERISTICS: General (continued)**

Typical values are at  $T_A = +25$ °C, AVDD = 1.8 V, LVDD = 1.8 V, 50% clock duty cycle, 100 MSPS, two-wire LVDS interface, and -1-dBFS differential analog input, unless otherwise noted.

Figure 20. SPURIOUS-FREE DYNAMIC RANGE vs AVDD AND TEMPERATURE

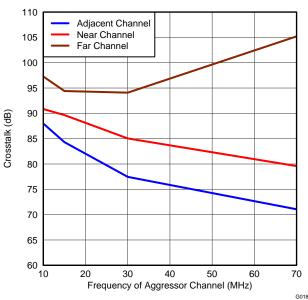

Figure 21. CROSSTALK vs FREQUENCY (1)

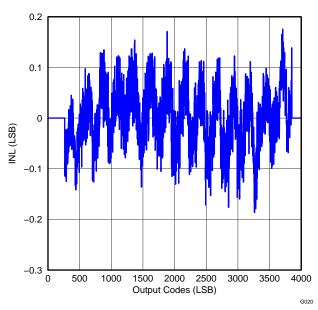

Figure 22. INTEGRAL NONLINEARITY

Figure 23. DIFFERENTIAL NONLINEARITY

(1) Adjacent channel: Neighboring channels on the immediate left and right of the channel of interest. Near channel: Channels on the same side of the package, except the immediate neighbors. Far channel: Channels on the opposite side of the package.

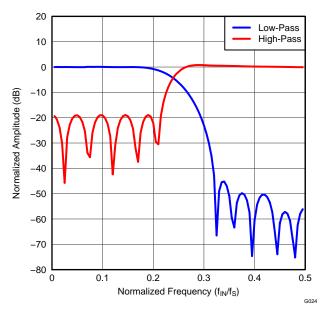

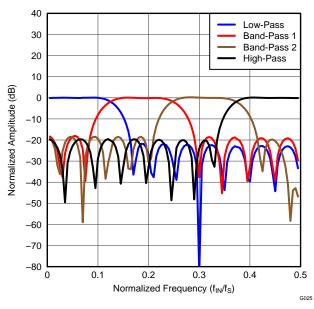

## **TYPICAL CHARACTERISTICS: Digital Processing**

Figure 24. DIGITAL FILTER RESPONSE (Decimate-by-2)

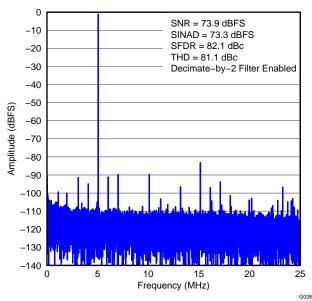

Figure 26. FFT FOR 5-MHz INPUT SIGNAL (Sample Rate = 100 MSPS, Decimation Filter = 2)

Figure 25. DIGITAL FILTER RESPONSE (Decimate-by-4)

Figure 27. FFT FOR 5-MHz INPUT SIGNAL (Sample Rate = 100 MSPS by Averaging Two Channels)

# TYPICAL CHARACTERISTICS: Digital Processing (continued)

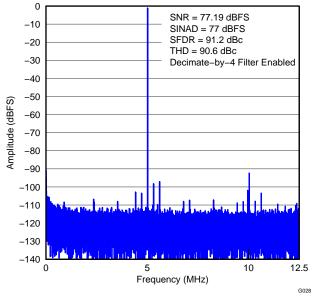

Figure 28. FFT FOR 5-MHz INPUT SIGNAL (Sample Rate = 100 MSPS, Decimation Filter = 4)

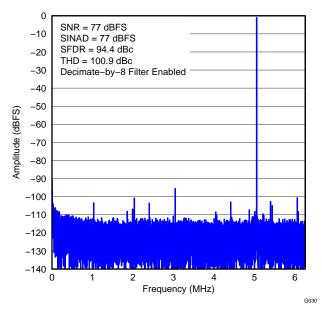

Figure 30. FFT FOR 5-MHz INPUT SIGNAL USING CUSTOM DECIMATION-BY-8 FILTER

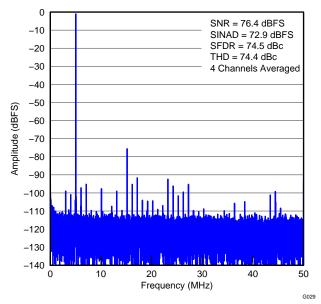

Figure 29. FFT FOR 5-MHz INPUT SIGNAL (Sample Rate = 100 MSPS by Averaging Four Channels)

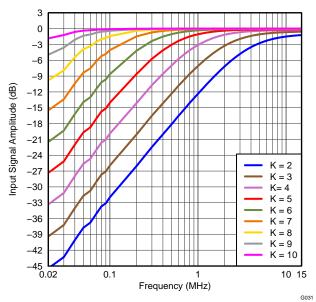

Figure 31. DIGITAL HIGH-PASS FILTER RESPONSE

# **TYPICAL CHARACTERISTICS: Digital Processing (continued)**

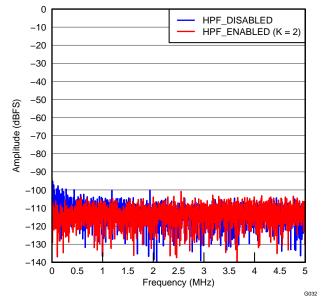

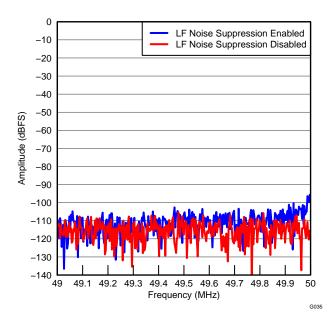

Figure 32. FFT WITH HPF ENABLED AND DISABLED (No Signal)

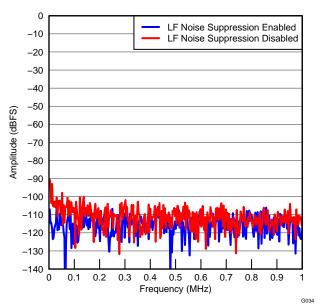

Figure 34. 0-MHz to 1 MHz FFT, 5-MHz INPUT (100-MHz FS with LFNS Enabled)

Figure 33. FULL-BAND FFT, 5-MHz INPUT (100-MHz FS with LFNS Enabled)

Figure 35. 49-MHz to 50-MHz FFT, 5-MHz INPUT (100-MHz FS with LFNS Enabled)

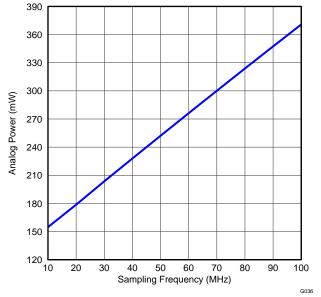

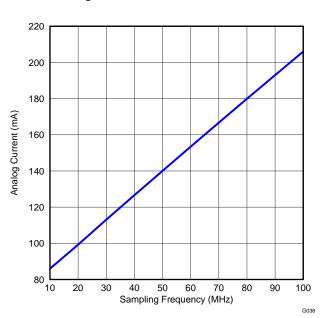

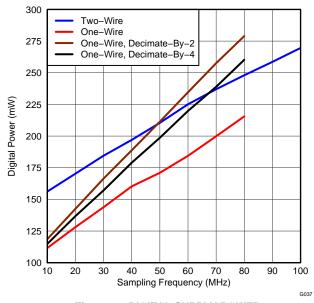

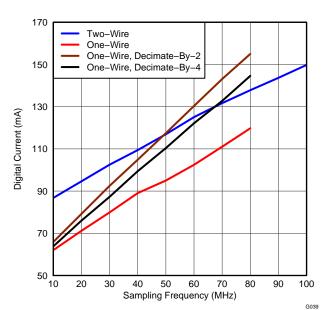

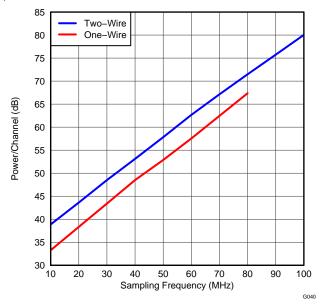

# **TYPICAL CHARACTERISTICS: Power Consumption**

Figure 36. ANALOG SUPPLY POWER

Figure 38. ANALOG SUPPLY CURRENT

Figure 37. DIGITAL SUPPLY POWER

Figure 39. DIGITAL SUPPLY CURRENT

# **TYPICAL CHARACTERISTICS: Power Consumption (continued)**

Figure 40. TOTAL POWER PER CHANNEL

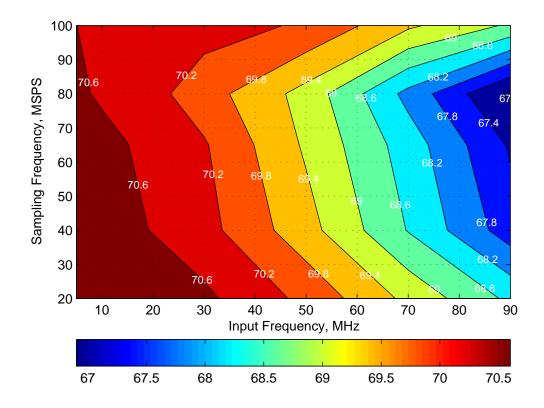

### **TYPICAL CHARACTERISTICS: Contour**

Figure 41. SIGNAL-TO-NOISE RATIO vs INPUT AND SAMPLING FREQUENCIES

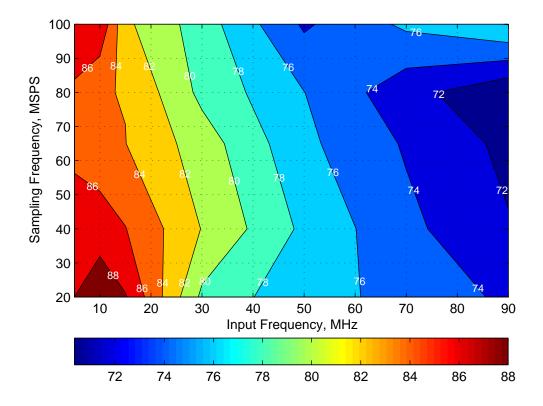

# **TYPICAL CHARACTERISTICS: Contour (continued)**

Figure 42. SPURIOUS-FREE DYNAMIC RANGE vs INPUT AND SAMPLING FREQUENCIES

#### **DEVICE CONFIGURATION**

#### **SERIAL INTERFACE**

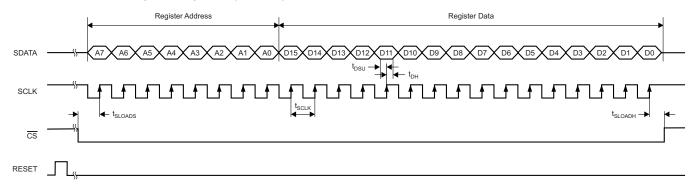

The ADC has a set of internal registers that can be accessed by the serial interface formed by the  $\overline{\text{CS}}$  (serial interface enable), SCLK (serial interface clock), and SDATA (serial interface data) pins. Serially shifting bits into the device is enabled when  $\overline{\text{CS}}$  is low. The serial data (on the SDATA pin) are latched at every SCLK falling edge when  $\overline{\text{CS}}$  is active (low). The serial data are loaded into the register at every 24th SCLK rising edge when  $\overline{\text{CS}}$  is low. When the word length exceeds a multiple of 24 bits, the excess bits are ignored. Data can be loaded in multiples of 24-bit words within a single active  $\overline{\text{CS}}$  pulse. The first eight bits form the register address and the remaining 16 bits are the register data. The interface can function with SCLK frequencies from 15 MHz down to very low speeds (of a few hertz) and also with a non-50% SCLK duty cycle.

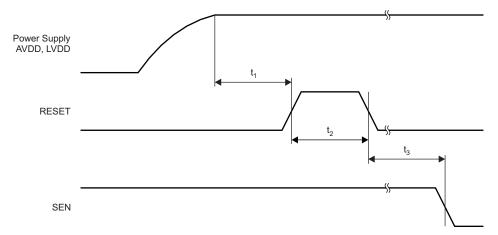

### **Register Initialization**

After power-up, the internal registers must be initialized to default values. This initialization can be accomplished in one of two ways:

- 1. Either through a hardware reset by applying a high pulse on the RESET pin (of widths greater than 10 ns), as shown in Figure 43; or

- 2. By applying a software reset. When using the serial interface, set the RESET bit (register 00h, bit D7) high. This setting initializes the internal registers to default values and then self-resets the RESET bit low. In this case, the RESET pin is kept low (inactive).

Figure 43. Serial Interface Timing Diagram

Table 5. Timing Characteristics for Figure 43<sup>(1)</sup>

|                     | PARAMETER                                        | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>   | SCLK frequency (equal to 1 / t <sub>SCLK</sub> ) | >dc |     | 15  | MHz  |

| t <sub>SLOADS</sub> | CS to SCLK setup time                            | 33  |     |     | ns   |

| t <sub>SLOADH</sub> | SCLK to CS hold time                             | 33  |     |     | ns   |

| t <sub>DSU</sub>    | SDATA setup time                                 | 33  |     |     | ns   |

| t <sub>DH</sub>     | SDATA hold time                                  | 33  |     |     | ns   |

<sup>(1)</sup> Typical values are at T<sub>A</sub> = +25°C, minimum and maximum values are across the full temperature range of T<sub>MIN</sub> = -40°C to T<sub>MAX</sub> = +85°C, unless otherwise noted.

### **Reset Timing**

Figure 44 shows a timing diagram for the reset function.

Figure 44. Reset Timing Diagram

Table 6. Timing Characteristics for Figure 44<sup>(1)(2)</sup>

|                | PARAMETER            | TEST CONDITIONS                                           | MIN | MIN TYP MAX |  |    |  |

|----------------|----------------------|-----------------------------------------------------------|-----|-------------|--|----|--|

| t <sub>1</sub> | Power-on delay       | Delay from AVDD and LVDD power-up to active RESET pulse   | 1   |             |  | ms |  |

| t <sub>2</sub> | Reset pulse width    | Pulse width of active RESET signal                        | 50  |             |  | ns |  |

| t <sub>3</sub> | Register write delay | Delay from RESET disable to $\overline{\text{CS}}$ active |     | 100         |  | ns |  |

<sup>(1)</sup> Typical values are at  $T_A = +25^{\circ}$ C, minimum and maximum values are across the full temperature range of  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = +85^{\circ}$ C, unless otherwise noted.

<sup>(2)</sup> A high pulse on the RESET pin is required when initialization is done via a hardware reset.

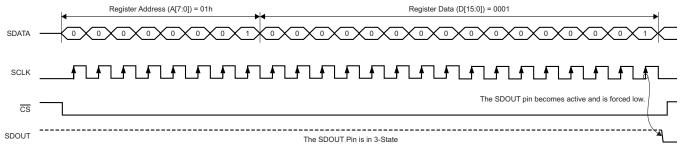

#### **Serial Register Readout**

The device includes a mode where the contents of the internal registers can be read back on the SDOUT pin. This readback mode may be useful as a diagnostic check to verify the serial interface communication between the external controller and the ADC.

By default, the SDOUT pin is in 3-state after a device power-up or reset. When the readout mode is enabled using the READOUT register bit, SDOUT serially outputs the contents of the selected register. The following steps describe how to achieve this functionality:

- 1. Set the READOUT register bit to '1'. This setting puts the device in serial readout mode. This mode prevents any further writes to the internal registers, *except* for at register 01h. Note that the READOUT bit is also located in register 01h. The device can exit readout mode by setting the READOUT bit to '0'. Note that only the contents of register 01h are unable to be read in register readout mode.

- 2. Initiate a serial interface cycle specifying the address of the register (A[7:0]) whose content must be read.

- 3. The device serially outputs the contents (D[15:0]) of the selected register on the SDOUT pin.

- 4. The external controller can latch the contents at the SCLK rising edge.

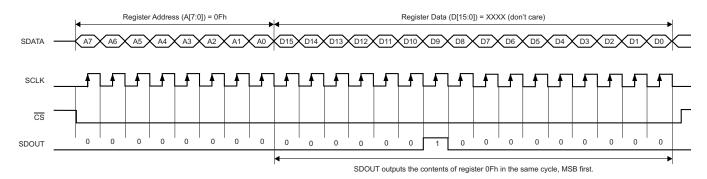

To exit serial readout mode, reset the READOUT register bit to '0', which enables writes to all device registers. At this point, the SDOUT pin is in 3-state. A detailed timing diagram for the serial readout mode is shown in Figure 45.

a) Enable Serial Readout (READOUT = 1)

b) Read contents of register 0Fh. This register is initialized with 0200 (the device was previously put in global power-down).

Figure 45. Serial Readout Timing Diagram

# **SERIAL INTERFACE REGISTERS MAP**

Table 7 lists the ADS5295 registers.

# Table 7. Register Map

| REGISTER         |                                   |                                   |                 |                |             |                 |                  |                               |            |                        |             |                        |          |                        |                   |                        |

|------------------|-----------------------------------|-----------------------------------|-----------------|----------------|-------------|-----------------|------------------|-------------------------------|------------|------------------------|-------------|------------------------|----------|------------------------|-------------------|------------------------|

| ADDRESS<br>(Hex) | D15                               | D14                               | D13             | D12            | D11         | D10             | D9               | D8                            | D7         | D6                     | D5          | D4                     | D3       | D2                     | D1                | D0                     |

| 00               | 0                                 | 0                                 | 0               | 0              | 0           | 0               | 0                | 0                             | 0          | 0                      | 0           | 0                      | 0        | 0                      | 0                 | RST                    |

| 01               | 0                                 | 0                                 | 0               | 0              | 0           | 0               | 0                | 0                             | 0          | 0                      | 0           | EN_HIGH_<br>ADDRS      | 0        | 0                      | 0                 | EN_<br>READOUT         |

| 0A               |                                   |                                   |                 |                | ,           |                 |                  | RAMP_PAT_F                    | RESET_VAL  | •                      | •           | ·                      | •        | •                      | ·                 | •                      |

| 0F               | 0                                 | 0                                 | 0               | 0              | 0           | PDN_PIN_<br>CFG | PDN_<br>COMPLETE | PDN_<br>E PARTIAL PDN_CH[8:1] |            |                        |             |                        |          |                        |                   |                        |

| 14               | 0                                 | 0                                 | 0               | 0              | 0           | 0               | 0                | 0                             |            |                        |             | LFNS_                  | CH[8:1]  |                        |                   |                        |

| 1C               | 0                                 | EN_FRAME<br>_PAT                  | 0               | 0              |             |                 |                  |                               |            | ADCLKO                 | OUT[11:0]   |                        |          |                        |                   |                        |

| 23               |                                   |                                   |                 |                |             |                 |                  | PRBS_SE                       | ED[15:0]   |                        |             |                        |          |                        |                   |                        |

| 24               |                                   |                                   | PI              | RBS_SEED[22:   | 16]         |                 |                  | 0                             |            |                        |             | INVERT                 | _CH[8:1] |                        |                   |                        |

| 25               | TP_HARD_<br>SYNC                  | PRBS_<br>SEED_<br>FROM_REG        | PRBS_<br>MODE_2 | PRBS_<br>TP_EN | 0           | 0               | 0                | TP_SOFT_<br>SYNC              | 0          | -                      | TEST_PATT[2 | :0]                    | BITS_CUS | TOM2[11:10]            | BITS_CUS          | ΓΟM1[11:10]            |

| 26               |                                   |                                   |                 |                | BITS_CU     | STOM1[9:0]      | 1                |                               |            |                        | 0           | 0                      | 0        | 0                      | 0                 | 0                      |

| 27               |                                   |                                   |                 |                | BITS_CU     | STOM2[9:0]      |                  |                               |            |                        | 0           | 0                      | 0        | 0                      | 0                 | 0                      |

| 28               | EN_WORD<br>_BIT_WISE              | 0                                 | 0               | 0              | 0           | 0               | 0                | EN_BIT<br>_WISE               |            | EN_WORDWISE_BY_CH[7:0] |             |                        |          |                        |                   |                        |

| 29               | 0                                 | 0                                 | 0               | 0              | 0           | 0               | 0                | 0                             | 0          | 0                      | 0           | 0                      | 0        | 0                      | EN_DIG_<br>FILTER | EN_<br>CHANNEL_<br>AVG |

| 2A               |                                   | GAIN_C                            | CH4[3:0]        |                |             | GAIN_           | CH3[3:0]         |                               |            | GAIN_0                 | CH2[3:0]    |                        |          | GAIN_0                 | CH1[3:0]          |                        |

| 2B               |                                   | GAIN_C                            | CH5[3:0]        |                |             | GAIN_           | CH6[3:0]         |                               |            |                        |             |                        | CH8[3:0] |                        |                   |                        |

| 2C               | 0                                 | 0                                 | 0               | 0              | 0           | AVG_C           | OUT4[1:0]        | 0                             | AVG_O      | UT3[1:0]               | 0           | AVG_O                  | UT2[1:0] | 0                      | AVG_C             | UT1[1:0]               |

| 2D               | 0                                 | 0                                 | 0               | 0              | 0           | AVG_C           | UT8[1:0]         | 0                             | AVG_O      | UT7[1:0]               | 0           | AVG_O                  | UT6[1:0] | 0                      | AVG_C             | UT5[1:0]               |

| 2E               | 0                                 | HPF_EN_<br>CH1                    |                 | HPF_CORN       | ER_CH1[3:0] |                 | FILT             | ER_TYPE_CH1                   | [2:0]      |                        | DEC_RATE_C  | H1                     | 0        | SEL_ODD_<br>TAP_CH1    | 0                 | USE_<br>FILTER_<br>CH1 |

| 2F               | 0                                 | HPF_EN_<br>CH2                    |                 | HPF_CORN       | ER_CH2[3:0] |                 | FILT             | ER_TYPE_CH2                   | [2:0]      | С                      | DEC_RATE_C  | H2                     | 0        | SEL_ODD_<br>TAP_CH2    | 0                 | USE_<br>FILTER_<br>CH2 |

| 30               | 0                                 | HPF_EN_<br>CH3                    |                 | HPF_CORN       | ER_CH3[3:0] |                 | FILT             | ER_TYPE_CH3                   | [2:0]      | DEC_RATE_CH3 0         |             | SEL_ODD_<br>TAP_CH3    | 0        | USE_<br>FILTER_<br>CH3 |                   |                        |

| 31               | 0 HPF_EN_ HPF_CORNER_CH4[3:0]     |                                   | FILT            | ER_TYPE_CH4    | [2:0]       | Г               | DEC_RATE_C       | H4                            | 0          | SEL_ODD_<br>TAP_CH4    | 0           | USE_<br>FILTER_<br>CH4 |          |                        |                   |                        |

| 32               | 0                                 | 0 HPF_EN_ CH5 HPF_CORNER_CH5[3:0] |                 |                | FILT        | ER_TYPE_CH5     | [2:0]            | Г                             | DEC_RATE_C | H5                     | 0           | SEL_ODD_<br>TAP_CH5    | 0        | USE_<br>FILTER_<br>CH5 |                   |                        |

| 33               | 0 HPF_EN_ CH6 HPF_CORNER_CH6[3:0] |                                   |                 |                | FILT        | ER_TYPE_CH6     | [2:0]            |                               | DEC_RATE_C | H6                     | 0           | SEL_ODD_<br>TAP_CH6    | 0        | USE_<br>FILTER_<br>CH6 |                   |                        |

# Table 7. Register Map (continued)

|                     |                            |                |          |          |                               |                               |             |           | P (     |                |                        | 1      |                  | 1                   | 1           |                        |

|---------------------|----------------------------|----------------|----------|----------|-------------------------------|-------------------------------|-------------|-----------|---------|----------------|------------------------|--------|------------------|---------------------|-------------|------------------------|

| REGISTER<br>ADDRESS |                            |                |          |          |                               |                               |             |           |         |                |                        |        |                  |                     |             |                        |

| (Hex)               | D15                        | D14            | D13      | D12      | D11                           | D10                           | D9          | D8        | D7      | D6             | D5                     | D4     | D3               | D2                  | D1          | D0                     |

| 34                  | 0                          | HPF_EN_<br>CH7 |          | HPF_CORN | ER_CH7[3:0]                   |                               | FILT        | ER_TYPE_C | H7[2:0] | ι              | DEC_RATE_CH            | 17     | 0                | SEL_ODD_<br>TAP_CH7 | 0           | USE_<br>FILTER_<br>CH7 |

| 35                  | 0                          | HPF_EN_<br>CH8 |          | HPF_CORN | ER_CH8[3:0]                   |                               | FILT        | ER_TYPE_C | H8[2:0] | ι              | DEC_RATE_CH            | 18     | 0                | SEL_ODD_<br>TAP_CH8 | 0           | USE_<br>FILTER_<br>CH8 |

| 38                  | 0                          | 0              | 0        | 0        | 0                             | 0                             | 0           | 0         | 0       | 0              | 0                      | 0      | 0                | 0                   | DATA_R      | RATE[1:0]              |

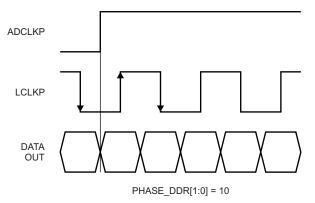

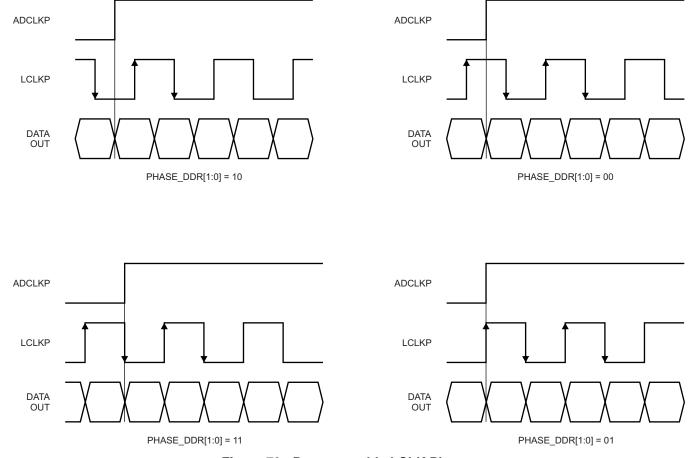

| 42                  | EN_PHASE<br>DDR            | 0              | 0        | 0        | 0                             | 0                             | 0           | 0         | 0       | PHASE_<br>DDR1 | PHASE_<br>DDR0         | 0      | 0                | 0                   | 0           | 0                      |

| 45                  | 0                          | 0              | 0        | 0        | 0                             | 0                             | 0           | 0         | 0       | 0              | 0                      | 0      | 0                | 0                   | PAT_DESKE   | W_SYNC[1:0]            |

| 46                  | ENABLE 46                  | 0              | FALL_SDR | 0        |                               | BIT_SI                        | ER_SEL      | i.        | 0       | 0              | 0                      | EN_SDR | EN_MSB_<br>FIRST | BTC_MODE            | 0           | EN_2WIRE               |

| 50                  | ENABLE 50                  | 0              | 0        | 0        |                               | MAP_Ch1234_to_OUT2A           |             |           |         | MAP_Ch123      | 34_to_OUT1B            | 1      |                  | MAP_Ch123           | 34_to_OUT1A |                        |

| 51                  | ENABLE 51                  | 0              | 0        | 0        |                               | MAP_Ch123                     | 4_to_OUT3B  |           |         | MAP_Ch123      | 34_to_OUT3A            |        |                  | MAP_Ch123           | 34_to_OUT2B |                        |

| 52                  | ENABLE 52                  | 0              | 0        | 0        | 0                             | 0                             | 0           | 0         |         | MAP_Ch123      | 34_to_OUT4B            |        |                  | MAP_Ch123           | 34_to_OUT4A |                        |

| 53                  | ENABLE 53                  | 0              | 0        | 0        |                               | MAP_Ch567                     | 8_to_OUT6B  |           |         | MAP_Ch567      | 8_to_OUT5A             |        |                  | MAP_Ch567           | 78_to_OUT5B |                        |

| 54                  | ENABLE 54                  | 0              | 0        | 0        |                               | MAP_Ch567                     | '8_to_OUT7A |           |         | MAP_Ch567      | 78_to_OUT7B            |        |                  | MAP_Ch5678_to_OUT6A |             |                        |

| 55                  | ENABLE 55                  | 0              | 0        | 0        | 0                             | 0                             | 0           | 0         |         | MAP_Ch567      | 78_to_OUT8A            |        |                  | MAP_Ch5678_to_OUT8B |             |                        |

| 5A to 65            | EN_<br>CUSTOM_<br>FILT_CH1 | 0              | 0        | 0        |                               |                               | ,           |           |         | COEFFn_        | SET_CH1 <sup>(1)</sup> |        | ı                |                     |             |                        |

| 66 to 71            | EN_<br>CUSTOM_<br>FILT_CH2 | 0              | 0        | 0        |                               |                               |             |           |         | COEFFn_        | SET_CH2 <sup>(1)</sup> |        |                  |                     |             |                        |

| 72 to 7D            | EN_<br>CUSTOM_<br>FILT_CH3 | 0              | 0        | 0        |                               |                               |             |           |         | COEFFn_        | SET_CH3 <sup>(1)</sup> |        |                  |                     |             |                        |

| 7E to 89            | EN_<br>CUSTOM_<br>FILT_CH4 | 0              | 0        | 0        |                               |                               |             |           |         | COEFFn_        | SET_CH4 <sup>(1)</sup> |        |                  |                     |             |                        |

| 8A to 95            | EN_<br>CUSTOM_<br>FILT_CH5 | 0              | 0        | 0        |                               |                               |             |           |         | COEFFn_        | SET_CH5 <sup>(1)</sup> |        |                  |                     |             |                        |