Support & training

# ADS131M02-Q1 汽车类、2 通道、64 kSPS、同步采样、24 位、Δ-Σ ADC

## 1 Features

- AEC-Q100 gualified for automotive applications: Temperature grade 1: - 40°C to +125°C, T<sub>A</sub>

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- 2 simultaneously sampling differential inputs ٠

- Programmable data rate up to 64 kSPS

- Programmable gain up to 128

- Noise performance:

- 102-dB dynamic range at gain = 1, 4 kSPS

- 80-dB dynamic range at gain = 64, 4 kSPS

- Total harmonic distortion: 100 dB

- High-impedance inputs for direct sensor ٠ connection:

- 330-k  $\Omega$  input impedance for gains of 1, 2, and 4

- $\ge 1$ -M  $\Omega$  input impedance for gains of 8, 16, 32, 64, and 128

- Programmable channel-to-channel phase delay calibration:

- Resolution = 244 ns, f<sub>CLKIN</sub> = 8.192 MHz

- Fast start-up: First data within 0.5 ms of supply • ramp

- Integrated negative charge pump allows input signals below ground

- Crosstalk between channels: 120 dB

- Low-drift internal voltage reference

- Cyclic redundancy check (CRC) on • communications and register map

- Analog and digital supplies: 2.7 V to 3.6 V

- Low-power consumption: 2.3 mW at 3-V AVDD • and DVDD

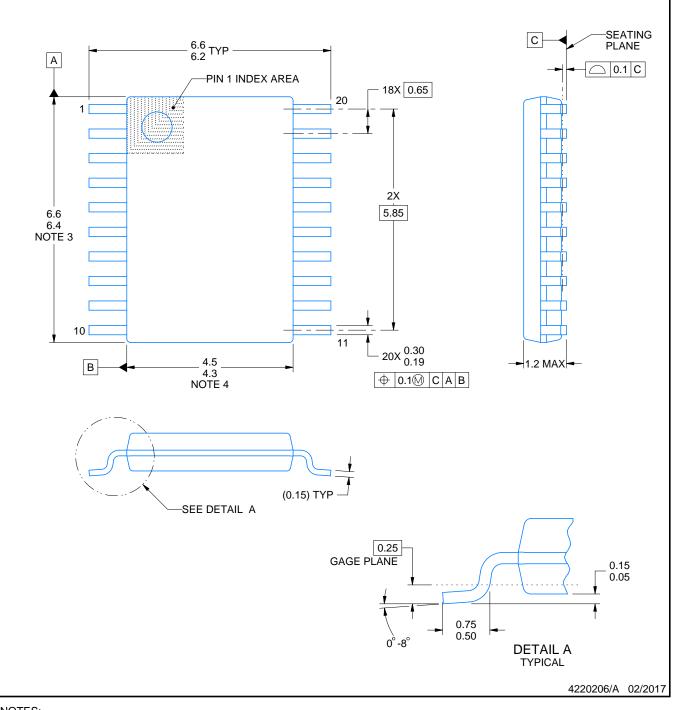

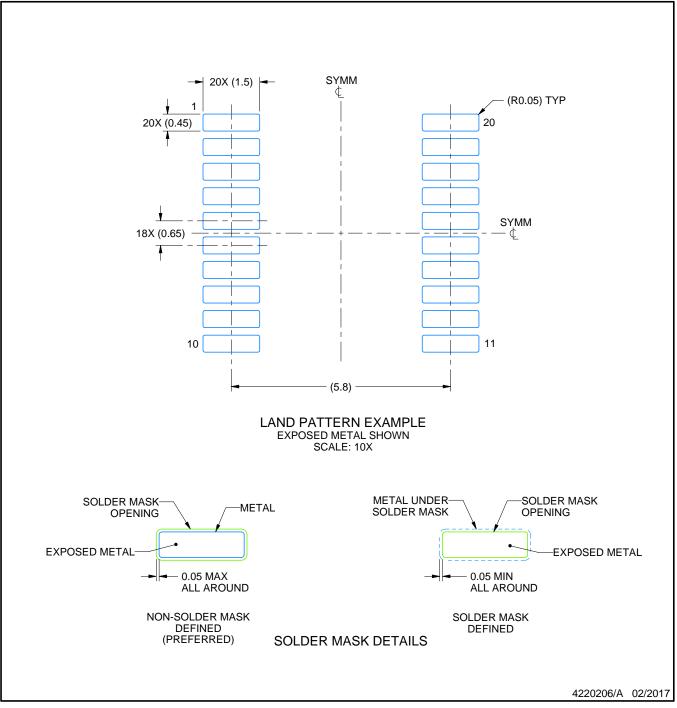

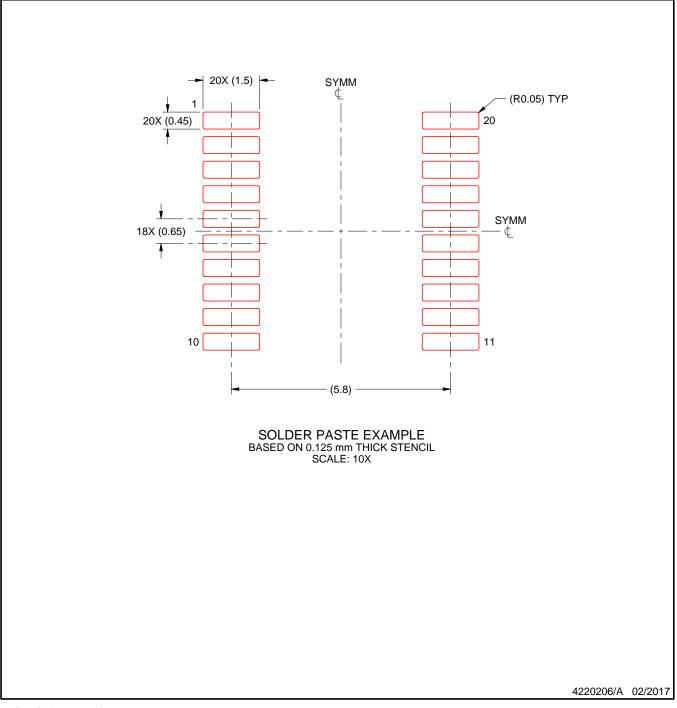

- Package: 20-pin TSSOP

## 2 Applications

- Automotive battery management systems (BMS):

- Current-shunt measurements

- Voltage measurements using external resistor dividers

- Temperature measurements using thermistors or analog output temperature sensors

- EV charging stations:

- DC e-metering

- AC e-metering

- Energy storage systems (ESS)

## **3 Description**

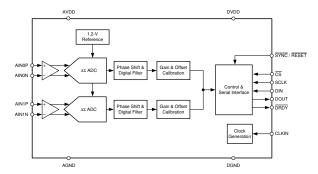

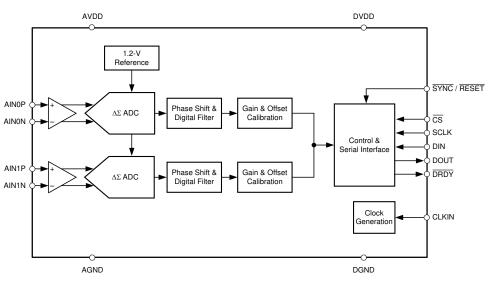

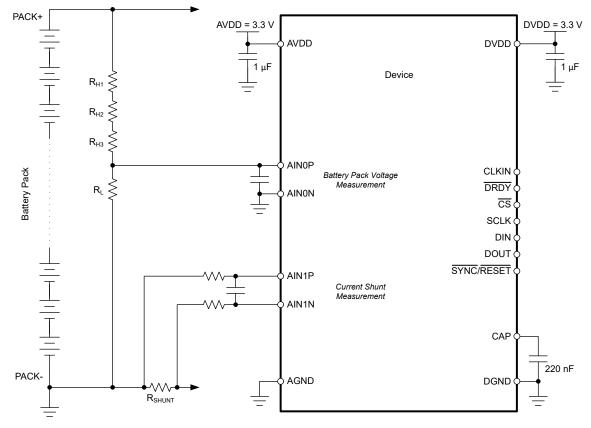

The ADS131M02-Q1 is a two-channel, simultaneously sampling, 24-bit, delta-sigma (  $\Delta \Sigma$  ), analog-to-digital converter (ADC) that offers wide dynamic range and low power, making the device designed for automotive battery management systems (BMS). The ADC inputs can be directly interfaced to shunt resistors for battery-current measurements. bidirectional to resistor-divider networks for high-voltage measurements, or to temperature sensors (such as thermistors or analog output temperature sensors).

The individual ADC channels can be independently configured depending on the sensor input. A lownoise, programmable gain amplifier (PGA) provides gains ranging from 1 to 128 to amplify low-level signals. Additionally, this device integrates channel-tochannel phase calibration and offset and gain calibration registers to help remove signal-chain errors.

A low-drift, 1.2-V reference is integrated into the device, reducing printed circuit board (PCB) area. Optional cyclic redundancy checks (CRCs) on the data input, data output, and register map maintain communication integrity.

The complete analog front-end (AFE) is offered in a 20-pin TSSOP package and is specified over the automotive temperature range of - 40°C to +125°C.

| Package In | formation <sup>(1)</sup> |

|------------|--------------------------|

|------------|--------------------------|

| PART NUMBER  | PACKAGE    | BODY SIZE (NOM)   |  |  |  |  |  |

|--------------|------------|-------------------|--|--|--|--|--|

| ADS131M02-Q1 | TSSOP (20) | 6.50 mm × 4.40 mm |  |  |  |  |  |

(1)For all available packages, see the orderable addendum at the end of the data sheet.

## Simplified Block Diagram

# **Table of Contents**

| 1 Features                           | 1               |

|--------------------------------------|-----------------|

| 2 Applications                       |                 |

| 3 Description                        | 1               |

| 4 Revision History                   |                 |

| 5 Pin Configuration and Functions    |                 |

| 6 Specifications                     |                 |

| 6.1 Absolute Maximum Ratings         | 4               |

| 6.2 ESD Ratings                      |                 |

| 6.3 Recommended Operating Conditions |                 |

| 6.4 Thermal Information              | <mark>5</mark>  |

| 6.5 Electrical Characteristics       |                 |

| 6.6 Timing Requirements              | <mark>8</mark>  |

| 6.7 Switching Characteristics        | <mark>8</mark>  |

| 6.8 Timing Diagrams                  | 10              |

| 6.9 Typical Characteristics          |                 |

| 7 Parameter Measurement Information  | 16              |

| 7.1 Noise Measurements               | 16              |

| 8 Detailed Description               | 18              |

| 8.1 Overview                         |                 |

| 8.2 Functional Block Diagram         | <mark>18</mark> |

| 8.3 Feature Description                 | 18        |

|-----------------------------------------|-----------|

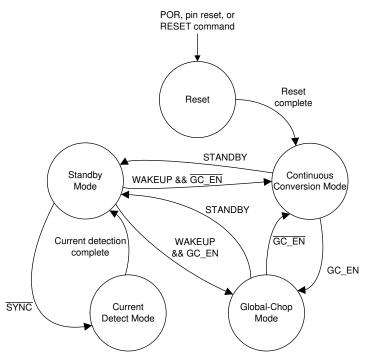

| 8.4 Device Functional Modes             | 30        |

| 8.5 Programming                         |           |

| 8.6 ADS131M02-Q1 Registers              |           |

| 9 Application and Implementation        |           |

| 9.1 Application Information             |           |

| 9.2 Typical Application                 | 71        |

| 9.3 Power Supply Recommendations        | 74        |

| 9.4 Layout                              | 74        |

| 10 Device and Documentation Support     | 76        |

| 10.1 Documentation Support              |           |

| 10.2 接收文档更新通知                           |           |

| 10.3 支持资源                               | 76        |

| 10.4 Trademarks                         |           |

| 10.5 Electrostatic Discharge Caution    | <b>76</b> |

| 10.6 术语表                                |           |

| 11 Mechanical, Packaging, and Orderable |           |

| Information                             | 76        |

|                                         |           |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| DATE        | REVISION | NOTES           |

|-------------|----------|-----------------|

| August 2022 | *        | Initial Release |

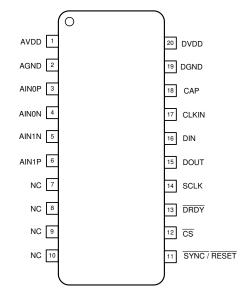

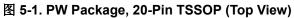

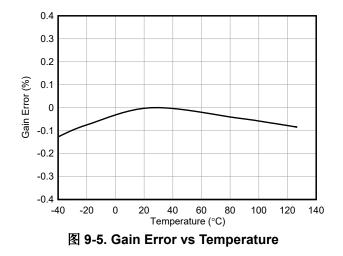

## **5** Pin Configuration and Functions

## 表 5-1. Pin Functions

| P          | IN          | I/O            | DESCRIPTION <sup>(1)</sup>                                                         |  |

|------------|-------------|----------------|------------------------------------------------------------------------------------|--|

| NAME       | NO.         | 1/0            | DESCRIPTION                                                                        |  |

| AGND       | 2           | Supply         | Analog ground                                                                      |  |

| AINON      | 4           | Analog input   | Negative analog input 0                                                            |  |

| AIN0P      | 3           | Analog input   | Positive analog input 0                                                            |  |

| AIN1N      | 5           | Analog input   | Negative analog input 1                                                            |  |

| AIN1P      | 6           | Analog input   | Positive analog input 1                                                            |  |

| AVDD       | 1           | Supply         | Analog supply. Connect a 1-µF capacitor to AGND.                                   |  |

| САР        | 18          | Analog output  | Digital low-dropout (LDO) regulator output.<br>Connect a 220-nF capacitor to DGND. |  |

| CLKIN      | 17          | Digital input  | Main clock input                                                                   |  |

| CS         | 12          | Digital input  | Chip select; active low                                                            |  |

| DGND       | 19          | Supply         | Digital ground                                                                     |  |

| DIN        | 16          | Digital input  | Serial data input                                                                  |  |

| DOUT       | 15          | Digital output | Serial data output                                                                 |  |

| DRDY       | 13          | Digital output | Data ready; active low                                                             |  |

| DVDD       | 20          | Supply         | Digital I/O supply. Connect a 1-µF capacitor to DGND.                              |  |

| NC         | 7, 8, 9, 10 |                | Leave unconnected or connect to AGND                                               |  |

| SCLK       | 14          | Digital input  | Serial data clock                                                                  |  |

| SYNC/RESET | 11          | Digital input  | Conversion synchronization or system reset; active low                             |  |

(1) See the Unused Inputs and Outputs section for details on how to connect unused pins.

## 6 Specifications

## 6.1 Absolute Maximum Ratings

see (1)

|                       |                                               | MIN        | MAX        | UNIT |

|-----------------------|-----------------------------------------------|------------|------------|------|

|                       | AVDD to AGND                                  | - 0.3      | 3.9        |      |

|                       | AGND to DGND                                  | - 0.3      | 0.3        |      |

| Power-supply voltage  | DVDD to DGND                                  | - 0.3      | 3.9        |      |

|                       | DVDD to DGND, CAP tied to DVDD                | - 0.3      | 2.2        | V    |

|                       | CAP to DGND                                   | - 0.3      | 2.2        |      |

| Analog input voltage  | AINxP, AINxN                                  | AGND - 1.6 | AVDD + 0.3 |      |

| Digital input voltage | CS, CLKIN, DIN, SCLK, SYNC/RESET              | DGND - 0.3 | DVDD + 0.3 |      |

| Input current         | Continuous, all pins except power-supply pins | - 10       | 10         | mA   |

| Tomporatura           | Junction, T <sub>J</sub>                      |            | 150        | °C   |

| Temperature           | Storage, T <sub>stg</sub>                     | - 60       | 150        | C    |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |                                                                                              |                                                      |                           | VALUE | UNIT |

|--------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|-------|------|

|                    | Human-body model (HBM),<br>per AEC Q100-002 <sup>(1)</sup><br>HBM ESD classification level 2 |                                                      | ±2000                     | V     |      |

| V <sub>(ESD)</sub> | Liechostatic discharge                                                                       | Charged-device model (CDM),                          | Corner pins               | ±750  |      |

|                    |                                                                                              | per AEC Q100-011<br>CDM ESD classification level C4B | All other non-corner pins | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                                            |                            |                                                           | MIN                          | NOM   | MAX                   | UNIT |  |

|--------------------------------------------|----------------------------|-----------------------------------------------------------|------------------------------|-------|-----------------------|------|--|

| POWEF                                      | R SUPPLY                   |                                                           |                              |       |                       |      |  |

|                                            |                            | AVDD to AGND, normal operating modes                      | 2.7                          | 3.0   | 3.6                   |      |  |

|                                            | Analog power supply        | AVDD to AGND, standby and current-detect modes            | 2.4                          | 3.0   | 3.6                   | V    |  |

|                                            |                            | AGND to DGND                                              | - 0.3                        | 0     | 0.3                   |      |  |

|                                            |                            | DVDD to DGND                                              | 2.7                          | 3.0   | 3.6                   |      |  |

|                                            | Digital power supply       | DVDD to DGND, DVDD shorted to CAP (digital LDO bypassed)  | 1.65                         | 1.8   | 2                     | V    |  |

| ANALO                                      | OG INPUTS <sup>(1)</sup>   |                                                           | 1                            |       |                       |      |  |

| V <sub>ainxp</sub> ,<br>V <sub>ainxn</sub> | Absolute input voltage     | Gain = 1, 2, or 4                                         | AGND -<br>1.3                |       | AVDD                  | - V  |  |

|                                            |                            | Gain = 8, 16, 32, 64 or 128                               | AGND -<br>1.3                | AV    | ′DD - 1.8             |      |  |

| V <sub>IN</sub>                            | Differential input voltage | V <sub>IN</sub> = V <sub>AINxP</sub> - V <sub>AINxN</sub> | - V <sub>REF</sub> /<br>Gain | V     | <sub>REF</sub> / Gain | V    |  |

| EXTER                                      | NAL CLOCK SOURCE           |                                                           | 1                            |       |                       |      |  |

|                                            |                            | High-resolution mode                                      | 0.3                          | 8.192 | 8.4                   |      |  |

| f <sub>CLKIN</sub>                         | External clock frequency   | Low-power mode                                            | 0.3                          | 4.096 | 4.15                  | MHz  |  |

|                                            |                            | Very-low-power mode                                       | 0.3                          | 2.048 | 2.08                  |      |  |

|                                            | Duty cycle                 |                                                           | 40%                          | 50%   | 60%                   |      |  |

| DIGITA                                     | LINPUTS                    |                                                           | 1                            |       |                       |      |  |

|                                            | Input voltage              |                                                           | DGND                         |       | DVDD                  | V    |  |

| TEMPE                                      | RATURE RANGE               |                                                           |                              |       | I                     |      |  |

| T <sub>A</sub>                             | Operating ambient tempera  | ature                                                     | - 40                         |       | 125                   | °C   |  |

(1) The subscript "x" signifies the channel. For example, the positive analog input to channel 0 is named AIN0P. See the *Pin Configuration and Functions* section for the pin names.

## **6.4 Thermal Information**

|                   |                                              | ADS131M02-Q1 |      |

|-------------------|----------------------------------------------|--------------|------|

|                   | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP)   | UNIT |

|                   |                                              | 20 PINS      |      |

| R <sub>0 JA</sub> | Junction-to-ambient thermal resistance       | 94.9         | °C/W |

| R <sub>θ</sub>    | Junction-to-case (top) thermal resistance    | 34.9         | °C/W |

| JC(top)           |                                              |              |      |

| $R_{\theta JB}$   | Junction-to-board thermal resistance         | 46.4         | °C/W |

| ΨJT               | Junction-to-top characterization parameter   | 2.7          | °C/W |

| Ψ <sub>JB</sub>   | Junction-to-board characterization parameter | 46.0         | °C/W |

| R <sub>θ</sub>    | Junction-to-case (bottom) thermal resistance | N/A          | °C/W |

| JC(bot)           |                                              |              |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

minimum and maximum specifications apply from  $T_A = -40^{\circ}$ C to +125°C; typical specifications are at  $T_A = 25^{\circ}$ C; all specifications are at AVDD = 3 V, DVDD = 3 V, f<sub>CLKIN</sub> = 8.192 MHz, data rate = 4 kSPS, all channels enabled, global-chop mode disabled and gain = 1 (unless otherwise noted)

|                   | PARAMETER                        | TEST CONDITIONS                                                                                                      | MIN TYP                     | MAX | UNIT             |

|-------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|------------------|

| ANALO             | G INPUTS                         |                                                                                                                      |                             |     |                  |

| 1-                | Input bias current               | Gain = 1, 2, or 4, $V_{INP} = V_{INN} = 0 V$ ,<br>$I_B = (I_{BP} + I_{BN}) / 2$                                      | 0.6                         |     | ΠA               |

| IB                | Input bias current               | Gain = 8, 16, 32, 64 or 128, $V_{INP} = V_{INN} =$<br>0 V, I <sub>B</sub> = (I <sub>BP</sub> + I <sub>BN</sub> ) / 2 | 0.2                         |     | μA               |

| 7                 | Differential input impedance     | Gain = 1, 2, or 4                                                                                                    | 300                         |     | kΩ               |

| Z <sub>in</sub>   | Differential input impedance     | Gain = 8, 16, 32, 64, or 128                                                                                         | ±1 <sup>(1)</sup>           |     | µA/V             |

| ADC CH            | ARACTERISTICS                    | · · · · ·                                                                                                            |                             |     |                  |

|                   | Resolution                       |                                                                                                                      | 24                          |     | Bits             |

|                   | Gain settings                    |                                                                                                                      | 1, 2, 4, 8, 16, 32, 64, 128 |     |                  |

|                   |                                  | High-resolution mode, f <sub>CLKIN</sub> = 8.192 MHz                                                                 | 250                         | 64k |                  |

| f <sub>DATA</sub> | Data rate                        | Low-power mode, f <sub>CLKIN</sub> = 4.096 MHz                                                                       | 125                         | 32k | SPS              |

|                   |                                  | Very-low-power mode, f <sub>CLKIN</sub> = 2.048 MHz                                                                  | 62.5                        | 16k |                  |

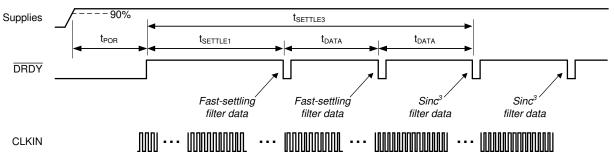

|                   | Startup time                     | Measured from supplies at 90% to first<br>DRDY falling edge                                                          | 0.5                         |     | ms               |

| ADC PE            | RFORMANCE                        |                                                                                                                      |                             |     |                  |

| INL               | Integral nonlinearity (best fit) |                                                                                                                      | 6                           |     | ppm o<br>FSR     |

|                   |                                  |                                                                                                                      | ±175                        |     |                  |

|                   | Offset error (input referred)    | Global-chop mode, channel 0                                                                                          | ±35                         |     | μV               |

|                   |                                  | Global-chop mode, channels 1-3                                                                                       | ±15                         |     |                  |

|                   |                                  |                                                                                                                      | 300                         |     |                  |

|                   | Offset drift                     | Global-chop mode                                                                                                     | 200                         |     | nV/°C            |

|                   | Offset error time drift          | 1000 hours at 85°C                                                                                                   | 4                           |     | μV               |

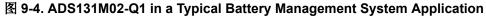

|                   | Gain error                       |                                                                                                                      | ±0.1%                       |     |                  |

|                   | O a in shrift                    |                                                                                                                      | 1                           |     |                  |

|                   | Gain drift                       | Including internal reference                                                                                         | 8.5                         |     | ppm/°            |

|                   | Gain error time drift            | 1000 hours at 85°C                                                                                                   | 400                         |     | ppm              |

| CMRR              | Common-mode rejection            | At dc                                                                                                                | 100                         |     | dB               |

| CIVIRR            | ratio                            | f <sub>CM</sub> = 50 Hz or 60 Hz                                                                                     | 94                          |     | uв               |

|                   |                                  | AVDD at dc                                                                                                           | 75                          |     |                  |

|                   | Power-supply rejection ratio     | DVDD at dc                                                                                                           | 88                          |     | AD               |

| PSRR              | Power-supply rejection ratio     | AVDD supply, f <sub>PS</sub> = 50 Hz or 60 Hz                                                                        | 78                          |     | dB               |

|                   |                                  | DVDD supply, f <sub>PS</sub> = 50 Hz or 60 Hz                                                                        | 85                          |     |                  |

|                   | Input-referred noise             |                                                                                                                      | 5.35                        |     | μV <sub>RM</sub> |

|                   |                                  | During fast-startup                                                                                                  | 1.5                         |     | mV <sub>RM</sub> |

|                   |                                  | Gain = 1                                                                                                             | 99 102                      |     | dB               |

|                   | Dynamic range                    | Gain = 64                                                                                                            | 80                          |     | ив               |

|                   |                                  | All other gain settings                                                                                              | See 表 7-1                   |     |                  |

|                   | Crosstalk                        | f <sub>IN</sub> = 50 Hz or 60 Hz                                                                                     | - 120                       |     | dB               |

|                   |                                  | $f_{IN}$ = 50 Hz or 60 Hz, gain = 1,<br>V <sub>IN</sub> = - 0.5 dBFS, normalized                                     | 100                         |     |                  |

| SNR               | Signal-to-noise ratio            | f <sub>IN</sub> = 50 Hz or 60 Hz, gain = 64,<br>V <sub>IN</sub> = - 0.5 dBFS, normalized                             | 79                          |     | dB               |

## 6.5 Electrical Characteristics (continued)

minimum and maximum specifications apply from  $T_A = -40^{\circ}$ C to +125°C; typical specifications are at  $T_A = 25^{\circ}$ C; all specifications are at AVDD = 3 V, DVDD = 3 V, f<sub>CLKIN</sub> = 8.192 MHz, data rate = 4 kSPS, all channels enabled, global-chop mode disabled and gain = 1 (unless otherwise noted)

|                   | PARAMETER                             | TEST CONDITIONS                                                                 | MIN      | ТҮР   | MAX      | UNIT   |

|-------------------|---------------------------------------|---------------------------------------------------------------------------------|----------|-------|----------|--------|

| THD               | Total harmonic distortion             | $f_{IN}$ = 50 Hz or 60 Hz (up to 50 harmonics),<br>V <sub>IN</sub> = -0.5 dBFS  |          | - 100 |          | dB     |

| SFDR              | Spurious-free dynamic range           | $f_{\rm IN}$ = 50 Hz or 60 Hz (up to 50 harmonics), $V_{\rm IN}$ = $-$ 0.5 dBFS |          | 105   |          | dB     |

| INTERN            | NAL VOLTAGE REFERENCE                 |                                                                                 |          |       |          |        |

| V <sub>REF</sub>  | Internal reference voltage            |                                                                                 |          | 1.2   |          | V      |

|                   | Accuracy                              | T <sub>A</sub> = 25°C                                                           |          | ±0.1% |          |        |

|                   | Temperature drift                     |                                                                                 |          | 7.5   | 20       | ppm/°C |

| DIGITA            | L INPUTS/OUTPUTS                      |                                                                                 |          |       |          |        |

| V <sub>IL</sub>   | Logic input level, low                |                                                                                 | DGND     |       | 0.2 DVDD | V      |

| V <sub>IH</sub>   | Logic input level, high               |                                                                                 | 0.8 DVDD |       | DVDD     | V      |

| V <sub>OL</sub>   | Logic output level, low               | $I_{OL} = -1 \text{ mA}$                                                        |          |       | 0.2 DVDD | V      |

| V <sub>OH</sub>   | Logic output level, high              | I <sub>OH</sub> = 1 mA                                                          | 0.8 DVDD |       |          | V      |

| I <sub>IN</sub>   | Input current                         | DGND < V <sub>Digital Input</sub> < DVDD                                        | - 1      |       | 1        | μA     |

| POWER             | R SUPPLY                              |                                                                                 | 1        |       |          | 1      |

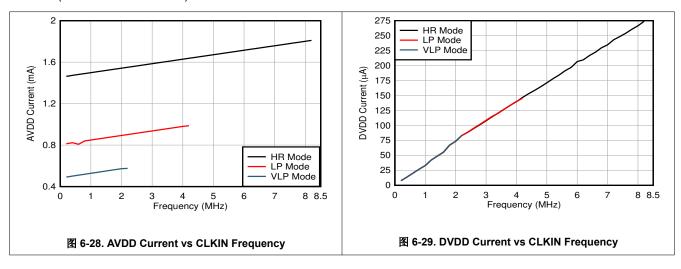

|                   |                                       | High-resolution mode                                                            |          | 1.8   | 2.15     |        |

|                   |                                       | Low-power mode                                                                  |          | 1.0   | 1.15     |        |

| I <sub>AVDD</sub> | Analog supply current                 | Very-low-power mode                                                             |          | 0.57  | 0.75     | mA     |

|                   |                                       | Current-detect mode                                                             |          | 0.55  |          |        |

|                   |                                       | Standby mode                                                                    |          | 0.3   |          | μA     |

|                   |                                       | High-resolution mode                                                            |          | 0.27  | 0.35     |        |

|                   |                                       | Low-power mode                                                                  |          | 0.14  | 0.19     | -      |

| I <sub>DVDD</sub> | Digital supply current <sup>(2)</sup> | Very-low-power mode                                                             |          | 0.08  | 0.12     | mA     |

|                   |                                       | Current-detect mode                                                             |          | 0.05  |          |        |

|                   |                                       | Standby mode                                                                    |          | 1     |          | uA     |

|                   |                                       | High-resolution mode                                                            |          | 6.2   |          |        |

|                   |                                       | Low-power mode                                                                  |          | 3.4   |          | mW     |

| PD                | Power dissipation                     | Very-low-power mode                                                             |          | 1.9   |          |        |

|                   |                                       | Current-detect mode                                                             |          | 1.8   |          |        |

|                   |                                       | Standby mode                                                                    |          | 3.9   |          | μW     |

(1) Specified in  $\mu$ A/V because current can flow either into or out of the input pin.

(2) Currents measured with SPI idle.

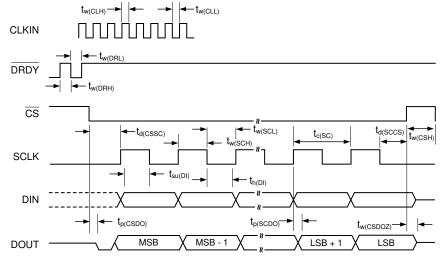

## 6.6 Timing Requirements

over operating ambient temperature range, DOUT load: 20 pF || 100 kΩ (unless otherwise noted)

|                      |                                                          | MIN  | MAX  | UNIT               |

|----------------------|----------------------------------------------------------|------|------|--------------------|

| 1.65 V ≤             | $DVDD \leq 2.0 V$                                        |      |      |                    |

| t <sub>w(CLH)</sub>  | Pulse duration, CLKIN high                               | 49   |      | ns                 |

| t <sub>w(CLL)</sub>  | Pulse duration, CLKIN low                                | 49   |      | ns                 |

| t <sub>c(SC)</sub>   | SCLK period                                              | 64   |      | ns                 |

| t <sub>w(SCL)</sub>  | Pulse duration, SCLK low                                 | 32   |      | ns                 |

| t <sub>w(SCH)</sub>  | Pulse duration, SCLK high                                | 32   |      | ns                 |

| t <sub>d(CSSC)</sub> | Delay time, first SCLK rising edge after CS falling edge | 16   |      | ns                 |

| t <sub>d(SCCS)</sub> | Delay time, CS rising edge after final SCLK falling edge | 10   |      | ns                 |

| t <sub>w(CSH)</sub>  | Pulse duration, CS high                                  | 20   |      | ns                 |

| t <sub>su(DI)</sub>  | Setup time, DIN valid before SCLK falling egde           | 5    |      | ns                 |

| t <sub>h(DI)</sub>   | Hold time, DIN valid after SCLK falling edge             | 8    |      | ns                 |

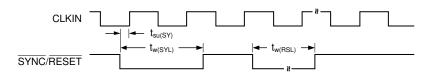

| t <sub>w(RSL)</sub>  | Pulse duration, SYNC/RESET low to generate device reset  | 2048 |      | t <sub>CLKIN</sub> |

| t <sub>w(SYL)</sub>  | Pulse duration, SYNC/RESET low for synchronization       | 1    | 2047 | t <sub>CLKIN</sub> |

| t <sub>su(SY)</sub>  | Setup time, SYNC/RESET valid before CLKIN rising edge    | 10   |      | ns                 |

| 2.7 V ≤ I            | DVDD ≤ 3.6 V                                             |      |      |                    |

| t <sub>w(CLL)</sub>  | Pulse duration, CLKIN low                                | 49   |      | ns                 |

| t <sub>w(CLH)</sub>  | Pulse duration, CLKIN high                               | 49   |      | ns                 |

| t <sub>c(SC)</sub>   | SCLK period                                              | 40   |      | ns                 |

| t <sub>w(SCL)</sub>  | Pulse duration, SCLK low                                 | 20   |      | ns                 |

| t <sub>w(SCH)</sub>  | Pulse duration, SCLK high                                | 20   |      | ns                 |

| t <sub>d(CSSC)</sub> | Delay time, first SCLK rising edge after CS falling edge | 16   |      | ns                 |

| t <sub>d(SCCS)</sub> | Delay time, CS rising edge after final SCLK falling edge | 10   |      | ns                 |

| t <sub>w(CSH)</sub>  | Pulse duration, CS high                                  | 15   |      | ns                 |

| t <sub>su(DI)</sub>  | Setup time, DIN valid before SCLK falling egde           | 5    |      | ns                 |

| t <sub>h(DI)</sub>   | Hold time, DIN valid after SCLK falling edge             | 8    |      | ns                 |

| t <sub>w(RSL)</sub>  | Pulse duration, SYNC/RESET low to generate device reset  | 2048 |      | t <sub>CLKIN</sub> |

| t <sub>w(SYL)</sub>  | Pulse duration, SYNC/RESET low for synchronization       | 1    | 2047 | t <sub>CLKIN</sub> |

| t <sub>su(SY)</sub>  | Setup time, SYNC/RESET valid before CLKIN rising edge    | 10   |      | ns                 |

## 6.7 Switching Characteristics

over operating ambient temperature range, DOUT load: 20 pF || 100 k $\Omega$  (unless otherwise noted)

| PARAMETER             |                                                                                   | TEST CONDITIONS                                               | MIN   | TYP | MAX | UNIT               |

|-----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------|-------|-----|-----|--------------------|

| 1.65 V ≤              | E DVDD ≤ 2.0 V                                                                    |                                                               |       |     |     |                    |

| t <sub>p(CSDO)</sub>  | Propagation delay time, $\overline{\text{CS}}$ falling edge to DOUT driven        |                                                               |       |     | 50  | ns                 |

| t <sub>p(SCDO)</sub>  | Progapation delay time, SCLK rising edge to valid new DOUT                        |                                                               |       |     | 32  | ns                 |

| t <sub>p(CSDOZ)</sub> | Propagation delay time, $\overline{\text{CS}}$ rising edge to DOUT high impedance |                                                               |       |     | 75  | ns                 |

| t <sub>w(DRH)</sub>   | Pulse duration, DRDY high                                                         |                                                               |       | 4   |     | t <sub>CLKIN</sub> |

| t <sub>w(DRL)</sub>   | Pulse duration, DRDY low                                                          |                                                               |       | 4   |     | t <sub>CLKIN</sub> |

|                       | SPI timeout                                                                       |                                                               | 32768 |     |     | t <sub>CLKIN</sub> |

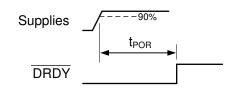

| t <sub>POR</sub>      | Power-on-reset time                                                               | Measured from supplies at<br>90% to first DRDY rising<br>edge |       | 250 |     | μs                 |

| t <sub>REGACQ</sub>   | Register default acquisition time                                                 |                                                               |       | 5   |     | μs                 |

## 6.7 Switching Characteristics (continued)

over operating ambient temperature range, DOUT load: 20 pF || 100 kΩ (unless otherwise noted)

| PARAMETER             |                                                                                   | TEST CONDITIONS                                               | MIN   | TYP | MAX | UNIT               |

|-----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------|-------|-----|-----|--------------------|

| 2.7 V ≤ I             | DVDD ≤ 3.6 V                                                                      |                                                               |       |     |     |                    |

| t <sub>p(CSDO)</sub>  | Propagation delay time, $\overline{\text{CS}}$ falling edge to DOUT driven        |                                                               |       |     | 50  | ns                 |

| t <sub>p(SCDO)</sub>  | Progapation delay time, SCLK rising edge to valid new DOUT                        |                                                               |       |     | 20  | ns                 |

| t <sub>p(CSDOZ)</sub> | Propagation delay time, $\overline{\text{CS}}$ rising edge to DOUT high impedance |                                                               |       |     | 75  | ns                 |

| t <sub>w(DRH)</sub>   | Pulse duration, DRDY high                                                         |                                                               |       | 4   |     | t <sub>CLKIN</sub> |

| t <sub>w(DRL)</sub>   | Pulse duration, DRDY low                                                          |                                                               |       | 4   |     | t <sub>CLKIN</sub> |

|                       | SPI timeout                                                                       |                                                               | 32768 |     |     | t <sub>CLKIN</sub> |

| t <sub>POR</sub>      | Power-on-reset time                                                               | Measured from supplies at<br>90% to first DRDY rising<br>edge |       | 250 |     | μs                 |

| t <sub>REGACQ</sub>   | Register default acquisition time                                                 |                                                               |       | 5   |     | μs                 |

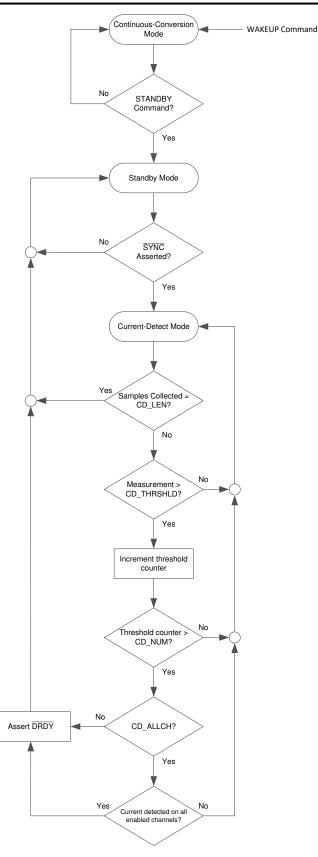

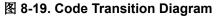

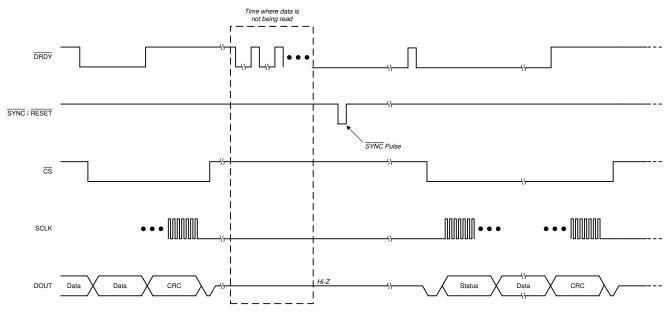

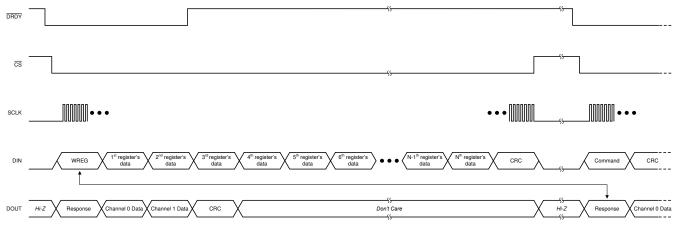

## 6.8 Timing Diagrams

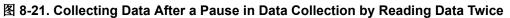

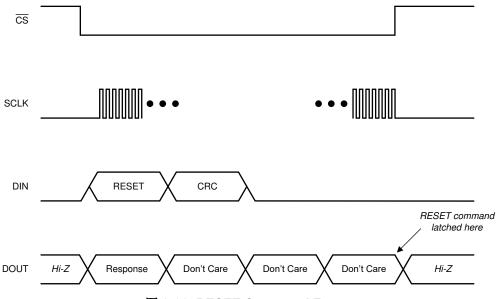

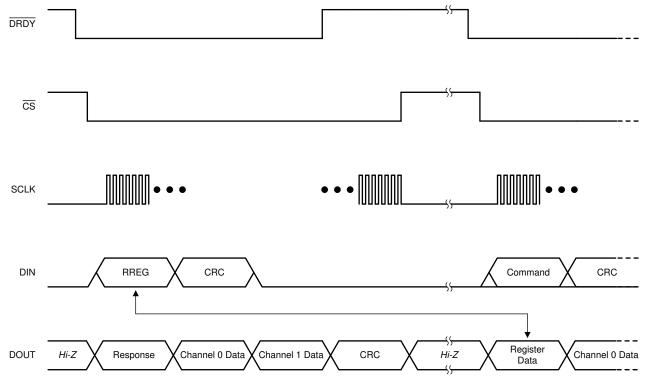

NOTE: SPI settings are CPOL = 0 and CPHA = 1.  $\overline{CS}$  transitions must take place when SCLK is low.

图 6-1. SPI Timing Diagram

## 图 6-2. SYNC/RESET Timing Requirements

图 6-3. Power-On-Reset Timing

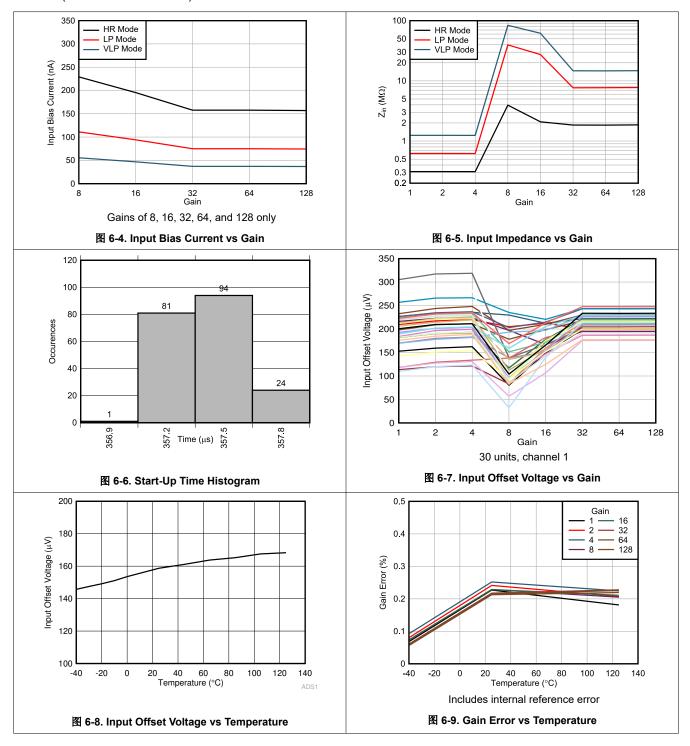

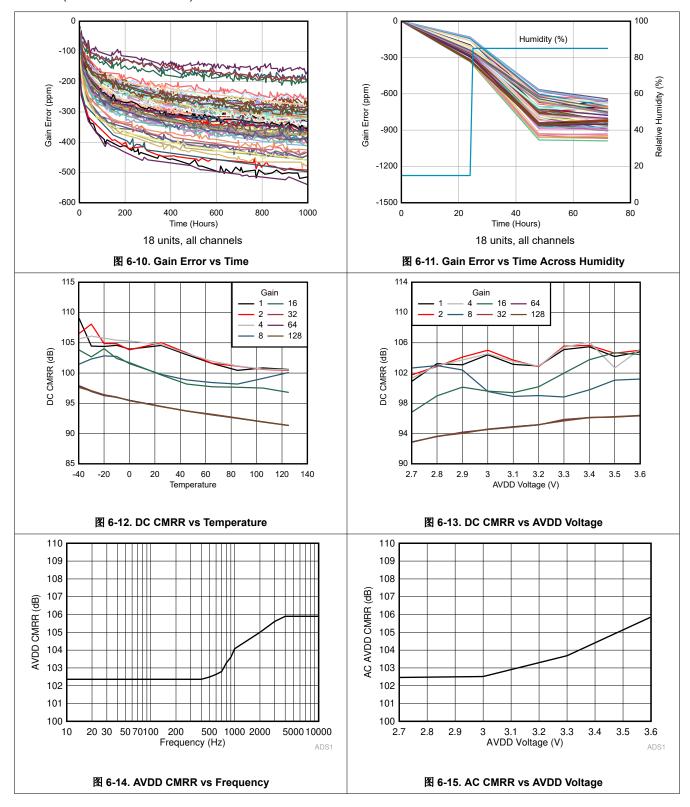

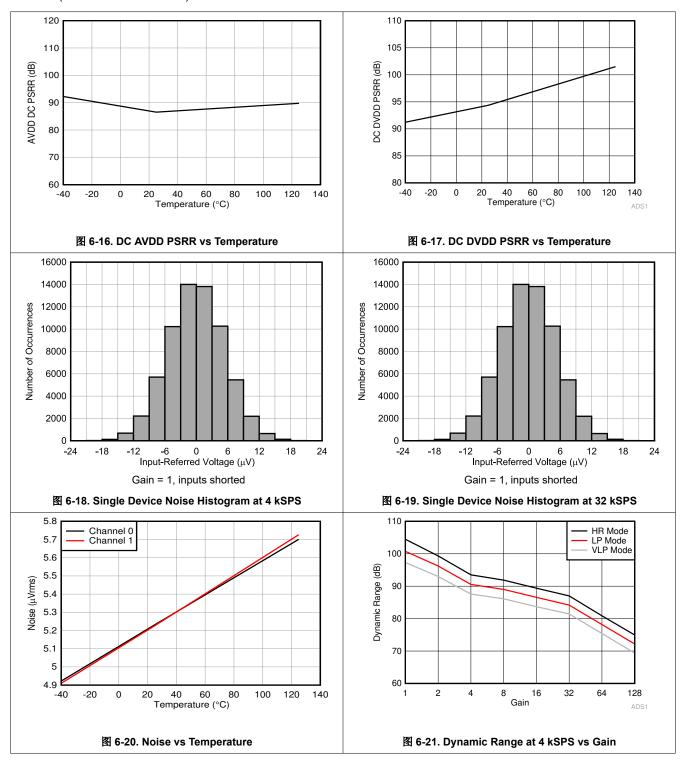

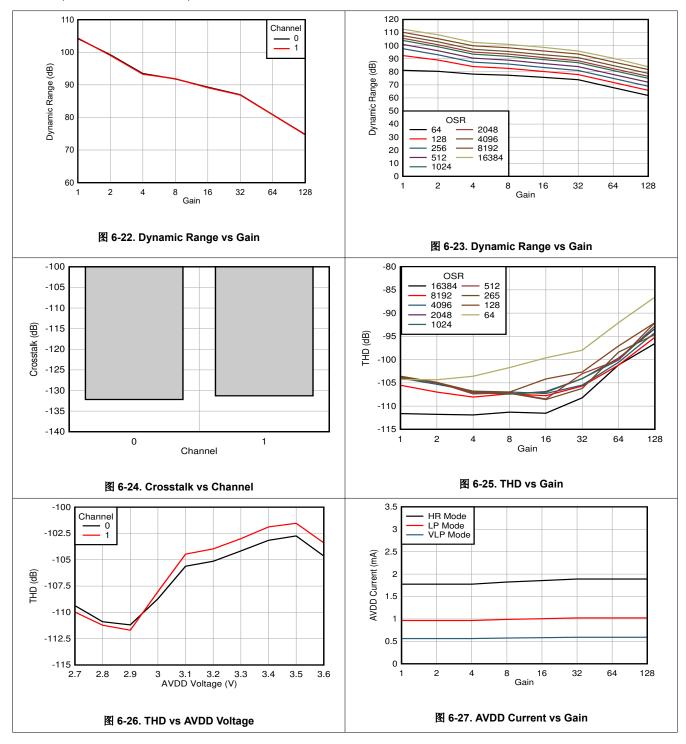

## **6.9 Typical Characteristics**

## 7 Parameter Measurement Information

## 7.1 Noise Measurements

Adjust the data rate and gain to optimize the ADS131M02-Q1 noise performance. When averaging is increased by reducing the data rate, noise drops correspondingly.  $\overline{\mathcal{R}}$  7-1 summarizes the ADS131M02-Q1 noise performance using the 1.2-V internal reference and a 3.0-V analog power supply. The data are representative of typical noise performance at  $T_A = 25^{\circ}$ C when  $f_{CLKIN} = 8.192$  MHz. The modulator clock frequency  $f_{MOD}$  is equal to  $f_{CLKIN} / 2$ . The data shown are typical input-referred noise results with the analog inputs shorted together and taking an average of multiple readings across all channels. A minimum 1 second of consecutive readings are used to calculate the RMS.  $\overline{\mathcal{R}}$  7-2 shows the dynamic range and effective resolution calculated from the noise data.  $\overline{\mathcal{T}}$   $\overline{\mathcal{R}}$   $\overline{\mathcal{I}}$  1 calculates dynamic range.  $\overline{\mathcal{T}}$   $\overline{\mathcal{R}}$   $\overline{\mathcal{I}}$  2 calculates effective resolution. In each case, V<sub>REF</sub> corresponds to the internal 1.2-V reference. In global-chop mode, noise is improved by a factor of  $\sqrt{2}$ .

The noise performance scales with the OSR and gain settings, but is independent from the configured power mode. Thus, the device exhibits the same noise performance in different power modes when selecting the same OSR and gain settings. However, the data rate at the OSR settings scales based on the applied clock frequency for the different power modes.

Dynamic Range =

$$20 \times \log \left( \frac{V_{REF}}{\sqrt{2} \times Gain \times V_{RMS}} \right)$$

Effective Resolution =

$$\log_2 \left( \frac{2 \times V_{REF}}{Gain \times V_{RMS}} \right)$$

(2)

(1)

| $\chi$ 7-1. Noise ( $\mu$ V <sub>RMS</sub> ) at T <sub>A</sub> = 25 °C |                                |       |       |       |       |      |      |      |      |  |

|------------------------------------------------------------------------|--------------------------------|-------|-------|-------|-------|------|------|------|------|--|

| OSR                                                                    | DATA RATE (kSPS),              | GAIN  |       |       |       |      |      |      |      |  |

| USK                                                                    | f <sub>CLKIN</sub> = 8.192 MHz | 1     | 2     | 4     | 8     | 16   | 32   | 64   | 128  |  |

| 16384                                                                  | 0.25                           | 1.90  | 1.69  | 1.56  | 0.95  | 0.64 | 0.42 | 0.42 | 0.42 |  |

| 8192                                                                   | 0.5                            | 2.39  | 2.13  | 2.13  | 1.29  | 0.86 | 0.57 | 0.57 | 0.57 |  |

| 4096                                                                   | 1                              | 3.38  | 2.99  | 2.88  | 1.74  | 1.17 | 0.77 | 0.77 | 0.77 |  |

| 2048                                                                   | 2                              | 4.25  | 3.91  | 3.79  | 2.27  | 1.52 | 1.00 | 1.00 | 1.00 |  |

| 1024                                                                   | 4                              | 5.35  | 4.68  | 4.52  | 2.70  | 1.82 | 1.20 | 1.20 | 1.20 |  |

| 512                                                                    | 8                              | 7.56  | 6.62  | 6.37  | 3.82  | 2.55 | 1.69 | 1.69 | 1.69 |  |

| 256                                                                    | 16                             | 10.68 | 9.56  | 9.09  | 5.42  | 3.63 | 2.39 | 2.39 | 2.40 |  |

| 128                                                                    | 32                             | 21.31 | 15.26 | 13.52 | 7.89  | 5.21 | 3.41 | 3.42 | 3.42 |  |

| 64                                                                     | 64                             | 75.34 | 41.63 | 26.84 | 14.59 | 8.9  | 5.57 | 5.58 | 5.58 |  |

## 表 7-1. Noise ( µ V<sub>RMS</sub>) at T<sub>A</sub> = 25°C

表 7-2. Dynamic Range (Effective Resolution) at T<sub>A</sub> = 25°C

| OSR   | DATA RATE (kSPS),              | GAIN       |            |            |            |           |           |           |           |  |

|-------|--------------------------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|--|

| USK   | f <sub>CLKIN</sub> = 8.192 MHz | 1          | 2          | 4          | 8          | 16        | 32        | 64        | 128       |  |

| 16384 | 0.25                           | 113 (20.3) | 108 (19.4) | 103 (18.6) | 101 (18.3) | 98 (17.8) | 96 (17.5) | 90 (16.5) | 84 (15.4) |  |

| 8192  | 0.5                            | 111 (19.9) | 106 (19.1) | 100 (18.1) | 98 (17.8)  | 96 (17.4) | 93 (17.0) | 87 (16.0) | 81 (15.0) |  |

| 4096  | 1                              | 108 (19.4) | 103 (18.6) | 97 (17.7)  | 96 (17.4)  | 93 (17.0) | 91 (16.6) | 85 (15.6) | 79 (14.6) |  |

| 2048  | 2                              | 106 (19.1) | 101 (18.2) | 95 (17.3)  | 93 (17.0)  | 91 (16.6) | 88 (16.2) | 82 (15.2) | 76 (14.2) |  |

| 1024  | 4                              | 104 (18.8) | 99 (18.0)  | 93 (17.0)  | 92 (16.8)  | 89 (16.3) | 87 (15.9) | 81 (14.9) | 75 (13.9) |  |

| 512   | 8                              | 101 (18.3) | 96 (17.5)  | 90 (16.5)  | 89 (16.3)  | 86 (15.8) | 84 (15.4) | 78 (14.4) | 72 (13.4) |  |

| 256   | 16                             | 98 (17.8)  | 93 (16.9)  | 87 (16.0)  | 86 (15.8)  | 83 (15.3) | 81 (14.9) | 75 (13.9) | 69 (12.9) |  |

| 128   | 32                             | 92 (16.8)  | 89 (16.3)  | 84 (15.4)  | 83 (15.2)  | 80 (14.8) | 78 (14.4) | 72 (13.4) | 65 (12.4) |  |

| OSR | DATA RATE (kSPS),              | S), GAIN  |           |           |           |           |           |           |           |

|-----|--------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| USK | f <sub>CLKIN</sub> = 8.192 MHz | 1         | 2         | 4         | 8         | 16        | 32        | 64        | 128       |

| 64  | 64                             | 81 (15.0) | 80 (14.8) | 78 (14.4) | 77 (14.3) | 75 (14.0) | 74 (13.7) | 68 (12.7) | 62 (11.7) |

## 8 Detailed Description

## 8.1 Overview

The ADS131M02-Q1 is a low-power, two-channel, simultaneous-sampling, 24-bit, delta-sigma ( $\Delta \Sigma$ ) analog-todigital converter (ADC) with a low-drift internal reference voltage. The dynamic range, size, feature set, and power consumption are optimized for cost-sensitive applications requiring simultaneous-sampling.

The ADS131M02-Q1 requires both analog and digital supplies. The analog power supply (AVDD - AGND) can operate between 2.7 V and 3.6 V. An integrated negative charge pump allows absolute input voltages as low as 1.3 V below AGND, which enables measurements of input signals varying around ground with a single-ended power supply. The digital power supply (DVDD - DGND) accepts both 1.8-V and 3.3-V supplies. The device features a programmable gain amplifier (PGA) with gains up to 128. An integrated input precharge buffer enabled at gains greater than 4 ensures high input impedance at high PGA gain settings. The ADC receives the reference voltage from an integrated 1.2-V reference. The device allows differential input voltages as large as the reference. Three power-scaling modes allow designers to trade power consumption for ADC dynamic range.

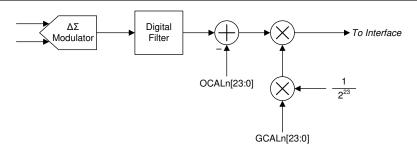

Each channel on the ADS131M02-Q1 contains a digital decimation filter that demodulates the output of the  $\Delta \Sigma$  modulators. The filter enables data rates as high as 32 kSPS per channel in high-resolution mode. The relative phase of the samples can be configured between channels, thus enabling an accurate compensation for the sensor phase response. Offset and gain calibration registers can be programmed to automatically adjust output samples for measured offset and gain errors. The *Functional Block Diagram* provides a detailed diagram of the ADS131M02-Q1.

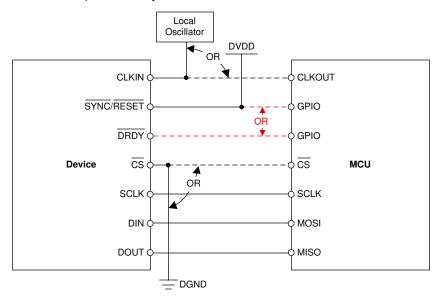

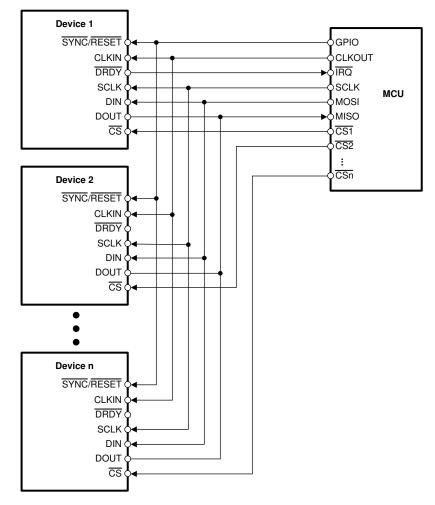

The device communicates via a serial programming interface (SPI)-compatible interface. Several SPI commands and internal registers control the operation of the ADS131M02-Q1. Other devices can be added to the same SPI bus by adding discrete  $\overline{CS}$  control lines. The  $\overline{SYNC}/\overline{RESET}$  pin can be used to synchronize conversions between multiple ADS131M02-Q1 devices as well as to maintain synchronization with external events.

## 8.2 Functional Block Diagram

# 8.3 Feature Description

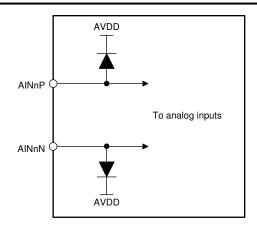

## 8.3.1 Input ESD Protection Circuitry

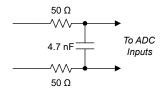

Basic electrostatic discharge (ESD) circuitry protects the ADS131M02-Q1 inputs from ESD and overvoltage events in conjunction with external circuits and assemblies. 🛛 8-1 depicts a simplified representation of the ESD circuit. The protection for input voltages exceeding AVDD can be modeled as a simple diode.

## 图 8-1. Input ESD Protection Circuitry

The ADS131M02-Q1 has an integrated negative charge pump that allows for input voltages below AGND with a unipolar supply. Consequently, shunt diodes between the inputs and AGND cannot be used to clamp excessive negative input voltages. Instead, the same diode that clamps overvoltage is used to clamp undervoltage at the reverse breakdown voltage. Take care to prevent input voltages or currents from exceeding the limits provided in the *Absolute Maximum Ratings* table.

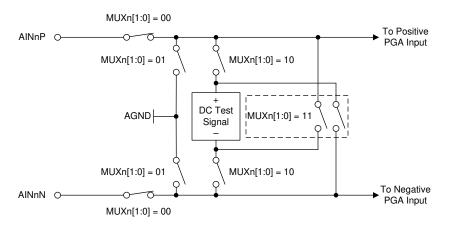

#### 8.3.2 Input Multiplexer

Each channel of the ADS131M02-Q1 has a dedicated input multiplexer. The multiplexer controls which signals are routed to the ADC channels. Configure the input multiplexer using the MUXn[1:0] bits in the CHn\_CFG register. The input multiplexer allows the following inputs to be connected to the ADC channel:

- The analog input pins corresponding to the given channel

- AGND, which is helpful for offset calibration

- Positive DC test signal

- Negative DC test signal

See the *Internal Test Signals* section for more information about the test signals. 图 8-2 shows a diagram of the input multiplexer on the ADS131M02-Q1.

## 图 8-2. Input Multiplexer

## 8.3.3 Programmable Gain Amplifier (PGA)

Each channel of the ADS131M02-Q1 features an integrated programmable gain amplifier (PGA) that provides gains of 1, 2, 4, 8, 16, 32, 64, and 128. The gains for all channels are individually controlled by the PGAGAINn bits for each channel in the GAIN1 register.

#### Copyright © 2022 Texas Instruments Incorporated

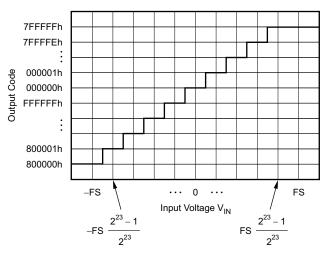

$FSR = \pm 1.2 V / Gain$

表 8-1 shows the corresponding full-scale ranges for each gain setting.

1

2

4

8

16

32

64

128

without accounting for gain error caused by tolerance in the reference voltage.

| The input impedance of the PGA dominates the input impedance characteristics of the ADS131M02-Q1. The  |

|--------------------------------------------------------------------------------------------------------|

| PGA input impedance for gain settings up to 4 behaves according to 方程式 4 without accounting for device |

| tolerance and change over temperature. Minimize the output impedance of the circuit that drives the    |

| ADS131M02-Q1 inputs to obtain the best possible gain error, INL, and distortion performance.           |

where:

-  $f_{MOD}$  is the  $\,\Delta\,\Sigma\,$  modulator frequency, f\_{CLKIN} / 2

The device uses an input precharge buffer for PGA gain settings of 8 and higher. The input impedance at these gain settings is very high. Specifying the input bias current for these gain settings is therefore more useful. A plot of input bias current for the high gain settings is provided in  $\mathbb{E}$  6-5.

## 8.3.4 Voltage Reference

The ADS131M02-Q1 uses an internally generated, low-drift, band-gap voltage to supply the reference for the ADC. The reference has a nominal voltage of 1.2 V, allowing the differential input voltage to swing from -1.2 V to 1.2 V. The reference circuitry starts up very quickly to accommodate the fast start-up feature of this device. The device waits until after the reference circuitry is fully settled before generating conversion data.

## 8.3.5 Clocking and Power Modes

An LVCMOS clock must be provided at the CLKIN pin continuously when the ADS131M02-Q1 is running in normal operation. The frequency of the clock can be scaled in conjunction with the power mode to provide a tradeoff between power consumption and dynamic range.

The PWR[1:0] bits in the CLOCK register allow the device to be configured in one of three power modes: high-resolution (HR) mode, low-power (LP) mode, and very low-power (VLP) mode. Changing the PWR[1:0] bits scales the internal bias currents to achieve the expected power levels. The external clock frequency must follow the guidance provided in the *Recommended Operating Conditions* table corresponding to the intended power mode in order for the device to perform according to the specification.

## 8.3.6 $\Delta \Sigma$ Modulator

The ADS131M02-Q1 uses a delta-sigma ( $\Delta \Sigma$ ) modulator to convert the analog input voltage to a one's density modulated digital bit-stream. The  $\Delta \Sigma$  modulator oversamples the input voltage at a frequency many times

| 表 8-1. Full-\$ | Scale Range |

|----------------|-------------|

| GAIN SETTING   | FSR         |

±1.2 V

±600 mV

+300 mV

±150 mV

±75 mV

±37.5 mV

±18.75 mV

±9.375 mV

Varying the PGA gain scales the differential full-scale input voltage range (FSR) of the ADC. 方程式 3 describes the relationship between FSR and gain. 方程式 3 uses the internal reference voltage, 1.2 V, as the scaling factor

(4)

Copyright © 2022 Texas Instruments Incorporated

greater than the output data rate. The modulator frequency,  $f_{MOD}$ , of the ADS131M02-Q1 is equal to half the controller clock frequency, that is,  $f_{MOD} = f_{CLKIN} / 2$ .

The output of the modulator is fed back to the modulator input through a digital-to-analog converter (DAC) as a means of error correction. This feedback mechanism shapes the modulator quantization noise in the frequency domain to make the noise more dense at higher frequencies and less dense in the band of interest. The digital decimation filter following the  $\Delta \Sigma$  modulator significantly attenuates the out-of-band modulator quantization noise, allowing the device to provide excellent dynamic range.

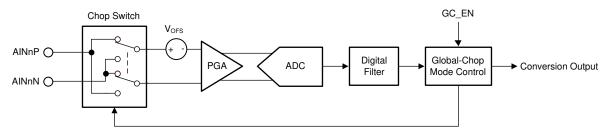

#### 8.3.7 Digital Filter

The  $\Delta \Sigma$  modulator bitstream feeds into a digital filter. The digital filter is a linear phase, finite impulse response (FIR), low-pass sinc-type filter that attenuates the out-of-band quantization noise of the  $\Delta \Sigma$  modulator. The digital filter demodulates the output of the  $\Delta \Sigma$  modulator by averaging. The data passing through the filter is decimated and downsampled, to reduce the rate at which data come out of the modulator (f<sub>MOD</sub>) to the output data rate (f<sub>DATA</sub>). The decimation factor is defined as per  $\overline{\beta}$  #式 5 and is called the *oversampling ratio (OSR*).

$OSR = f_{MOD} / f_{DATA}$

(5)

The OSR is configurable and set by the OSR[2:0] bits in the CLOCK register. In addition, the TBM bit in the CLOCK registers can be used to enable an even lower OSR setting of 64 for highest speed application. There are nine OSR settings in the ADS131M02-Q1, allowing nine different data rate settings for any given controller clock frequency.  $\frac{1}{2}$  8-2 lists the OSR settings and their corresponding output data rates for the nominal CLKIN frequencies mentioned.

The OSR determines the amount of averaging of the modulator output in the digital filter and therefore also the filter bandwidth. The filter bandwidth directly affects the noise performance of the ADC because lower bandwidth results in lower noise whereas higher bandwidth results in higher noise. See  $\gtrsim$  7-1 for the noise specifications for various OSR settings.

ADS131M02-Q1 ZHCSOL6 - AUGUST 2022

# . .

| 表 8-2. OSR Settings and Data Rates for Nominal Controller Clock Frequencies |                                       |                  |       |                  |  |  |  |

|-----------------------------------------------------------------------------|---------------------------------------|------------------|-------|------------------|--|--|--|

| OWER MODE                                                                   | NOMINAL CONTROLLER<br>CLOCK FREQUENCY | f <sub>MOD</sub> | OSR   | OUTPUT DATA RATE |  |  |  |

|                                                                             |                                       |                  | 64    | 64 kSPS          |  |  |  |

|                                                                             |                                       |                  | 128   | 32 kSPS          |  |  |  |

|                                                                             |                                       |                  | 256   | 16 kSPS          |  |  |  |

|                                                                             |                                       |                  | 512   | 8 kSPS           |  |  |  |

| HR                                                                          | 8.192 MHz                             | 4.096 MHz        | 1024  | 4 kSPS           |  |  |  |

|                                                                             |                                       |                  | 2048  | 2 kSPS           |  |  |  |

|                                                                             |                                       |                  | 4096  | 1 kSPS           |  |  |  |

|                                                                             |                                       |                  | 8192  | 500 SPS          |  |  |  |

|                                                                             |                                       |                  | 16384 | 250 SPS          |  |  |  |

|                                                                             | 4.096 MHz                             | 2.048 MHz        | 64    | 32 kSPS          |  |  |  |

|                                                                             |                                       |                  | 128   | 16 kSPS          |  |  |  |

|                                                                             |                                       |                  | 256   | 8 kSPS           |  |  |  |

|                                                                             |                                       |                  | 512   | 4 kSPS           |  |  |  |

| LP                                                                          |                                       |                  | 1024  | 2 kSPS           |  |  |  |

|                                                                             |                                       |                  | 2048  | 1 kSPS           |  |  |  |

|                                                                             |                                       |                  | 4096  | 500 SPS          |  |  |  |

|                                                                             |                                       |                  | 8192  | 250 SPS          |  |  |  |

|                                                                             |                                       |                  | 16384 | 125 SPS          |  |  |  |

|                                                                             |                                       |                  | 64    | 16 kSPS          |  |  |  |

|                                                                             |                                       |                  | 128   | 8 kSPS           |  |  |  |

|                                                                             |                                       |                  | 256   | 4 kSPS           |  |  |  |

|                                                                             |                                       |                  | 512   | 2 kSPS           |  |  |  |

| VLP                                                                         | 2.048 MHz                             | 1.024 MHz        | 1024  | 1 kSPS           |  |  |  |

|                                                                             |                                       |                  | 2048  | 500 SPS          |  |  |  |

|                                                                             |                                       |                  | 4096  | 250 SPS          |  |  |  |

|                                                                             |                                       |                  | 8192  | 125 SPS          |  |  |  |

|                                                                             |                                       |                  | 16384 | 62.5 SPS         |  |  |  |

|                                                                             |                                       |                  |       |                  |  |  |  |

## 8.3.7.1 Digital Filter Implementation

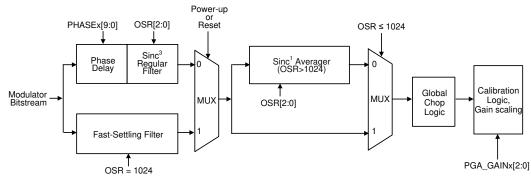

8-3 shows the digital filter implementation of the ADS131M02-Q1. The modulator bit-stream feeds two parallel filter paths, a sinc<sup>3</sup> filter, and a fast-settling filter path.

#### 8.3.7.1.1 Fast-Settling Filter

At power-up or after a device reset, the ADS131M02-Q1 selects the fast-settling filter to allow for settled output data generation with minimal latency. The fast-settling filter has the characteristic of a first-order sinc filter (sinc<sup>1</sup>). After two conversions, the device switches to and remains in the sinc<sup>3</sup> filter path until the next time the device is reset or powered cycled.

The fast-settling filter exhibits wider bandwidth and less stop-band attenuation than the sinc<sup>3</sup> filter. Consequently, the noise performance when using the fast-settling filter is not as high as with the sinc<sup>3</sup> filter. The first two samples available from the ADS131M02-Q1 after a supply ramp or reset have the noise performance and frequency response corresponding to the fast-settling filter as specified in the *Electrical Characteristics* table in the *Specifications* section, whereas subsequent samples have the noise performance and frequency response consistent with the sinc<sup>3</sup> filter. See the *Fast Start-Up Behavior* section for more details regarding the fast start-up capabilities of the ADS131M02-Q1.

#### 8.3.7.1.2 SINC<sup>3</sup> and SINC<sup>3</sup> + SINC<sup>1</sup> Filter

The ADS131M02-Q1 selects the sinc<sup>3</sup> filter path two conversion after power-up or device reset. For OSR settings of 64 to 1024 the sinc<sup>3</sup> filter output directly feeds into the global-chop and calibration logic. For OSR settings of 2048 and higher the sinc<sup>3</sup> filter is followed by a sinc<sup>1</sup> filter. As shown in  $\mathbb{R}$  8-3, the sinc<sup>3</sup> filter operates at a fixed OSR of 1024 in this case while the sinc<sup>1</sup> filter implements the additional OSRs of 2 to 16. That means when an OSR of 4096 (for example) is selected, the sinc<sup>3</sup> filter operates at an OSR of 1024 and the sinc<sup>1</sup> filter at an OSR of 4.

The filter has infinite attenuation at integer multiples of the data rate except for integer multiples of  $f_{MOD}$ . Like all digital filters, the digital filter response of the ADS131M02-Q1 repeats at integer multiples of the modulator frequency,  $f_{MOD}$ . The data rate and filter notch frequencies scale with  $f_{MOD}$ .

When possible, plan frequencies for unrelated periodic processes in the application for integer multiples of the data rate such that any parasitic effect they have on data acquisition is effectively canceled by the notches of the digital filter. Avoid frequencies near integer multiples of  $f_{MOD}$  whenever possible because tones in these bands can alias to the band of interest.

The sinc<sup>3</sup> and sinc<sup>3</sup> + sinc<sup>1</sup> filters for a given channel require time to settle after a channel is enabled, the channel multiplexer or gain setting is changed, or a resynchronization event occurs. See the *Synchronization* section for more details on resynchronization.  $\overline{\mathcal{R}}$  8-3 lists the settling times of the sinc<sup>3</sup> and sinc<sup>3</sup> + sinc<sup>1</sup> filters for each OSR setting. The ADS131M02-Q1 does not gate unsettled data. Therefore, the host must account for the filter settling time and disregard unsettled data if any are read. The data at the next DRDY falling edge after the filter settling time listed in  $\overline{\mathcal{R}}$  8-3 has expired can be considered fully settled.

| OSR (OVERALL) | OSR (SINC <sup>3</sup> ) | OSR (SINC <sup>1</sup> ) | SETTLING TIME (t <sub>CLKIN</sub> ) |

|---------------|--------------------------|--------------------------|-------------------------------------|

| 64            | 64                       | N/A                      | 728                                 |

| 128           | 128                      | N/A                      | 856                                 |

| 256           | 256                      | N/A                      | 1112                                |

| 512           | 512                      | N/A                      | 1624                                |

| 1024          | 1024                     | N/A                      | 2648                                |

| 2048          | 1024                     | 2                        | 4696                                |

| 4096          | 1024                     | 4                        | 8792                                |

| 8192          | 1024                     | 8                        | 16984                               |

| 16384         | 1024                     | 16                       | 33368                               |

表 8-3. Digital Filter Start-Up Times After Power-Up or Resynchronization

## 8.3.7.2 Digital Filter Characteristic

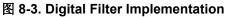

方程式 6 calculates the z-domain transfer function of a sinc<sup>3</sup> filter that is used for OSRs of 1024 and lower.

$$\left|H(z)\right| = \left|\frac{1 - Z^{-N}}{N(1 - Z^{-1})}\right|^{3}$$

(6)

where N is the OSR.

方程式 7 calculates the transfer function of a sinc<sup>3</sup> filter in terms of the continuous-time frequency parameter *f*.

$$H(f) \mid = \left| \frac{\sin\left(\frac{N\pi f}{f_{MOD}}\right)}{N \times \sin\left(\frac{\pi f}{f_{MOD}}\right)} \right|^{3}$$

(7)

where N is the OSR.

8 - 4 and 8 - 5 show the digital filter response of the fast-settling filter and the sinc<sup>3</sup> filter for OSRs of 1024 and lower. 8 - 6 and 8 - 7 show the digital filter response of the sinc<sup>3</sup> + sinc<sup>1</sup> filter for an OSR of 4096.

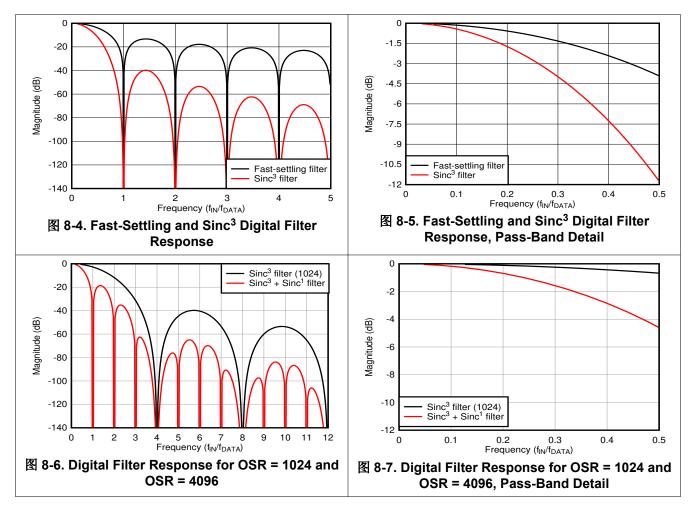

#### 8.3.8 DC Block Filter

The ADS131M02-Q1 includes an optional high-pass filter to eliminate any systematic offset or low-frequency noise. The filter is enabled by writing any value in the DCBLOCK[3:0] bits in the CD\_TH\_LSB register besides 0h. The DC block filter can be enabled and disabled on a channel-by-channel basis by the DCBLKn\_DIS bit in the CHn\_CFG register for each respective channel.

图 8-8 shows the topology of the DC block filter. Coefficient *a* represents a register configurable value that configures the cutoff frequency of the filter. The cutoff frequency is configured using the DCBLOCK[3:0] bits in the CD\_TH\_LSB register. 表 8-4 describes the characteristics of the filter for various DCBLOCK[3:0] settings. The data provided in 表 8-4 is provided for an 8.192-MHz CLKIN frequency and a 4-kSPS data rate. The frequency response of the filter response scales directly with the frequency of CLKIN and the data rate.

图 8-8. DC Block Filter Topology

|              |               | - 3-dB                | PASS-BAND ATTENUATION <sup>(1)</sup> |                   | SETTLING TI  | ME (Samples)  |

|--------------|---------------|-----------------------|--------------------------------------|-------------------|--------------|---------------|

| DCBLOCK[3:0] | a COEFFICIENT | CORNER <sup>(1)</sup> | 50 Hz                                | 60 Hz             | SETTLED >99% | FULLY SETTLED |

| 0h           |               |                       | DC bloc                              | k filter disabled |              |               |

| 1h           | 1/4           | 181 Hz                | 11.5 dB                              | 10.1 dB           | 17           | 88            |

| 2h           | 1/8           | 84.8 Hz               | 5.89 dB                              | 4.77 dB           | 36           | 187           |

| 3h           | 1/16          | 41.1 Hz               | 2.24 dB                              | 1.67 dB           | 72           | 387           |

| 4h           | 1/32          | 20.2 Hz               | 657 mdB                              | 466 mdB           | 146          | 786           |

| 5h           | 1/64          | 10.0 Hz               | 171 mdB                              | 119 mdB           | 293          | 1585          |

| 6h           | 1/128         | 4.99 Hz               | 43.1 mdB                             | 29.9 mdB          | 588          | 3182          |

| 7h           | 1/256         | 2.49 Hz               | 10.8 mdB                             | 7.47 mdB          | 1178         | 6376          |

| 8h           | 1/512         | 1.24 Hz               | 2.69 mdB                             | 1.87 mdB          | 2357         | 12764         |

| 9h           | 1/1024        | 622 mHz               | 671 µdB                              | 466 µdB           | 4714         | 25540         |

| Ah           | 1/2048        | 311 mHz               | 168 µdB                              | 116 µdB           | 9430         | 51093         |

| Bh           | 1/4096        | 155 mHz               | 41.9 µdB                             | 29.1 µdB          | 18861        | 102202        |

| Ch           | 1/8192        | 77.7 mHz              | 10.5 µdB                             | 7.27 µdB          | 37724        | 204447        |

| Dh           | 1/16384       | 38.9 mHz              | 2.63 µdB                             | 1.82 µdB          | 75450        | 409156        |

| Eh           | 1/32768       | 19.4 mHz              | 655 ndB                              | 455 ndB           | 150901       | 820188        |

| Fh           | 1/65536       | 9.70 mHz              | 164 ndB                              | 114 ndB           | 301803       | 1627730       |

#### 表 8-4. DC Block Filter Characteristics

(1) Values given are for a 4-kSPS data rate with a 8.192-MHz CLKIN frequency.

## 8.3.9 Internal Test Signals

The ADS131M02-Q1 features an internal analog test signal that is useful for troubleshooting and diagnosis. A positive or negative DC test signal can be applied to the channel inputs through the input multiplexer. The multiplexer is controlled through the MUXn[1:0] bits in the CHn\_CFG register. The test signals are created by internally dividing the internal reference voltage. The same signal is shared by all channels.

The test signal is nominally 2 / 15 ×  $V_{REF}$ . The test signal automatically adjusts the voltage level with the gain setting such that the ADC always measures a signal that is 2 / 15 ×  $V_{Diff Max}$ . For example, at a gain of 1, this voltage equates to 160 mV. At a gain of 2, this voltage is 80 mV.

#### 8.3.10 Channel Phase Calibration

The ADS131M02-Q1 allows fine adjustment of the sample phase between channels through the use of channel phase calibration. This feature is helpful when different channels are measuring the outputs of different types of sensors that have different phase responses. For example, in power metrology applications, voltage can be measured by a voltage divider, whereas current is measured using a current transformer that exhibits a phase difference between the input and output signals. The differences in phase between the voltage and current measurement must be compensated to measure the power and related parameters accurately.

The phase setting of the different channels is configured by the PHASEn[9:0] bits in the CHn\_CFG register corresponding to the channel whose phase adjustment is desired. The register value is a 10-bit two's complement value corresponding to the number of modulator clock cycles of phase offset compared to a reference phase of 0 degrees.

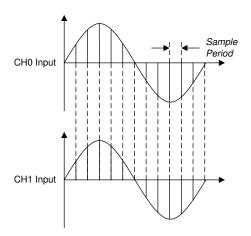

The mechanism for achieving phase adjustment derives from the  $\Delta \Sigma$  architecture. The  $\Delta \Sigma$  modulator produces samples continuously at the modulator frequency,  $f_{MOD}$ . These samples are filtered and decimated to the output data rate by the digital filter. The ratio between  $f_{MOD}$  and the data rate is the oversampling ratio (OSR). Each conversion result corresponds to an OSR number of modulator samples provided to the digital filter. When the different channels of the ADS131M02-Q1 have no programmed phase offset between them, the modulator clock cycles corresponding to the conversion results of the different channels are aligned in the time domain. 🕅 8-9 depicts an example scenario where the voltage input to channel 1 has no phase offset from channel 0.

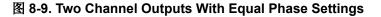

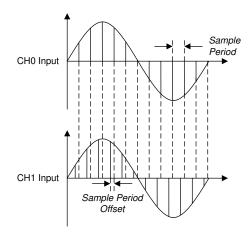

However, the sample period of one channel can be shifted with respect to another. If the inputs to both channels are sinusoids of the same frequency and the samples for these channels are retrieved by the host at the same time, the effect is that the phase of the channel with the modified sample period appears *shifted*.  $\boxtimes$  8-10 depicts how the period corresponding to the samples are shifted between channels.  $\boxtimes$  8-11 illustrates how the samples appear as having generated a phase shift when they are retrieved by the host.

## 图 8-10. Channel 1 With a Positive Sample Phase Shift With Respect to Channel 0

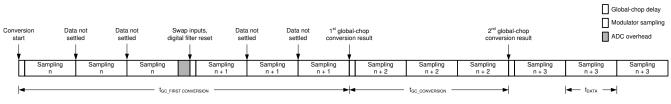

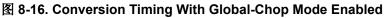

#### 图 8-11. Channels 1 and 0 From the Perspective of the Host