**ADC3664** ZHCSMZ6B - DECEMBER 2020 - REVISED JULY 2022

# ADC3664 14 位、125MSPS、低噪声、低功率双通道 ADC

# 1 特性

• 14 位 125MSPS ADC

本底噪声:-156.9dBFS/Hz

• 低功耗: 100mW/ch • 延迟:2个时钟周期

• 电压基准:

- 外部:65MSPS 至 125MSPS - 内部: 100MSPS 至 125MSPS

• 保证 14 位. 无丢码

输入带宽: 1.4GHz (3dB)

INL: ±2.6LSB; DNL: ±0.9LSB

• 工业温度范围: -40°C 至 +105°C

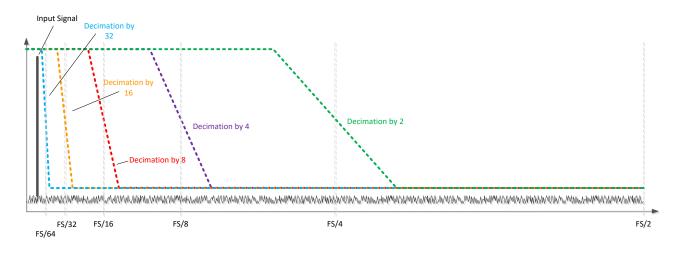

片上数字滤波器(可选)

- 2 倍、4 倍、8 倍、16 倍、32 倍抽取率

- 32 位 NCO

• 串行 LVDS 数字接口(2线、1线和1/2线)

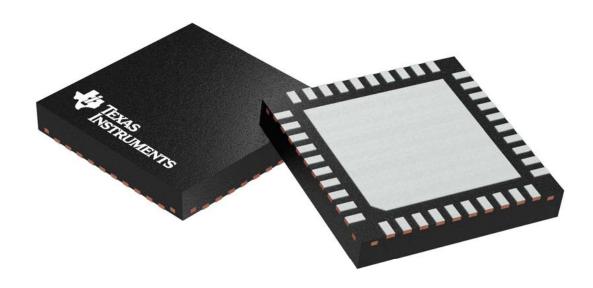

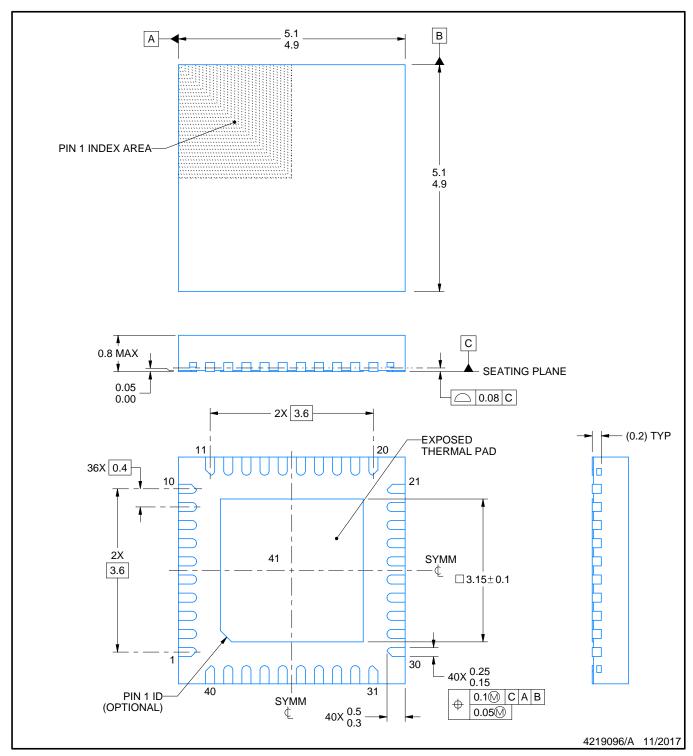

• 小尺寸: 40 引脚 VQFN (5mm × 5mm) 封装

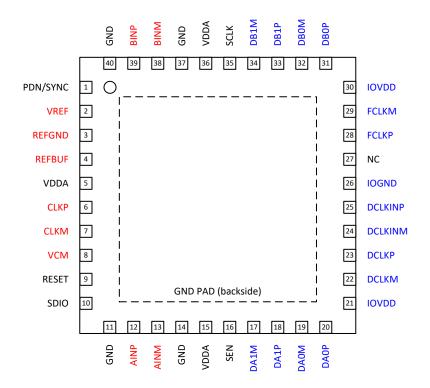

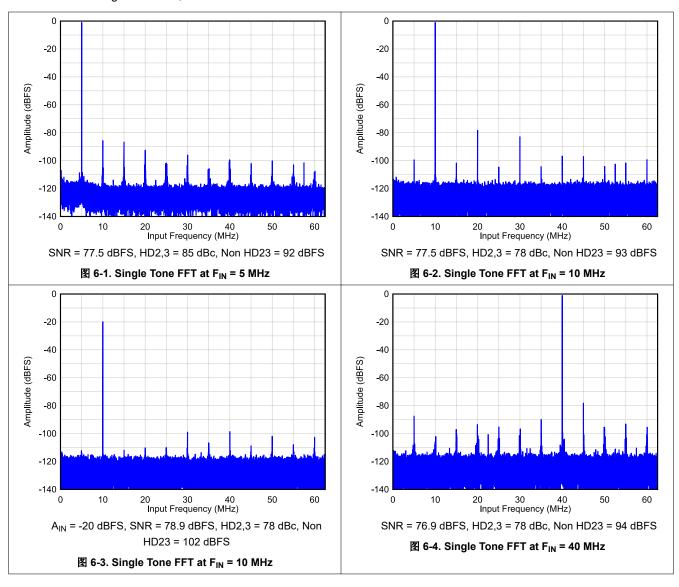

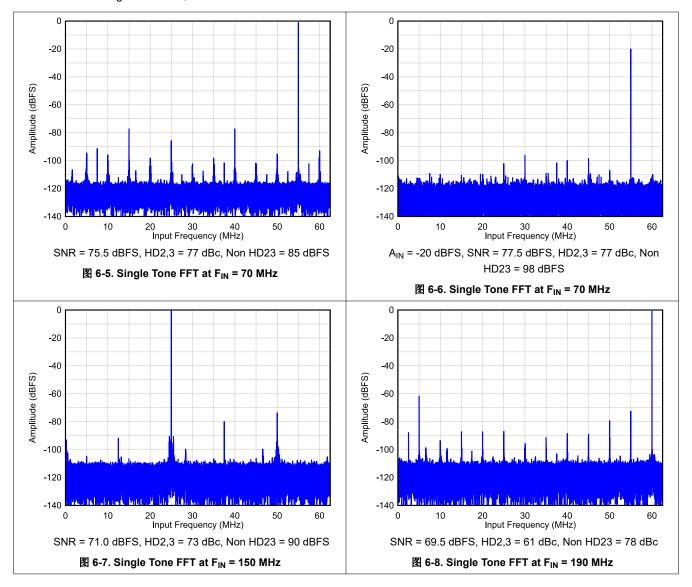

• 频谱性能 (f<sub>IN</sub> = 5MHz):

- SNR: 77.5dBFS

- SFDR: 84dBc HD2 \ HD3 - SFDR: 92dBFS 最严重毛刺

频谱性能 (f<sub>IN</sub> = 70MHz):

- SNR: 75.5dBFS

SFDR: 76dBc HD2、HD3 - SFDR:84dBFS 最严重毛刺

### 2 应用

- 高速数据采集

- 软件定义无线电

- 通信基础设施

- 频谱分析仪

- OTDR

- 控制环路

- 源测量单元 (SMU)

- 仪表

- 光谱分析

- 雷达

### 3 说明

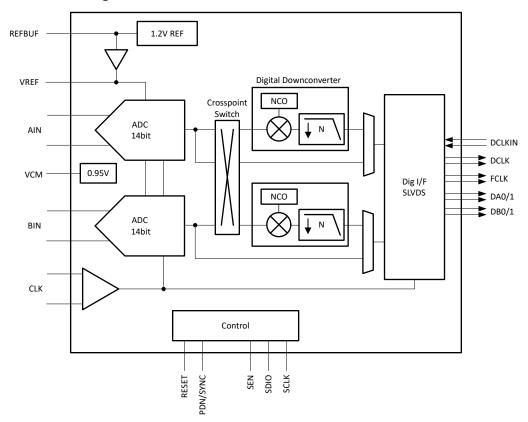

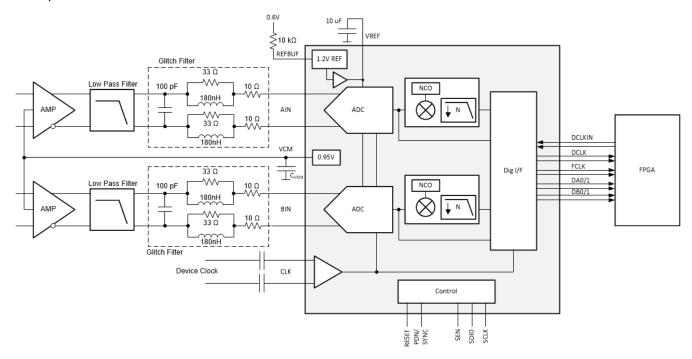

ADC3664 器件是一款低噪声、超低功耗、14 位、 125MSPS 高速双通道 ADC。该器件可实现超低噪声 性能和 -156.9dBFS/Hz 的噪声频谱密度,还具有出色 的线性度和动态范围。ADC3664 可提供中频采样支 持,使器件适合各种应用。高速控制环路受益于低至一 个时钟周期的低延迟。该 ADC 在 125MSPS 下的功耗 仅为每通道 100mW, 其功耗随采样率减小而迅速降

ADC3664 使用串行 LVDS (SLVDS) 接口输出数据,可 更大限度减少数字互连的次数。该器件提供双通道、单 通道和半通道选项。ADC3664 与 16 位分辨率 ADC 系 列实现了引脚对引脚兼容。该器件支持 - 40°C 至 +105℃ 的工业级工作温度范围。

#### 封装信息

| 器件型号    | 封装 <sup>(1)</sup> | 封装尺寸(标称值)     |  |  |

|---------|-------------------|---------------|--|--|

| ADC3664 | VQFN (40)         | 5.00 × 5.00mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

表 3-1. 器件比较

| 器件型号    | 分辨率  | 采样率     |

|---------|------|---------|

| ADC3661 | 16 位 | 10MSPS  |

| ADC3662 | 16 位 | 25MSPS  |

| ADC3663 | 16 位 | 65MSPS  |

| ADC3664 | 14 位 | 125MSPS |

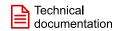

简化版方框图

# **Table of Contents**

| 1 特性1                                               | 8.2 Functional Block Diagram            | 20               |

|-----------------------------------------------------|-----------------------------------------|------------------|

| 2 应用1                                               | 8.3 Feature Description                 |                  |

| 3 说明                                                | 8.4 Device Functional Modes             |                  |

| 4 Revision History 2                                | 8.5 Programming                         |                  |

| 5 Pin Configuration and Functions                   | 8.6 Register Maps                       |                  |

| 6 Specifications5                                   | 9 Application Information Disclaimer    | 58               |

| 6.1 Absolute Maximum Ratings                        | 9.1 Typical Application                 |                  |

| 6.2 ESD Ratings                                     | 9.2 Initialization Set Up               |                  |

| 6.3 Recommended Operating Conditions                | 9.3 Power Supply Recommendations        |                  |

| 6.4 Thermal Information                             | 9.4 Layout                              |                  |

| 6.5 Electrical Characteristics - Power Consumption6 | 10 Device and Documentation Support     |                  |

| 6.6 Electrical Characteristics - DC Specifications  | 10.1 接收文档更新通知                           | 6 <mark>5</mark> |

| 6.7 Electrical Characteristics - AC Specifications9 | 10.2 支持资源                               |                  |

| 6.8 Timing Requirements                             | 10.3 Trademarks                         |                  |

| 6.9 Typical Characteristics                         | 10.4 Electrostatic Discharge Caution    | 65               |

| 7 Parameter Measurement Information                 | 10.5 术语表                                |                  |

| 8 Detailed Description                              | 11 Mechanical, Packaging, and Orderable |                  |

| 8.1 Overview                                        | Information                             | 65               |

|                                                     |                                         |                  |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision A (August 2021) to Revision B (July 2022)                      | Page |

|---|-------------------------------------------------------------------------------------|------|

| • | Changed the output clock jitter unit from ps to ps pk-pk in the Timing Requirements | 10   |

| • | Added GND symbol to REFGND pin for all voltage reference option diagrams            | 25   |

| • | Added the section Output Bit Mapper                                                 | 37   |

|   | Added default power up configuration summary                                        |      |

|   | Updated power-up initialization diagram with correct indexing                       |      |

| С | hanges from Revision * (December 2020) to Revision A (August 2021)                  | Page |

| • | All wake up time values moved from MAX to NOM                                       | 10   |

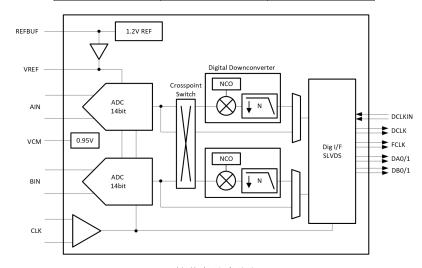

# **5 Pin Configuration and Functions**

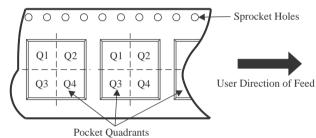

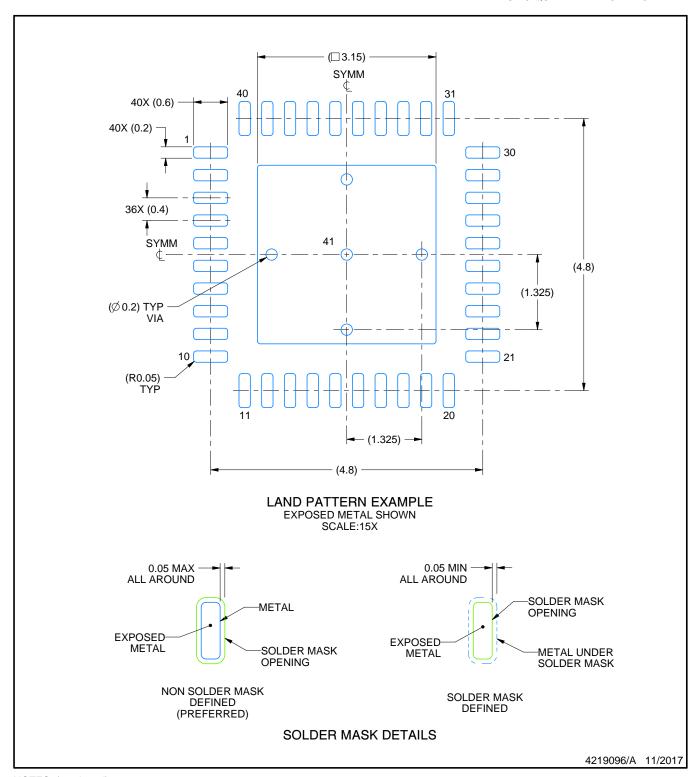

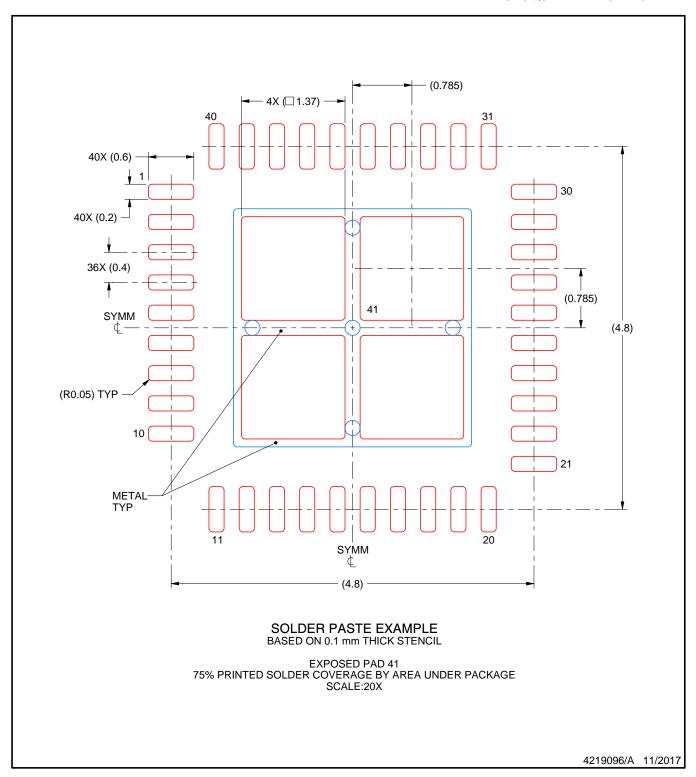

图 5-1. RSB (WQFN) Package, 40-Pin (Top View)

表 5-1. Pin Descriptions

| P           | PIN I/O |     | DESCRIPTION                                                                                                                                                                                       |  |  |

|-------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.     | 1/0 | DESCRIPTION                                                                                                                                                                                       |  |  |

| INPUT/REFER | RENCE   |     |                                                                                                                                                                                                   |  |  |

| AINM        | 13      | I   | Negative analog input, channel A                                                                                                                                                                  |  |  |

| AINP        | 12      | 1   | Positive analog input, channel A                                                                                                                                                                  |  |  |

| BINP        | 39      | 1   | Positive analog input, channel B                                                                                                                                                                  |  |  |

| BINM        | 38      | I   | Negative analog input, channel B                                                                                                                                                                  |  |  |

| REFBUF      | 4       | I   | 1.2 V external voltage reference input for use with internal reference buffer. Internal 100 k $\Omega$ pull-up resistor to AVDD. This pin is also used to configure default operating conditions. |  |  |

| REFGND      | 3       | I   | Reference ground input, 0 V                                                                                                                                                                       |  |  |

| VCM         | 8       | 0   | Common-mode voltage output for the analog inputs, 0.95V                                                                                                                                           |  |  |

| VREF        | 2       | I   | External voltage reference input                                                                                                                                                                  |  |  |

| CLOCK       |         |     |                                                                                                                                                                                                   |  |  |

| CLKM        | 7       | I   | Negative differential sampling clock input for the ADC                                                                                                                                            |  |  |

| CLKP        | 6       | I   | Positive differential sampling clock input for the ADC                                                                                                                                            |  |  |

| CONFIGURAT  | TION    | •   |                                                                                                                                                                                                   |  |  |

| PDN/SYNC    | 1       | I   | Power down/Synchronization input. This pin can be configured via the SPI interface. Active high. This pin has an internal 21 k $\Omega$ pull-down resistor.                                       |  |  |

### 表 5-1. Pin Descriptions (continued)

| ı            | PIN                      | I/O | DESCRIPTION                                                                                           |  |  |

|--------------|--------------------------|-----|-------------------------------------------------------------------------------------------------------|--|--|

| NAME         | NO.                      | 1/0 | DESCRIPTION                                                                                           |  |  |

| RESET        | 9                        | I   | Hardware reset. Active high. This pin has an internal 21 k Ω pull-down resistor.                      |  |  |

| SCLK         | 35                       | I   | Serial interface clock input. This pin has an internal 21 k Ω pull-down resistor.                     |  |  |

| SDIO         | 10                       | I   | Serial interface data input and output. This pin has an internal 21 k $\Omega$ pull-down resistor.    |  |  |

| SEN          | 16                       | I   | Serial interface enable. Active low. This pin has an internal 21 k $\Omega$ pull-up resistor to AVDD. |  |  |

| NC           | 27                       | -   | Do not connect                                                                                        |  |  |

| DIGITAL INTE | ERFACE                   |     |                                                                                                       |  |  |

| DA0P         | 20                       | 0   | Positive differential serial LVDS output for lane 0, channel A.                                       |  |  |

| DA0M         | 19                       | 0   | Negative differential serial LVDS output for lane 0, channel A.                                       |  |  |

| DA1P         | 18                       | 0   | Positive differential serial LVDS output for lane 1, channel A.                                       |  |  |

| DA1M         | 17                       | 0   | Negative differential serial LVDS output for lane 1, channel A.                                       |  |  |

| DB0P         | 31                       | 0   | Positive differential serial LVDS output for lane 0, channel B.                                       |  |  |

| DB0M         | 32                       | 0   | Negative differential serial LVDS output for lane 0, channel B.                                       |  |  |

| DB1P         | 33                       | 0   | Positive differential serial LVDS output for lane 1, channel B.                                       |  |  |

| DB1M         | 34                       | 0   | Negative differential serial LVDS output for lane 1, channel B.                                       |  |  |

| DCLKP        | 23                       | 0   | Positive differential serial LVDS bit clock output.                                                   |  |  |

| DCLKM        | 22                       | 0   | Negative differential serial LVDS bit clock output.                                                   |  |  |

| FCLKP        | 28                       | 0   | Positive differential serial LVDS frame clock output.                                                 |  |  |

| FCLKM        | 29                       | 0   | Negative differential serial LVDS frame clock output.                                                 |  |  |

| DCLKINP      | 25                       | I   | Positive differential serial LVDS bit clock input. Internal 100 $\Omega$ differential termination.    |  |  |

| DCLKINM      | 24                       | I   | Negative differential serial LVDS bit clock input. Internal 100 $^{\Omega}$ differential termination. |  |  |

| POWER SUP    | PLY                      |     |                                                                                                       |  |  |

| AVDD         | 5,15,36                  | I   | Analog 1.8-V power supply                                                                             |  |  |

| GND          | 11,14,37,40,<br>PowerPAD | I   | Ground, 0 V                                                                                           |  |  |

| IOGND        | 26                       | I   | Ground, 0 V for digital interface                                                                     |  |  |

| IOVDD        | 21,30                    | I   | 1.8-V power supply for digital interface                                                              |  |  |

### **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| PARAMETER                                | TEST CONDITIONS                                 | MIN   | MAX | UNIT |

|------------------------------------------|-------------------------------------------------|-------|-----|------|

| Supply voltage rang                      | Supply voltage range, AVDD, IOVDD               |       | 2.1 | V    |

| Supply voltage range, GND, IOGND, REFGND |                                                 | - 0.3 | 0.3 | V    |

| Voltage applied to                       | AINP/M, BINP/M, CLKP/M, DCLKINP/M, VREF, REFBUF | - 0.3 | 2.1 | V    |

| input pins                               | PDN/SYNC, RESET, SCLK, SEN, SDIO                | - 0.3 | 2.1 |      |

| lunction temperature, T <sub>J</sub>     |                                                 |       | 105 | °C   |

| Storage temperatur                       | re, T <sub>stg</sub>                            | - 65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |               |                                                                                          | VALUE | UNIT |

|--------------------|---------------|------------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | 2500  |      |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | 1000  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX                | UNIT |

|----------------|--------------------------------|------|-----|--------------------|------|

| Supply         | AVDD <sup>(1)</sup>            | 1.75 | 1.8 | 1.85               | V    |

| voltage range  | IOVDD <sup>(1)</sup>           | 1.75 | 1.8 | 1.85               | V    |

| T <sub>A</sub> | Operating free-air temperature | - 40 |     | 105                | °C   |

| T <sub>J</sub> | Operating junction temperature |      |     | 105 <sup>(2)</sup> | °C   |

<sup>(1)</sup> Measured to GND.

#### 6.4 Thermal Information

|                        |                                              | ADC3664   |      |

|------------------------|----------------------------------------------|-----------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RSB (QFN) | UNIT |

|                        |                                              | 40 Pins   |      |

| R⊕JA                   | Junction-to-ambient thermal resistance       | 30.7      | °C/W |

| R <sub>⊕</sub> JC(top) | Junction-to-case (top) thermal resistance    | 16.4      | °C/W |

| R⊕JB                   | Junction-to-board thermal resistance         | 10.5      | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.2       | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 10.5      | °C/W |

| R <sub>⊕ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Prolonged use above this junction temperature may increase the device failure-in-time (FIT) rate.

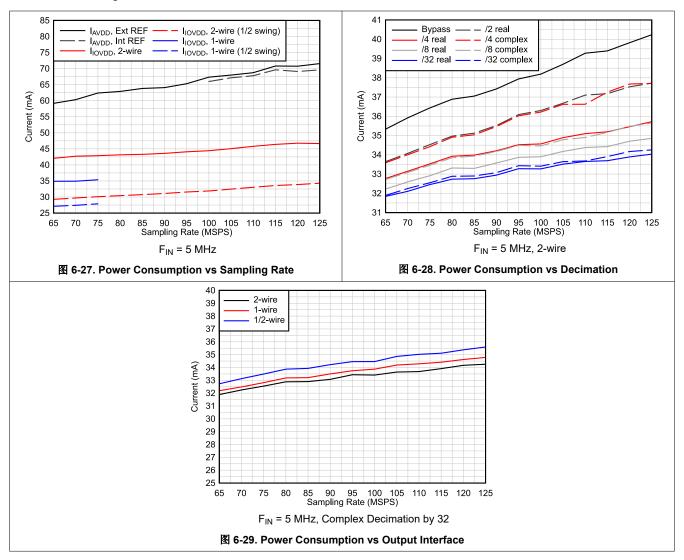

# **6.5 Electrical Characteristics - Power Consumption**

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, external 1.6V reference, and -1-dBFS differential input, unless otherwise noted

|                    | PARAMETER                                                          | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------------------------------|------------------------------------------|-----|-----|-----|------|

| ADC3664:           | 125 MSPS                                                           |                                          |     |     | '   |      |

| I <sub>AVDD</sub>  | Analog supply current                                              | External reference                       |     | 64  | 80  | mA   |

| I <sub>IOVDD</sub> | I/O supply current                                                 | SLVDS 2-wire                             |     | 47  | 72  | ША   |

| P <sub>DIS</sub>   | Power dissipation                                                  | External reference, 2-wire               |     | 200 | 274 | mW   |

|                    |                                                                    | 2-wire, 1/2-swing                        |     | 35  |     |      |

|                    |                                                                    | 4x real decimation, 16-bit, 1-wire       |     | 50  |     |      |

|                    |                                                                    | 16x real decimation, 16-bit, 1-wire      |     | 45  |     |      |

|                    | I/O supply current                                                 | 16x real decimation, 16-bit, 1/2-wire    |     | 41  |     | mA   |

|                    |                                                                    | 4x complex decimation, 16-bit, 1-wire    |     | 57  |     |      |

| $I_{IOVDD}$        |                                                                    | 8x complex decimation, 16-bit, 1-wire    |     | 54  |     |      |

|                    |                                                                    | 8x complex decimation, 16-bit, 1/2-wire  | ,   | 50  |     |      |

|                    |                                                                    | 16x complex decimation, 16-bit, 1-wire   | ,   | 50  |     |      |

|                    |                                                                    | 16x complex decimation, 16-bit, 1/2-wire |     | 47  |     |      |

|                    |                                                                    | 32x complex decimation, 16-bit, 1-wire   |     | 48  |     |      |

|                    |                                                                    | 32x complex decimation, 16-bit, 1/2-wire |     | 43  |     |      |

| MISCELLA           | NOUS                                                               |                                          | ,   |     |     |      |

|                    | Internal reference, additional analog supply current               |                                          |     | 4   |     |      |

| I <sub>AVDD</sub>  | External 1.2V reference (REFBUF), additional analog supply current | Enabled via SPI                          |     | 0.5 |     | mA   |

|                    | Single ended clock input, reduces analog supply current by         |                                          |     | 1   |     |      |

| P <sub>DIS</sub>   | Power consumption in global power down mode                        | Default mask settings                    |     | 12  |     | mW   |

Submit Document Feedback

# 6.6 Electrical Characteristics - DC Specifications

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, 1.6 V external reference, and -1-dBFS differential input, unless otherwise noted

|                                            | PARAMETER                           | TEST CONDITIONS         | MIN   | TYP    | MAX      | UNIT       |

|--------------------------------------------|-------------------------------------|-------------------------|-------|--------|----------|------------|

| DC ACCUR                                   | ACY                                 |                         |       |        | <u>'</u> |            |

| No missing o                               | codes                               |                         | 14    |        |          | bits       |

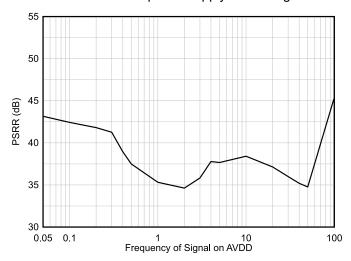

| PSRR                                       |                                     | F <sub>IN</sub> = 1 MHz |       | 35     |          | dB         |

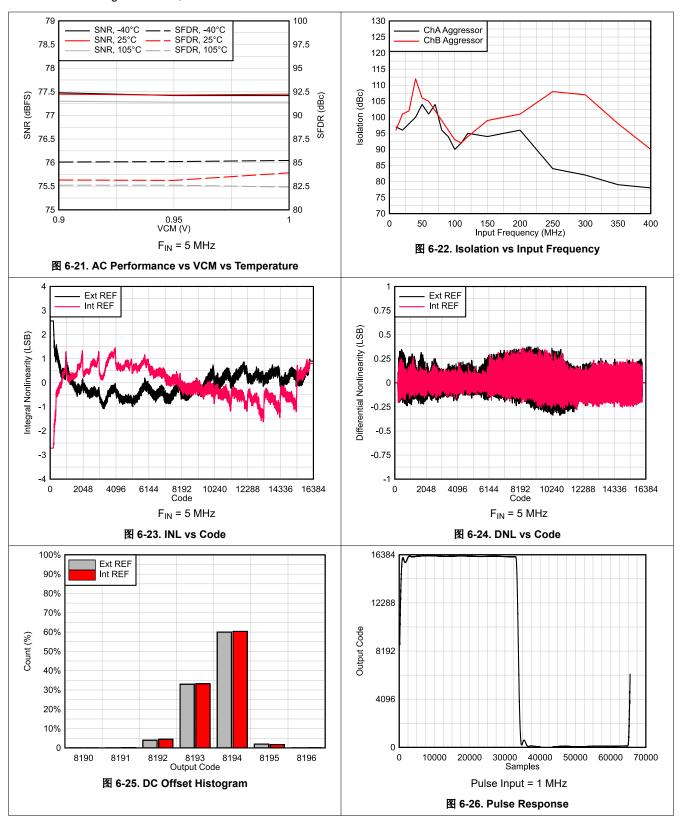

| DNL                                        | Differential nonlinearity           | F <sub>IN</sub> = 5 MHz | -0.97 | ± 0.9  | 0.97     | LSB        |

| INL                                        | Integral nonlinearity               | F <sub>IN</sub> = 5 MHz | -7.5  | ± 2.6  | 7.5      | LSB        |

| V <sub>OS_ERR</sub>                        | Offset error                        |                         | -55   | ± 30   | 55       | LSB        |

| V <sub>OS_DRIFT</sub>                      | Offset drift over temperature       |                         |       | ± 0.06 |          | LSB/ºC     |

| GAIN <sub>ERR</sub>                        | Gain error                          | External 1.6V Reference |       | ± 2    |          | %FSR       |

| GAIN <sub>DRIFT</sub>                      | Gain drift over temperature         | External 1.6V Reference |       | ± 57   |          | ppm/°C     |

| GAIN <sub>ERR</sub>                        | Gain error                          | Internal Reference      |       | ± 3    |          | %FSR       |

| GAIN <sub>DRIFT</sub>                      | Gain drift over temperature         | Internal Reference      |       | 106    |          | ppm/°C     |

| Transition No                              | oise                                |                         |       | 0.7    |          | LSB        |

| ADC ANALO                                  | OG INPUT (AINP/M, BINP/M)           |                         |       |        |          |            |

| FS                                         | Input full scale                    | Differential            |       | 3.2    |          | Vpp        |

| V <sub>CM</sub>                            | Input common model voltage          |                         | 0.9   | 0.95   | 1.0      | V          |

| R <sub>IN</sub>                            | Input resistance                    | Differential at DC      |       | 8      |          | <b>k</b> Ω |

| C <sub>IN</sub>                            | Input Capacitance                   | Differential at DC      |       | 5.4    |          | pF         |

| V <sub>OCM</sub>                           | Output common mode voltage          |                         |       | 0.95   |          | V          |

| BW                                         | Analog Input Bandwidth (-3dB)       |                         |       | 1.4    |          | GHz        |

| Internal Vol                               | tage Reference                      |                         |       | ,      |          |            |

| V <sub>REF</sub>                           | Internal reference voltage          |                         |       | 1.6    |          | V          |

| V <sub>REF</sub> Output                    | Impedance                           |                         |       | 8      |          | Ω          |

| Reference I                                | nput Buffer (REFBUF)                |                         |       |        |          |            |

| External refe                              | erence voltage                      |                         |       | 1.2    |          | V          |

| External vo                                | Itage reference (VREF)              |                         |       |        |          |            |

| V <sub>REF</sub>                           | External voltage reference          |                         |       | 1.6    |          | V          |

| Input Curren                               | t                                   |                         |       | 1      |          | mA         |

| Input impeda                               | ance                                |                         |       | 5.3    |          | <b>k</b> Ω |

| Clock Input                                | (CLKP/M)                            |                         |       |        |          |            |

| Input close f                              | roguenov                            | External reference      | 0.5   |        | 125      | MHz        |

| Input clock fi                             | requericy                           | Internal reference      | 100   |        | 125      | MHz        |

| V <sub>ID</sub> Differential input voltage |                                     |                         |       | 1      | 3.6      | Vpp        |

| V <sub>CM</sub> Input common mode voltage  |                                     |                         |       | 0.9    |          | V          |

| R <sub>IN</sub>                            | Single ended input resistance to co | mmon mode               |       | 5      |          | kΩ         |

| C <sub>IN</sub>                            | Single ended input capacitance      |                         |       | 1.5    |          | pF         |

| Clock duty c                               | ycle                                |                         | 45    | 50     | 60       | %          |

# **6.6 Electrical Characteristics - DC Specifications (continued)**

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, 1.6 V external reference, and -1-dBFS differential input, unless otherwise noted

|                  | PARAMETER                          | TEST CONDITIONS               | MIN            | TYP   | MAX | UNIT |

|------------------|------------------------------------|-------------------------------|----------------|-------|-----|------|

| Digital In       | puts (RESET, PDN, SCLK, SEN, SDIO) |                               |                |       |     |      |

| V <sub>IH</sub>  | High level input voltage           |                               | 1.4            |       |     | V    |

| V <sub>IL</sub>  | Low level input voltage            |                               |                | ,     | 0.4 | V    |

| I <sub>IH</sub>  | High level input current           |                               |                | 90    | 150 | uA   |

| I <sub>IL</sub>  | Low level input current            |                               | -150           | -90   |     | uA   |

| Cı               | Input capacitance                  |                               | 1.5            |       | pF  |      |

| Digital O        | utput (SDOUT)                      |                               | <u> </u>       |       |     |      |

| V <sub>OH</sub>  | High level output voltage          | I <sub>LOAD</sub> = -400 uA   | IOVDD<br>- 0.1 | IOVDD |     | V    |

| V <sub>OL</sub>  | Low level output voltage           | I <sub>LOAD</sub> = 400 uA    |                |       | 0.1 |      |

| SLVDS Ir         | nterface                           |                               | <u> </u>       |       | '   |      |

| V <sub>ID</sub>  | Differential input voltage         | DCLKIN                        | 200            | 350   | 650 | mVpp |

| V <sub>CM</sub>  | Input common mode voltage          | DCLKIN                        | 1              | 1.2   | 1.3 | V    |

| Output data rate |                                    | per differential SLVDS output |                |       | 1   | Gbps |

| V <sub>OD</sub>  | Differential output voltage        |                               | 500            | 700   | 850 | mVpp |

| V <sub>CM</sub>  | Output common mode voltage         |                               |                | 1.0   |     | V    |

# 6.7 Electrical Characteristics - AC Specifications

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, 1.6 V external reference, and -1-dBFS differential input, unless otherwise noted

| PARAMETER |                                                  | TEST CONDITIONS                                                                  |      | MIN TYP N |  | UNIT    |  |  |

|-----------|--------------------------------------------------|----------------------------------------------------------------------------------|------|-----------|--|---------|--|--|

| NSD       | Noise Spectral Density                           | f <sub>IN</sub> = 5 MHz, A <sub>IN</sub> = -20 dBFS                              |      | -156.9    |  | dBFS/Hz |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 72   | 77.5      |  | dBFS    |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz, A <sub>IN</sub> = -20 dBFS                              |      | 78.9      |  |         |  |  |

| OND       | Oliver all the specific annuality                | f <sub>IN</sub> = 10 MHz                                                         |      | 77.6      |  |         |  |  |

| SNR       | Signal to noise ratio                            | f <sub>IN</sub> = 40 MHz                                                         |      | 76.9      |  | dBFS    |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 75.5      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 74.1      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          |      | 75.7      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 74.2      |  |         |  |  |

| SINAD     | Signal to noise and distortion ratio             | f <sub>IN</sub> = 40 MHz                                                         |      | 72.6      |  | dBFS    |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 71.3      |  | QBF3    |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 72.4      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          |      | 12.6      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 12.6      |  | bit     |  |  |

| ENOB      | Effective number of bits                         | f <sub>IN</sub> = 40 MHz                                                         |      | 12.5      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 12.3      |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 12.0      |  |         |  |  |

|           | Total Harmonic Distortion (First five harmonics) | f <sub>IN</sub> = 5 MHz                                                          | 71.5 | 80        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 76        |  |         |  |  |

| THD       |                                                  | f <sub>IN</sub> = 40 MHz                                                         |      | 74        |  | dBc     |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 72        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 76        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 77   | 84        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 78        |  |         |  |  |

| HD2       | Second Harmonic Distortion                       | f <sub>IN</sub> = 40 MHz                                                         |      | 75        |  | dBc     |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 77        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 79        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 73.5 | 84        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 81        |  |         |  |  |

| HD3       | Third Harmonic Distortion                        | f <sub>IN</sub> = 40 MHz                                                         |      | 88        |  | dBc     |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 76        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 81        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 84   | 92        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 93        |  |         |  |  |

| Non HD2,3 | Spur free dynamic range (excluding HD2 and HD3)  | f <sub>IN</sub> = 40 MHz                                                         |      | 89        |  | dBFS    |  |  |

|           | TIDE and TIDS)                                   | f <sub>IN</sub> = 70 MHz                                                         |      | 84        |  |         |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 86        |  |         |  |  |

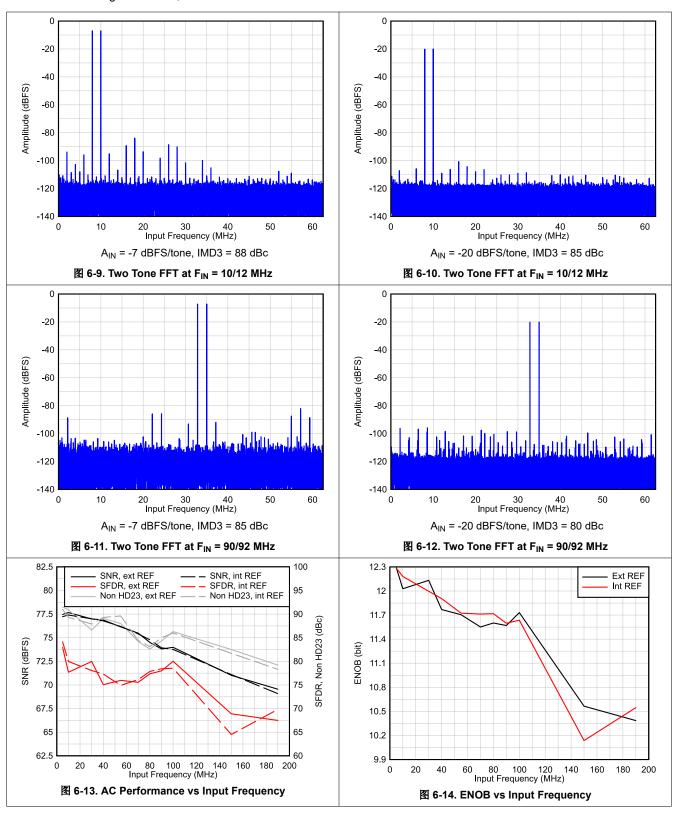

| IMD3      | Two tone inter-modulation distortion             | f <sub>1</sub> = 10 MHz, f <sub>2</sub> = 12 MHz, A <sub>IN</sub> = -7 dBFS/tone |      | 88        |  | dBc     |  |  |

# 6.8 Timing Requirements

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, 1.6 V external reference, and -1-dBFS differential input, unless otherwise noted

| PARAMETER           |                                                                              | TEST CONDITIONS MIN NOM                                                                                                                                                             |                                                       | MAX  | UNIT                        |  |

|---------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-----------------------------|--|

| ADC Timi            | ng Specifications                                                            |                                                                                                                                                                                     |                                                       |      |                             |  |

| t <sub>AD</sub>     | Aperture Delay                                                               |                                                                                                                                                                                     | 0.85                                                  |      | ns                          |  |

| t <sub>A</sub>      | Aperture Jitter                                                              | square wave clock with fast edges                                                                                                                                                   | 250                                                   |      | fs                          |  |

| tJ                  | Jitter on DCLKIN                                                             |                                                                                                                                                                                     |                                                       | ± 50 | ps pk-pk                    |  |

| Recory tim          | ne from +6 dB overload condition                                             | SNR within 1 dB of expected value                                                                                                                                                   | 1                                                     |      | Clock<br>cycle              |  |

| t <sub>ACQ</sub>    | Signal acquisition period                                                    | referenced to sampling clock falling edge                                                                                                                                           | -T <sub>S</sub> /4                                    |      | Sampling<br>clock<br>period |  |

| $t_{CONV}$          | Signal conversion period                                                     |                                                                                                                                                                                     | 6                                                     |      | ns                          |  |

|                     |                                                                              | Bandgap reference enabled, single ended clock                                                                                                                                       | 13                                                    |      | us                          |  |

|                     | Time to valid data after coming out of                                       | Bandgap reference enabled, differential clock                                                                                                                                       | 15                                                    |      | us                          |  |

|                     | power down. Internal reference.                                              | Bandgap reference disabled, single ended clock                                                                                                                                      | 2.4                                                   |      |                             |  |

| Wake up             |                                                                              | Bandgap reference disabled, differential clock                                                                                                                                      | 2.3                                                   | ms   |                             |  |

| time                |                                                                              | Bandgap reference enabled, single ended clock                                                                                                                                       | 13                                                    |      | us                          |  |

|                     | Time to valid data after coming out of power down.  External 1.6V reference. | Bandgap reference enabled, differential clock                                                                                                                                       | 14                                                    |      |                             |  |

|                     |                                                                              | Bandgap reference disabled, single ended clock                                                                                                                                      | 2.0                                                   |      | me                          |  |

|                     |                                                                              | Bandgap reference disabled, differential clock                                                                                                                                      | 2.2                                                   |      | ms                          |  |

| t <sub>S,SYNC</sub> | Setup time for SYNC input signal                                             | Deferenced to compling clock vising adds                                                                                                                                            | 500                                                   |      |                             |  |

| t <sub>H,SYNC</sub> | Hold time for SYNC input signal                                              | Referenced to sampling clock rising edge                                                                                                                                            | 600                                                   |      | ps                          |  |

|                     |                                                                              | 1/2-wire SLVDS                                                                                                                                                                      | 1 1                                                   |      | Clock<br>cycles             |  |

| ADC<br>Latency      | Signal input to data output                                                  | 1-wire SLVDS                                                                                                                                                                        |                                                       |      |                             |  |

| Laterioy            |                                                                              | 2-wire SLVDS                                                                                                                                                                        | 2                                                     |      | oyoloo                      |  |

|                     | Real decimation by 2                                                         |                                                                                                                                                                                     | 21                                                    |      |                             |  |

| Add.                | Complex decimation by 2                                                      |                                                                                                                                                                                     | 22                                                    |      | Output clock                |  |

| Latency             | Real or complex decimation by 4, 8, 16, 32                                   |                                                                                                                                                                                     | 23                                                    |      | cycles                      |  |

| Interface           | Timing: Serial LVDS Interface                                                |                                                                                                                                                                                     |                                                       |      |                             |  |

|                     | Propagation delay: sampling clock falling edge to DCLK rising edge           | Delay between sampling clock falling edge to DCLKIN falling edge < 2.5ns.  T <sub>DCLK</sub> = DCLK period  t <sub>CDCLK</sub> = Sampling clock falling edge to DCLKIN falling edge | 2+ 3+ 4+ TDCLK TDCLK TDCLK + + + tCDCLK tCDCLK tCDCLK |      |                             |  |

| PD                  |                                                                              | Delay between sampling clock falling edge to DCLKIN falling edge >= 2.5ns.  T <sub>DCLK</sub> = DCLK period t <sub>CDCLK</sub> = Sampling clock falling edge to DCLKIN falling edge | 2+ 3+<br>tcdclk tcdclk tc                             | 4+   | ns                          |  |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.8 Timing Requirements (continued)

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, 1.6 V external reference, and -1-dBFS differential input, unless otherwise noted

|                       | PARAMETER                                                      | TEST CONDITIONS                           | MIN  | NOM  | MAX  | UNIT |  |  |  |

|-----------------------|----------------------------------------------------------------|-------------------------------------------|------|------|------|------|--|--|--|

|                       | DCLK rising edge to output data                                | Fout = 65 MSPS, DA/B0,1 = 455 MBPS        | 0    | 0.1  |      |      |  |  |  |

|                       | delay,                                                         | Fout = 80 MSPS, DA/B0,1 = 560 MBPS        | 0    | 0.1  |      |      |  |  |  |

|                       | 2-wire SLVDS, 14-bit                                           | Fout = 125 MSPS, DA/B0,1 = 875 MBPS       | -0.2 | 0.1  |      |      |  |  |  |

|                       | DCLK rising edge to output data delay,<br>1-wire SLVDS, 14-bit | Fout = 65 MSPS, DA/B0 = 910 MBPS          | 0    | 0.1  |      |      |  |  |  |

| $t_{CD}$              | DCLK rising edge to output data                                | Fout = 10 MSPS, DA/B0 = 160 MBPS          | 0    | 0.1  |      | ns   |  |  |  |

|                       | delay,                                                         | Fout = 25 MSPS, DA/B0 = 400 MBPS          | 0    | 0.1  |      | _    |  |  |  |

|                       | 1-wire SLVDS, 16-bit                                           | Fout = 62.5 MSPS, DA/B0= 1000 MBPS        | -0.6 | 0.1  |      |      |  |  |  |

|                       | DCLK rising edge to output data                                | Fout = 5 MSPS, DA0 = 160 MBPS             | 0    | 0.1  |      |      |  |  |  |

|                       | delay,                                                         | Fout = 10 MSPS, DA0 = 320 MBPS            | 0    | 0.1  |      |      |  |  |  |

|                       | 1/2-wire SLVDS, 16-bit                                         | Fout = 25 MSPS, DA0 = 800 MBPS            | 0    | 0.1  |      |      |  |  |  |

|                       |                                                                | Fout = 65 MSPS, DA/B0,1 = 455 MBPS        | 1.8  | 1.9  |      |      |  |  |  |

|                       | Data valid, 2-wire SLVDS, 14-bit                               | Fout = 80 MSPS, DA/B0,1 = 560 MBPS        | 1.4  | 1.5  |      |      |  |  |  |

|                       |                                                                | Fout = 125 MSPS, DA/B0,1 = 875 MBPS       | 0.6  | 8.0  |      | - ns |  |  |  |

|                       | Data valid, 1-wire SLVDS, 14-bit                               | Fout = 65 MSPS, DA/B0 = 910 MBPS          | 0.6  | 0.8  |      |      |  |  |  |

|                       | Data valid, 1-wire SLVDS, 16-bit                               | Fout = 10 MSPS, DA/B0 = 160 MBPS          | 5.7  | 5.8  |      |      |  |  |  |

| t <sub>DV</sub>       |                                                                | Fout = 25 MSPS, DA/B0 = 400 MBPS          | 2.0  | 2.1  |      |      |  |  |  |

|                       |                                                                | Fout = 62.5 MSPS, DA/B0= 1000 MBPS        | 0.5  | 0.6  |      |      |  |  |  |

|                       | Data valid, 1/2-wire SLVDS, 16-bit                             | Fout = 5 MSPS, DA0 = 160 MBPS             | 5.7  | 5.8  |      |      |  |  |  |

|                       |                                                                | Fout = 10 MSPS, DA0 = 320 MBPS            | 2.7  | 2.8  |      |      |  |  |  |

|                       |                                                                | Fout = 25 MSPS, DA0 = 800 MBPS            | 0.8  | 0.9  |      |      |  |  |  |

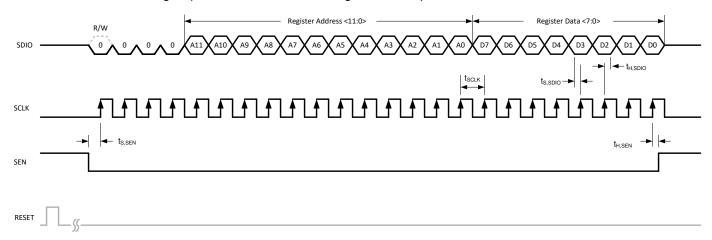

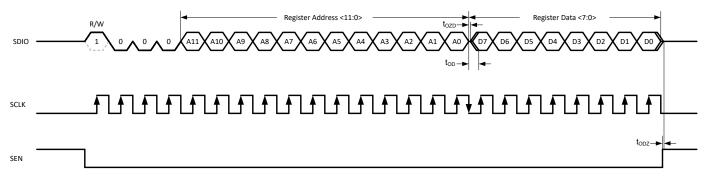

| SERIAL                | PROGRAMMING INTERFACE (SCLK,                                   | SEN, SDIO) - Input                        |      |      |      |      |  |  |  |

| f <sub>CLK,SCLK</sub> | Serial clock frequency                                         |                                           |      |      | 20   | MHz  |  |  |  |

| t <sub>S,SEN</sub>    | SEN falling edge to SCLK rising edge                           | 9                                         | 10   |      |      |      |  |  |  |

| t <sub>H,SEN</sub>    | SCLK rising edge to SEN rising edge                            |                                           | 9    |      |      | ns   |  |  |  |

| t <sub>s,sdio</sub>   | SDIO setup time from rising edge of                            | SDIO setup time from rising edge of SCLK  |      |      |      | 115  |  |  |  |

| t <sub>H,SDIO</sub>   | SDIO hold time from rising edge of S                           | 9                                         |      |      |      |      |  |  |  |

| SERIAL                | PROGRAMMING INTERFACE (SDIO)                                   | - Output                                  |      |      |      |      |  |  |  |

| t <sub>OZD</sub>      | Delay from falling edge of 16th SCLK tri-state to valid data   | 3.9                                       |      | 10.8 |      |      |  |  |  |

| t <sub>ODZ</sub>      | Delay from SEN rising edge for SDIC                            | transition from valid data to tri-state   | 3.4  |      | 14   | ns   |  |  |  |

| t <sub>OD</sub>       | Delay from falling edge of 16th SCLk                           | Cycle during read operation to SDIO valid | 3.9  |      | 10.8 |      |  |  |  |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

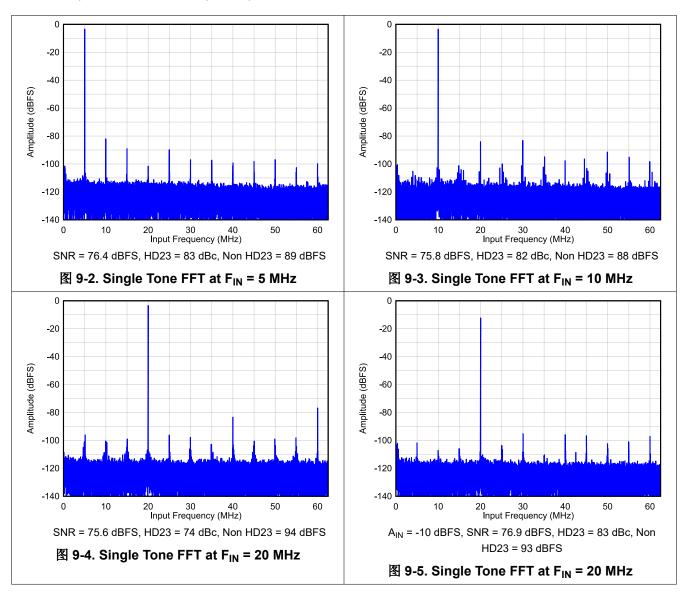

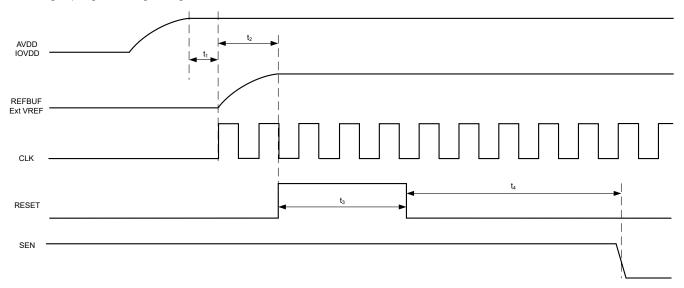

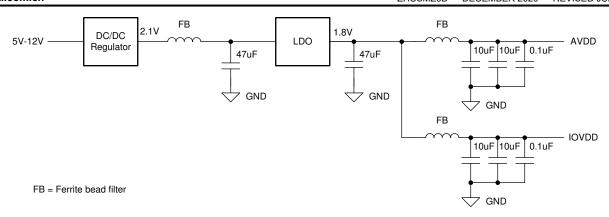

# **6.9 Typical Characteristics**

### 7 Parameter Measurement Information

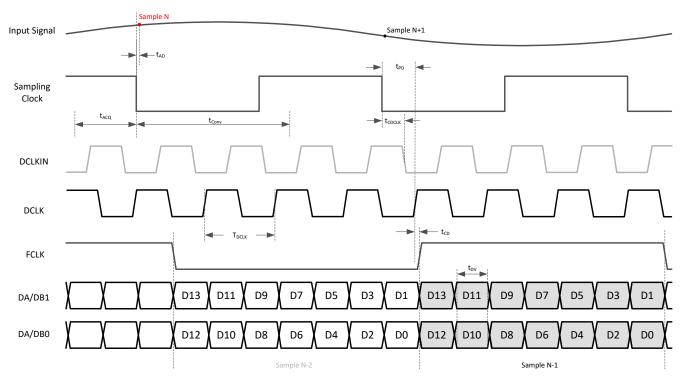

图 7-1. Timing diagram: 2-wire SLVDS

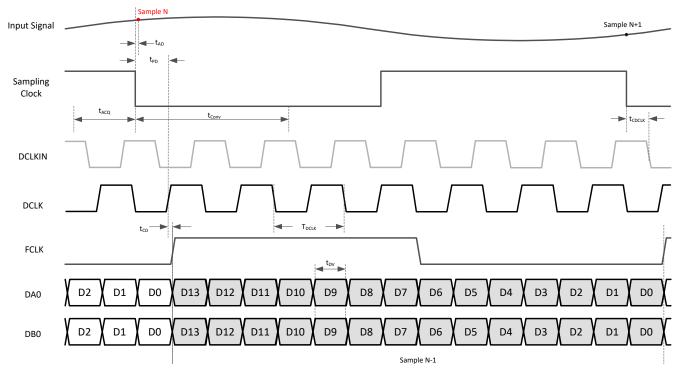

图 7-2. Timing diagram: 1-wire SLVDS

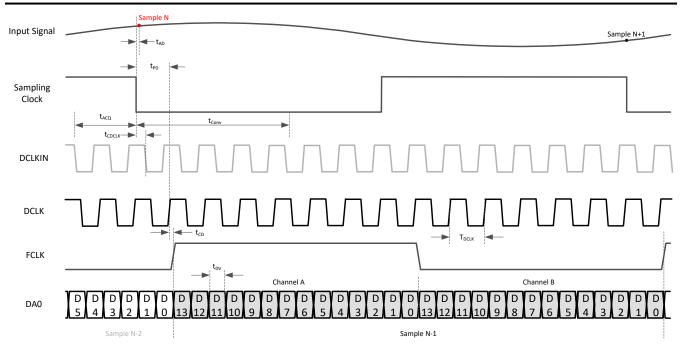

图 7-3. Timing diagram: 1/2-wire SLVDS

### 8 Detailed Description

### 8.1 Overview

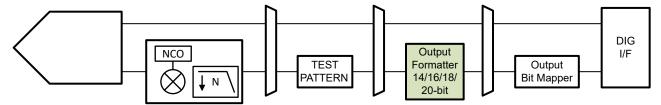

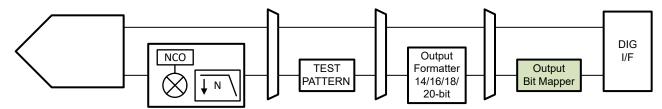

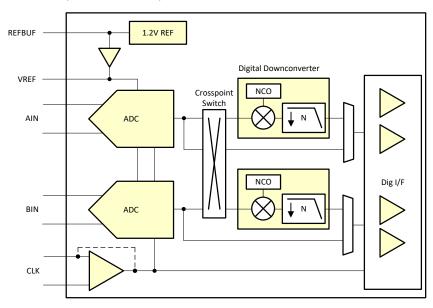

The ADC3664 is a low noise, ultra-low power 14-bit high-speed dual channel ADC supporting sampling rates up to 125 MSPS. It offers very good DC precision together with IF sampling support which makes it ideally suited for a wide range of applications. The ADC3664 is equipped with an on-chip internal reference option but it also supports the use of an external, high precision 1.6V voltage reference or an external 1.2V reference which is buffered and gained up internally. Because of the inherent low latency architecture, the digital output result is available after as low as one clock cycle on the digital output interface.

### 备注

The ADC3664 supports the following sampling rates:

External Reference: 65 to 125 MSPS

Internal Reference: 100 to 125 MSPS

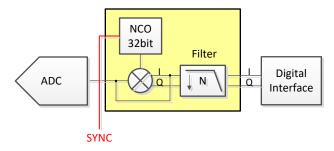

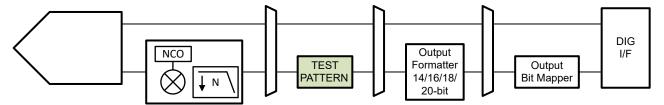

An optional programmable digital down converter enables external anti-alias filter relaxation as well as output data rate reduction. The digital filter provides a 32-bit programmable NCO and supports both real or complex decimation.

The ADC3664 uses a serial LVDS (SLVDS) interface to output the data which minimizes the number of digital interconnects. The device supports a two-lane (2-wire), a one-lane (1-wire) and a half-lane (1/2-wire) option. The ADC3664 includes a digital output formatter which supports output resolutions from 14 to 20-bit.

The device features and control options can be set up either through pin configurations or via SPI register writes.

### 8.2 Functional Block Diagram

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

### 8.3 Feature Description

### 8.3.1 Analog Input

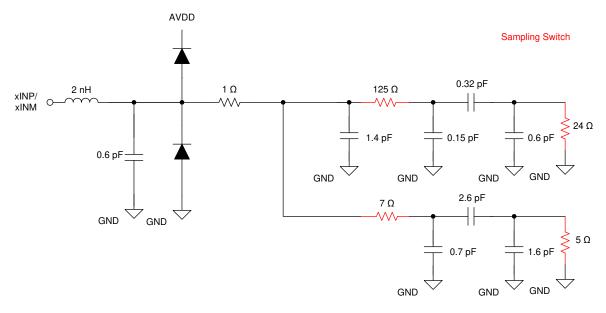

The analog inputs of ADC3664 are intended to be driven differentially. Both AC coupling and DC coupling of the analog inputs is supported. The analog inputs are designed for an input common mode voltage of 0.95 V which must be provided externally on each input pin. DC-coupled input signals must have a common mode voltage that meets the device input common mode voltage range.

The equivalent input network diagram is shown in 88-1. All four sampling switches, on-resistance shown in red are in same position (open or closed) simultaneously.

图 8-1. Equivalent Input Network

#### 8.3.1.1 Analog Input Bandwidth

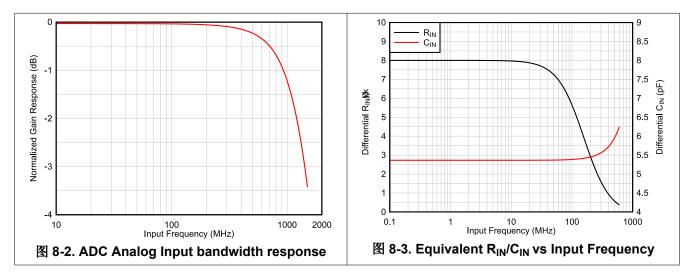

$\boxtimes$  8-2 shows the analog full power input bandwidth of the ADC3664 with a 50  $\Omega$  differential termination. The -3 dB bandwidth is approximately 1.4 GHz and the useful input bandwidth with good AC performance is approximately 200 MHz.

The equivalent differential input resistance  $R_{\text{IN}}$  and input capacitance  $C_{\text{IN}}$  vs frequency are shown in  $\boxed{8}$  8-3.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

### 8.3.1.2 Analog Front End Design

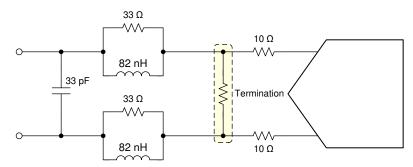

The ADC3664 is an unbuffered ADC and thus a passive kick-back filter is recommended to absorb the glitch from the sampling operation. Depending on if the input is driven by a balun or a differential amplifier with low output impedance, a termination network may be needed. Additionally a passive DC bias circuit is needed in AC-coupled applications which can be combined with the termination network.

### 8.3.1.2.1 Sampling Glitch Filter Design

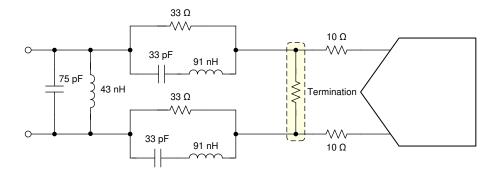

The front end sampling glitch filter is designed to optimize the SNR and HD3 performance of the ADC. The filter performance is dependent on input frequency and therefore the following filter designs are recommended for different input frequency ranges as shown in 8-4 and 8-5 (assuming 50  $\Omega$  source impedance).

图 8-4. Sampling glitch filter example for input frequencies from DC to 60 MHz

图 8-5. Sampling glitch filter example for input frequencies from 60 to 120 MHz

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

### 8.3.1.2.2 Analog Input Termination and DC Bias

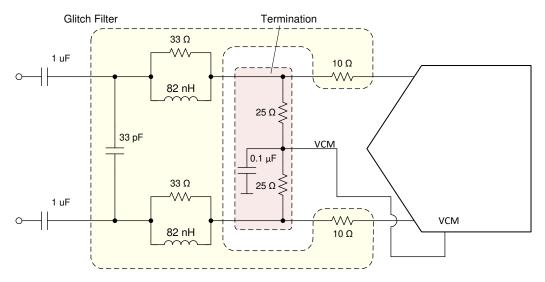

Depending on the input drive circuitry, a termination network and/or DC biasing needs to be provided.

### 8.3.1.2.2.1 AC-Coupling

The ADC3664 requires external DC bias using the common mode output voltage (VCM) of the ADC together with the termination network as shown in 8-6. The termination is located within the glitch filter network. When using a balun on the input, the termination impedance has to be adjusted to account for the turns ratio of the transformer. When using an amplifier, the termination impedance can be adjusted to optimize the amplifier performance.

图 8-6. AC-Coupling: termination network provides DC bias (glitch filter example for up to 60 MHz)

### 8.3.1.2.2.2 DC-Coupling

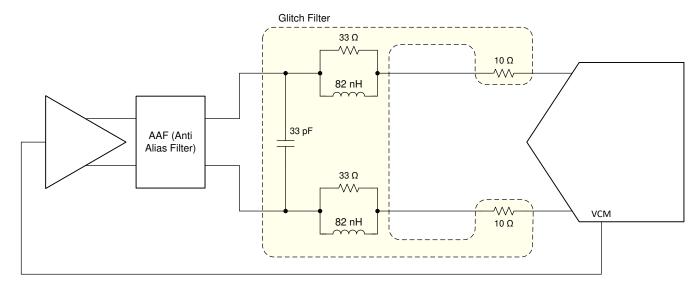

In DC coupled applications the DC bias needs to be provided from the fully differential amplifier (FDA) using VCM output of the ADC as shown in 88-7. The glitch filter in this case is located between the anti-alias filter and the ADC. No termination may be needed if amplifier is located close to the ADC or if the termination is part of the anti-alias filter.

图 8-7. DC-Coupling: DC bias provided by FDA (glitch filter example for DC - 60 MHz)

### 8.3.2 Clock Input

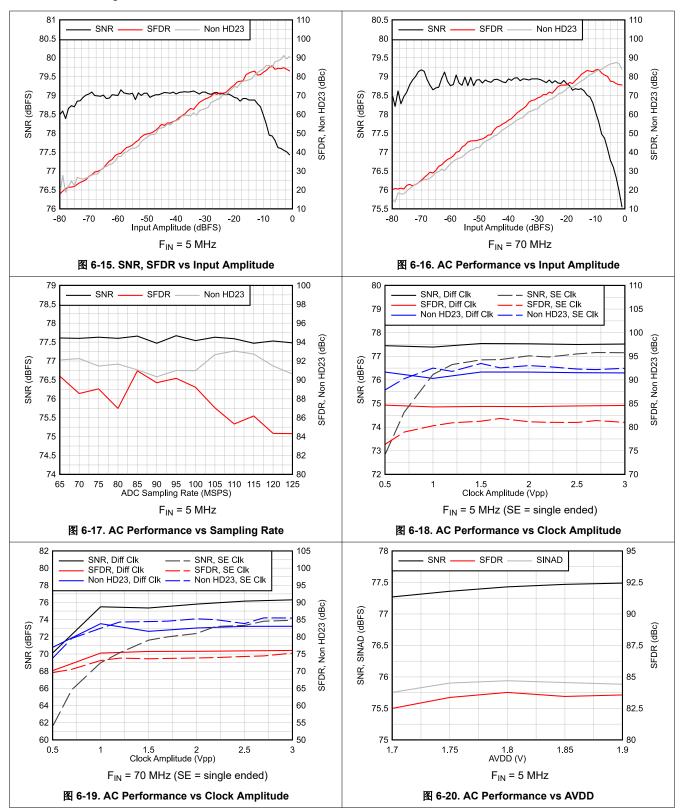

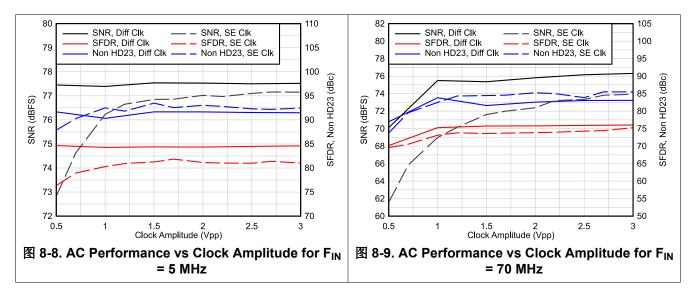

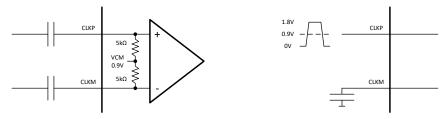

In order to maximize the ADC SNR performance, the external sampling clock should be low jitter and differential signaling with a high slew rate. This is especially important in IF sampling applications (图 8-8 and 图 8-9). For less jitter sensitive applications, the ADC3664 provides the option to operate with single ended signaling which saves additional power consumption.

### 8.3.2.1 Single Ended vs Differential Clock Input

The ADC3664 can be operated using a differential or a single ended clock input where the single ended clock consumes less power consumption. However clock amplitude impacts the ADC aperture jitter and consequently the SNR. For maximum SNR performance, a large clock signal with fast slew rates needs to be provided.

- Differential Clock Input: The clock input can be AC coupled externally. The ADC3664 provides internal biasing for that use case.

- Single Ended Clock Input: This mode needs to be configured using SPI register (0x0E, D2 and D0) or with the REFBUF pin. In this mode there is no internal clock biasing and thus the clock input needs to be DC coupled around a 0.9V center. The unused input needs to be AC coupled to ground.

图 8-10. External and internal connection using differential (left) and single ended (right) clock input

### 8.3.3 Voltage Reference

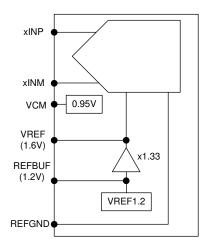

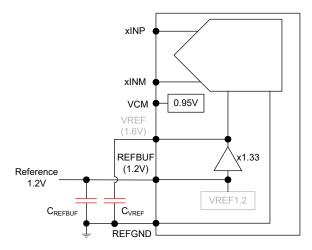

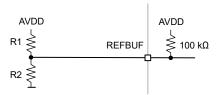

The ADC3664 provides three different options for supplying the voltage reference to the ADC. An external 1.6V reference can be directly connected to the VREF input; a voltage 1.2V reference can be connected to the REFBUF input using the internal gain buffer or the internal 1.2V reference can be enabled to generate a 1.6V reference voltage. For best performance, the reference noise should be filtered by connecting a 10 uF and a 0.1 uF ceramic bypass capacitor to the VREF pin. The internal reference circuitry of the ADC3664 is shown in 8-11.

### 备注

The voltage reference mode can be selected using SPI writes or by using the REFBUF pin (default) as a control pin ( $\dagger$  8.5.1). If the REFBUF pin is not used for configuration, the REFBUF pin should be connected to AVDD (even though the REFBUF pin has a weak internal pullup to AVDD) and the voltage reference option has to be selected using the SPI interface.

图 8-11. Different voltage reference options for ADC3664

#### 8.3.3.1 Internal voltage reference

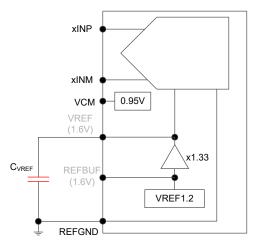

The 1.6V reference for the ADC can be generated internal using the on-chip 1.2V reference along with the internal gain buffer. A 10 uF and a 0.1 uF ceramic bypass capacitor ( $C_{VREF}$ ) should be connected between the VREF and REFGND pins as close to the pins as possible.

图 8-12. Internal reference

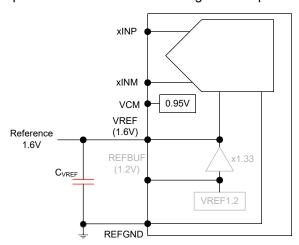

### 8.3.3.2 External voltage reference (VREF)

For highest accuracy and lowest temperature drift, the VREF input can be directly connected to an external 1.6V reference. A 10 uF and a 0.1 uF ceramic bypass capacitor ( $C_{VREF}$ ) should be connected between the VREF and REFGND pins and placed as close to the pins as possible is recommended. The load current from the external reference is about 1mA.

Note: The internal reference is also used for other functions inside the device, therefore the reference amplifier should only be powered down in power down state but not during normal operation.

图 8-13. External 1.6V reference

### 8.3.3.3 External voltage reference with internal buffer (REFBUF)

The ADC3664 is equipped with an on-chip reference buffer that also includes gain to generate the 1.6V reference voltage from an external 1.2V reference. A 10 uF and a 0.1 uF ceramic bypass capacitor ( $C_{VREF}$ ) between the VREF and REFGND pins and a 10 uF and a 0.1 uF ceramic bypass capacitor between the REFBUF and REFGND pins are recommended. Both capacitors should be placed as close to the pins as possible. The load current from the external reference is less than 100uA.

图 8-14. External 1.2V reference using internal reference buffer

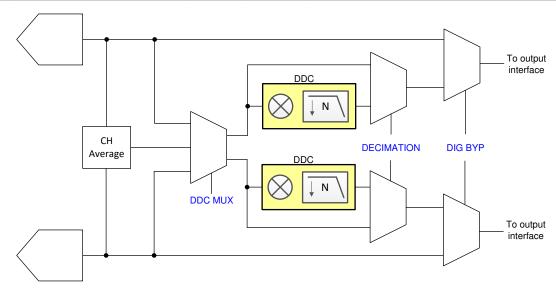

### 8.3.4 Digital Down Converter

The ADC3664 includes an optional on-chip digital down conversion (DDC) decimation filter that can be enabled via SPI register settings. It supports complex decimation by 2, 4, 8, 16 and 32 using a digital mixer and a 32-bit numerically controlled oscillator (NCO) as shown in 88-15. Furthermore it supports a mode with real decimation where the complex mixer is bypassed (NCO should be set to 0 for lowest power consumption) and the digital filter acts as a low pass filter.

Internally the decimation filter calculations are performed with a 20-bit resolution in order to avoid any SNR degradation due to quantization noise limitation. The Output Formatter truncates to the selected resolution prior to outputting the data on the digital interface.

图 8-15. Internal Digital Decimation Filter

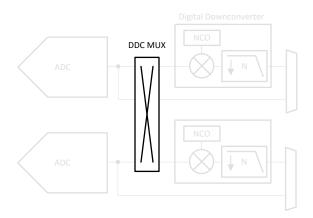

#### 8.3.4.1 DDC MUX

The ADC3664 contains a MUX in front of the digital decimation filter which allows the ADC channel A input to be connected to the DDC of channel B and vice versa.

图 8-16. DDC MUX

### 8.3.4.2 Digital Filter Operation

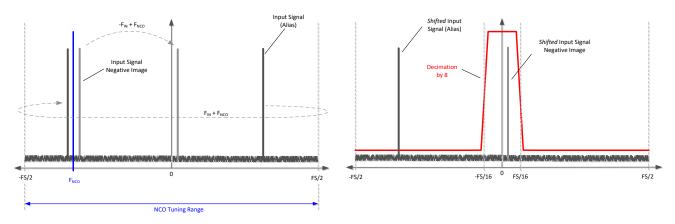

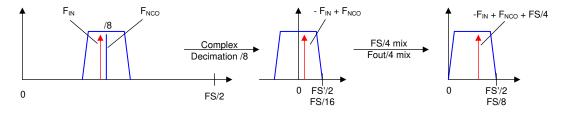

The complex decimation operation is illustrated with an example in  $\boxtimes$  8-17. First the input signal (and the negative image) are frequency shifted by the NCO frequency as shown on the left. Next a digital filter is applied (centered around 0 Hz) and the output data rate is decimated - in this example the output data rate  $F_{S,OUT} = F_S/8$  with a Nyquist zone of  $F_S/16$ . During the complex mixing the spectrum (signal and noise) is split into real and complex parts and thus the amplitude is reduced by 6-dB. In order to compensate this loss, there is a 6-dB digital gain option in the decimation filter block that can be enabled via SPI write.

图 8-17. Complex decimation illustration

The real decimation operation is illustrated with an example in  $\boxtimes$  8-18. There is no frequency shift happening and only the real portion of the complex digital filter is exercised. The output data rate is decimated - a decimation of 8 would result in an output data rate  $F_{S,OUT} = F_S/8$  with a Nyquist zone of  $F_S/16$ .

During the real mixing the spectrum (signal and noise) amplitude is reduced by 3-dB. In order to compensate this loss, there is a 3-dB digital gain option in the decimation filter block that can be enabled via SPI write.

图 8-18. Real decimation illustration

### 8.3.4.3 FS/4 Mixing with Real Output

In this mode, the output after complex decimation gets mixed with FS/4 (FS = output data rate in this case). Instead of a complex output with the input signal centered around 0 Hz, the output is transmitted as a real output at twice the data rate and the signal is centered around FS/4 (Fout/4) as illustrated in 88-19.

In this example, complex decimation by 8 is used. The output data is transmitted as a real output with an output rate of Fout = FS'/4 (FS' = ADC sampling rate). The input signal is now centered around FS/4 (Fout/4) or FS'/16.

图 8-19. FS/4 Mixing with real output

### 8.3.4.4 Numerically Controlled Oscillator (NCO) and Digital Mixer

The decimation block is equipped with a 32-bit NCO and a digital mixer to fine tune the frequency placement prior to the digital filtering. The oscillator generates a complex exponential sequence of:

$$e^{j\omega n}$$

(default) or  $e^{-j\omega n}$

where: frequency (  $\omega$  ) is specified as a signed number by the 32-bit register setting

The complex exponential sequence is multiplied with the real input from the ADC to mix the desired carrier to a frequency equal to  $f_{\text{IN}}$  +  $f_{\text{NCO}}$ . The NCO frequency can be tuned from  $-F_{\text{S}}/2$  to  $+F_{\text{S}}/2$  and is processed as a signed, 2s complement number. After programming a new NCO frequency, the MIXER RESTART register bit or SYNC pin has to be toggled for the new frequency to get active. Additionally the ADC3664 provides the option via SPI to invert the mixer phase.

The NCO frequency setting is set by the 32-bit register value given and calculated as:

NCO frequency = 0 to +

$$F_S/2$$

: NCO =  $f_{NCO} \times 2^{32} / F_S$

NCO frequency =

$$-F_S/2$$

to 0: NCO =  $(f_{NCO} + F_S) \times 2^{32} / F_S$

#### where:

- NCO = NCO register setting (decimal value)

- f<sub>NCO</sub> = Desired NCO frequency (MHz)

- F<sub>S</sub> = ADC sampling rate (MSPS)

The NCO programming is further illustrated with this example:

- ADC sampling rate F<sub>S</sub> = 125 MSPS

- Input signal f<sub>IN</sub> = 10 MHz

- Desired output frequency f<sub>OUT</sub> = 0 MHz

For this example there are actually four ways to program the NCO and achieve the desired output frequency as shown in  $\frac{1}{8}$  8-1.

表 8-1. NCO value calculations example

| Alias or negative image    | f <sub>NCO</sub>            | NCO Value  | Mixer Phase Frequency translation for f <sub>OUT</sub> |                                                                                      |  |

|----------------------------|-----------------------------|------------|--------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| $f_{IN} = -10 \text{ MHz}$ | f <sub>NCO</sub> = 10 MHz   | 343597384  | as is                                                  | $f_{OUT} = f_{IN} + f_{NCO} = -10 \text{ MHz} + 10 \text{ MHz} = 0 \text{ MHz}$      |  |

| f <sub>IN</sub> = 10 MHz   | $f_{NCO} = -10 \text{ MHz}$ | 4638564680 | 45 15                                                  | f <sub>OUT</sub> = f <sub>IN</sub> + f <sub>NCO</sub> = 10 MHz + ( - 10 MHz) = 0 MHz |  |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

# 表 8-1. NCO value calculations example (continued)

| Alias or negative image   | ge f <sub>NCO</sub> NCO Value Mixer Phase |            | Frequency translation for f <sub>OUT</sub> |                                                                                |  |

|---------------------------|-------------------------------------------|------------|--------------------------------------------|--------------------------------------------------------------------------------|--|

| f <sub>IN</sub> = 10 MHz  | f <sub>NCO</sub> = 10 MHz                 | 343597384  |                                            | $f_{OUT} = f_{IN} - f_{NCO} = 10 \text{ MHz} - 10 \text{ MHz} = 0 \text{ MHz}$ |  |

| f <sub>IN</sub> = -10 MHz | f <sub>NCO</sub> = -10 MHz                | 4638564680 | inverted                                   | $f_{OUT} = f_{IN} - f_{NCO} = -10 \text{ MHz} - (-10 \text{ MHz}) = 0$ MHz     |  |

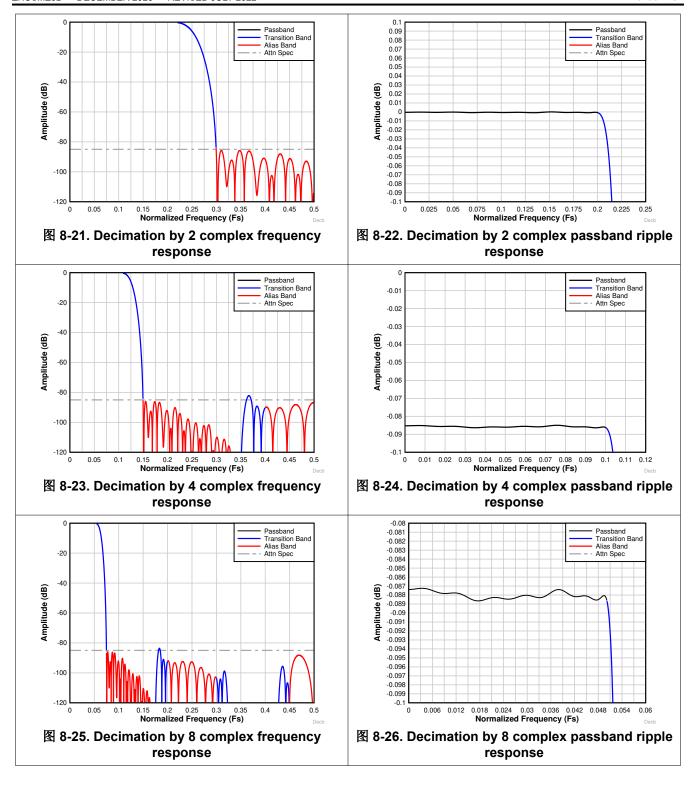

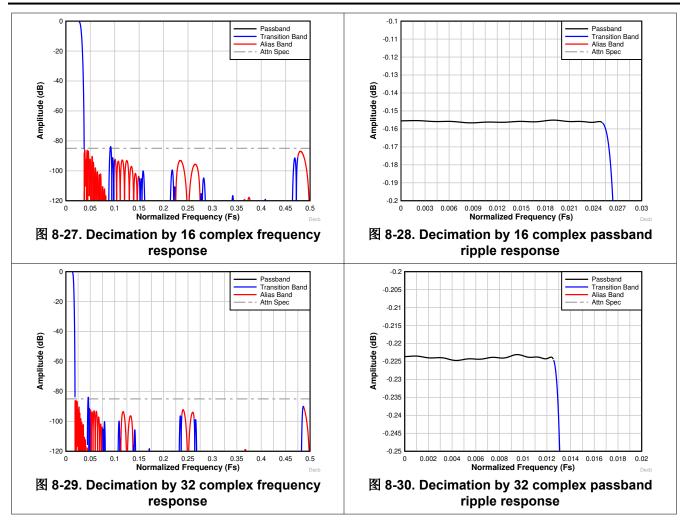

#### 8.3.4.5 Decimation Filter

The ADC3664 supports complex decimation by 2, 4, 8, 16 and 32 with a pass-band bandwidth of ~ 80% and a stopband rejection of at least 85 dB. 表 8-2 gives an overview of the pass-band bandwidth of the different decimation settings with respect to ADC sampling rate F<sub>S</sub>. In real decimation mode the output bandwidth is half of the complex bandwidth.

表 8-2. Decimation Filter Summary and Maximum Available Output Bandwidth

| ~~                                | 70 21 200 madon 1 mor Cammary and maximum 7 transactor Campat 2 and maximum |                            |                                                          |                    |                                           |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------|----------------------------|----------------------------------------------------------|--------------------|-------------------------------------------|--|--|--|--|--|

| REAL/COMPLEX DECIMATION SETTING N |                                                                             | OUTPUT RATE                | OUTPUT OUTPUT RATE BANDWIDTH (F <sub>S</sub> = 125 MSPS) |                    | OUTPUT BANDW<br>(F <sub>S</sub> = 125 MSP |  |  |  |  |  |

|                                   | 2                                                                           | F <sub>S</sub> / 2 complex | 0.8 × F <sub>S</sub> / 2                                 | 62.5 MSPS complex  | 50 MHz                                    |  |  |  |  |  |

|                                   | 4                                                                           | F <sub>S</sub> / 4 complex | 0.8 × F <sub>S</sub> / 4                                 | 31.25 MSPS complex | 25 MHz                                    |  |  |  |  |  |

|                                   |                                                                             |                            |                                                          |                    |                                           |  |  |  |  |  |

WIDTH PS) Complex 8 F<sub>S</sub> / 8 complex  $0.8 \times F_{S} / 8$ 15.625 MSPS complex 12.5 MHz 16 F<sub>S</sub> / 16 complex  $0.8 \times F_{S} / 16$ 7.8125 MSPS complex 6.25 MHz  $0.8 \times F_{S} / 32$ 32 F<sub>S</sub> / 32 complex 3.90625 MSPS complex 3.125 MHz F<sub>S</sub> / 2 real  $0.4 \times F_{S} / 2$ 62.5 MSPS 2 25 MHz  $0.4 \times F_{S} / 4$ F<sub>S</sub> / 4 real 31.25 MSPS 12.5 MHz 4 8 F<sub>S</sub> / 8 real  $0.4 \times F_{S} / 8$ 15.625 MSPS 6.25 MHz Real 0.4 × F<sub>S</sub> / 16 F<sub>S</sub> / 16 real 7.8125 MSPS 3.125 MHz 16  $0.4 \times F_{S} / 32$ 32 F<sub>S</sub> / 32 real 3.90625 MSPS 1.5625 MHz

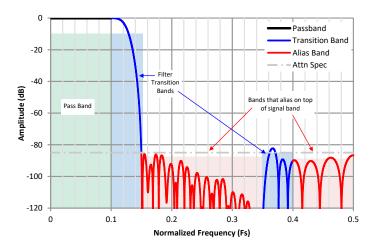

The decimation filter responses normalized to the ADC sampling clock frequency are illustrated in

■ 8-21 to 8-30. They are interpreted as follows:

Each figure contains the filter pass-band, transition band(s) and alias or stop-band(s) as shown in 🛭 8-20. The x-axis shows the offset frequency (after the NCO frequency shift) normalized to the ADC sampling rate F<sub>S</sub>.

For example, in the divide-by-4 complex setup, the output data rate is F<sub>S</sub> / 4 complex with a Nyquist zone of F<sub>S</sub> / 8 or 0.125 × F<sub>S</sub>. The transition band (colored in blue) is centered around 0.125 × F<sub>S</sub> and the alias transition band is centered at 0.375 × F<sub>S</sub>. The stop-bands (colored in red), which alias on top of the pass-band, are centered at  $0.25 \times F_S$  and  $0.5 \times F_S$ . The stop-band attenuation is greater than 85 dB.

图 8-20. Interpretation of the Decimation Filter Plots

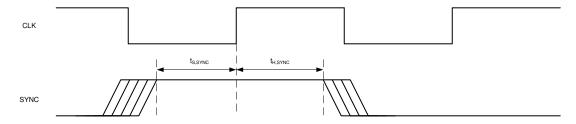

#### 8.3.4.6 SYNC

The PDN/SYNC pin can be used to synchronize multiple devices using an external SYNC signal. The PDN/SYNC pin can be configured via SPI (SYNC EN bit) from power down to synchronization functionality and is latched in by the rising edge of the sampling clock as shown in

8 8-31.

图 8-31. External SYNC timing diagram

The synchronization signal is only required when using the decimation filter - either using the SPI SYNC register or the PDN/SYNC pin. It resets internal clock dividers used in the decimation filter and aligns the internal clocks as well as I and Q data within the same sample. If no SYNC signal is given, the internal clock dividers is not be synchronized, which can lead to a fractional delay across different devices. The SYNC signal also resets the NCO phase and loads the new NCO frequency (same as the MIXER RESTART bit).

When trying to resynchronize during operation, the SYNC toggle should occur at 64\*K clock cycles, where K is an integer. This provids the phase continuity of the clock divider.

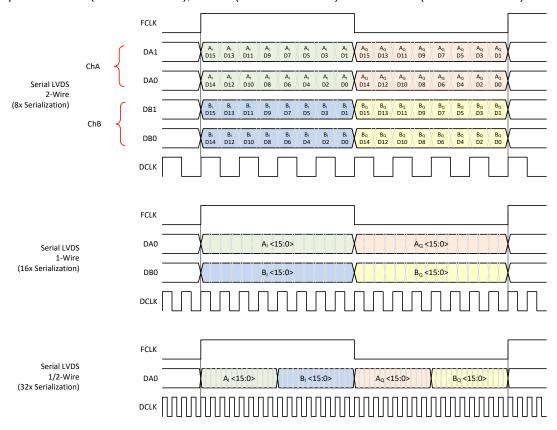

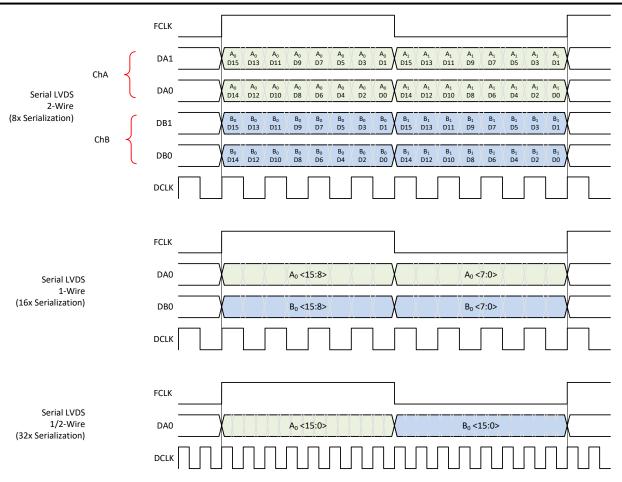

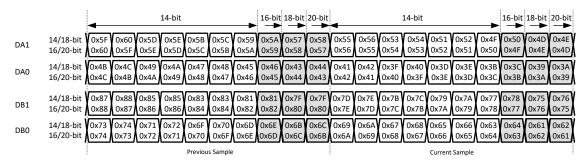

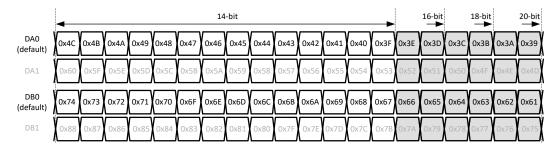

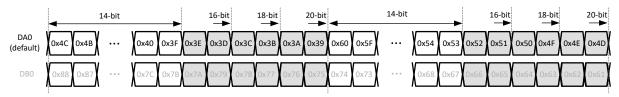

### 8.3.4.7 Output Formatting with Decimation

When using decimation, the output data is formatted as shown in 8 - 32 and 8 - 33. The examples are shown for 16-bit output for 2-wire (8x serialization), 1-wire (16x serialization) and 1/2-wire (32x serialization).

图 8-32. Output Data Format in Complex Decimation

表 8-3 illustrates the output interface data rate along with the corresponding DCLK/DCLKIN and FCLK frequencies based on output resolution (R), number of SLVDS lanes (L) and complex decimation setting (N).

Furthermore the table shows an actual lane rate example for the 2-, 1- and 1/2-wire interface, 16-bit output resolution and complex decimation by 4.

表 8-3. Serial LVDS Lane Rate Examples with Complex Decimation and 16-bit Output Resolution

| _ |                       |                      | •                    |            |                    | •             |                            |

|---|-----------------------|----------------------|----------------------|------------|--------------------|---------------|----------------------------|

|   | DECIMATION<br>SETTING | ADC SAMPLING<br>RATE | OUTPUT<br>RESOLUTION | # of WIRES | FCLK               | DCLKIN, DCLK  | DA/B0,1                    |

|   | N                     | F <sub>S</sub>       | R                    | L          | F <sub>S</sub> / N | [DA/B0,1] / 2 | F <sub>S</sub> x 2 x R/L/N |

|   |                       | 125 MSPS<br>55 MSPS  | 16                   | 2          | 31.25 MHz          | 250 MHz       | 500 MHz                    |

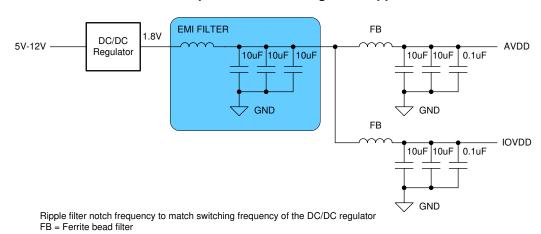

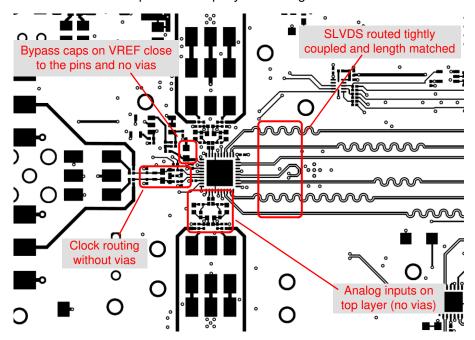

|   | 4                     |                      |                      | 1          | 31.23 1/11/12      | 500 MHz       | 1000 MHz                   |