www.ti.com

# ADC16V130 16-Bit, 130 MSPS A/D Converter With LVDS Outputs

Check for Samples: ADC16V130

## **FEATURES**

- **Dual Supplies: 1.8V and 3.0V Operation**

- On Chip Automatic Calibration During Power-

- **Low Power Consumption**

- Multi-Level Multi-Function Pins for CLK/DF and

- **Power-Down and Sleep Modes**

- On Chip Precision Reference and Sample-and-**Hold Circuit**

- On Chip Low Jitter Duty-Cycle Stabilizer

- Offset Binary or 2's Complement Data Format

- **Full Data Rate LVDS Output Port**

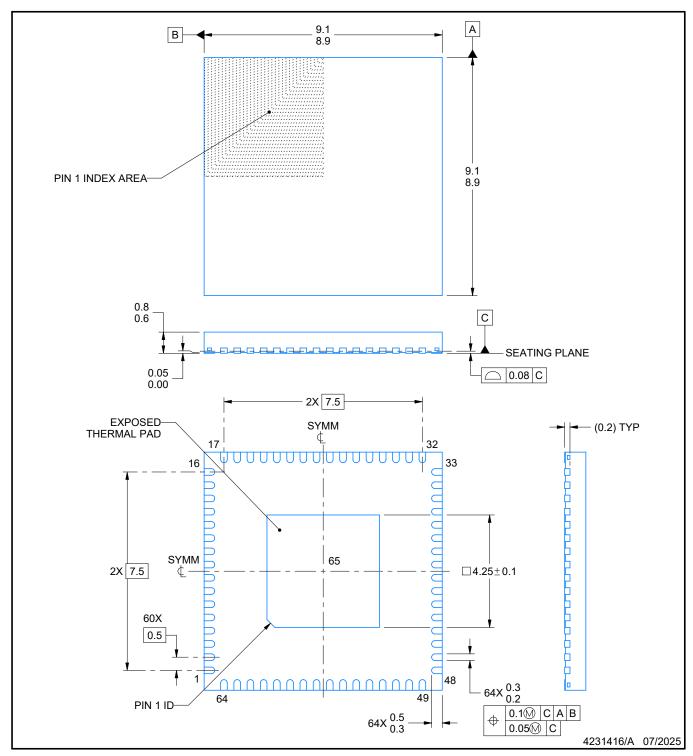

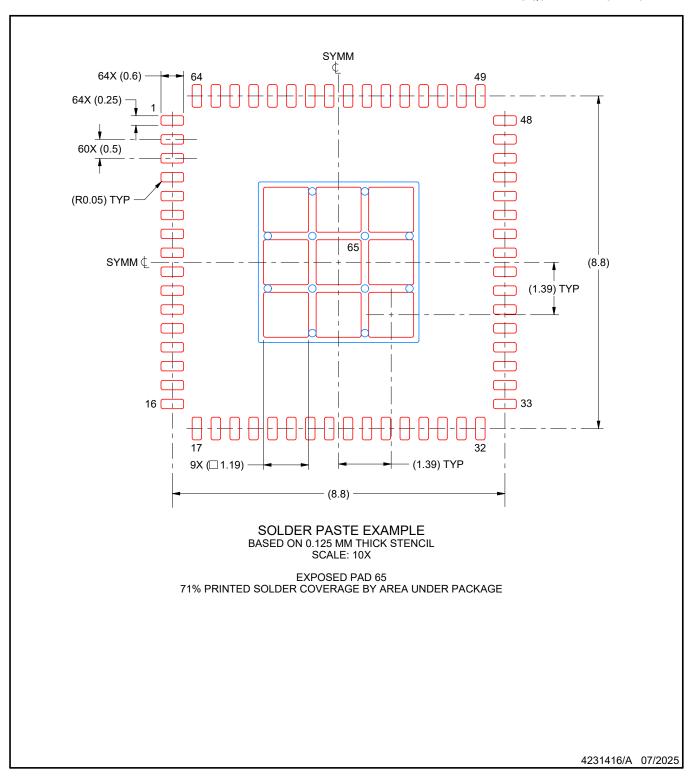

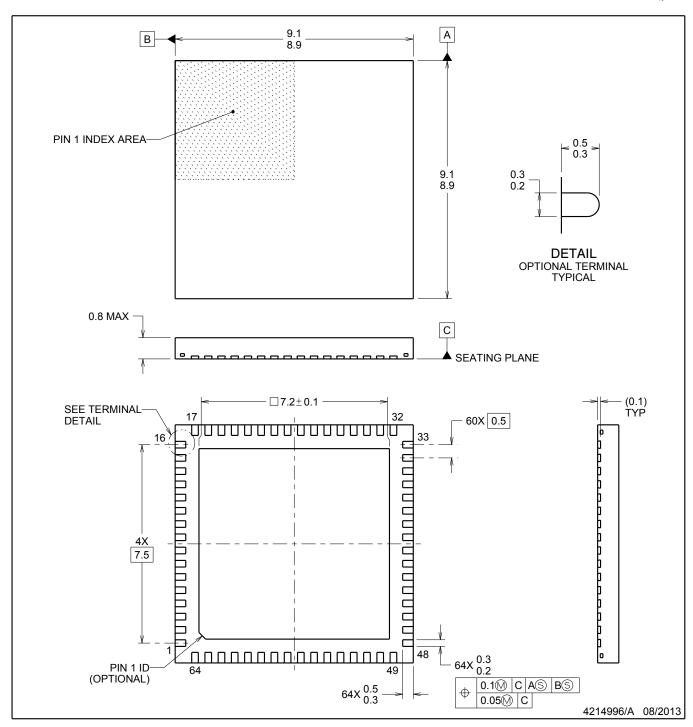

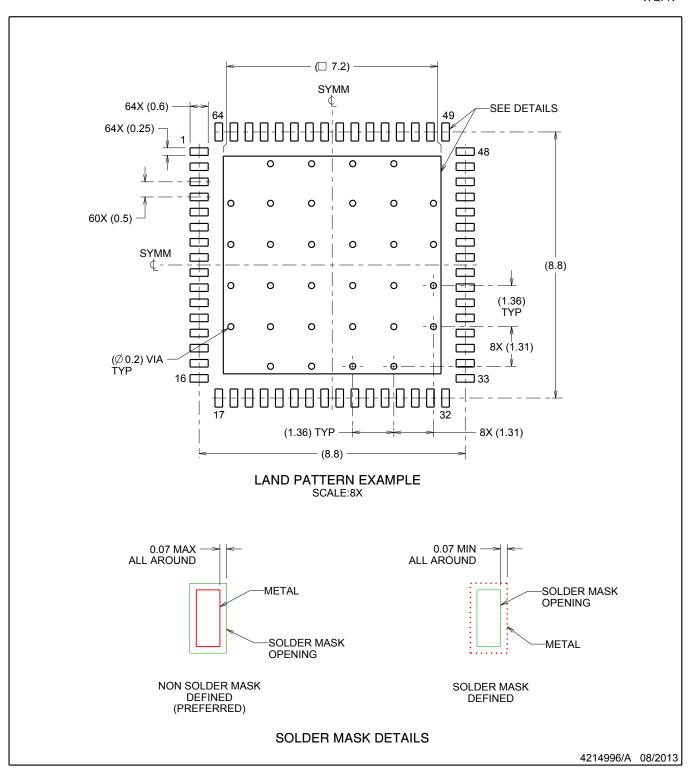

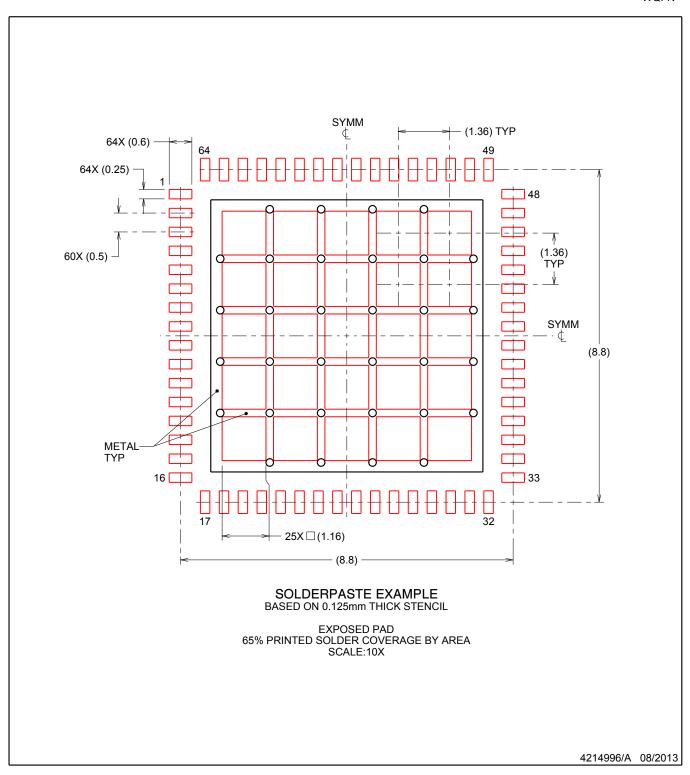

- 64-pin WQFN Package (9x9x0.8, 0.5mm Pin-Pitch)

#### **KEY SPECIFICATIONS**

**Resolution: 16 Bits**

**Conversion Rate: 130 MSPS**

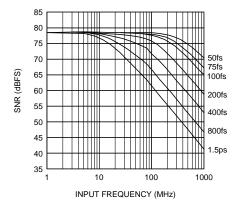

SNR

- (f<sub>IN</sub> = 10MHz): 78.5 dBFS (Typ)

$- (f_{IN} = 70MHz): 77.8 dBFS (Typ)$

- (f<sub>IN</sub> = 160MHz): 76.7 dBFS (Typ)

- (f<sub>IN</sub> = 10MHz): 95.5 dBFS (Typ)

- (f<sub>IN</sub> = 70MHz): 92.0 dBFS (Typ)

- (f<sub>IN</sub> = 160MHz): 90.6 dBFS (Typ)

Full Power Bandwidth: 1.4 GHz (Typ)

**Power Consumption**

Core: 650 mW (Typ)

- LVDS Driver: 105 mW (Typ)

Total: 755 mW (Typ)

Operating Temperature Range: -40°C ~ 85°C

#### APPLICATIONS

- **High IF Sampling Receivers**

- **Multi-carrier Base Station Receivers**

- GSM/EDGE, CDMA2000, UMTS, LTE, and WiMax

- **Test and Measurement Equipment**

- **Communications Instrumentation**

- **Data Acquisition**

- **Portable Instrumentation**

#### DESCRIPTION

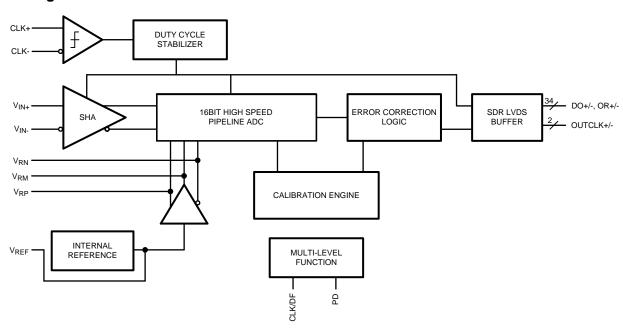

The ADC16V130 is a monolithic high performance analog-to-digital converter capable converting analog input signals into 16-bit digital words at rates up to 130 Mega Samples Per Second (MSPS). This converter uses a differential, pipelined architecture with digital error correction and an onchip sample-and-hold circuit to minimize power consumption and external component count while providing excellent dynamic performance. Automatic power-up calibration enables excellent dynamic performance and reduces part-to-part variation, and the ADC16V130 could be re-calibrated at any time by asserting and then de-asserting power-down. An integrated low noise and stable voltage reference and differential reference buffer amplifier easies board level design. On-chip duty cycle stabilizer with low additive jitter allows wide duty cycle range of input clock without compromising its dynamic performance. A unique sample-and-hold stage yields a full-power bandwidth of 1.4 GHz. The digital data is provided via full data rate LVDS outputs - making possible the 64pin, 9mm x 9mm WQFN package. The ADC16V130 operates on dual power supplies +1.8V and +3.0V with a power-down feature to reduce the power consumption to very low levels while allowing fast recovery to full operation.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

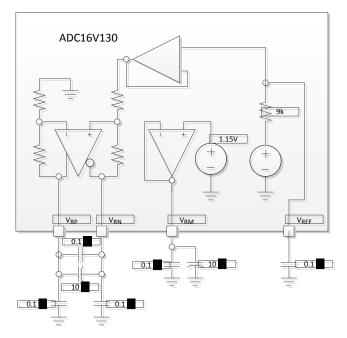

## **Block Diagram**

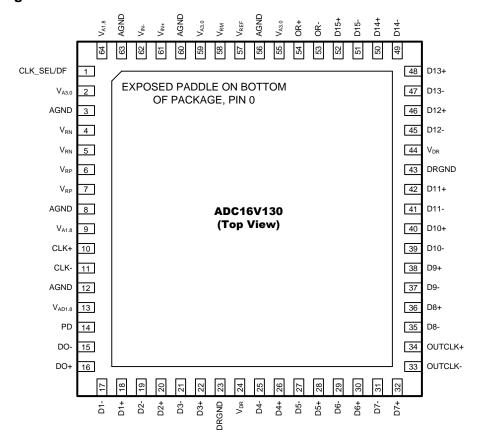

# **Connection Diagram**

## **PIN DESCRIPTIONS**

| Pin No.   | Sumb al          | Equivalent Circuit                 | CRIPTIONS  Function and Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG I/ | Symbol           | Equivalent Circuit                 | Function and Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |                  | 1                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 61        | V <sub>IN+</sub> | VA3.0  AGND                        | Differential analog input pins. The differential full-scale input signal level is 2.4Vpp as default. Each input pin signal centered on a common mode voltage, $V_{\text{CM}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6,7       | $V_{RP}$         | V <sub>A3.0</sub>                  | Upper reference voltage. This pin should not be used to source or sink current. The decoupling capacitor to AGND (low ESL $0.1\mu F$ ) should be placed very close to the pin to minimize stray inductance. $V_{RP}$ needs to be connected to $V_{RN}$ through a low ESL $0.1\mu F$ and a low ESR $10\mu F$ capacitors in parallel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4,5       | $V_{RN}$         | V <sub>REF</sub> O V <sub>RM</sub> | Lower reference voltage. This pin should not be used to source or sink current. The decoupling capacitor to AGND (low ESL 0.1µF) should be placed very close to the pin to minimize stray inductance. $V_{RN}$ needs to be connected to $V_{RP}$ through a low ESL 0.1µF and a low ESR 10µF capacitors in parallel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 58        | $V_{RM}$         | VA3.0<br>VRP                       | Common mode voltage The decoupling capacitor to AGND (low ESL $0.1\mu F$ ) should be placed as close to the pin as possible to minimize stray inductance. It is recommended to use $V_{RM}$ to provide the common mode voltage for the differential analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 57        | $V_{REF}$        | VA3.0  VA3.0  LDC  AGND            | Internal reference voltage output / External reference voltage input. By default, this pin is the output for the internal 1.2V voltage reference. This pin should not be used to sink or source current and should be decoupled to AGND with a 0.1µF, low ESL capacitor. The decoupling capacitors should be placed as close to the pins as possible to minimize inductance and optimize ADC performance. The size of decoupling capacitor should not be larger than 0.1µF, otherwise dynamic performance after power-up calibration can drop due to the long $V_{REF}$ settling. This pin can also be used as the input for a low noise external reference voltage. The output impedance for the internal reference at this pin is 9 k $\Omega$ and this can be overdriven provided the impedance of the external source is <<9 k $\Omega$ . Careful decoupling is just as essential when an external reference is used. The 0.1µF low ESL decoupling capacitor should be placed as close to this pin as possible. The Input differential voltage swing is equal to 2 * $V_{REF}$ . |

| 10        | CLK+             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11        | CLK-             | VA3.0 VA1.8 VA3.0 AGND             | Differential clock input pins. DC biasing is provided internally. For single-ended clock mode, drive CLK+ through AC coupling while decoupling CLK- pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **PIN DESCRIPTIONS (continued)**

| Pin No.                                  | Symbol                                                                     | Equivalent Circuit                                     | Function and Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL I/O                              |                                                                            |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15 - 22<br>25 - 32<br>35 - 42<br>45 - 52 | D0+/- to D3+/-<br>D4+/- to D7+/-<br>D8+/- to D11+/-<br>D12+/- to<br>D15+/- |                                                        | LVDS Data Output. The 16-bit digital output of the data converter is provided on these ports in a full data rate manner. A 100 $\Omega$ termination resistor must be placed between each pair of differential signals at the far end of the transmission line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 53, 54                                   | OR+/-                                                                      | VAS.0 VOR VAS.0 D. | Over-Range Indicator. Active High. This output is set High when analog input signal exceeds full scale of 16 bit conversion range (<0,> 65535). This signal is asserted coincidently with the over-range data word. A 100 $\Omega$ termination resistor must be placed between the differential signals at the far end of the transmission.                                                                                                                                                                                                                                                                                                                                                                                            |

| 33, 34                                   | OUTCLK+/-                                                                  | AGND DRGND AGND                                        | Output Clock. This pin is used to clock the output data. It has the same frequency as the sampling clock. One word of data is output in each cycle of this signal. A 100 $\Omega$ termination resistor must be placed between the differential clock signals at the far end of the transmission line. The rising edge of this signal should be used to capture the output data. See the detail Section on Timing Diagrams .                                                                                                                                                                                                                                                                                                            |

| 14                                       | PD                                                                         | VA3.0                                                  | This is a three-state pin.  PD = V <sub>A3.0</sub> , then Power Down is enabled. In the Power Down state, only the reference voltage circuitry remains active and power dissipation is reduced.  PD = V <sub>A3.0</sub> * (2/3), then Sleep mode is enabled. In Sleep mode is similar to Power Down mode - it consumes more power but has a faster recovery time.  PD = AGND, then Normal operation mode is turned on.                                                                                                                                                                                                                                                                                                                 |

| 1                                        | CLK_SEL/DF                                                                 | AGND                                                   | This is a four-state pin controlling two parameters: input clock selection and output data format.  CLK_SEL/DF = V <sub>A3.0</sub> , then CLK+ and CLK- are configured as a differential clock input and the output data format is 2's complement.  CLK_SEL/DF = V <sub>A3.0</sub> * (2/3), then CLK+ and CLK- are configured as a differential clock input and the output data format is offset binary.  CLK_SEL/DF = V <sub>A3.0</sub> * (1/3), then CLK+ is configured as a single-ended clock input and CLK- should be tied to AGND. The output data format is 2's complement.  CLK_SEL/DF = AGND, then CLK+ is configured as a single-ended clock input and CLK- should be tied to AGND. The output data format is offset binary. |

| POWER SU                                 | JPPLIES                                                                    |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2, 55, 59                                | V <sub>A3.0</sub>                                                          | Analog Power                                           | 3.0V Analog Power Supply. These pins should be connected to a quiet source and should be decoupled to AGND with 0.1µF capacitors located close to the power pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9, 64                                    | V <sub>A1.8</sub>                                                          | Analog Power                                           | 1.8V Analog Power Supply. These pins should be connected to a quiet source and should be decoupled to AGND with 0.1µF capacitors located close to the power pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13                                       | V <sub>AD1.8</sub>                                                         | Analog/Digital Power                                   | 1.8V Analog/Digital Power Supply. These pins should be connected to a quiet source and should be decoupled to AGND with 0.1µF capacitors located close to the power pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

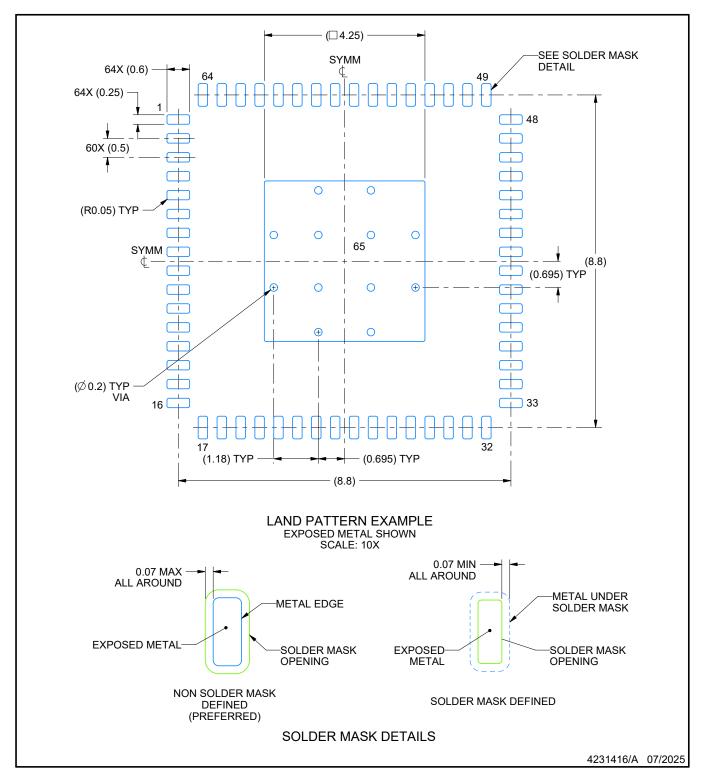

| 0, 3, 8, 12,<br>56, 60, 63               | AGND                                                                       | Analog Ground                                          | Analog Ground Return. The exposed pad (Pin 0) on back of the package must be soldered to ground plane to ensure rated performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24, 44                                   | $V_{DR}$                                                                   | Power                                                  | Output Driver Power Supply. This pin should be connected to a quiet voltage source and be decoupled to DRGND with a $0.1\mu F$ capacitor close to the power pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23, 43                                   | DRGND                                                                      | Ground                                                 | Output Driver Ground Return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| Supply Voltage (V <sub>A3.0</sub> )                                                                              | -                                                         | -0.3V to 4.2V                                              |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|--|--|--|--|

| Supply Voltage (V <sub>A1.8</sub> , V <sub>AD1.8</sub> , V <sub>DR</sub> )                                       |                                                           | -0.3V to 2.35V                                             |  |  |  |  |

| Voltage at any Pin except D0-D15,                                                                                | OVR, OUTCLK, CLK, V <sub>IN</sub>                         | -0.3V to (V <sub>A3.0</sub> +0.3V)<br>(Not to exceed 4.2V) |  |  |  |  |

| Voltage at CLK, V <sub>IN</sub> Pins                                                                             | ege at CLK, V <sub>IN</sub> Pins -0.3 (Not                |                                                            |  |  |  |  |

| Voltage at D0-D15, OR, OUTCLK P                                                                                  | 0.3V to (V <sub>DR</sub> + 0.3V)<br>(Not to exceed 2.35V) |                                                            |  |  |  |  |

| Input Current at any pin (4)                                                                                     | 5 mA                                                      |                                                            |  |  |  |  |

| Storage Temperature Range                                                                                        |                                                           | -65°C to +150°C                                            |  |  |  |  |

| Maximum Junction Temp (T <sub>J</sub> )                                                                          |                                                           | +150°C                                                     |  |  |  |  |

| Thermal Resistance (θ <sub>JA</sub> )                                                                            |                                                           | 20.4°C/W                                                   |  |  |  |  |

| Thermal Resistance (θ <sub>JC</sub> )                                                                            |                                                           | 1.4°C/W                                                    |  |  |  |  |

| ESD Rating <sup>(5)</sup>                                                                                        | Machine Model                                             | 200 V                                                      |  |  |  |  |

|                                                                                                                  | Human Body Model                                          | 2000 V                                                     |  |  |  |  |

| Soldering process must comply with Reflow Temperature Profile specifications. Refer to www.ti.com/packaging. (6) |                                                           |                                                            |  |  |  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is ensured to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified.

- (4) When the input voltage at any pin exceeds the power supplies (that is, V<sub>IN</sub> < AGND, or V<sub>IN</sub> > V<sub>A</sub>), the current at that pin should be limited to ±5 mA. The ±50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.

- (5) Human Body Model is 100 pF discharged through a 1.5 kΩ resistor. Machine Model is 220 pF discharged through 0 Ω.

- (6) Reflow temperature profiles are different for lead-free and non-lead-free packages.

# Operating Ratings<sup>(1)(2)</sup>

| 1 5 5                                                                               |                |

|-------------------------------------------------------------------------------------|----------------|

| Specified Temperature Range:                                                        | -40°C to +85°C |

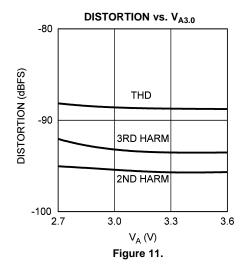

| 3.0V Analog Supply Voltage Range: (V <sub>A3.0</sub> )                              | +2.7V to +3.6V |

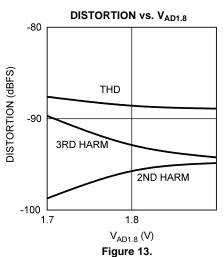

| 1.8V Supply Voltage Range: V <sub>A1.8</sub> , V <sub>AD1.8</sub> , V <sub>DR</sub> | +1.7V to +1.9V |

| Clock Duty Cycle                                                                    | 30/70 %        |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is ensured to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (2) All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified.

## **Converter Electrical Characteristics**

Unless otherwise specified, the following specifications apply:  $V_{A3.0} = +3.0V$ ,  $V_{A1.8} = V_{AD1.8} = V_{DR} = +1.8V$ ,  $f_{CLK} = 130$  MSPS,  $A_{IN} = -1$ dBFS, LVDS Rterm = 100  $\Omega$ ,  $C_L = 5$  pF. Typical values are for  $T_A = 25^{\circ}$ C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}$ C, unless otherwise noted. (1)

| Symbol           | Parameter                                            | Conditions                                           | Typical (2)           | Limits | Units<br>(Limits) |

|------------------|------------------------------------------------------|------------------------------------------------------|-----------------------|--------|-------------------|

| STATIC CO        | ONVERTER CHARACTERISTICS                             |                                                      |                       |        |                   |

|                  | Resolution with No Missing Codes                     |                                                      |                       | 16     | Bits (min)        |

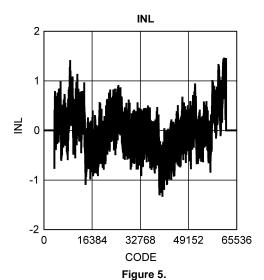

| INL              | Integral Non Linearity                               |                                                      | ±1.5                  |        | LSB               |

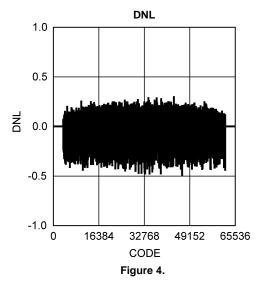

| DNL              | Differential Non Linearity                           |                                                      | ±0.45                 |        | LSB               |

| PGE              | Positive Gain Error                                  |                                                      | -4.2                  |        | %FS               |

| NGE              | Negative Gain Error                                  |                                                      | 3.7                   |        | %FS               |

| V <sub>OFF</sub> | Offset Error (V <sub>IN</sub> + = V <sub>IN</sub> −) |                                                      | 0.12                  |        | %FS               |

|                  | Under Range Output Code                              |                                                      | 0                     | 0      |                   |

|                  | Over Range Output Code                               |                                                      | 65535                 | 65535  |                   |

| REFEREN          | CE AND ANALOG INPUT CHARACTER                        | ISTICS(3)                                            |                       |        |                   |

| V <sub>CM</sub>  | Common Mode Input Voltage                            | V <sub>RM</sub> is the common mode reference voltage | V <sub>RM</sub> ±0.05 |        | V                 |

| $V_{RM}$         | Reference Ladder Midpoint Output Voltage             |                                                      | 1.15                  |        | V                 |

| V <sub>REF</sub> | Internal Reference Voltage                           |                                                      | 1.20                  |        | V                 |

|                  | Differential Analog Input Range                      | Internal Reference                                   | 2.4                   |        | $V_{PP}$          |

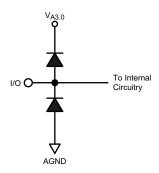

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A3.0</sub> or below GND will not damage this device, provided current is limited per Note 4 of the Absolute Maximum Ratings table. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section see Figure 1.

<sup>(2)</sup> Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

<sup>(3)</sup> The input capacitance is the sum of the package/pin capacitance and the sample and hold circuit capacitance.

## **Dynamic Converter Electrical Characteristics**

Unless otherwise specified, the following specifications apply:  $V_{A3.0} = +3.0V$ ,  $V_{A1.8} = V_{AD1.8} = V_{DR} = +1.8V$ ,  $f_{CLK} = 130$  MSPS,  $A_{IN} = -1$ dBFS, LVDS Rterm = 100  $\Omega$ ,  $C_L = 5$  pF. Typical values are for  $T_A = 25^{\circ}$ C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}$ C, unless otherwise noted. (1)

| Symbol                | Parameter                                                          | Conditions                 | Тур    | Limits | Units |

|-----------------------|--------------------------------------------------------------------|----------------------------|--------|--------|-------|

|                       | Resolution with no missing codes                                   |                            |        | 16     | Bits  |

| DR                    | Dynamic Range                                                      | 0V analog input is applied | 79     |        | dBFS  |

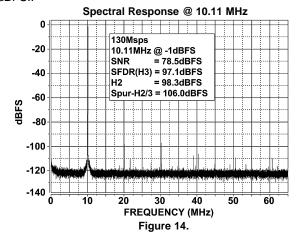

|                       |                                                                    | Fin = 10 MHz               | 78.5   |        | dBFS  |

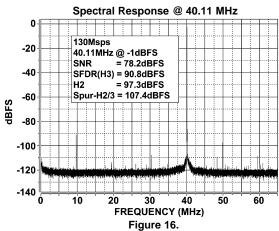

|                       |                                                                    | Fin = 40 MHz               | 78.2   |        | dBFS  |

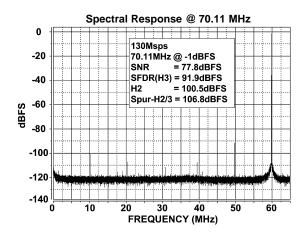

| DR SNR SFDR THD       | Signal-to-Noise Ratio (2)                                          | Fin = 70 MHz               | 77.8   |        | dBFS  |

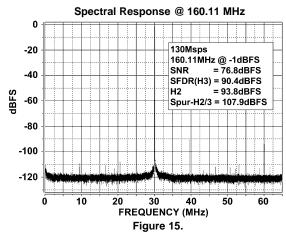

|                       |                                                                    | Fin = 160 MHz              | 76.7   | 75.5   | dBFS  |

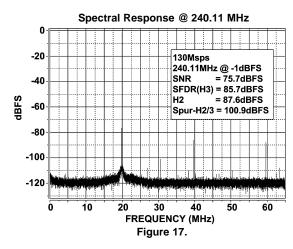

|                       |                                                                    | Fin = 240 MHz              | 75.6   |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | 95.5   |        | dBFS  |

|                       |                                                                    | Fin = 40 MHz               | 91     |        | dBFS  |

| SFDR                  | Single-tone Spurious Free Dynamic Range <sup>(2)</sup>             | Fin = 70 MHz               | 92     |        | dBFS  |

| THD                   | Tungo                                                              | Fin = 160 MHz              | 90.6   | 87     | dBFS  |

|                       |                                                                    | Fin = 240 MHz              | 85.3   |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | -91.5  |        | dBFS  |

|                       |                                                                    | Fin = 40 MHz               | -88.4  |        | dBFS  |

| THD                   | Total Harmonic Distortion <sup>(2)</sup>                           | Fin = 70 MHz               | -89.4  |        | dBFS  |

|                       |                                                                    | Fin = 160 MHz              | -87.1  | -81    | dBFS  |

|                       |                                                                    | Fin = 240 MHz              | -82.8  |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | -95.5  |        | dBFS  |

| H2                    |                                                                    | Fin = 40 MHz               | -104.1 |        | dBFS  |

|                       | Second-order Harmonic <sup>(2)</sup>                               | Fin = 70 MHz               | -95.6  |        | dBFS  |

|                       |                                                                    | Fin = 160 MHz              | -91.5  | -88    | dBFS  |

|                       |                                                                    | Fin = 240 MHz              | -85.3  |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | -98.3  |        | dBFS  |

| H2<br>H3<br>Spur-H2/3 |                                                                    | Fin = 40 MHz               | -89.4  |        | dBFS  |

|                       | Third-order Harmonic <sup>(2)</sup>                                | Fin = 70 MHz               | -92    |        | dBFS  |

|                       |                                                                    | Fin = 160 MHz              | -90.6  | -87    | dBFS  |

|                       |                                                                    | Fin = 240 MHz              | -87.8  |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | 106    |        | dBFS  |

|                       |                                                                    | Fin = 40 MHz               | 103.2  |        | dBFS  |

| Spur-H2/3             | Worst Harmonic or Spurious Tone excluding H2 and H3 <sup>(2)</sup> | Fin = 70 MHz               | 104.1  |        | dBFS  |

|                       | evenantia i is and i is.                                           | Fin = 160 MHz              | 101.5  | 94     | dBFS  |

|                       |                                                                    | Fin = 240 MHz              | 98.4   |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | 78.3   |        | dBFS  |

|                       |                                                                    | Fin = 40 MHz               | 77.8   |        | dBFS  |

| SINAD                 | Signal-to-Noise and Distortion Ratio (2)                           | Fin = 70 MHz               | 77.5   |        | dBFS  |

|                       |                                                                    | Fin = 160 MHz              | 76.3   |        | dBFS  |

|                       |                                                                    | Fin = 240 MHz              | 74.8   |        | dBFS  |

|                       |                                                                    | Fin = 10 MHz               | 12.7   |        | Bits  |

|                       |                                                                    | Fin = 40 MHz               | 12.6   |        | Bits  |

| ENOB                  | Effective Number of Bits                                           | Fin = 70 MHz               | 12.6   |        | Bits  |

|                       |                                                                    | Fin = 160 MHz              | 12.4   |        | Bits  |

|                       |                                                                    | Fin = 240 MHz              | 12.1   |        | Bits  |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A3.0</sub> or below GND will not damage this device, provided current is limited per Note 4 of the Absolute Maximum Ratings table. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section see Figure 1.

<sup>2)</sup> This parameter is specified in units of dBFS - indicating the equivalent value that would be attained with a full-scale input signal.

## **Dynamic Converter Electrical Characteristics (continued)**

Unless otherwise specified, the following specifications apply:  $V_{A3.0} = +3.0V$ ,  $V_{A1.8} = V_{AD1.8} = V_{DR} = +1.8V$ ,  $f_{CLK} = 130$  MSPS,  $A_{IN} = -1$ dBFS, LVDS Rterm = 100  $\Omega$ ,  $C_L = 5$  pF. Typical values are for  $T_A = 25^{\circ}$ C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}$ C, unless otherwise noted.<sup>(1)</sup>

| Symbol | Parameter            | Conditions             | Тур | Limits | Units |

|--------|----------------------|------------------------|-----|--------|-------|

|        | Full Power Bandwidth | -3dB Compression Point | 1.4 |        | GHz   |

# **Power Supply Electrical Characteristics**

Unless otherwise specified, the following specifications apply:  $V_{A3.0} = +3.0V$ ,  $V_{A1.8} = V_{AD1.8} = V_{DR} = +1.8V$ ,  $f_{CLK} = 130$  MSPS,  $A_{IN} = -1$ dBFS, LVDS Rterm = 100  $\Omega$ ,  $C_L = 5$  pF. Typical values are for  $T_A = 25^{\circ}$ C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}$ C, unless otherwise noted. (1)

| Symbol              | Parameter                    | Conditions                                                                | Typical | Limits | Units<br>(Limits) |

|---------------------|------------------------------|---------------------------------------------------------------------------|---------|--------|-------------------|

| I <sub>A3.0</sub>   | Analog 3.0V Supply Current   | Full Operation <sup>(2)</sup>                                             | 174.5   | 208    | mA (max)          |

| I <sub>A1.8</sub>   | Analog 1.8V Supply Current   | Full Operation <sup>(2)</sup>                                             | 36      | 42     | mA (max)          |

| I <sub>AD1.8R</sub> | Digital 1.8V Supply Current  | Full Operation (2)                                                        | 34      | 41     | mA (max)          |

| I <sub>DR</sub>     | Output Driver Supply Current | Full Operation                                                            | 58.3    |        | mA                |

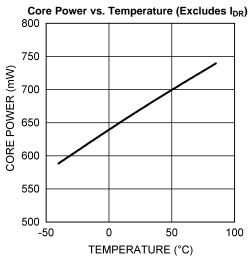

|                     | Core Power Consumption       | Excludes I <sub>DR</sub> <sup>(2)</sup>                                   | 650     | 773    | mW (max)          |

|                     | Driver Power Consumption     | Current drawn from the $V_{DR}$ supply; Fin = 10 MHz Rterm = 100 $\Omega$ | 105     |        | mW                |

|                     |                              | Normal operation; Fin = 10 MHz                                            | 755     |        | mW                |

|                     | Total Power Consumption      | Power down state, with external clock                                     | 3       |        | mW                |

|                     |                              | Sleep state, with external clock                                          | 30      |        | mW                |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A3.0</sub> or below GND will not damage this device, provided current is limited per Note 4 of the Absolute Maximum Ratings table. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section see Figure 1.

#### **LVDS Electrical Characteristics**

Unless otherwise specified, the following specifications apply:  $V_{A3.0} = +3.0V$ ,  $V_{A1.8} = V_{AD1.8} = V_{DR} = +1.8V$ ,  $f_{CLK} = 130$  MSPS,  $A_{IN} = -1$ dBFS, LVDS Rterm = 100  $\Omega$ ,  $C_L = 5$  pF. Typical values are for  $T_A = 25$ °C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25$ °C, unless otherwise noted. (1)

| Symbol                                               | Parameter                    | Parameter Conditions    |      | Тур | Max  | Units |  |

|------------------------------------------------------|------------------------------|-------------------------|------|-----|------|-------|--|

| LVDS DC SPECIFICATIONS (apply to pins DO to D15, OR) |                              |                         |      |     |      |       |  |

| V <sub>OD</sub>                                      | Output Differential Voltage  | 100 Ω Differential Load | 175  | 250 | 325  | mV    |  |

| Vos                                                  | Output Offset Voltage        | 100 Ω Differential Load | 1.15 | 1.2 | 1.25 | V     |  |

| Ios                                                  | Output Short Circuit Current | 0 Ω Differential Load   |      | 2.5 |      | mA    |  |

| I <sub>OZ</sub>                                      | Output Open Circuit Current  | Termination is open     | -20  | ± 1 | 20   | μΑ    |  |

(1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A3.0</sub> or below GND will not damage this device, provided current is limited per Note 4 of the Absolute Maximum Ratings table. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section see Figure 1.

<sup>(2)</sup> This parameter is ensured only at 25°C. For power dissipation over temperature range, refer to Core Power vs. Temperature plot in Typical Performance Characteristics, Dynamic Performance

## **Timing Specifications**

Unless otherwise specified, the following specifications apply:  $V_{IN} = -1 dBFS$ , AGND = DRGND = 0V,  $V_{A3.0} = +3.0 V$ ,  $V_{A1.8} = V_{AD1.8} = V_{DR} = +1.8 V$ , Internal  $V_{REF} = +1.2 V$ ,  $f_{CLK} = 130$  MHz,  $V_{CM} = V_{RM}$ ,  $C_L = 5$  pF, Single-Ended Clock Mode, Offset Binary Format. Typical values are for  $T_A = 25^{\circ}C$ . Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}C$ , unless otherwise noted. (1)

| Parameter                       | Conditions                                                     | Тур                                                            | Limits | Units           |

|---------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|--------|-----------------|

| Input Clock Frequency           |                                                                |                                                                | 130    | MHz (max)       |

| Minimum Clock Frequency         |                                                                | 1                                                              |        | MHz (min)       |

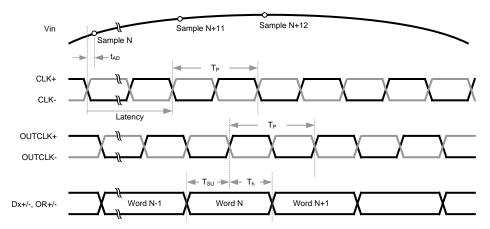

| Data Output Setup Time (Tsu)(2) | Measured @ Vdr/2; Fclk = 130 MHz.                              | 3.3                                                            | 2.5    | nS (min)        |

| Data Output Hold Time (Th)(2)   | Measured @ Vdr/2; Fclk = 130 MHz.                              | 3.3                                                            | 2.5    | nS (min)        |

| Pipeline Latency <sup>(3)</sup> |                                                                | 11                                                             |        | Clock<br>Cycles |

| Aperture Jitter                 |                                                                | 80                                                             |        | fS rms          |

| Power-Up Time                   | From assertion of Power to specified level of performance.     | 0.5+ 10 <sup>3</sup> *(2 <sup>22</sup> +2 <sup>16</sup> )/FCLK |        | mS              |

| Power-Down Recovery Time        | From de-assertion of power down mode to output data available. | 0.1+ 10 <sup>3</sup> *(2 <sup>19</sup> +2 <sup>16</sup> )/FCLK |        | mS              |

| Sleep Recovery Time             | From de-assertion of sleep mode to output data available.      | 100                                                            |        | μS              |

- (1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A3.0</sub> or below GND will not damage this device, provided current is limited per Note 4 of the Absolute Maximum Ratings table. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section see Figure 1.

- (2) This parameter is a function of the CLK frequency increasing directly as the frequency is lowered. At frequencies less than 130 MHz, use the following formulae to calculate the setup and hold times:

- For Data and OR+/- Outputs:  $Tsu = \frac{1}{2}*Tp 0.5$  ns (typical)

- For Data and OR+/- Outputs: Th =  $\frac{1}{2}$ \*Tp 0.5 ns (typical) where Tp = CLK input period = OUTCLK period

- (3) Input signal is sampled with the falling edge of the CLK input.

Figure 1.

(1)

#### **Specification Definitions**

**APERTURE DELAY** is the time after the falling edge of the clock to when the input signal is acquired or held for conversion.

**APERTURE JITTER (APERTURE UNCERTAINTY)** is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.

**CLOCK DUTY CYCLE** is the ratio of the time during one cycle that a repetitive digital waveform is high to the total time of one period. The specification here refers to the ADC clock input signal.

**COMMON MODE VOLTAGE (V<sub>CM</sub>)** is the common DC voltage applied to both input terminals of the ADC.

**CONVERSION LATENCY** is the number of clock cycles between initiation of conversion and the time when data is presented to the output driver stage. Data for any given sample is available at the output pins the Pipeline Delay plus the Output Delay after the sample is taken. New data is available at every clock cycle, but the data lags the conversion by the pipeline delay.

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

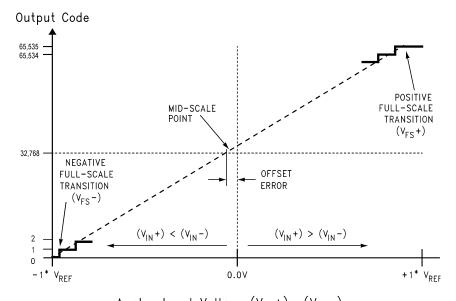

**GAIN ERROR** is the deviation from the ideal slope of the transfer function. It can be calculated as:

Gain Error = Positive Full Scale Error - Negative Full Scale Error

It can also be expressed as Positive Gain Error and Negative Gain Error, which are calculated as:

PGE = Positive Full Scale Error - Offset Error NGE = Offset Error - Negative Full Scale Error (2)

**INTEGRAL NON LINEARITY (INL)** is a measure of the deviation of each individual code from a best fit straight line. The deviation of any given code from this straight line is measured from the center of that code value.

**INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time. It is defined as the ratio of the power in the intermodulation products to the total power in the original frequencies. IMD is usually expressed in dBFS.

**LSB (LEAST SIGNIFICANT BIT)** is the bit that has the smallest value or weight of all bits. This value is  $V_{FS}/2^n$ , where " $V_{FS}$ " is the full scale input voltage and "n" is the ADC resolution in bits.

**MISSING CODES** are those output codes that will never appear at the ADC outputs. The ADC16V130 is ensured not to have any missing codes.

MSB (MOST SIGNIFICANT BIT) is the bit that has the largest value or weight. Its value is one half of full scale.

**NEGATIVE FULL SCALE ERROR** is the difference between the actual first code transition and its ideal value of ½ LSB above negative full scale.

**OFFSET ERROR** is the difference between the two input voltages  $(V_{IN+} - V_{IN-})$  required to cause a transition from code 32767LSB and 32768LSB with offset binary data format.

PIPELINE DELAY (LATENCY) See CONVERSION LATENCY.

**POSITIVE FULL SCALE ERROR** is the difference between the actual last code transition and its ideal value of 1½ LSB below positive full scale.

**SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the power of input signal to the total power of all other spectral components below one-half the sampling frequency, not including harmonics and DC.

**SIGNAL TO NOISE AND DISTORTION (SINAD)** Is the ratio, expressed in dB, of the power of the input signal to the total power of all of the other spectral components below half the clock frequency, including harmonics but excluding DC.

**SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the power of input signal and the peak spurious signal power, where a spurious signal is any signal present in the output spectrum that is not present at the input.

**TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dB, of the total power of the first seven harmonic to the input signal power. THD is calculated as:

THD =

$$20\log_{10}\sqrt{\frac{f_2^2 + f_3^2 + ... + f_8^2}{f_1^2}}$$

where

f<sub>1</sub><sup>2</sup> is the power of the fundamental frequency and f<sub>2</sub><sup>2</sup> through f<sub>8</sub><sup>2</sup> are the powers of the first seven harmonics in the output spectrum.

**SECOND HARMONIC DISTORTION (2^{ND} HARM or H2)** is the difference expressed in dB, from the power of its  $2^{nd}$  harmonic level to the power of the input signal.

**THIRD HARMONIC DISTORTION (3<sup>RD</sup> HARM or H3)** is the difference expressed in dB, from the power of the 3<sup>nd</sup> harmonic level to the power of the input signal.

**HIGHEST SPURIOUS EXCEPT H2 and H3 (Spur-H2/3)** is the difference, expressed in dB, between the power of input signal and the peak spurious signal power except H2 and H3, where a spurious signal is any signal present in the output spectrum that is not present at the input.

# **Timing Diagrams**

Figure 2. Digital Output Timing

## **Transfer Characteristic**

Analog Input Voltage  $(V_{IN} +) - (V_{IN} -)$

Figure 3. Transfer Characteristic (Offset Binary Format)

Copyright © 2008–2013, Texas Instruments Incorporated

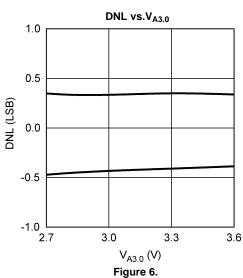

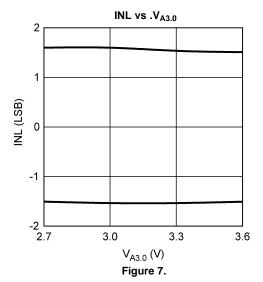

# Typical Performance Characteristics, DNL, INL

Unless otherwise noted, these specifications apply:  $V_{A3.0}$ = +3.0V,  $V_{A1.8}$ ,  $V_{AD1.8}$ ,  $V_{DR}$  = 1.8V,  $f_{CLK}$  = 130 MSPS. Differential Clock Mode, Offset Binary Format. LVDS Rterm = 100  $\Omega$ .  $C_L$  = 5 pF. Typical values are at  $T_A$  = +25°C. Fin = 10MHz with -1dBFS.

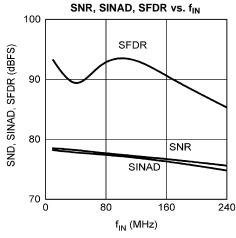

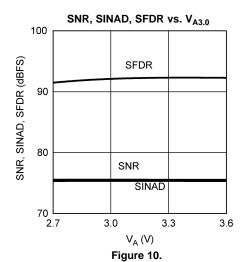

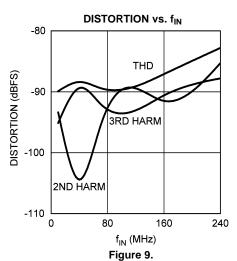

# Typical Performance Characteristics, Dynamic Performance

Unless otherwise noted, these specifications apply:  $V_{A3.0}$ = +3.0V,  $V_{A1.8}$ ,  $V_{AD1.8}$ ,  $V_{DR}$  = 1.8V,  $f_{CLK}$  = 130 MSPS. Differential Clock Mode, Offset Binary Format. LVDS Rterm = 100  $\Omega$ .  $C_L$  = 5 pF. Typical values are at  $T_A$  = +25°C. Fin = 160MHz with

SNR, SINAD, SFDR vs. VAD1.8

SNR, SINAD, SFDR (dBFS) 90 80 SNR SINAD

SFDR

$V_{AD1.8}\left(V\right)$ Figure 12.

1.8

Submit Documentation Feedback

100

70 └ 1.7

# Typical Performance Characteristics, Dynamic Performance (continued)

Unless otherwise noted, these specifications apply:  $V_{A3.0}$ = +3.0V,  $V_{A1.8}$ ,  $V_{AD1.8}$ ,  $V_{DR}$  = 1.8V,  $f_{CLK}$  = 130 MSPS. Differential Clock Mode, Offset Binary Format. LVDS Rterm = 100  $\Omega$ .  $C_L$  = 5 pF. Typical values are at  $T_A$  = +25°C. Fin = 160MHz with -1dBFS..

Figure 19.

Figure 18.

#### **FUNCTIONAL DESCRIPTION**

Operating on dual +1.8 and +3.0V supplies, the ADC16V130 digitizes a differential analog input signals to 16 bits, using a differential pipelined architecture with error correction circuitry and an on-chip sample-and-hold circuit to ensure maximum performance. The user has the choice of using an internal 1.2V stable reference, or using an external 1.2V reference. Internal 1.2V reference has high output impedance of > 9 k $\Omega$  and can be easily over-driven by external reference. Two multi-level multi-function pins can program data format, clock mode, power down and sleep mode.

#### **ADC Architecture**

The ADC16V130 architecture consists of a highly linear and wide bandwidth sample-and-hold circuit, followed by a switched capacitor pipeline ADC. Each stage of the pipeline ADC consists of low resolution flash sub-ADC and an inter-stage multiplying digital-to-analog converter (MDAC), which is a switched capacitor amplifier with a fixed stage signal gain and DC level shifting circuits. The amount of DC level shifting is dependent on sub-ADC digital output code. 16bit final digital output is the result of the digital error correction logic, which receives digital output of each stage including redundant bits to correct offset error of each sub-ADC.

### **APPLICATIONS INFORMATION**

#### **OPERATING CONDITIONS**

We recommend that the following conditions be observed for operation of the ADC16V130:

$2.7V \le V_{A3.0} \le 3.6V$   $1.7V \le V_{A1.8} \le 1.9V$   $1.7V \le V_{AD1.8} \le 1.9V$   $1.7V \le V_{DR} \le 1.9V$   $5 \text{ MSPS} \le F_{CLK} \le 130 \text{ MSPS}$   $V_{REF} \le 1.2V$  $V_{CM} = 1.15V \text{ (from } V_{RM})$

## **ANALOG INPUTS**

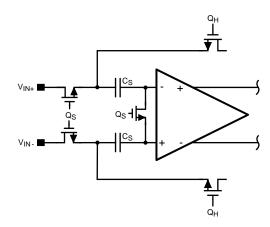

Analog input circuit of the ADC16V130 is a differential switched capacitor sample-and-hold circuit (see Figure 20) that provides optimum dynamic performance wide input frequency range with minimum power consumption. The clock signal alternates sample mode  $(Q_S)$  and hold mode  $(Q_H)$ . An integrated low jitter duty cycle stabilizer ensures constant optimal sample and hold time over wide range of input clock duty cycle. The duty cycle stabilizer is always turned on during normal operation.

During sample mode, analog signals ( $V_{IN+}$ ,  $V_{IN-}$ ) are sampled across two sampling capacitor ( $C_S$ ) while the amplifier in the sample-and-hold circuit is idle. The dynamic performance of the ADC16V130 is likely determined during sampling mode. The sampled analog inputs ( $V_{IN+}$ ,  $V_{IN-}$ ) are held during hold mode by connecting input side of the sampling capacitors to output of the amplifier in the sample-and-hold circuit while driving pipeline ADC core.

The signal source, which drives the ADC16V130, is recommended to have source impedance less than 100  $\Omega$  over wide frequency range for optimal dynamic performance.

A shunt capacitor can be placed across the inputs to provide high frequency dynamic charging current during sample mode and also absorb any switching charge coming from the ADC16V130. A shunt capacitor can be placed across each input to GND for similar purpose. Smaller physical size and low ESR and ESL shunt capacitor is recommended.

The value of shunt capacitor should be carefully chosen to optimize the dynamic performance at certain input frequency range. Larger value shunt capacitors can be used for low input frequency range, but the value has to be reduced at high input frequency range.

Balancing impedance at positive and negative input pin over entire signal path must be ensured for optimal dynamic performance.

Copyright © 2008–2013, Texas Instruments Incorporated

Figure 20. Simplified Switched-Capacitor Sample-and-hold Circuit

#### **Input Common Mode**

The analog inputs of the ADC16V130 are not internally dc biased and the range of input common mode is very narrow. Hence it is highly recommended to use the common mode voltage ( $V_{RM}$ , typically 1.15V) as input common mode for optimal dynamic performance regardless of DC and AC coupling applications. Input common mode signal must be decoupled with low ESL  $0.1\mu F$  at the far end of load point to minimize noise performance degradation due to any coupling or switching noise between the ADC16V130 and input driving circuit.

## **Driving Analog Inputs**

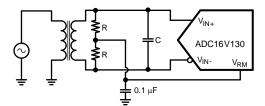

For low frequency applications, either a flux or balun transformer can convert single-ended input signal into differential and drive the ADC16V130 without additive noise. An example is shown in Figure 21.  $V_{RM}$  pin is used to bias the input common mode by connecting the center tap of the transformer's secondary ports. Flux transformer is used for this example, but AC coupling capacitors should be added once balun type transformer is used.

Figure 21. Transformer Drive Circuit for Low Input Frequency

Transformer has a characteristic of band pass filtering. It sets lower band limit by being saturated at frequencies below a few MHz and sets upper frequency limit due to its parasitic resistance and capacitance. The transformer core will be saturated with excessive signal power and it causes distortion as equivalent load termination becomes heavier at high input frequencies. This is a reason to reduce shunt capacitors for high IF sampling application to balance the amount of distortion caused by transformer and charge kick-back noise from the device.

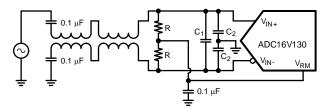

As input frequency goes higher with the input network in Figure 22, amplitude and phase unbalance increase between positive and negative inputs ( $V_{IN+}$  and  $V_{IN-}$ ) due to the inherent impedance mismatch between the two primary ports of the transformer while one is connected to the signal source and the other is connected to GND. Distortion increases as the result.

Cascaded transmission line transformers can be used for high frequency applications like high IF sampling base station receiver channel. Transmission line transformer has less stray capacitance between primary and secondary ports and so the amount of impedance at secondary ports is effectively less even with the given inherent impedance mismatch on the primary ports. Cascading two transmission line transformers further reduces the effective stray capacitance from the secondary of ports of the secondary transformer to primary ports of first transformer, where impedance is mismatched. A transmission line transformer, for instance MABACT0040 from M/A-COM, with center tap on secondary port could further reduce amplitude and phase mismatch.

Figure 22. Transformer Drive Circuit for High Input Frequency

## **Equivalent Input Circuit and Its S11**

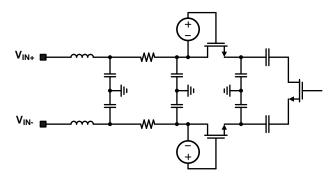

Input circuit of the ADC16V130 during sample mode is a differential switched capacitor as shown in Figure 23. Bottom plate sampling switch is bootstrapped in order to reduce its turn on impedance and its variation across input signal amplitude. Bottom plate sampling switches and top plate sampling switch are all turned off during hold mode. The sampled analog input signal is processed throughout the following pipeline ADC core. Equivalent impedance changes drastically between sample and hold mode while significant amount of charge injection occurs during the transition between the two operating modes.

Distortion and SNR heavily rely on the signal integrity, impedance matching during sample mode and charge injection while switching sampling switches.

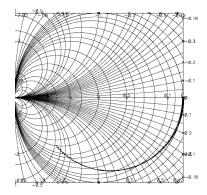

Figure 23. Input Equivalent Circuit

A measured S11 of the input circuit of the ADC16V130 is shown in Figure 24 (Currently the figure is a simulated one. It is subject to be changed later. Note that the simulated S11 closely matches with the measured S11). Up to 500 MHz, it is predominantly capacitive loading with small stray resistance and inductance as shown in Figure 24. An appropriate resistive termination at a given input frequency band has to be added to improve signal integrity. Any shunt capacitor on analog input pin deteriorates signal integrity but it provides high frequency charge to absorb the charge inject generated while sampling switches are toggling. A optimal shunt capacitor is dependent on input signal frequency as well as impedance characteristic of analog input signal path including components like transformer, termination resistor, DC coupling capacitors.

Figure 24. S11 Curve of Input Circuit

# **CLOCK INPUT CONSIDERATIONS**

#### **Clock Input Modes**

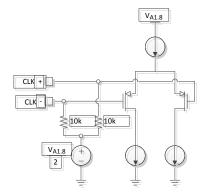

The ADC16V130 provides a low additive jitter differential clock receiver for optimal dynamic performance at wide input frequency range. Input common mode of the clock receiver is internally biased at  $V_{A1.8}/2$  through a 10 k $\Omega$  each to be driven by DC coupled clock input as shown in Figure 25. However while DC coupled clock input drives CLK+ and CLK-, it is recommend the common mode (average voltage of CLK+ and CLK-) not to be higher than  $V_{A1.8}/2$  in order to prevent substantial tail current reduction, which might cause lowered jitter performance. Meanwhile, CLK+ and CLK- should not become lower than AGND. A high speed back-to-back diode connected between CLK+ and CLK- could limit the maximum swing, but this could cause signal integrity concerns when the diode turns on and reduce load impedance instantaneously.

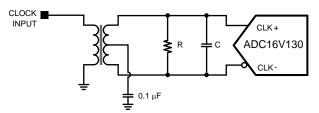

A preferred differential clocking through a transformer coupled is shown in Figure 26. A  $0.1\mu F$  decoupling capacitor on the center tap of the secondary ports of a flux type transformer stabilizes clock input common mode. Differential clocking increases the maximum amplitude of the clock input at the pins twice as large as that with singled-ended mode as shown in Figure 27. Clock amplitude is recommended to be as large as possible while CLK+ and CLK- both never exceed supply rails of  $V_{A1.8}$  and AGND. With a given equivalent input noise of the differential clock receiver shown in Figure 25, larger clock amplitude at CLK+ and CLK- pins increases its slope around zero-crossing point so that higher signal-to-noise could be obtained by reducing the noise contributed by clock signal path.

Figure 25. Equivalent Clock Receiver

The differential receiver of the ADC16V130 has excellent low noise floor but its bandwidth is wide as multiple times of clock rate. The wide band noise folds back to nyquist frequency band in frequency domain at ADC output. Increased slope of the input clock lowers the equivalent noise contributed by the differential receiver.

A band-pass filter (BPF) with narrow pass band and low insertion loss could be added on the clock input signal path when wide band noise of clock source is noticeably large compared to the input equivalent noise of the differential clock receiver.

Load termination could be a combination of R and C instead of a pure R. This RC termination could improve noise performance of clock signal path by filtering out high frequency noise through a low pass filter. The size of R and C is dependent on the clock rate and slope of the clock input.

A LVPECL and/or LVDS driver could also drive the ADC16V130. However the full dynamic performance of the ADC16V130 might not be achieved due to the high noise floor of the driving circuit itself especially in high IF sampling application.

Figure 26. Differential Clocking, Transformer Coupled

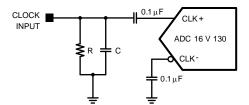

Singled-ended clock can drive CLK+ pin through a 0.1µF AC coupling capacitor while CLK- is decoupled to AGND through a 0.1µF capacitor as shown in Figure 27.

Figure 27. Singled-Ended 1.8V Clocking, Capacitive AC Coupled

## **Duty Cycle Stabilizer**

Highest operating speed with optimal performance could be only achieved with 50% of clock duty cycle because the switched-capacitor circuit of the ADC16V130 is designed to have equal amount of settling time between each stage. The maximum operating frequency could be reduced accordingly while clock duty cycle departs from 50%.

The ADC16V130 contains a duty cycle stabilizer that adjusts non-sampling (rising) clock edge to make the duty cycle of the internal clock over 30 to 70% of input clock duty cycle. The duty cycle stabilizer is always on because the noise and distortion performance are not affected at all. It is not recommended to use the ADC16V130 at the clock frequencies less than 5 MSPS, at which the feedback loop in the duty cycle stabilizer becomes unstable.

# Clock Jitter vs. Dynamic Performance

High speed and high resolution ADCs require low noise clock input to ensure its full dynamic performance over wide input frequency range. SNR  $(SNR_{Fin})$  at a given input frequency (Fin) can be calculated by:

SNR<sub>Fin</sub> =

$$10 \log_{10} \left[ \frac{A^2/2}{V_N^2 + (2\pi \text{Fin x Tj})^2/2} \right]$$

with a given total noise power  $(V_N^2)$  of an ADC, total rms jitter  $(T_i)$ , and input amplitude (A) in dBFS.

Clock signal path must be treated as an analog signal whenever aperture jitter affects the dynamic performance of the ADC16V130. Power supplies for the clock drivers has to be separated from the ADC output drive supplies to prevent modulated clock signal with the ADC digital output signals. Higher noise floor and/or increased distortion/spur might result from any coupling noise from ADC digital output signals to analog input and clock signals.

In IF sampling applications, the signal-to-noise ratio is particularly affected by clock jitter as shown in Figure 28. *Tj* is the integrated noise power of the clock signal divided by the slope of clock signal around tripping point. Upper limit of the noise integration is independent of applications and set by the bandwidth of the clock signal path. However lower limit of the noise integration highly relies on the applications. In base station receiver channel applications, the lower limit is determined by channel bandwidth and space from an adjacent channel.

Figure 28. SNR with given Jitter vs. Input Frequency

## **CALIBRATION**

Automatic calibration engine contained within the ADC16V130 improves dynamic performance and reduces its part-to-part variation. Digital output signals including output clock (OUTCLK+/-) are all logic low while calibrating. The ADC16V130 is automatically calibrated when the device is powered up. Optimal dynamic performance might not be obtained if power-up time is longer than internal delay time (~32mS @ 130 MSPS clock rate). In this case, the ADC16V130 could be re-calibrated by asserting and then de-asserting power down mode. Re-calibration is recommended whenever operating clock rate changes.

#### **VOLTAGE REFERENCE**

A stable and low noise voltage reference and its buffer amplifier are built into the ADC16V130. The input full scale is two times of  $V_{REF}$ , which is same as VBG (On-chip bandgap output having 9 k $\Omega$  output impedance) as well as  $V_{RP}$  -  $V_{RN}$  as shown in Figure 29. The input range can be adjusted by changing  $V_{REF}$  either internally or externally. An external reference with low output impedance can easily over-drive  $V_{REF}$  pin. Default  $V_{REF}$  is 1.2V. Input common mode voltage ( $V_{RM}$ ) is a fixed voltage level of 1.15V. Maximum SNR can be achieved at maximum input range of 1.2V  $V_{REF}$ . Although the ADC16V130 dynamic and static performance is optimized at  $V_{REF}$  of 1.2V, reducing  $V_{REF}$  can improve SFDR performance with sacrificing SNR of the ADC16V130.

#### Reference Decoupling