# ADC12DJ5200-SP 10.4GSPS 单通道或 5.2GSPS 双通道 12 位射频采样模数转换器 (ADC)

## 1 特性

- 辐射耐受性：

- 电离辐射总剂量 (TID) : 300krad (Si)

- 单粒子锁定 (SEL) : 120MeV-cm<sup>2</sup>/mg

- 单粒子翻转 (SEU) 抗扰度寄存器

- ADC 内核：

- 12 位分辨率

- 单通道模式下的采样率高达 10.4GSPS

- 双通道模式下的采样率高达 5.2GSPS

- 性能规格：

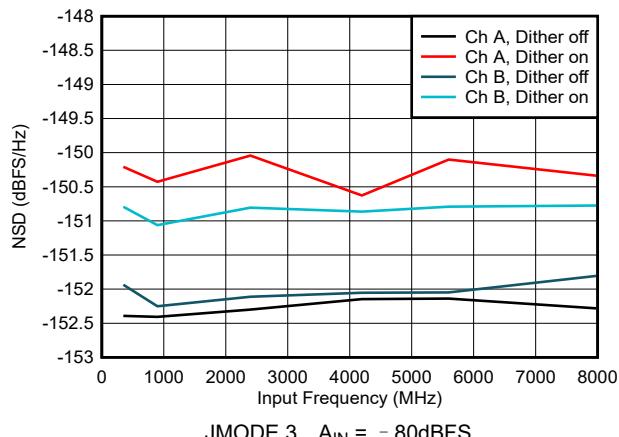

- 本底噪声 ( -20dBFS ,  $V_{FS} = 1V_{PP-DIFF}$  ) :

- 双通道模式 : -151.8dBFS/Hz

- 单通道模式 : -154.4dBFS/Hz

- ENOB ( 双通道 ,  $F_{IN} = 2.4GHz$  ) : 8.6 位

- $V_{CMI}$  为 0V 时的缓冲模拟输入：

- 模拟输入带宽 (-3dB) : 8GHz

- 可用输入频率范围 : > 10GHz

- 满量程输入电压 ( $V_{FS}$  , 默认值) : 0.8V<sub>PP</sub>

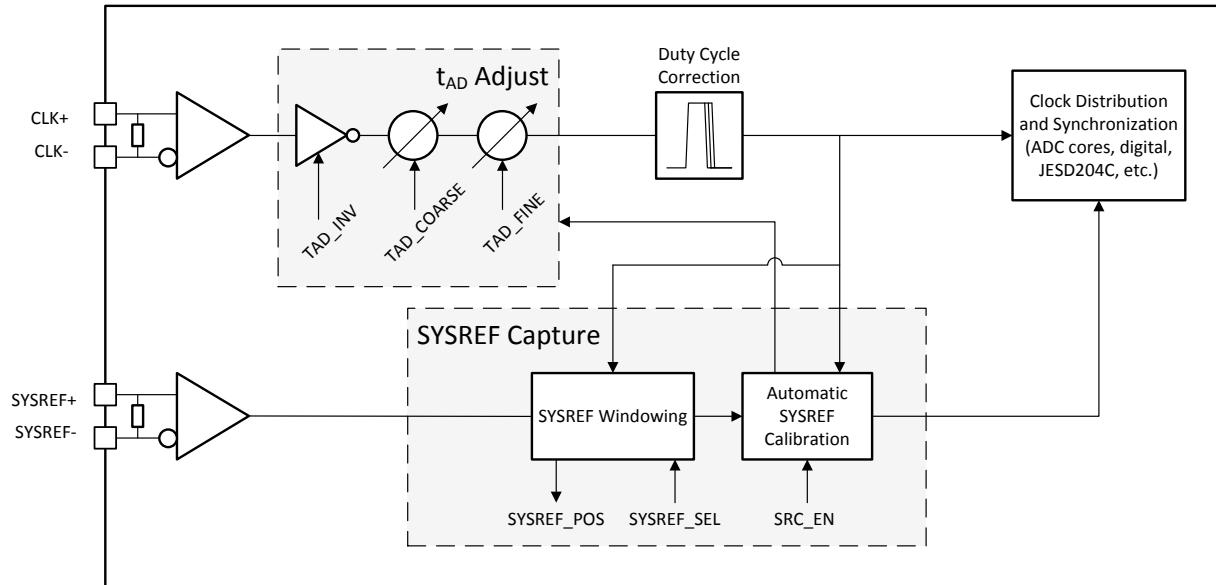

- 无噪声孔径延迟 ( $t_{AD}$ ) 调节：

- 精确采样控制 : 19fs 步长

- 简化同步和交错

- 温度和电压不变延迟

- 简便易用的同步特性：

- 自动 SYSREF 计时校准

- 样片标记时间戳

- JESD204C 串行数据接口：

- 最大通道速率 : 17.16Gbps

- 支持 64b/66b 和 8b/10b 编码

- 8b/10b 模式兼容 JESD204B

- 可选数字下变频器 (DDC) :

- 4 倍、8 倍、16 倍和 32 倍复杂抽取

- 每个 DDC 均具有四个独立的 32 位 NCO

- 峰值射频输入功率 (Diff) : +26.5dBm

( +27.5dBFS , 560x 满量程功率 )

- 可实现均衡的可编程 FIR 滤波器

- 功耗 : 4W

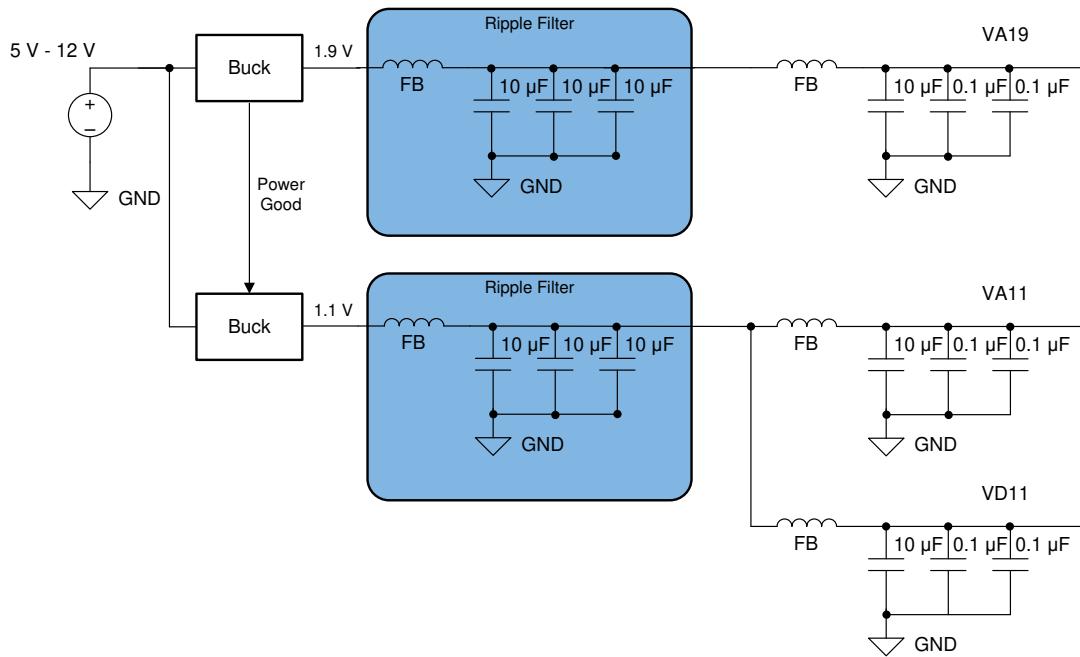

- 电源 : 1.1V、1.9V

## 2 应用

- 宽带数字转换器

- 电子战 (信号情报、电子情报)

- 卫星通信 (SATCOM)

- 射频采样软件定义无线电 (SDR)

### 3 说明

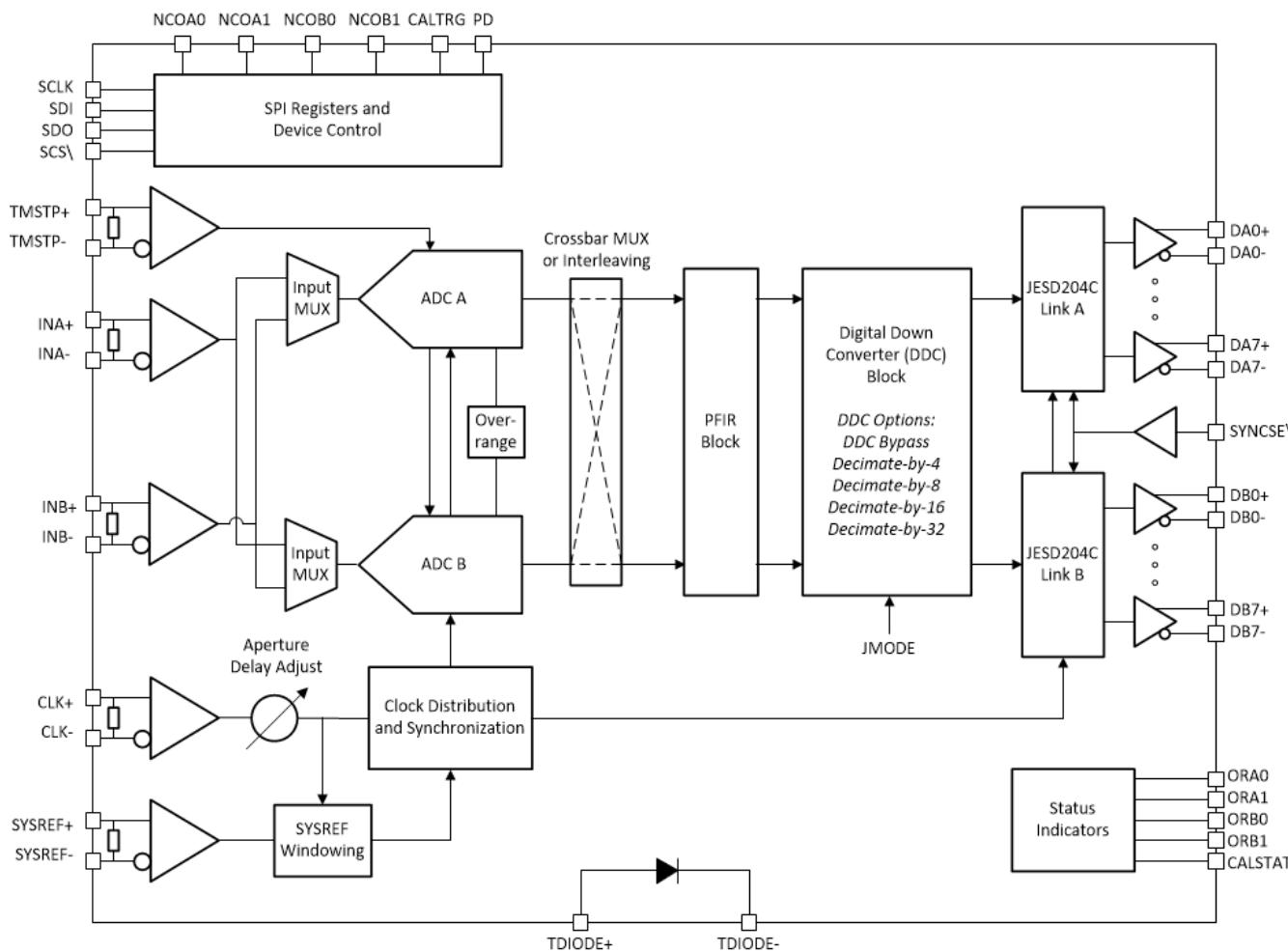

ADC12DJ5200-SP 器件是一款射频采样千兆采样模数转换器 (ADC)，可对从直流到 10GHz 以上的输入频率进行直接采样。ADC12DJ5200-SP 可配置为双通道 5.2GSPS ADC 或单通道 10.4GSPS ADC。支持高达 10GHz 的可用输入频率范围，可对频率捷变系统的 L、S、C 和 X 频带进行直接射频采样。

ADC12DJ5200-SP 使用具有多达 16 个串行通道的高速 JESD204C 输出接口，支持高达 17.16Gbps 的线路速率。通过 JESD204C 子类 1 支持确定性延迟和多器件同步。JESD204C 接口可进行配置，对线路速率和通道数进行权衡。支持 8b/10b 和 64b/66b 数据编码方案。64b/66b 编码支持前向纠错 (FEC)，可改进误码率。此接口向后兼容 JESD204B 接收器。

无噪声孔径延迟调节和 **SYSREF** 窗口等创新的同步特性可简化多通道应用的系统设计。提供可选的数字下变频器 (**DDC**)，以便将数字信号频谱下变频到基带信号并降低接口速率。可编程 **FIR** 滤波器可实现片上均衡。

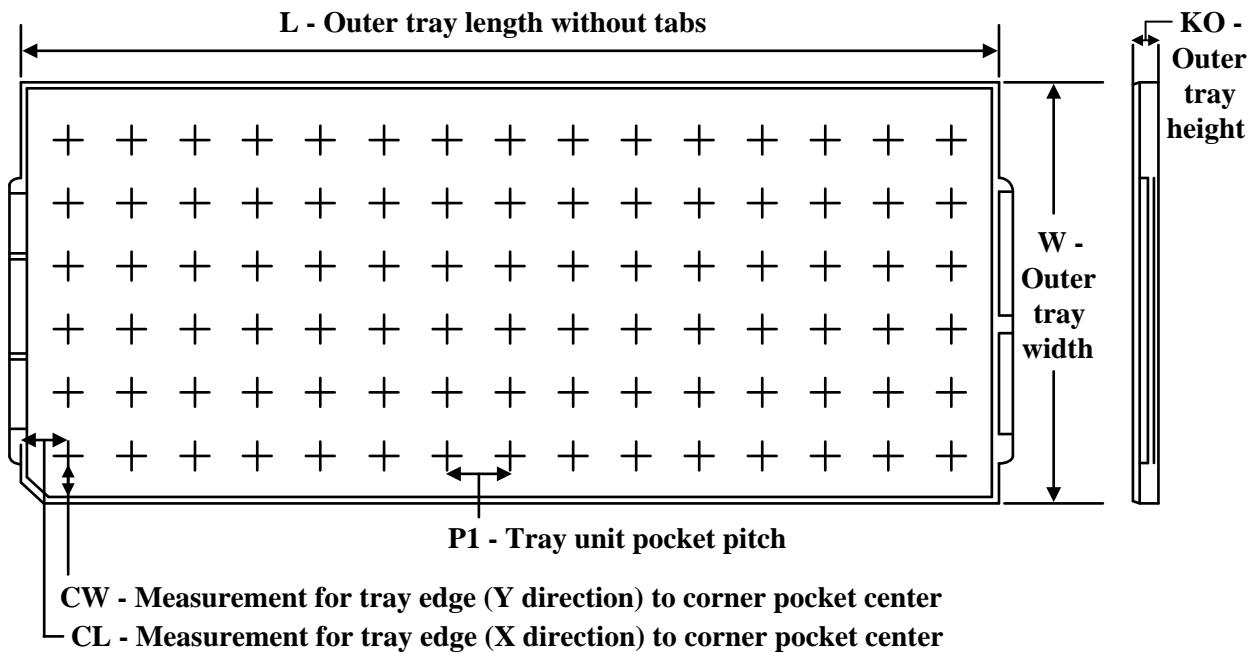

## 封装信息

| 器件型号           | 封装 <sup>(1)</sup> | 封装尺寸 <sup>(2)</sup> |

|----------------|-------------------|---------------------|

| ADC12DJ5200-SP | FCBGA (144)       | 10mm × 10mm         |

(1) 有关更多信息, 请参阅 [节 10](#)。

(2) 封装尺寸(长×宽)为标称值,并包括引脚(如适用)。

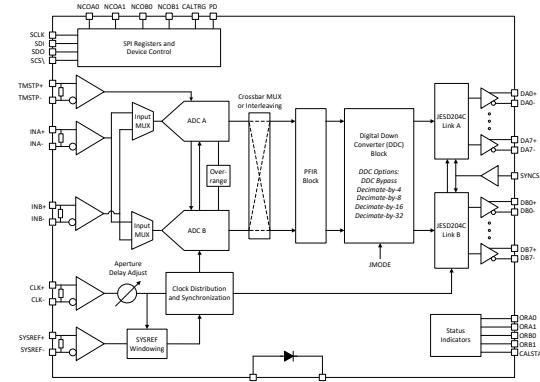

ADC12DJ5200-SP 方框图

本资源的原文使用英文撰写。为方便起见, TI 提供了译文;由于翻译过程中可能使用了自动化工具, TI 不保证译文的准确性。为确认准确性, 请务必访问 [ti.com](http://ti.com) 参考最新的英文版本 (控制文档)。

## 内容

|                      |           |                       |            |

|----------------------|-----------|-----------------------|------------|

| <b>1 特性</b>          | <b>1</b>  | 6.4 器件功能模式            | <b>92</b>  |

| <b>2 应用</b>          | <b>1</b>  | 6.5 编程                | <b>114</b> |

| <b>3 说明</b>          | <b>1</b>  | 6.6 SPI 寄存器映射         | <b>116</b> |

| <b>4 引脚配置和功能</b>     | <b>3</b>  | <b>7 应用信息免责声明</b>     | <b>178</b> |

| <b>5 规格</b>          | <b>9</b>  | 7.1 应用信息              | <b>178</b> |

| 5.1 绝对最大额定值          | 9         | 7.2 典型应用              | <b>178</b> |

| 5.2 ESD 等级           | 9         | 7.3 初始化设置             | <b>181</b> |

| 5.3 建议运行条件           | 10        | 7.4 电源相关建议            | <b>182</b> |

| 5.4 热性能信息            | 10        | 7.5 布局                | <b>183</b> |

| 5.5 电气特性：直流规格        | 11        | <b>8 器件和文档支持</b>      | <b>188</b> |

| 5.6 电气特性：功耗          | 13        | 8.1 器件支持              | <b>188</b> |

| 5.7 电气特性：交流规格（双通道模式） | 14        | 8.2 文档支持              | <b>188</b> |

| 5.8 电气特性：交流规格（单通道模式） | 19        | 8.3 接收文档更新通知          | <b>189</b> |

| 5.9 时序要求             | 25        | 8.4 支持资源              | <b>189</b> |

| 5.10 开关特性            | 27        | 8.5 商标                | <b>189</b> |

| 5.11 典型特性            | 31        | 8.6 静电放电警告            | <b>189</b> |

| <b>6 详细说明</b>        | <b>62</b> | 8.7 术语表               | <b>189</b> |

| 6.1 概述               | 62        | <b>9 修订历史记录</b>       | <b>189</b> |

| 6.2 功能方框图            | 63        | <b>10 机械、封装和可订购信息</b> | <b>190</b> |

| 6.3 特性说明             | 64        |                       |            |

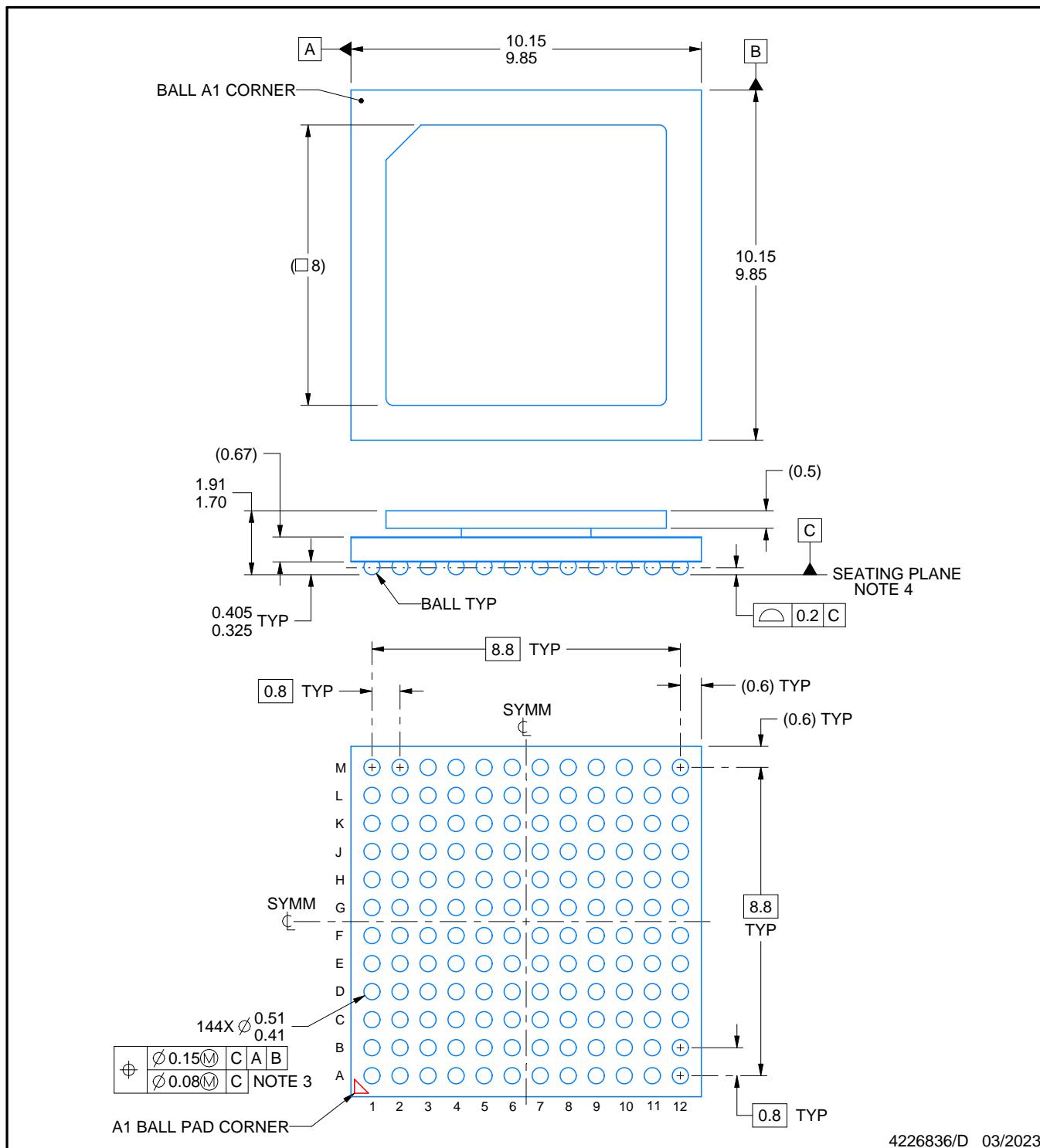

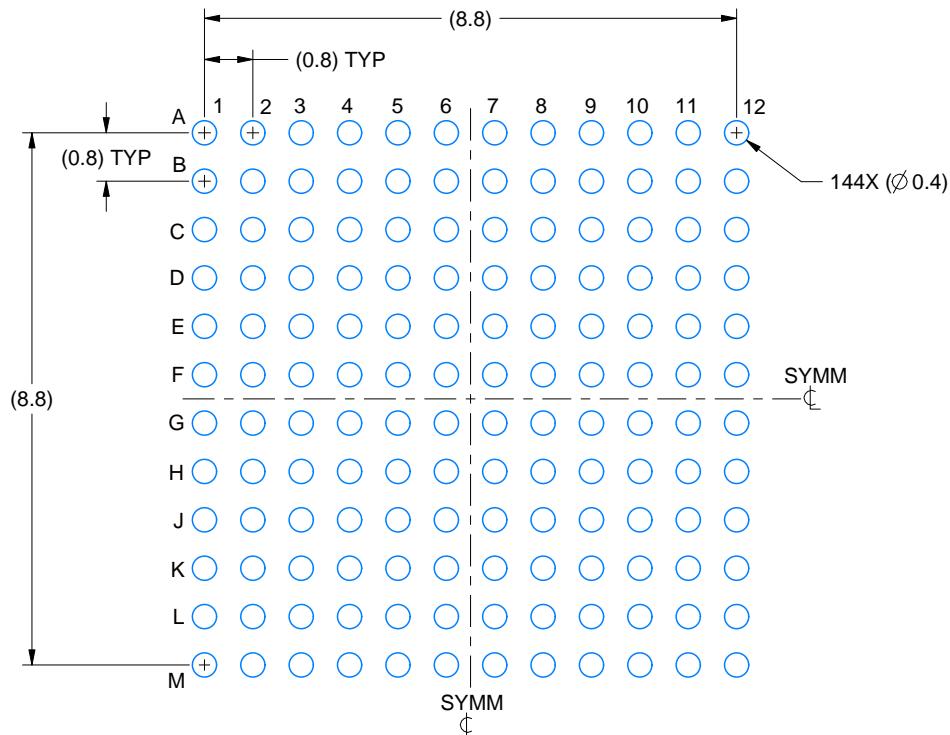

## 4 引脚配置和功能

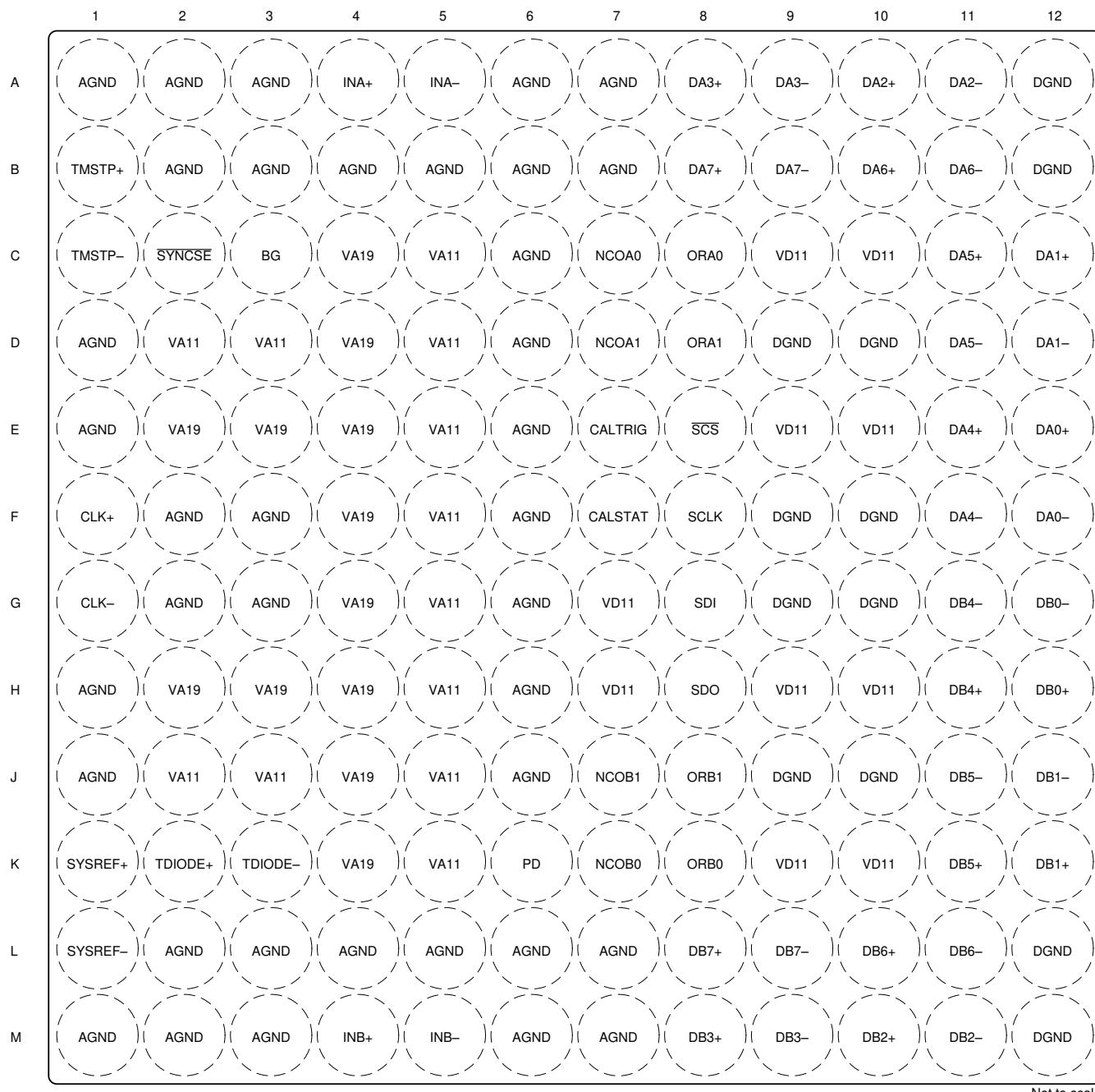

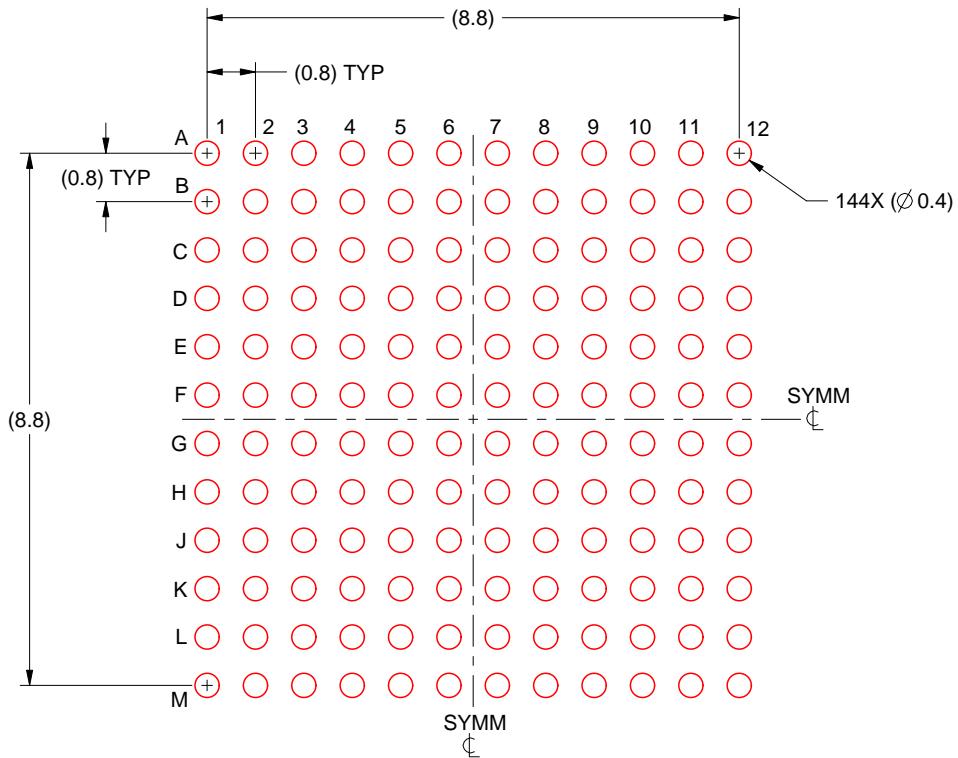

图 4-1. ALR 封装、144 焊球倒装芯片 BGA

( 顶视图 )

表 4-1. 引脚功能

| 引脚      |                                                                                                                                                                            | 类型 | 说明                                                                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 编号                                                                                                                                                                         |    |                                                                                                                                                                           |

| AGND    | A1、A2、<br>A3、A6、<br>A7、B2、<br>B3、B4、<br>B5、B6、<br>B7、C6、<br>D1、D6、<br>E1、E6、<br>F2、F3、F6、<br>G2、G3、<br>G6、H1、<br>H6、J1、J6、<br>L2、L3、L4、<br>L5、L6、L7、<br>M1、M2、<br>M3、M6、M7 | —  | 模拟电源接地。将 AGND 和 DGND 连接到电路板上的公共接地层 (GND)。                                                                                                                                 |

| BG      | C3                                                                                                                                                                         | O  | 带隙电压输出。如 <a href="#">建议运行条件</a> 表中所指定，该引脚只能提供小电流并驱动有限的电容负载。该引脚可以在不使用时保持断开。                                                                                                |

| CALSTAT | F7                                                                                                                                                                         | O  | 前台校准状态输出或器件警报输出。功能通过 CAL_STATUS_SEL 进行编程。该引脚可以在不使用时保持断开。                                                                                                                  |

| CALTRIG | E7                                                                                                                                                                         | I  | 前台校准触发器输入。只有在 CAL_TRIG_EN 中选择硬件校准触发时才使用此引脚，否则将使用 CAL_SOFT_TRIG 执行软件触发。不使用时将此引脚连接到 GND。                                                                                    |

| CLK+    | F1                                                                                                                                                                         | I  | 器件 (采样) 时钟正输入。强烈建议将时钟信号交流耦合至这个输入以获得最佳性能。在单通道模式下，在上升沿和下降沿对模拟输入信号进行采样。在双通道模式下，在上升沿对模拟信号进行采样。该差分输入具有内部未修整 $100\Omega$ 差分终端，并且只要将 DEVCLK_LVPECL_EN 设置为 0，该差分输入就会自偏置为理想输入共模电压。 |

| CLK -   | G1                                                                                                                                                                         | I  | 器件 (采样) 时钟负输入。TI 强烈建议使用交流耦合以获得最佳性能。                                                                                                                                       |

| DA0+    | E12                                                                                                                                                                        | O  | 用于通道 A、通道 0 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。        |

| DA0 -   | F12                                                                                                                                                                        | O  | 用于通道 A、通道 0 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                         |

| DA1+    | C12                                                                                                                                                                        | O  | 用于通道 A、通道 1 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。        |

| DA1 -   | D12                                                                                                                                                                        | O  | 用于通道 A、通道 1 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                         |

| DA2+    | A10                                                                                                                                                                        | O  | 用于通道 A、通道 2 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。        |

| DA2 -   | A11                                                                                                                                                                        | O  | 用于通道 A、通道 2 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                         |

| DA3+    | A8                                                                                                                                                                         | O  | 用于通道 A、通道 3 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。        |

| DA3 -   | A9                                                                                                                                                                         | O  | 用于通道 A、通道 3 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                         |

| DA4+    | E11                                                                                                                                                                        | O  | 用于通道 A、通道 4 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。        |

| DA4 -   | F11                                                                                                                                                                        | O  | 用于通道 A、通道 4 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                         |

**表 4-1. 引脚功能 (续)**

| 引脚    |     | 类型 | 说明                                                                                                                                                                 |

|-------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 编号  |    |                                                                                                                                                                    |

| DA5+  | C11 | ○  | 用于通道 A、通道 5 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DA5 - | D11 | ○  | 用于通道 A、通道 5 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DA6+  | B10 | ○  | 用于通道 A、通道 6 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接，或者使用 $0\Omega$ 至 $1M\Omega$ 电阻连接到 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。该引脚可以在不使用时保持断开。     |

| DA6 - | B11 | ○  | 用于通道 A、通道 6 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DA7+  | B8  | ○  | 用于通道 A、通道 7 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DA7 - | B9  | ○  | 用于通道 A、通道 7 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DB0+  | H12 | ○  | 用于通道 B、通道 0 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DB0 - | G12 | ○  | 用于通道 B、通道 0 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DB1+  | K12 | ○  | 用于通道 B、通道 1 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开。                                                                        |

| DB1 - | J12 | ○  | 用于通道 B、通道 1 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DB2+  | M10 | ○  | 用于通道 B、通道 2 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DB2 - | M11 | ○  | 用于通道 B、通道 2 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DB3+  | M8  | ○  | 用于通道 B、通道 3 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DB3 - | M9  | ○  | 用于通道 B、通道 3 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开。                                                                                                                         |

| DB4+  | H11 | ○  | 用于通道 B、通道 4 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DB4 - | G11 | ○  | 用于通道 B、通道 4 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DB5+  | K11 | ○  | 用于通道 B、通道 5 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DB5 - | J11 | ○  | 用于通道 B、通道 5 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

| DB6+  | L10 | ○  | 用于通道 B、通道 6 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。 |

| DB6 - | L11 | ○  | 用于通道 B、通道 6 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                  |

表 4-1. 引脚功能 (续)

| 引脚    |                                                                 | 类型 | 说明                                                                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 编号                                                              |    |                                                                                                                                                                                                                                                                    |

| DB7+  | L8                                                              | O  | 用于通道 B、通道 7 的高速串行化数据输出，正连接。该差分输出必须采用交流耦合，并且必须始终在接收器上使用 $100\Omega$ 差分终端进行端接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                                                                 |

| DB7 - | L9                                                              | O  | 用于通道 B、通道 7 的高速串行化数据输出，负连接。该引脚可以在不使用时保持断开，或使用 $0\Omega$ 至 $1M\Omega$ 电阻器将其连接至介于 GND (0V) 和 VD11 (1.1V) 之间的任何电压电平。                                                                                                                                                  |

| DGND  | A12、B12、<br>D9、D10、<br>F9、F10、<br>G9、G10、<br>J9、J10、<br>L12、M12 | —  | 数字电源接地。将 AGND 和 DGND 连接到电路板上的公共接地层 (GND)。                                                                                                                                                                                                                          |

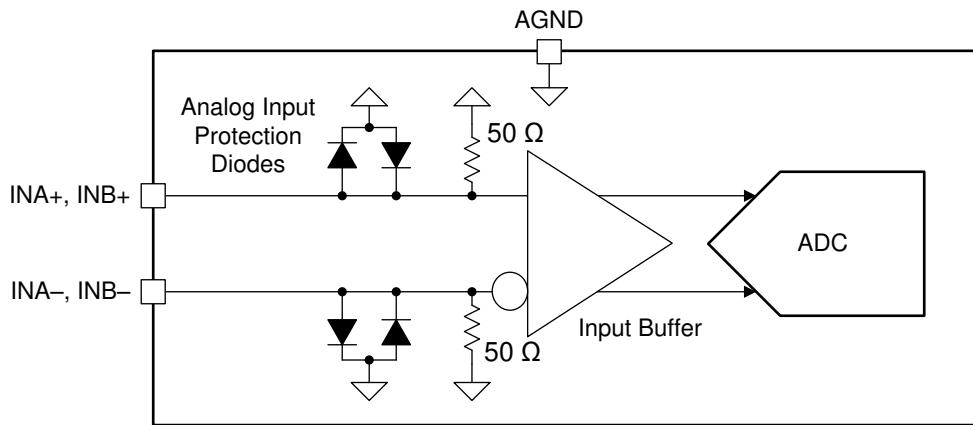

| INA+  | A4                                                              | I  | 通道 A 模拟输入正连接。为实现最佳性能，建议在单通道模式下使用 INA $\pm$ 。差分满量程输入电压由 FS_RANGE_A 寄存器确定（请参阅 <a href="#">满量程电压 (V<sub>FS</sub>) 调整</a> 部分）。该输入通过 $50\Omega$ 终端电阻器端接至接地。输入共模电压通常设置为 0V (GND)，必须遵循 <a href="#">建议运行条件</a> 表中的建议。该引脚可以在不使用时保持断开。                                       |

| INA-  | A5                                                              | I  | 通道 A 模拟输入负连接。为实现最佳性能，建议在单通道模式下使用 INA $\pm$ 。有关详细说明，请参阅 <a href="#">INA+ (pin A4)</a> 。该输入通过 $50\Omega$ 终端电阻器端接至接地。该引脚可以在不使用时保持断开。                                                                                                                                  |

| INB+  | M4                                                              | I  | 通道 B 模拟输入正连接。为实现最佳性能，建议在单通道模式下使用 INA $\pm$ 。差分满量程输入电压由 FS_RANGE_B 寄存器确定（请参阅 <a href="#">满量程电压 (V<sub>FS</sub>) 调整</a> 部分）。该输入通过 $50\Omega$ 终端电阻器端接至接地。输入共模电压通常必须设置为 0V (GND)，必须遵循 <a href="#">建议运行条件</a> 表中的建议。该引脚可以在不使用时保持断开。                                     |

| INB - | M5                                                              | I  | 通道 B 模拟输入负连接。为实现最佳性能，建议在单通道模式下使用 INA $\pm$ 。有关详细说明，请参阅 <a href="#">INB+</a> 。该输入通过 $50\Omega$ 终端电阻器端接至接地。该引脚可以在不使用时保持断开。                                                                                                                                           |

| NCOA0 | C7                                                              | I  | 用于 DDC A 的 NCO 选择控制的最低有效位 (LSB)。当使用复数输出 JMODE 时，NCOA0 和 NCOA1 从四个可选的 NCO 中选出一个 NCO 用于数字混合。其余未选择的 NCO 继续运行以保持相位一致性，可以通过更改 NCOA0 和 NCOA1 (当 CMODE = 1 时) 的值来交换。此引脚属于异步输入类型的引脚。有关更多信息，请参阅 <a href="#">NCO 快速跳频 (FFH)</a> 和 <a href="#">NCO 选择</a> 部分。不使用时将此引脚连接到 GND。 |

| NCOA1 | D7                                                              | I  | 用于 DDC A 的 NCO 选择控制的 MSB。如果不使用该引脚，则将其连接至 GND。                                                                                                                                                                                                                      |

| NCOB0 | K7                                                              | I  | 用于 DDC B 的 NCO 选择控制的最低有效位 (LSB)。当使用复数输出 JMODE 时，NCOB0 和 NCOB1 从四个可选的 NCO 中选出一个 NCO 用于数字混合。其余未选择的 NCO 继续运行以保持相位一致性，可以通过更改 NCOB0 和 NCOB1 (当 CMODE = 1 时) 的值来交换。此引脚属于异步输入类型的引脚。有关更多信息，请参阅 <a href="#">NCO 快速跳频 (FFH)</a> 和 <a href="#">NCO 选择</a> 部分。不使用时将此引脚连接到 GND。 |

| NCOB1 | J7                                                              | I  | 用于 DDC B 的 NCO 选择控制的 MSB。如果不使用该引脚，则将其连接至 GND。                                                                                                                                                                                                                      |

| ORA0  | C8                                                              | O  | 通道 A 的 OVR_T0 阈值快速超范围检测状态。当模拟输入超过 OVR_T0 中编程的阈值时，此状态指示器将变为高电平。最小脉冲持续时间由 OVR_N 设置。有关更多信息，请参阅 <a href="#">ADC 超范围检测</a> 部分。该引脚可以在不使用时保持断开。                                                                                                                           |

| ORA1  | D8                                                              | O  | 通道 A 的 OVR_T1 阈值快速超范围检测状态。当模拟输入超过 OVR_T1 中编程的阈值时，此状态指示器将变为高电平。最小脉冲持续时间由 OVR_N 设置。有关更多信息，请参阅 <a href="#">ADC 超范围检测</a> 部分。该引脚可以在不使用时保持断开。                                                                                                                           |

| ORB0  | K8                                                              | O  | 通道 B 的 OVR_T0 阈值快速超范围检测状态。当模拟输入超过 OVR_T0 中编程的阈值时，此状态指示器将变为高电平。最小脉冲持续时间由 OVR_N 设置。有关更多信息，请参阅 <a href="#">ADC 超范围检测</a> 部分。该引脚可以在不使用时保持断开。                                                                                                                           |

| ORB1  | J8                                                              | O  | 通道 B 的 OVR_T1 阈值快速超范围检测状态。当模拟输入超过 OVR_T1 中编程的阈值时，此状态指示器将变为高电平。最小脉冲持续时间由 OVR_N 设置。有关更多信息，请参阅 <a href="#">ADC 超范围检测</a> 部分。该引脚可以在不使用时保持断开。                                                                                                                           |

| PD    | K6                                                              | I  | 当设置为高电平时，该引脚会禁用所有模拟电路和串行器输出，以进行温度二极管校准或在不使用器件时降低功耗。不使用时将此引脚连接到 GND。                                                                                                                                                                                                |

**表 4-1. 引脚功能 ( 续 )**

| 引脚       |                                                         | 类型 | 说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 编号                                                      |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SCLK     | F8                                                      | I  | 串行接口时钟。此引脚用作串行接口时钟输入，可为串行编程数据输入和输出提供时钟。 <a href="#">使用串行接口</a> 部分更详细地介绍了串行接口。支持 1.1V 至 1.8V CMOS 电平。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCS      | E8                                                      | I  | 串行接口芯片选择低电平有效输入。 <a href="#">使用串行接口</a> 部分更详细地介绍了串行接口。支持 1.1V 至 1.8V CMOS 电平。该引脚到 VD11 有一个 82k $\Omega$ 上拉电阻器。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SDI      | G8                                                      | I  | 串口数据输入。 <a href="#">使用串行接口</a> 部分更详细地介绍了串行接口。支持 1.1V 至 1.8V CMOS 电平。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDO      | H8                                                      | O  | 串行接口数据输出。 <a href="#">使用串行接口</a> 部分更详细地介绍了串行接口。该引脚在器件正常运行期间处于高阻抗状态。在串行接口读取操作期间，该引脚输出 1.9V CMOS 电平。该引脚可以在不使用时保持断开。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SYNCSE   | C2                                                      | I  | 单端 JESD204C SYNC 信号。此输入为低电平有效输入，当 SYNC_SEL 设置为 0 时，用于在 8B/10B 模式中初始化 JESD204C 串行链路。64B/66B 模式不使用 SYNC 信号进行初始化，但可用于 NCO 同步。当在 8B/10B 模式中切换为低电平时，此输入会启动代码组同步（请参阅 <a href="#">代码组同步 (CGS)</a> 部分）。代码组同步后，必须将此输入切换为高电平以启动初始通道对齐序列（请参阅 <a href="#">初始通道对齐序列 (ILAS)</a> 部分）。通过将 SYNC_SEL 设置为 1 并使用 TMSTP $\pm$ 作为差分 SYNC 输入，可以改用差分 SYNC 信号。如果将差分 SYNC (TMSTP $\pm$ ) 用作 JESD204C SYNC 信号，则应将该引脚连接到 GND。                                                                                                                                                                                                                            |

| SYSREF+  | K1                                                      | I  | SYSREF 正输入用于在 JESD204C 接口上实现同步和确定性延迟。该差分输入 (SYSREF+ 至 SYSREF-) 具有内部未修整的 100 $\Omega$ 差分端接，当 SYSREF_LVPECL_EN 设置为 0 时，可以进行交流耦合。当 SYSREF_LVPECL_EN 设置为 0 时，该输入会自偏置。每个输入引脚 (SYSREF+ 和 SYSREF-) 上的终端改为 50 $\Omega$ 接地，并且当 SYSREF_LVPECL_EN 设置为 1 时，可以进行直流耦合。当 SYSREF_LVPECL_EN 设置为 1 时，该输入不会自偏置，必须从外部偏置到 <a href="#">建议运行条件</a> 表中提供的输入共模电压范围。                                                                                                                                                                                                                                                                                   |

| SYSREF-  | L1                                                      | I  | SYSREF 负输入                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TDIODE+  | K2                                                      | I  | 温度二极管正（阳极）连接。可以将外部温度传感器连接到 TDIODE+ 和 TDIODE- 来监测器件的结温。该引脚可以在不使用时保持断开。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TDIODE - | K3                                                      | I  | 温度二极管负（阴极）连接。该引脚可以在不使用时保持断开。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMSTP+   | B1                                                      | I  | 时间戳输入正连接或差分 JESD204C SYNC 正连接。当 TIMESTAMP_EN 设置为 1 时，该输入为时间戳输入，用于标记特定采样。当 SYNC_SEL 设置为 1 时，该差分输入用作 JESD204C SYNC 信号输入。此输入可同时用作时间戳和差分 SYNC 输入，从而允许使用时间戳机制来反馈 SYNC 信号。当用作 JESD204C SYNC 时，TMSTP $\pm$ 使用低电平有效的信号传输方式。有关更多使用信息，请参阅 <a href="#">时间戳</a> 部分。必须将 TMSTP_RECV_EN 设置为 1 才能使用该输入。该差分输入 (TMSTP+ 至 TMSTP-) 具有内部未修整的 100 $\Omega$ 差分终端，当 TMSTP_LVPECL_EN 设置为 0 时，可以进行交流耦合。每个输入引脚 (TMSTP+ 和 TMSTP-) 上的终端改为 50 $\Omega$ 接地，并且当 TMSTP_LVPECL_EN 设置为 1 时，可以进行直流耦合。该引脚不会自偏置，因此对于交流和直流耦合配置，必须从外部偏置。当交流和直流耦合时，共模电压必须处于 <a href="#">建议运行条件</a> 表中提供的范围内。如果 SYNCSE 用于 JESD204C SYNC 且无需使用时间戳功能，则可以将此引脚保持断开并禁用 (TMSTP_RECV_EN = 0)。 |

| TMSTP -  | C1                                                      | I  | 时间戳输入正连接或差分 JESD204C SYNC 负连接。如果 SYNCSE 用于 JESD204C SYNC 且无需使用时间戳功能，则可以将此引脚保持断开并禁用 (TMSTP_RECV_EN = 0)。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VA11     | C5、D2、<br>D3、D5、<br>E5、F5、<br>G5、H5、<br>J2、J3、J5、<br>K5 | I  | 1.1V 模拟电源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VA19     | C4、D4、<br>E2、E3、<br>E4、F4、<br>G4、H2、<br>H3、H4、<br>J4、K4 | I  | 1.9V 模拟电源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

表 4-1. 引脚功能 (续)

| 引脚   |                                                   | 类型 | 说明        |

|------|---------------------------------------------------|----|-----------|

| 名称   | 编号                                                |    |           |

| VD11 | C9、C10、<br>E9、E10、<br>G7、H7、<br>H9、H10、<br>K9、K10 | I  | 1.1V 数字电源 |

## 5 规格

### 5.1 绝对最大额定值

在自然通风条件下的工作温度范围内测得 (除非另有说明) <sup>(1)</sup>

|                       |                                        |                                                                                                       | 最小值   | 最大值                       | 单位  |

|-----------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|-------|---------------------------|-----|

| V <sub>DD</sub>       | 电源电压范围                                 | VA19 <sup>(2)</sup>                                                                                   | -0.3  | 2.35                      | V   |

|                       |                                        | VA11 <sup>(2)</sup>                                                                                   | -0.3  | 1.32                      |     |

|                       |                                        | VD11 <sup>(3)</sup>                                                                                   | -0.3  | 1.32                      |     |

|                       |                                        | VD11 和 VA11 之间的电压                                                                                     | -1.32 | 1.32                      |     |

| V <sub>GND</sub>      | AGND 和 DGND 之间的电压                      |                                                                                                       | -0.1  | 0.1                       | V   |

| V <sub>PIN</sub>      | 引脚电压范围                                 | DA[7:0]+、DA[7:0]-、DB[7:0]+、DB[7:0]-、TMSTP+、TMSTP- <sup>(3)</sup>                                      | -0.5  | VD11 + 0.5 <sup>(5)</sup> | V   |

|                       |                                        | CLK+、CLK-、SYSREF+、SYSREF- <sup>(2)</sup>                                                              | -0.5  | VA11 + 0.5 <sup>(4)</sup> |     |

|                       |                                        | BG、TDIODE+、TDIODE- <sup>(2)</sup>                                                                     | -0.5  | VA19 + 0.5 <sup>(6)</sup> |     |

|                       |                                        | INA+、INA-、INB+、INB- <sup>(2)</sup>                                                                    | -1    | 1                         |     |

|                       |                                        | CALSTAT、CALTRIG、NCOA0、NCOA1、NCOB0、NCOB1、ORA0、ORA1、ORB0、ORB1、PD、SCLK、SCS、SDI、SDO、SYNCSE <sup>(2)</sup> | -0.5  | VA19 + 0.5 <sup>(6)</sup> |     |

| I <sub>MAX(ANY)</sub> | 峰值输入电流 (除 INA+、INA-、INB+、INB- 之外的任何输入) |                                                                                                       | -25   | 25                        | mA  |

| I <sub>MAX(INx)</sub> | 峰值输入电流 (INA+、INA-、INB+、INB-)           |                                                                                                       | -50   | 50                        | mA  |

| P <sub>MAX(INx)</sub> | 峰值射频输入功率 (INA+、INA-、INB+、INB-)         | 差分为 $Z_{S-DIFF} = 100 \Omega$ ，最长 21 天 <sup>(7)</sup>                                                 |       | 26.5                      | dBm |

|                       |                                        | $Z_{S-SE} = 50 \Omega$ 的单端                                                                            |       | 16.4                      | dBm |

| I <sub>MAX(ALL)</sub> | 峰值总输入电流 (强制输入或输出的所有电流的绝对值之和, 不包括电源电流)  |                                                                                                       |       | 100                       | mA  |

| T <sub>j</sub>        | 结温                                     |                                                                                                       |       | 150                       | °C  |

| T <sub>stg</sub>      | 贮存温度                                   |                                                                                                       | -65   | 150                       | °C  |

(1) 应力超出**绝对最大额定值** 下面列出的值可能会对器件造成永久损坏。这些列出的值仅仅是应力等级，这并不表示器件在这些条件下以及在**建议运行条件** 以外的任何其他条件下能够正常运行。长时间处于绝对最大额定条件下可能会影响器件的可靠性。

- (2) 测量至 AGND。

- (3) 测量至 DGND。

- (4) 最大电压不超过 VA11 绝对最大额定值。

- (5) 最大电压不超过 VD11 绝对最大额定值。

- (6) 最大电压不超过 VA19 绝对最大额定值。

- (7) 在典型器件上，在  $F_{IN} = 1.2\text{GHz}$  的情况下连续测试 21 天。测试结束时，器件未损坏。在过驱期间，ADC 仍能正确转换输入信号，尽管它会因电压超出输入满量程而饱和。

### 5.2 ESD 等级

|                    |      |                                                          | 值     | 单位 |

|--------------------|------|----------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静电放电 | 人体放电模型 (HBM)，符合 ANSI/ESDA/JEDEC JS-001 标准 <sup>(1)</sup> | ±2000 | V  |

|                    |      | 充电器件模型 (CDM)，符合 JEDEC 规范 JESD22-C101 <sup>(2)</sup>      | ±500  |    |

(1) JEDEC 文档 JEP155 指出：500V HBM 允许在标准 ESD 控制流程下安全生产。

(2) JEDEC 文档 JEP157 指出：250V CDM 时能够在标准 ESD 控制流程下安全生产。

## 5.3 建议运行条件

在自然通风条件下的工作温度范围内测得 (除非另有说明)

|            |                |                                               | 最小值  | 标称值 | 最大值                | 单位            |

|------------|----------------|-----------------------------------------------|------|-----|--------------------|---------------|

| $V_{DD}$   | 电源电压范围         | VA19、1.9V 模拟电源 <sup>(2)</sup>                 | 1.8  | 1.9 | 2.0                | V             |

|            |                | VA11、1.1V 模拟电源 <sup>(2)</sup>                 | 1.05 | 1.1 | 1.15               |               |

|            |                | VD11、1.1V 数字电源 <sup>(3)</sup>                 | 1.05 | 1.1 | 1.15               |               |

| $V_{CMi}$  | 输入共模电压         | INA+、INA-、INB+、INB- <sup>(2)</sup>            | -50  | 0   | 100                | mV            |

|            |                | CLK+、CLK-、SYSREF+、SYSREF- <sup>(2) (4)</sup>  | 0    | 0.3 | 0.55               | V             |

|            |                | TMSTP+、TMSTP- <sup>(3) (5)</sup>              | 0    | 0.3 | 0.55               |               |

| $V_{ID}$   | 输入电压、差分峰峰值电压   | CLK+ 至 CLK-、SYSREF+ 至 SYSREF-、TMSTP+ 至 TMSTP- | 0.4  | 1.0 | 2.0                | $V_{PP-DIFF}$ |

|            |                | INA+ 至 INA-，INB+ 至 INB-                       |      |     | 0.8 <sup>(6)</sup> |               |

| $I_{C_TD}$ | 温度二极管输入电流      | TDIODE+ 至 TDIODE-                             |      | 100 |                    | $\mu A$       |

| $C_L$      | BG 最大负载电容      |                                               |      |     | 50                 | $pF$          |

| $I_O$      | BG 最大输出电流      |                                               |      |     | 100                | $\mu A$       |

| DC         | 输入时钟占空比        |                                               | 30   | 50  | 70                 | %             |

| $T_A$      | 自然通风条件下的工作温度范围 |                                               | -55  |     | 125                | $^{\circ}C$   |

| $T_J$      | 工作结温           |                                               |      |     | 150 <sup>(1)</sup> | $^{\circ}C$   |

- (1) 芯片的工作温度设计为  $T_J = 150^{\circ}C$  ,  $T_J = 125^{\circ}C$  时器件和芯片金属化降级高达 150,000 POH 连续运行。但是 , 如果在高于  $T_J = 105^{\circ}C$  结温下长时间使用 , 可能会增加封装时基故障 (FIT) 率。

- (2) 测量至 AGND。

- (3) 测量至 DGND。

- (4) TI 强烈建议对  $CLK\pm$  进行交流耦合 , 并将  $DEVCLK\_LVPECL\_EN$  设置为 0 , 以使  $CLK\pm$  自偏置到最佳输入共模电压 , 从而实现最高性能。TI 建议对  $SYSREF\pm$  进行交流耦合 , 除非需要直流耦合 , 在这种情况下 , 必须使用 LVPECL 输入模式 ( $SYSREF\_LVPECL\_EN = 1$ )。

- (5) 无论是  $TMSTP\_LVPECL\_EN=0$  时的交流耦合 , 还是  $TMSTP\_LVPECL\_EN=1$  时的直流耦合 ,  $TMSTP\pm$  都没有内部偏置 , 需要从外部对  $TMSTP\pm$  进行偏置。

- (6) 当  $INA\pm$  或  $INB\pm$  的  $V_{ID}$  超出由  $INA\pm$  的  $FS\_RANGE\_A$  或  $INB\pm$  的  $FS\_RANGE\_B$  设置的编程满量程电压 ( $V_{FS}$ ) 时 , ADC 输出代码将饱和。

## 5.4 热性能信息

| 热指标 <sup>(1)</sup>   |              | 10mmx10mm FC-BGA | 单位            |

|----------------------|--------------|------------------|---------------|

|                      |              | 144 引脚           |               |

| $R_{\theta JA}$      | 结至环境热阻       | 23.9             | $^{\circ}C/W$ |

| $R_{\theta JC(top)}$ | 结至外壳 (顶部) 热阻 | 0.8              | $^{\circ}C/W$ |

| $R_{\theta JB}$      | 结至电路板热阻      | 8.4              | $^{\circ}C/W$ |

| $\Psi_{JT}$          | 结至顶部特征参数     | 0.23             | $^{\circ}C/W$ |

| $\Psi_{JB}$          | 结至电路板特征参数    | 8.4              | $^{\circ}C/W$ |

- (1) 有关新旧热指标的更多信息 , 请参阅 [半导体和 IC 封装热指标](#) 应用报告。

## 5.5 电气特性：直流规格

典型值为  $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、默认全量程电压、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、滤波  $1\text{-V}_{PP}$  正弦波时钟、 $\text{JMODE} = 1$ ，抖动启用（采用默认设置）、 $\text{VA11}$ 、 $\text{VD11}$  和  $\text{VS11}$  噪声抑制 ON ( $\text{EN\_VA11\_NOISE\_SUPPR} = \text{EN\_VD11\_NOISE\_SUPPR} = \text{EN\_VS11\_NOISE\_SUPPR} = 1$ )，和后台校准（除非另有说明）；最小值和最大值均为标称电源电压，超出了建议的工作条件表中的工作结温范围。

| 参数                                |               | 测试条件                                                                                                                 | 最小值   | 典型值    | 最大值 | 单位               |

|-----------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------|-------|--------|-----|------------------|

| <b>直流精度</b>                       |               |                                                                                                                      |       |        |     |                  |

|                                   | 分辨率           | 无代码丢失时的分辨率                                                                                                           | 12    |        |     | 位                |

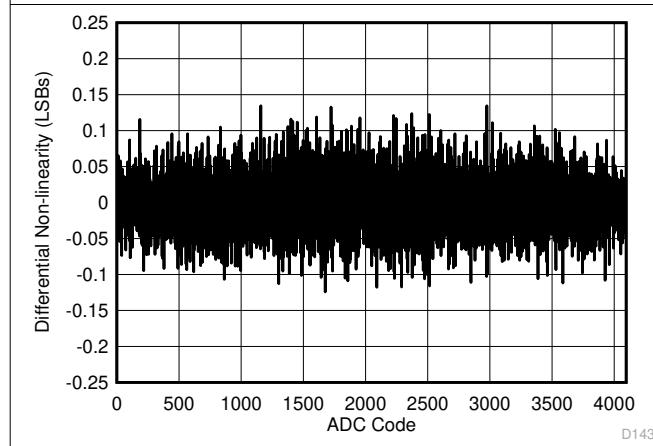

| DNL                               | 微分非线性         | 距离理想步长的最大正偏移                                                                                                         | 0.14  |        |     | LSB              |

|                                   |               | 距离理想步长的最大负偏移                                                                                                         | -0.13 |        |     |                  |

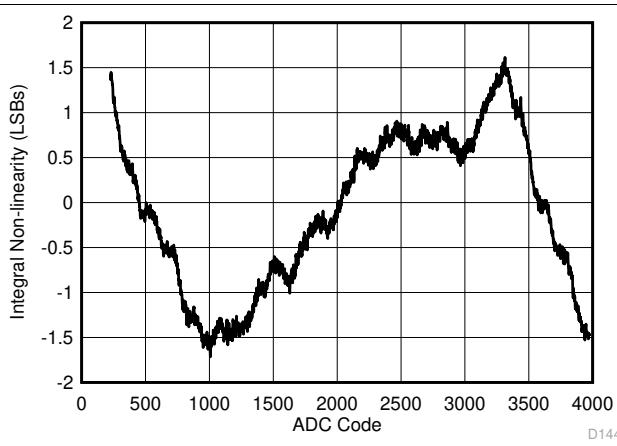

| INL                               | 积分非线性         | 距离理想传递函数的最大正偏移                                                                                                       | 2.0   |        |     | LSB              |

|                                   |               | 距离理想传递函数的最大负偏移                                                                                                       | -2.4  |        |     | LSB              |

| <b>模拟输入 (INA+、INA-、INB+、INB-)</b> |               |                                                                                                                      |       |        |     |                  |

| V <sub>OFF</sub>                  | 偏移误差          | CAL_OS = 0                                                                                                           |       | ±0.50  |     | mV               |

|                                   |               | CAL_OS = 1                                                                                                           |       | ±0.15  |     | mV               |

| V <sub>OFF_ADJ</sub>              | 输入失调电压调节范围    | 可用的偏移校正范围（请参见 OS_CAL 或 OADJ_X_INx）                                                                                   |       | ±50    |     | mV               |

| V <sub>OFF_DRIFT</sub>            | 偏移漂移          | 仅限标称温度下的前台校准                                                                                                         |       | 18     |     | μV/°C            |

|                                   |               | 每个温度下的前台校准                                                                                                           |       | -5.5   |     |                  |

|                                   |               | 每个温度下的前台校准和 FGOS 校准                                                                                                  |       | 0      |     |                  |

| V <sub>FS</sub>                   | 模拟差分输入满量程     | 默认满量程电压 (FS_RANGE_A = FS_RANGE_B = 0xA000)                                                                           | 750   | 825    | 910 | mV <sub>PP</sub> |

|                                   |               | 最大满量程电压 (FS_RANGE_A = FS_RANGE_B = 0xFFFF)                                                                           | 975   | 1060   |     |                  |

|                                   |               | 最小满量程电压 (FS_RANGE_A = FS_RANGE_B = 0x2000)                                                                           | 500   | 560    |     |                  |

| V <sub>FS_DRIFT</sub>             | 模拟差分输入满量程范围漂移 | 默认 FS_RANGE_A 和 FS_RANGE_B 设置，每个温度下的前台校准，由 $50\Omega$ 源驱动的输入，包括 $R_{IN}$ 漂移的影响                                       |       | 0.033  |     | %/°C             |

| V <sub>FS_MATCH</sub>             | 模拟差分输入满量程范围匹配 | INA $\pm$ 和 INB $\pm$ 之间的匹配，默认设置，双通道模式                                                                               |       | 0.625% |     |                  |

| R <sub>IN</sub>                   | AGND 单端输入电阻   | 每个输入引脚端接至 AGND，在 $T_A = 25^\circ\text{C}$ 时测量                                                                        | 48    | 50     | 52  | Ω                |

| R <sub>IN_TEMP</sub>              | 输入终端线性温度系数    |                                                                                                                      |       | 14.7   |     | mΩ/°C            |

| C <sub>IN</sub>                   | 单端输入电容        | 在直流时测量单通道模式                                                                                                          |       | 0.4    |     | pF               |

|                                   |               | 在直流时测量双通道模式                                                                                                          |       | 0.4    |     |                  |

| <b>温度二极管特性 (TDIODE+、TDIODE-)</b>  |               |                                                                                                                      |       |        |     |                  |

| ΔV <sub>BE</sub>                  | 温度二极管电压斜率     | 100μA 的强制正向电流。失调电压（在 $0^\circ\text{C}$ 时约为 0.792V）随工艺不同而变化，必须针对每个器件进行测量。必须在器件未上电或 PD 引脚置位的情况下完成失调电压测量，以更大限度地减少器件自发热。 |       | -1.65  |     | mV/°C            |

## 5.5 电气特性：直流规格（续）

典型值为  $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、默认全量程电压、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、滤波  $1\text{-V}_{PP}$  正弦波时钟、 $JMODE = 1$ ，抖动启用（采用默认设置）、 $\text{VA11}$ 、 $\text{VD11}$  和  $\text{VS11}$  噪声抑制 ON ( $\text{EN\_VA11\_NOISE\_SUPPR} = \text{EN\_VD11\_NOISE\_SUPPR} = \text{EN\_VS11\_NOISE\_SUPPR} = 1$ )，和后台校准（除非另有说明）；最小值和最大值均为标称电源电压，超出了建议的工作条件表中的工作结温范围。

| 参数                                                                                                      | 测试条件       | 最小值                                                                                       | 典型值  | 最大值      | 单位                           |

|---------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------|------|----------|------------------------------|

| <b>带隙电压输出 (BG)</b>                                                                                      |            |                                                                                           |      |          |                              |

| $V_{BG}$                                                                                                | 基准输出电压     | $I_L \leq 100\mu\text{A}$                                                                 | 1.1  |          | V                            |

| $V_{BG\_DRIFT}$                                                                                         | 基准输出温度漂移   | $I_L \leq 100\mu\text{A}$                                                                 | -64  |          | $\mu\text{V}/^\circ\text{C}$ |

| <b>时钟输入 (CLK+、CLK-、SYSREF+、SYSREF-、TMSTP+、TMSTP-)</b>                                                   |            |                                                                                           |      |          |                              |

| $Z_T$                                                                                                   | 内部端接       | DEVCLK_LVPECL_EN = 0、<br>SYSREF_LVPECL_EN = 0 且 TMSTP_LVPECL_EN = 0 时的差分终端                | 100  |          | $\Omega$                     |

|                                                                                                         |            | 在 DEVCLK_LVPECL_EN = 0、<br>SYSREF_LVPECL_EN = 0、TMSTP_LVPECL_EN = 0 时单端终端至 GND (每引脚)      | 50   |          |                              |

| $V_{CM}$                                                                                                | 输入共模电压自偏置  | 交流耦合时 $CLK\pm$ 的自偏置共模电压<br>( DEVCLK_LVPECL_EN 必须设置为 0)                                    | 0.3  |          | V                            |

|                                                                                                         |            | 在交流耦合时 (SYSREF_LVPECL_EN 必须设置为 0) 且接收器启用 (SYSREF_RECV_EN = 1) 时，<br>SYSREF $\pm$ 的自偏置共模电压 | 0.28 |          |                              |

|                                                                                                         |            | 在交流耦合 (SYSREF_LVPECL_EN 必须设置为 0) 且接收器被禁用 (SYSREF_RECV_EN = 0) 时，<br>SYSREF $\pm$ 的自偏置共模电压 | 0.28 |          |                              |

| $C_{L\_DIFF}$                                                                                           | 差分输入电容     | 正负差分输入引脚之间                                                                                | 0.04 |          | pF                           |

| $C_{L\_SE}$                                                                                             | 单端输入电容     | 每个输入端接地                                                                                   | 0.5  |          | pF                           |

| <b>串行器/解串器输出 (DA[7:0]+、DA[7:0]-、DB[7:0]+、DB[7:0]-)</b>                                                  |            |                                                                                           |      |          |                              |

| $V_{OD}$                                                                                                | 差分输出电压，峰峰值 | 100- $\Omega$ 负载                                                                          | 540  | 600      | 650 mV <sub>PP-DIFF</sub>    |

| $V_{CM}$                                                                                                | 输出共模电压     | 交流耦合                                                                                      |      | VD11 / 2 | V                            |

| $Z_{DIFF}$                                                                                              | 差分输出阻抗     |                                                                                           |      | 100      | $\Omega$                     |

| <b>CMOS 接口 : SCLK、SDI、SDO、SCS、PD、NCOA0、NCOA1、NCOB0、NCOB1、CALSTAT、CALTRIG、ORA0、ORA1、ORB0、ORB1、SYNCSE</b> |            |                                                                                           |      |          |                              |

| $V_{IH}$                                                                                                | 高电平输入电压    | 所需输入电压                                                                                    | 0.7  |          | V                            |

| $V_{IL}$                                                                                                | 低电平输入电压    | 所需输入电压                                                                                    |      | 0.45     | V                            |

| $I_{IH}$                                                                                                | 高电平输入电流    |                                                                                           |      | 40       | $\mu\text{A}$                |

| $I_{IL}$                                                                                                | 低电平输入电流    |                                                                                           | -40  |          | $\mu\text{A}$                |

| $C_I$                                                                                                   | 输入电容       |                                                                                           | 3.4  |          | pF                           |

| $V_{OH}$                                                                                                | 高电平输出电压    | $I_{LOAD} = -400\mu\text{A}$                                                              | 1.65 |          | V                            |

| $V_{OL}$                                                                                                | 低电平输出电压    | $I_{LOAD} = 400\mu\text{A}$                                                               |      | 150      | mV                           |

## 5.6 电气特性：功耗

典型值为  $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、默认全量程电压、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、滤波 1-V<sub>PP</sub> 正弦波时钟、JMODE = 1，抖动启用（采用默认设置）、VA11、VD11 和 VS11 噪声抑制 ON ([EN\\_VA11\\_NOISE\\_SUPPR = EN\\_VD11\\_NOISE\\_SUPPR = EN\\_VS11\\_NOISE\\_SUPPR = 1](#))，和后台校准（除非另有说明）；最小值和最大值均为标称电源电压，超出了[建议的工作条件](#)表中的工作结温范围。

| 参数         |             | 测试条件                                                      | 最小值 | 典型值  | 最大值  | 单位 |

|------------|-------------|-----------------------------------------------------------|-----|------|------|----|

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 1 : JMODE 1 ( 单通道模式、16 个通道、8B/10B 编码、绕过 DDC ) 、前台校准  |     | 934  |      | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 845  |      | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 1170 |      | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 4.01 |      | W  |

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 2 : JMODE 30 ( 单通道模式、8 个通道、64B/66B 编码、绕过 DDC ) 、前台校准 |     | 935  | 1050 | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 850  | 1000 | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 1195 | 1650 | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 4.0  | 4.98 | W  |

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 3 : JMODE 1 ( 单通道模式、16 个通道、8B/10B 编码、绕过 DDC ) 、后台校准  |     | 1242 |      | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 1030 |      | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 1265 |      | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 4.90 |      | W  |

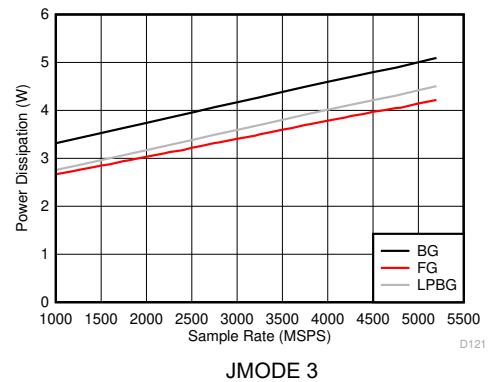

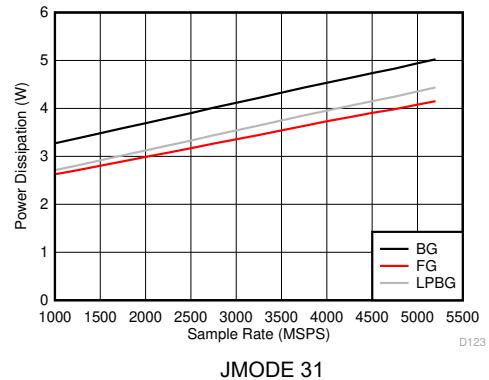

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 4 : JMODE 3 ( 双通道模式、16 个通道、8B/10B 编码、绕过 DDC ) 、后台校准  |     | 1320 |      | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 1030 |      | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 1250 |      | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 5.03 |      | W  |

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 5 : JMODE 22 ( 单通道模式、8 个通道、8B/10B 编码、4x 抽取 ) 、前台校准   |     | 936  |      | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 845  |      | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 2350 |      | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 5.3  |      | W  |

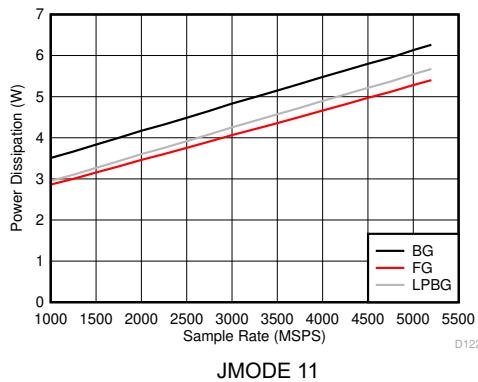

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 6 : JMODE 11 ( 双通道模式、8 个通道、8B/10B 编码、4x 抽取 ) 、前台校准   |     | 1014 |      | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 845  |      | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 2260 |      | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 5.34 |      | W  |

| $I_{VA19}$ | 1.9V 模拟电源电流 | 电源模式 7 : PD 引脚保持高电平，时钟禁用                                  |     | 44   |      | mA |

| $I_{VA11}$ | 1.1V 模拟电源电流 |                                                           |     | 30   |      | mA |

| $I_{VD11}$ | 1.1V 数字电源电流 |                                                           |     | 56   |      | mA |

| $P_{DIS}$  | 功率耗散        |                                                           |     | 0.18 |      | W  |

## 5.7 电气特性：交流规格 ( 双通道模式 )

典型值为  $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、默认全量程电压、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、滤波 1-V<sub>PP</sub> 正弦波时钟、JMODE = 3，抖动启用 ( 采用默认设置 ) 、VA11、VD11 和 VS11 噪声抑制 ON ( $\text{EN\_VA11\_NOISE\_SUPPR} = \text{EN\_VD11\_NOISE\_SUPPR} = \text{EN\_VS11\_NOISE\_SUPPR} = 1$ )，和后台校准 ( 除非另有说明 ) ；最小值和最大值均为标称电源电压，超出了建议的工作条件表中的工作结温范围。

| 参数    |                                                    | 测试条件                                                                | 最小值                                                    | 典型值        | 最大值  | 单位          |

|-------|----------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|------------|------|-------------|

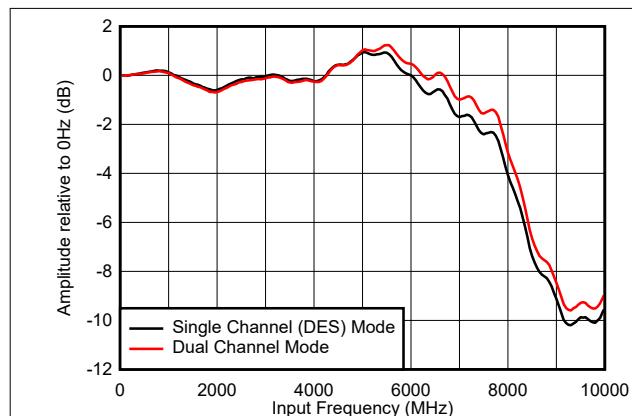

| FPBW  | 全功率输入带宽 ( -3 dB) <sup>(1)</sup>                    | 前台校准                                                                | 8.1                                                    |            |      | GHz         |

|       |                                                    | 后台校准                                                                | 8.1                                                    |            |      |             |

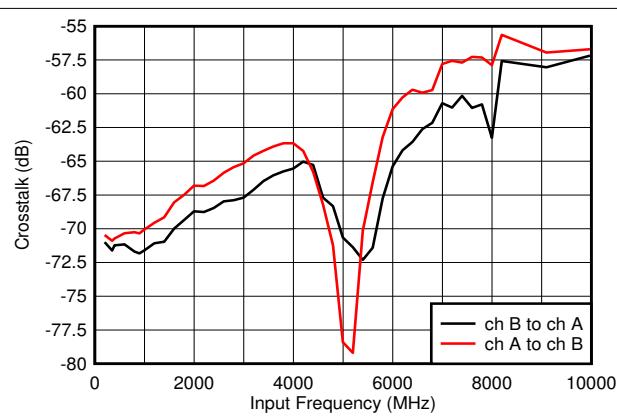

| XTALK | 通道间串扰                                              | 干扰源 = 1 GHz, -1 dBFS                                                |                                                        | -77        |      | dB          |

|       |                                                    | 干扰源 = 3 GHz, -1 dBFS                                                |                                                        | -71        |      |             |

|       |                                                    | 干扰源 = 6 GHz, -1 dBFS                                                |                                                        | -63        |      |             |

| CER   | 误码率                                                | 最大 CER，不包括 JESD204C 接口 BER                                          |                                                        | $10^{-18}$ |      | 错误/样本       |

| 噪声 DC | 直流输入噪声标准偏差                                         | 无输入、前台校准，不包括 DC 偏移，包括固定交错杂散 ( $f_S/2$ 杂散 )                          |                                                        | 2.3        |      | LSB         |

| NSD   | 噪声频谱密度，不包括固定交错杂散 ( $f_S/2$ 杂散 )                    | 最大满量程电压 ( $V_{FS} = 1.0\text{V}_{PP}$ ) , $A_{IN} = -20\text{dBFS}$ |                                                        | -152.0     |      | dBFS/<br>Hz |

|       |                                                    | 默认满量程电压 ( $V_{FS} = 0.8\text{V}_{PP}$ ) , $A_{IN} = -20\text{dBFS}$ |                                                        | -150.4     |      |             |

| NF    | 噪声系数， $Z_S = 100\Omega$                            | 最大满量程电压 ( $V_{FS} = 1.0\text{V}_{PP}$ ) , $A_{IN} = -20\text{dBFS}$ |                                                        | 23.0       |      | dB          |

|       |                                                    | 默认满量程电压 ( $V_{FS} = 0.8\text{V}_{PP}$ ) , $A_{IN} = -20\text{dBFS}$ |                                                        | 22.6       |      |             |

| SNR   | 信噪比，不包括 DC、HD2 至 HD9、 $f_S/2$ 、 $f_S/2 - f_{IN}$ 、 | $f_{IN} = 347\text{MHz}$                                            | $A_{IN} = -1\text{dBFS}$                               | 55.6       |      | dBFS        |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$                               | 55.9       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -12\text{dBFS}$                              | 56.3       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$ , $V_{FS} = 1.0\text{V}_{PP}$ | 57.2       |      |             |

|       |                                                    | $f_{IN} = 997\text{MHz}$                                            | $A_{IN} = -1\text{dBFS}$                               | 55.4       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$                               | 55.8       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -12\text{dBFS}$                              | 56.3       |      |             |

|       |                                                    | $f_{IN} = 2397\text{MHz}$                                           | $A_{IN} = -1\text{dBFS}$ , $T_A = -55^\circ\text{C}$   | 48         |      |             |

|       |                                                    |                                                                     | $A_{IN} = -1\text{dBFS}$ , $T_A = 25^\circ\text{C}$    | 52         | 54.7 |             |

|       |                                                    |                                                                     | $A_{IN} = -1\text{dBFS}$ , $T_A = 125^\circ\text{C}$   | 51         |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$                               | 55.2       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -12\text{dBFS}$                              | 56.2       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$ , $V_{FS} = 1.0\text{V}_{PP}$ | 56.3       |      |             |

|       |                                                    | $f_{IN} = 4197\text{MHz}$                                           | $A_{IN} = -1\text{dBFS}$                               | 53.0       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$                               | 54.0       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -12\text{dBFS}$                              | 56.0       |      |             |

|       |                                                    | $f_{IN} = 5997\text{MHz}$                                           | $A_{IN} = -1\text{dBFS}$                               | 51.4       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$                               | 52.6       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -12\text{dBFS}$                              | 55.6       |      |             |

|       |                                                    | $f_{IN} = 7997\text{MHz}$                                           | $A_{IN} = -1\text{dBFS}$                               | 49.6       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -3\text{dBFS}$                               | 51.1       |      |             |

|       |                                                    |                                                                     | $A_{IN} = -12\text{dBFS}$                              | 55.2       |      |             |

## 5.7 电气特性：交流规格（双通道模式）（续）

典型值为  $T_J = 50^\circ\text{C}$ 、 $VA19 = 1.9\text{V}$ 、 $VA11 = 1.1\text{V}$ 、 $VD11 = 1.1\text{V}$ 、默认全量程电压、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、滤波  $1\text{-}V_{PP}$  正弦波时钟、JMODE = 3，抖动启用（采用默认设置）、VA11、VD11 和 VS11 噪声抑制 ON ( $EN_{VA11\_NOISE\_SUPPR} = EN_{VD11\_NOISE\_SUPPR} = EN_{VS11\_NOISE\_SUPPR} = 1$ )，和后台校准（除非另有说明）；最小值和最大值均为标称电源电压，超出了建议的工作条件表中的工作结温范围。

| 参数    |                               | 测试条件                      | 最小值                                                     | 典型值  | 最大值  | 单位   |

|-------|-------------------------------|---------------------------|---------------------------------------------------------|------|------|------|

| SINAD | 信噪比和失真比，不包括 DC 和 $f_S/2$ 固定杂散 | $f_{IN} = 347\text{MHz}$  | $A_{IN} = -1\text{dBFS}$                                | 54.5 |      | dBFS |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 55.3 |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 56.1 |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$ , $V_{FS} = 1.0\text{ V}_{PP}$ | 56.3 |      |      |

|       |                               | $f_{IN} = 997\text{MHz}$  | $A_{IN} = -1\text{dBFS}$                                | 54.4 |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 55.3 |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 56.1 |      |      |

|       |                               | $f_{IN} = 2397\text{MHz}$ | $A_{IN} = -1\text{dBFS}$ , $T_A = -55^\circ\text{C}$    | 46   |      |      |

|       |                               |                           | $A_{IN} = -1\text{dBFS}$ , $T_A = 25^\circ\text{C}$     | 49   | 53.9 |      |

|       |                               |                           | $A_{IN} = -1\text{dBFS}$ , $T_A = 125^\circ\text{C}$    | 48   |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 54.7 |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 56.1 |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$ , $V_{FS} = 1.0\text{ V}_{PP}$ | 55.7 |      |      |

|       |                               | $f_{IN} = 4197\text{MHz}$ | $A_{IN} = -1\text{dBFS}$                                | 51.5 |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 53.2 |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 55.8 |      |      |

|       |                               | $f_{IN} = 5997\text{MHz}$ | $A_{IN} = -1\text{dBFS}$                                | 48.8 |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 51.5 |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 55.5 |      |      |

|       |                               | $f_{IN} = 7997\text{MHz}$ | $A_{IN} = -1\text{dBFS}$                                | 46.2 |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 49.2 |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 55.0 |      |      |

| ENOB  | 有效位数，不包括 DC 和 $f_S/2$ 固定杂散    | $f_{IN} = 347\text{MHz}$  | $A_{IN} = -1\text{dBFS}$                                | 8.8  |      | 位    |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 8.9  |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 9.0  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$ , $V_{FS} = 1.0\text{ V}_{PP}$ | 9.1  |      |      |

|       |                               | $f_{IN} = 997\text{MHz}$  | $A_{IN} = -1\text{dBFS}$                                | 8.7  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 8.9  |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 9.0  |      |      |

|       |                               | $f_{IN} = 2397\text{MHz}$ | $A_{IN} = -1\text{dBFS}$ , $T_A = -55^\circ\text{C}$    | 7.35 |      |      |

|       |                               |                           | $A_{IN} = -1\text{dBFS}$ , $T_A = 25^\circ\text{C}$     | 7.85 | 8.7  |      |

|       |                               |                           | $A_{IN} = -1\text{dBFS}$ , $T_A = 125^\circ\text{C}$    | 7.7  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 8.8  |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 9.0  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$ , $V_{FS} = 1.0\text{ V}_{PP}$ | 9.0  |      |      |

|       |                               | $f_{IN} = 4197\text{MHz}$ | $A_{IN} = -1\text{dBFS}$                                | 8.3  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 8.5  |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 9.0  |      |      |

|       |                               | $f_{IN} = 5997\text{MHz}$ | $A_{IN} = -1\text{dBFS}$                                | 7.8  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 8.3  |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 8.9  |      |      |

|       |                               | $f_{IN} = 7997\text{MHz}$ | $A_{IN} = -1\text{dBFS}$                                | 7.4  |      |      |

|       |                               |                           | $A_{IN} = -3\text{dBFS}$                                | 7.9  |      |      |

|       |                               |                           | $A_{IN} = -12\text{dBFS}$                               | 8.8  |      |      |

## 5.7 电气特性：交流规格（双通道模式）（续）

典型值为  $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、默认全量程电压、 $f_{\text{IN}} = 347\text{MHz}$ 、 $A_{\text{IN}} = -1\text{dBFS}$ 、 $f_{\text{CLK}} = 5.12\text{GHz}$ 、滤波 1- $V_{\text{PP}}$  正弦波时钟、JMODE = 3，抖动启用（采用默认设置）、VA11、VD11 和 VS11 噪声抑制 ON ( $\text{EN\_VA11\_NOISE\_SUPPR} = \text{EN\_VD11\_NOISE\_SUPPR} = \text{EN\_VS11\_NOISE\_SUPPR} = 1$ )，和后台校准（除非另有说明）；最小值和最大值均为标称电源电压，超出了建议的工作条件表中的工作结温范围。

| 参数   |                               | 测试条件                             | 最小值                                                                       | 典型值 | 最大值 | 单位   |

|------|-------------------------------|----------------------------------|---------------------------------------------------------------------------|-----|-----|------|

| SFDR | 无杂散动态范围，不包括 DC 和 $f_s/2$ 固定杂散 | $f_{\text{IN}} = 347\text{MHz}$  | $A_{\text{IN}} = -1\text{dBFS}$                                           | 65  |     | dBFS |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}$                                           | 67  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -12\text{dBFS}$                                          | 73  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}, V_{\text{FS}} = 1.0\text{ V}_{\text{PP}}$ | 67  |     |      |

|      |                               | $f_{\text{IN}} = 997\text{MHz}$  | $A_{\text{IN}} = -1\text{dBFS}$                                           | 64  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}$                                           | 69  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -12\text{dBFS}$                                          | 74  |     |      |

|      |                               | $f_{\text{IN}} = 2397\text{MHz}$ | $A_{\text{IN}} = -1\text{dBFS}$                                           | 52  | 65  |      |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}$                                           | 67  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -12\text{dBFS}$                                          | 73  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}, V_{\text{FS}} = 1.0\text{ V}_{\text{PP}}$ | 68  |     |      |

|      |                               | $f_{\text{IN}} = 4197\text{MHz}$ | $A_{\text{IN}} = -1\text{dBFS}$                                           | 59  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}$                                           | 64  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -12\text{dBFS}$                                          | 73  |     |      |

|      |                               | $f_{\text{IN}} = 5997\text{MHz}$ | $A_{\text{IN}} = -1\text{dBFS}$                                           | 54  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -3\text{dBFS}$                                           | 61  |     |      |

|      |                               |                                  | $A_{\text{IN}} = -12\text{dBFS}$                                          | 75  |     |      |

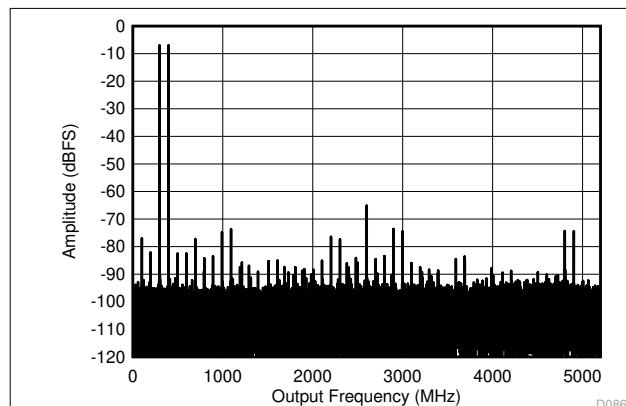

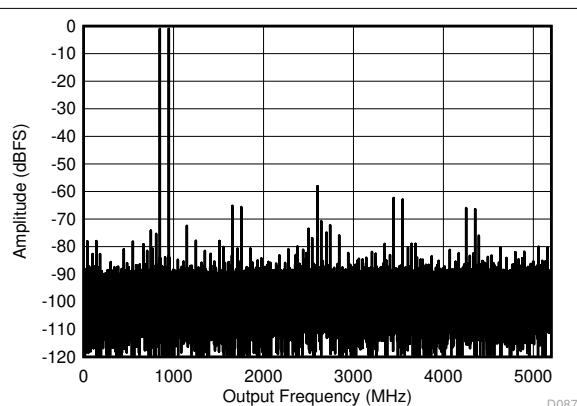

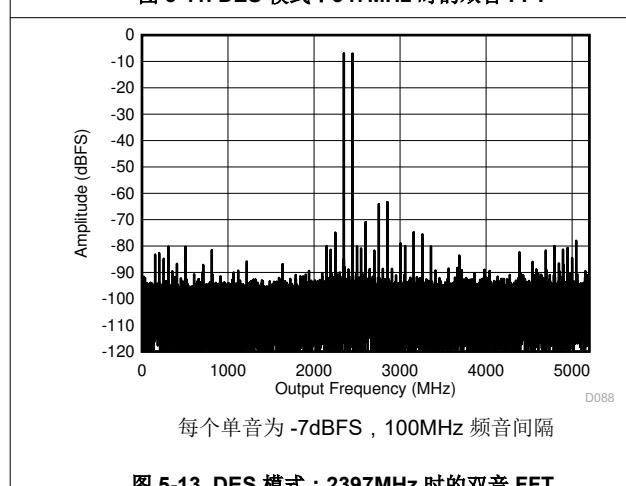

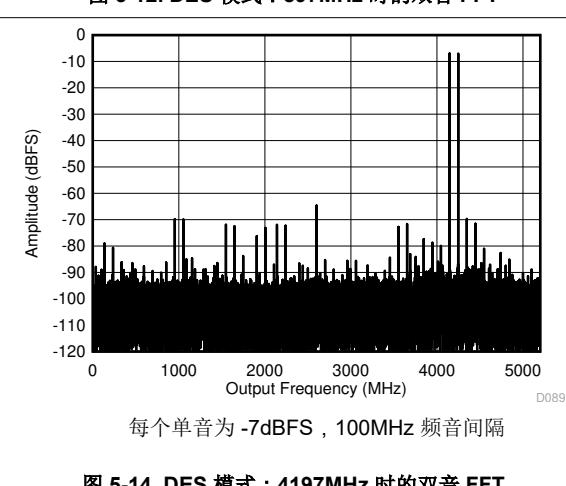

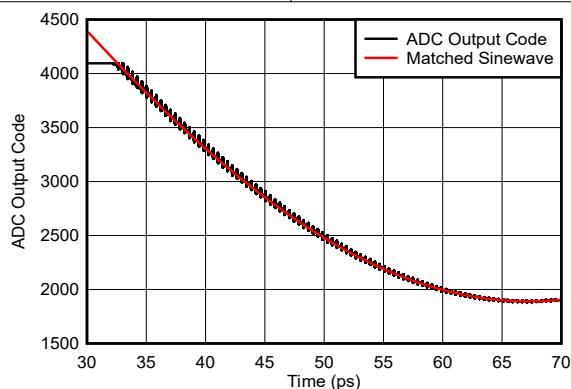

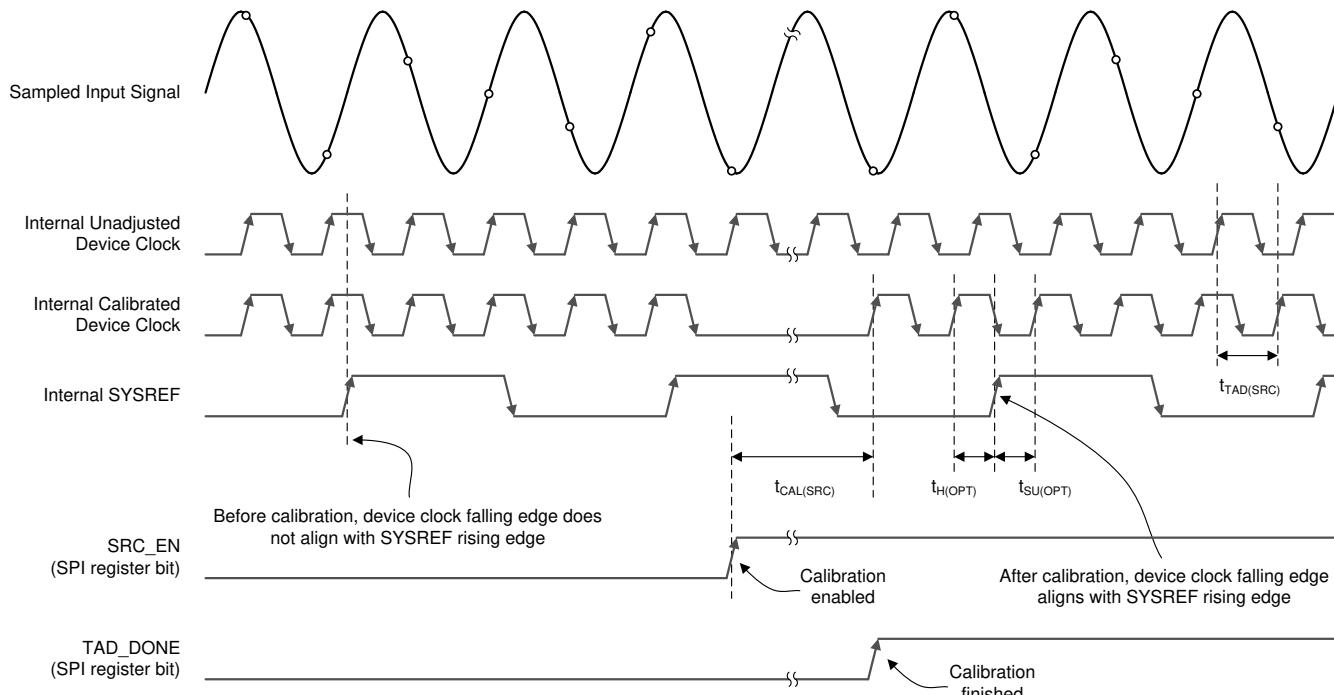

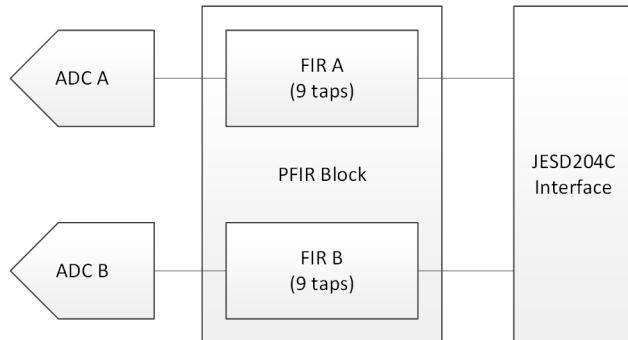

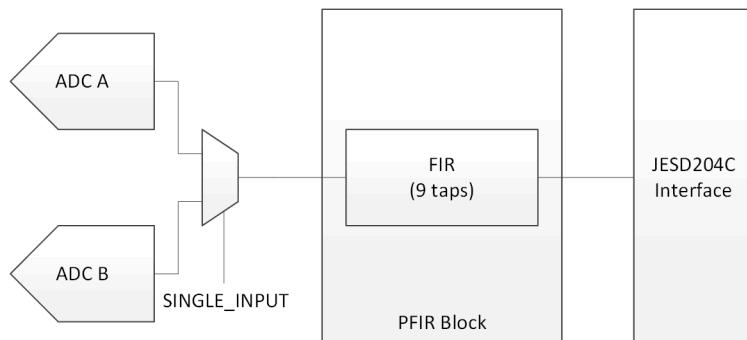

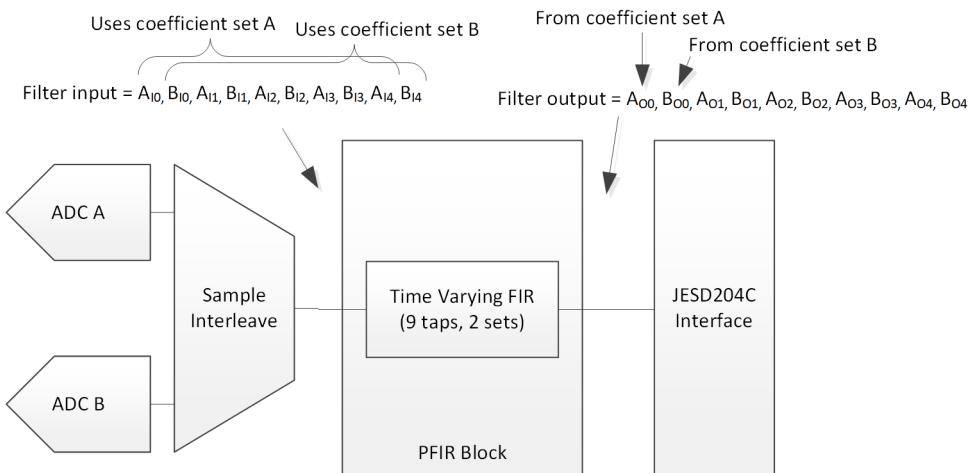

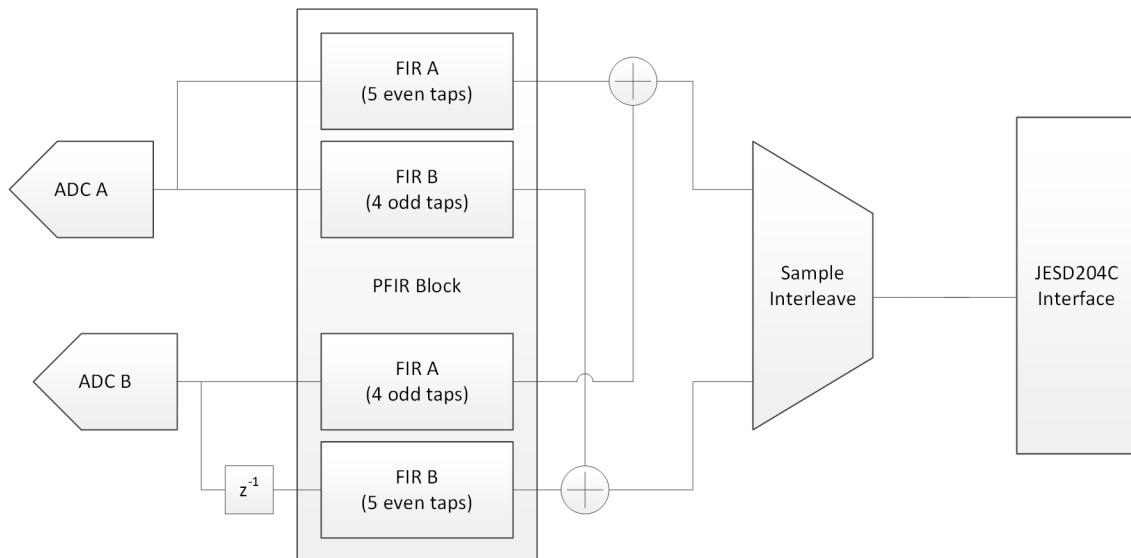

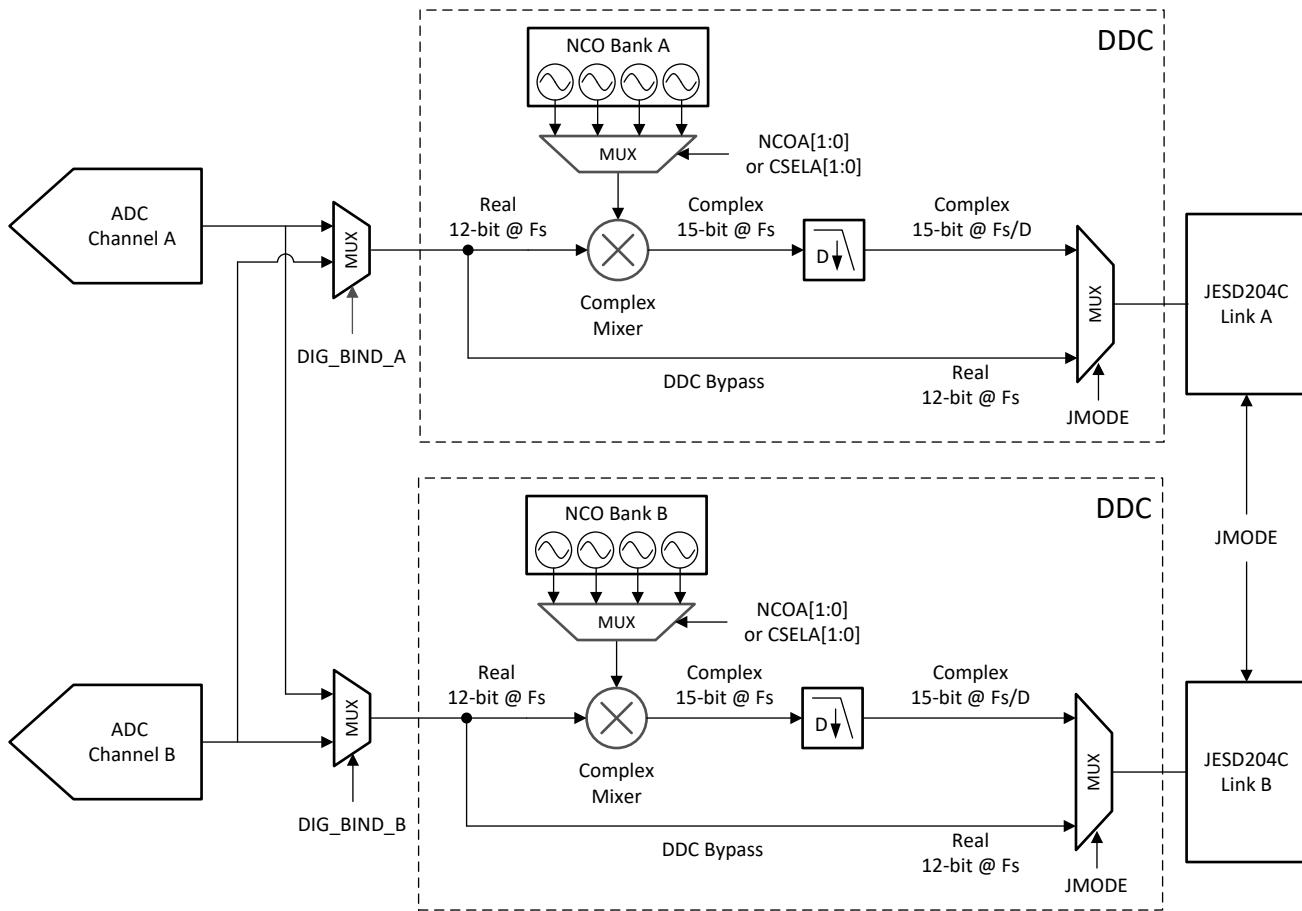

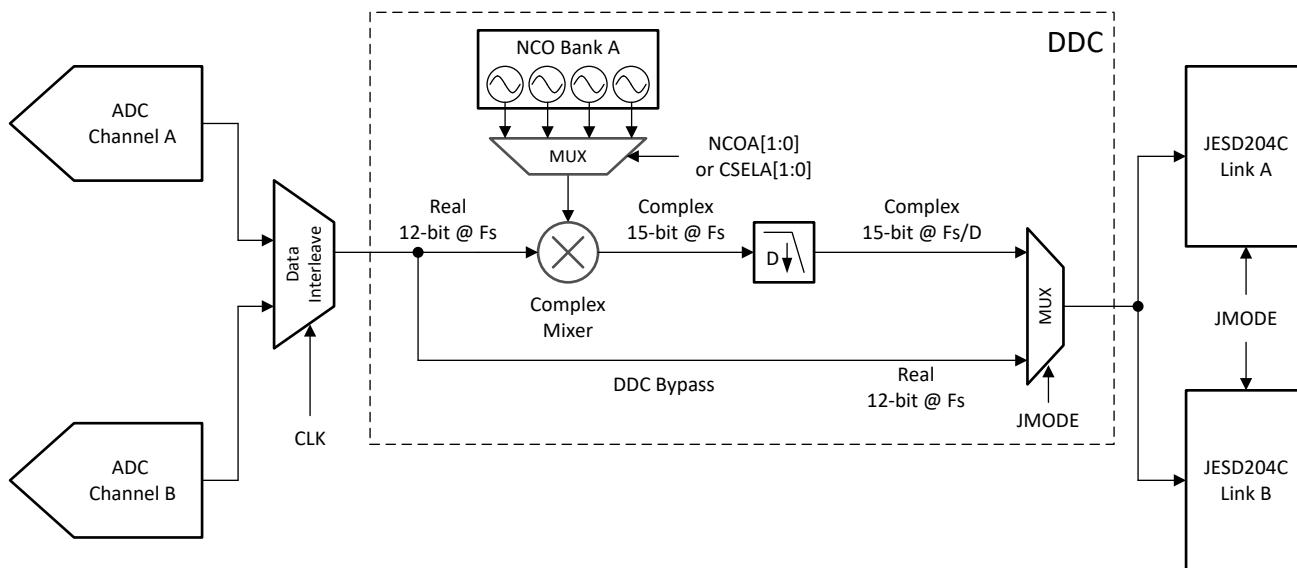

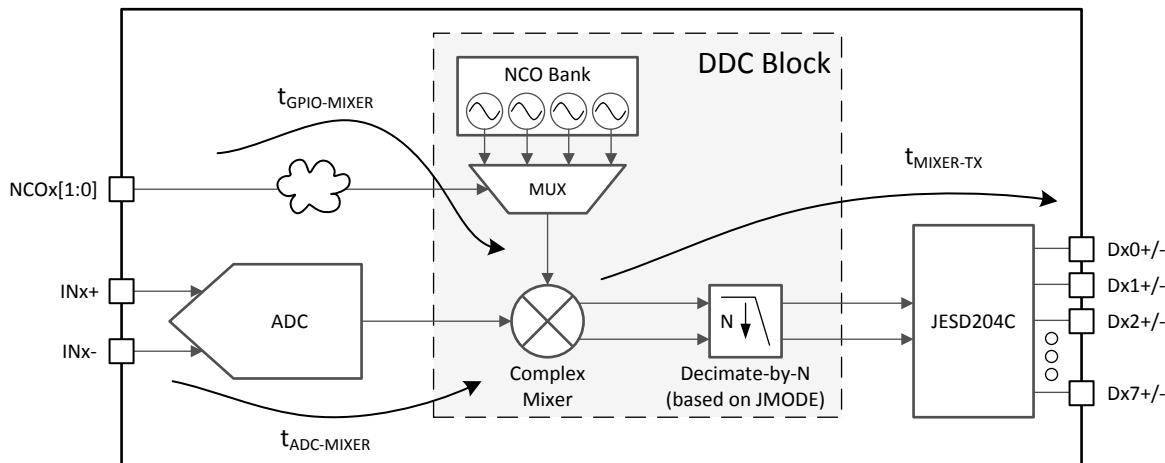

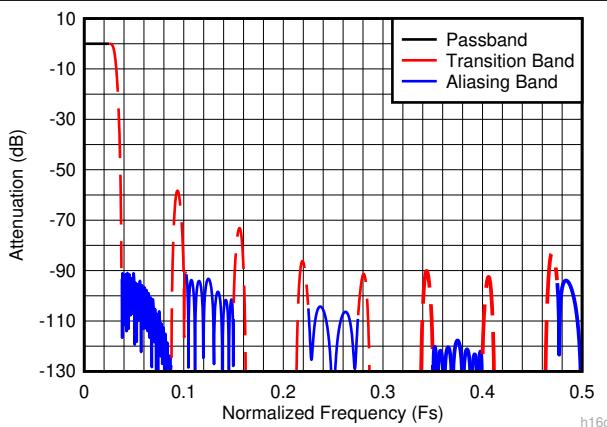

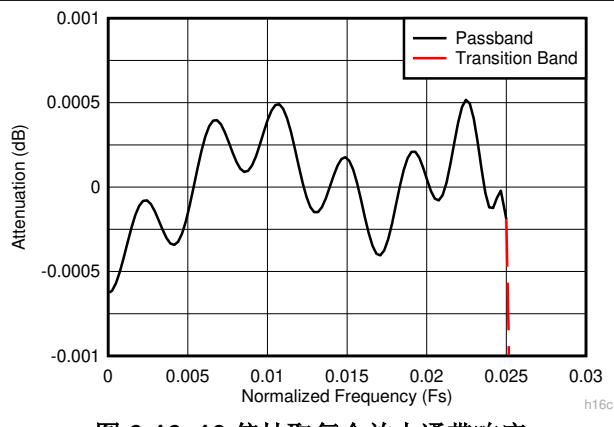

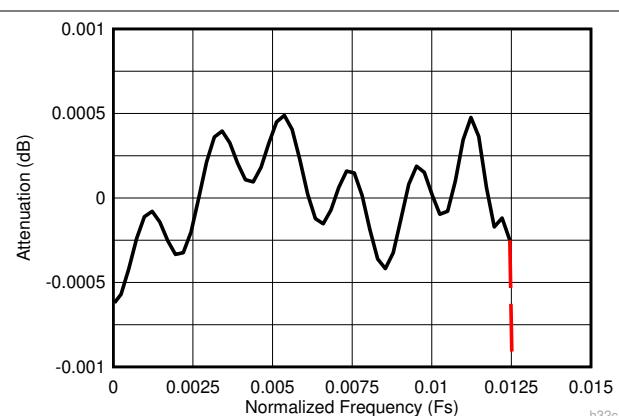

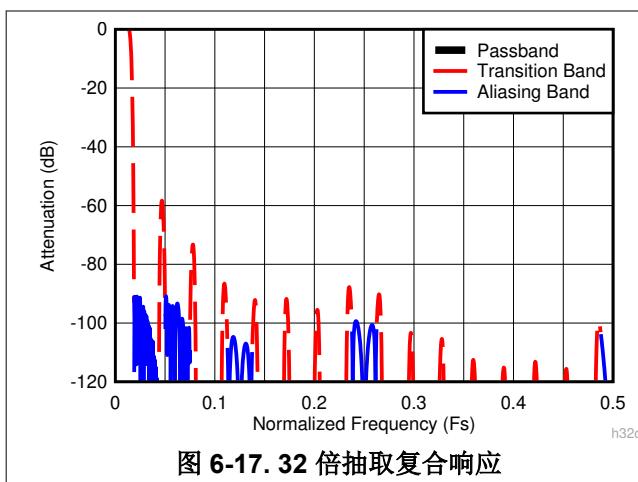

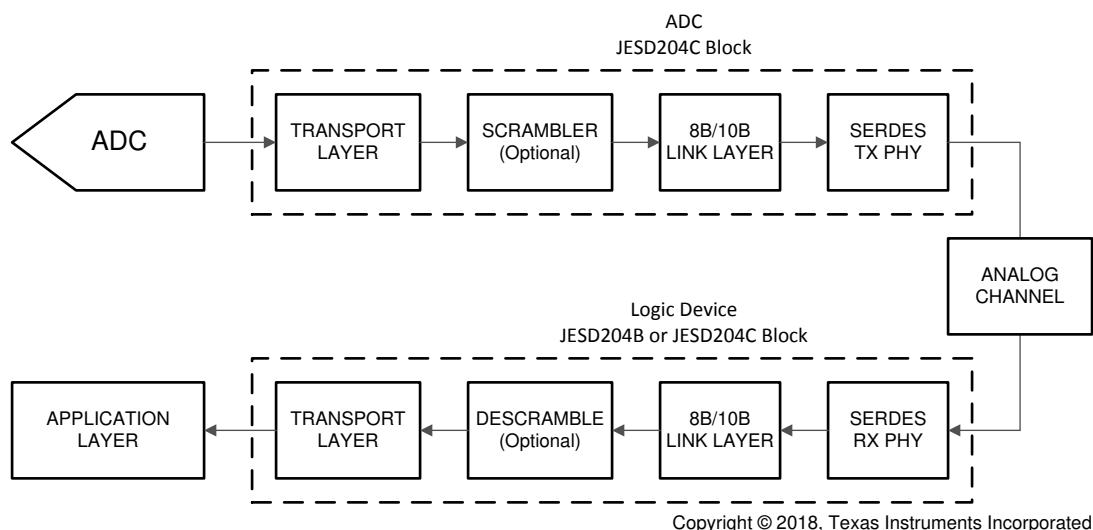

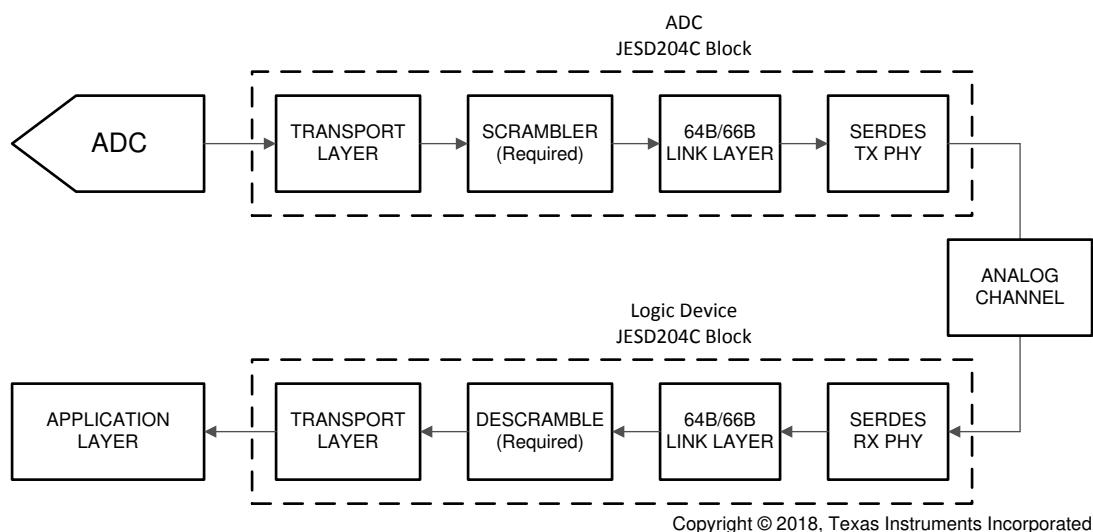

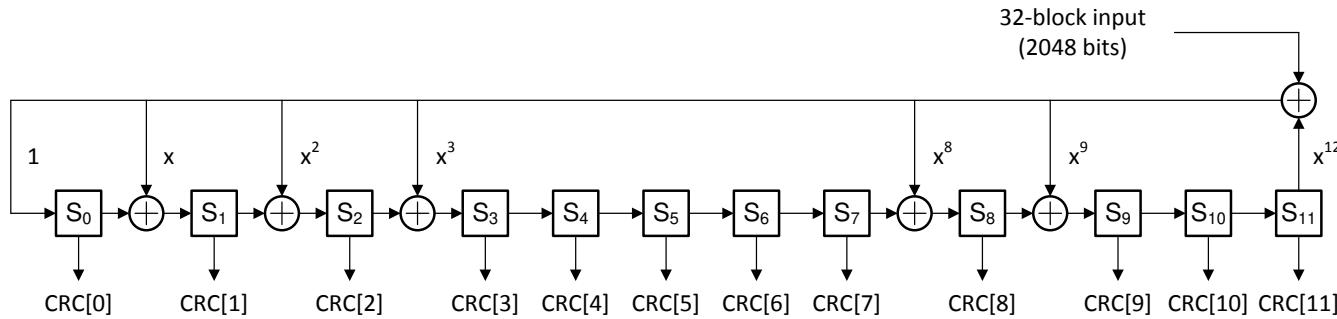

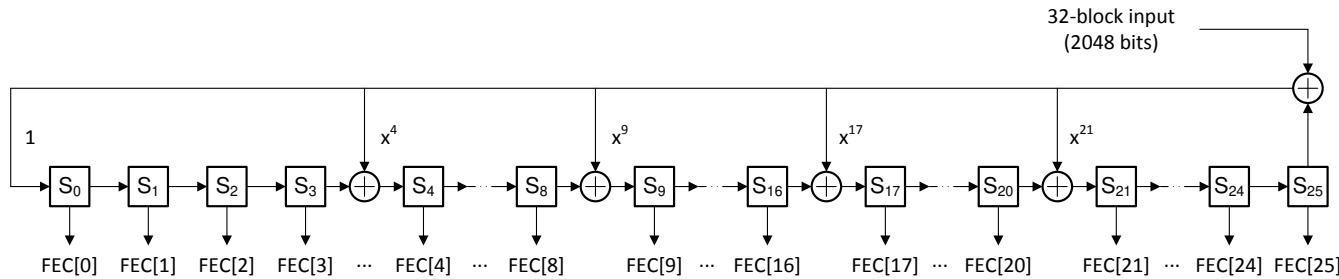

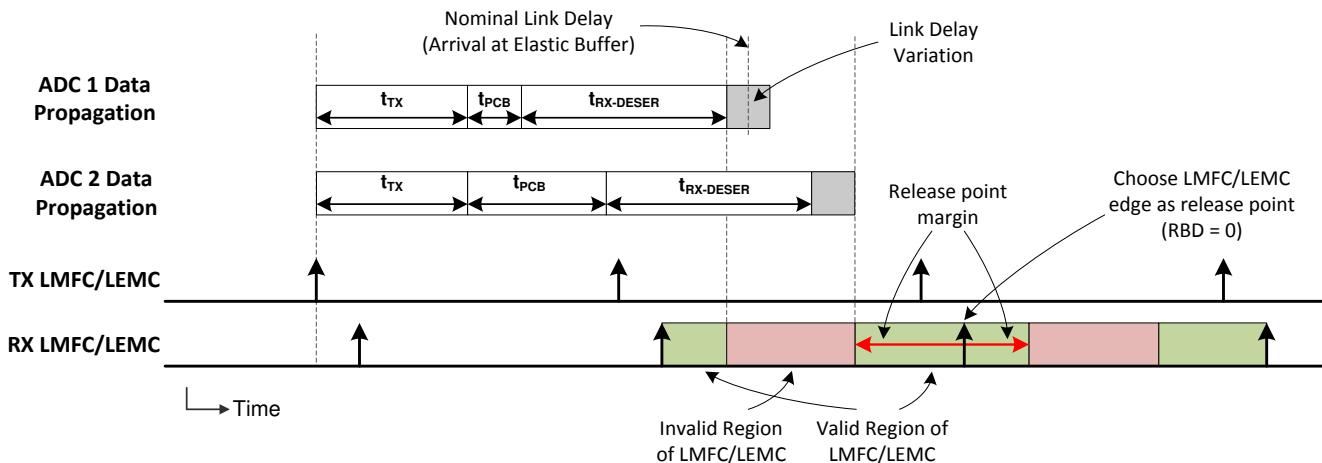

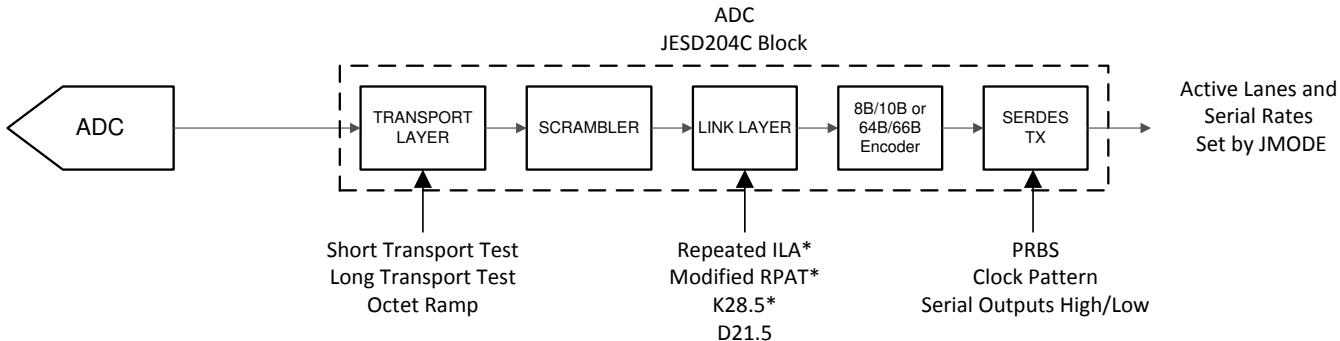

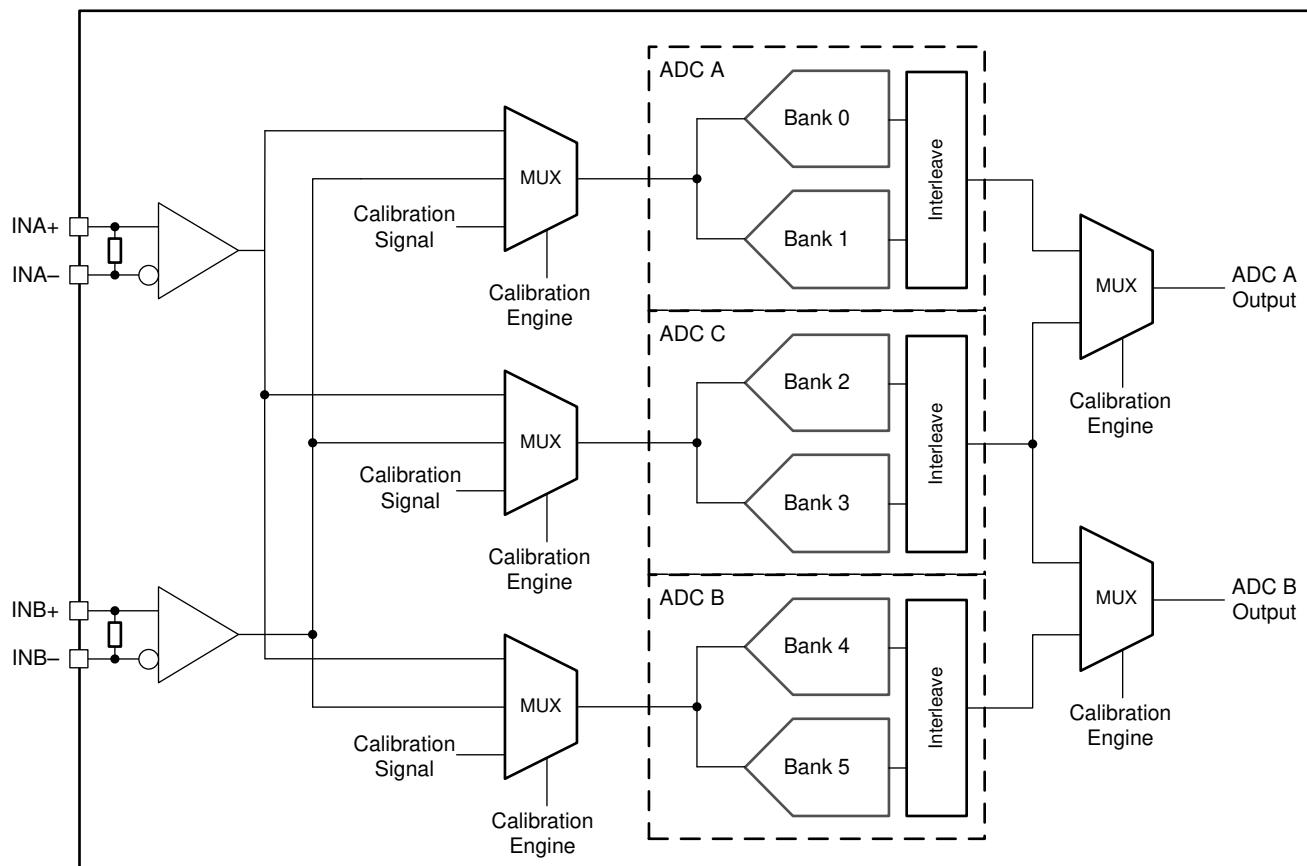

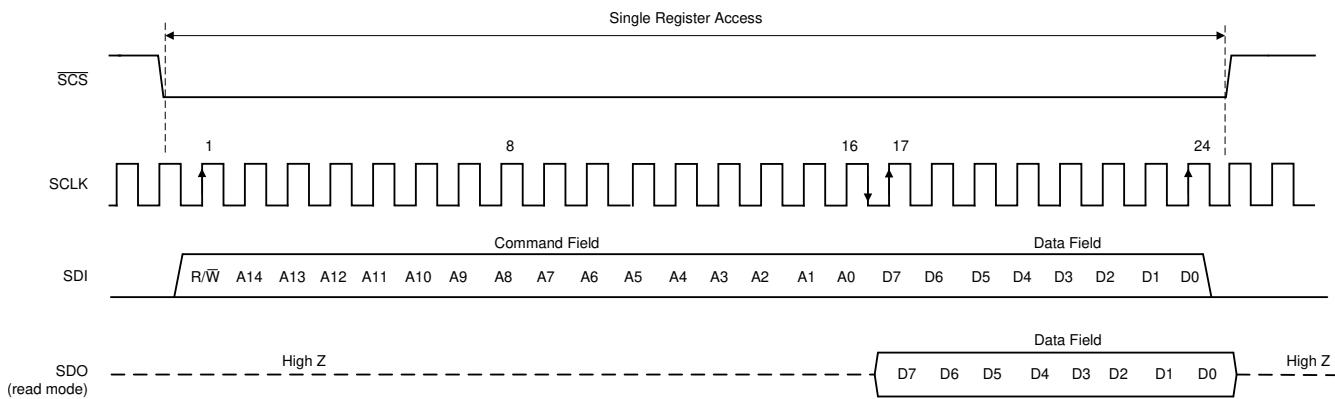

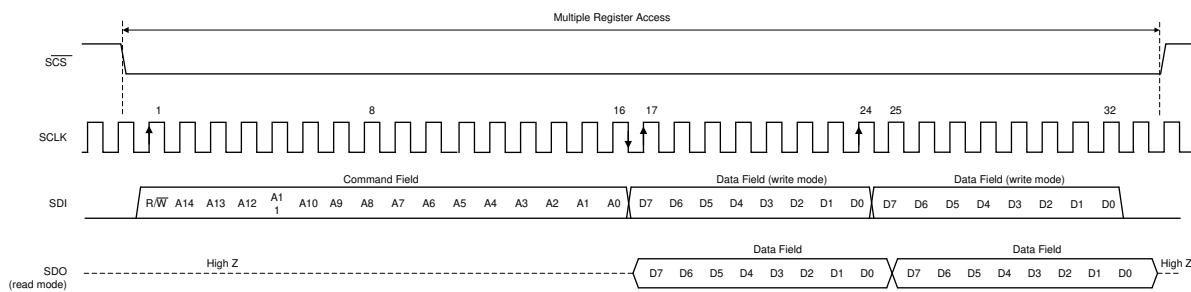

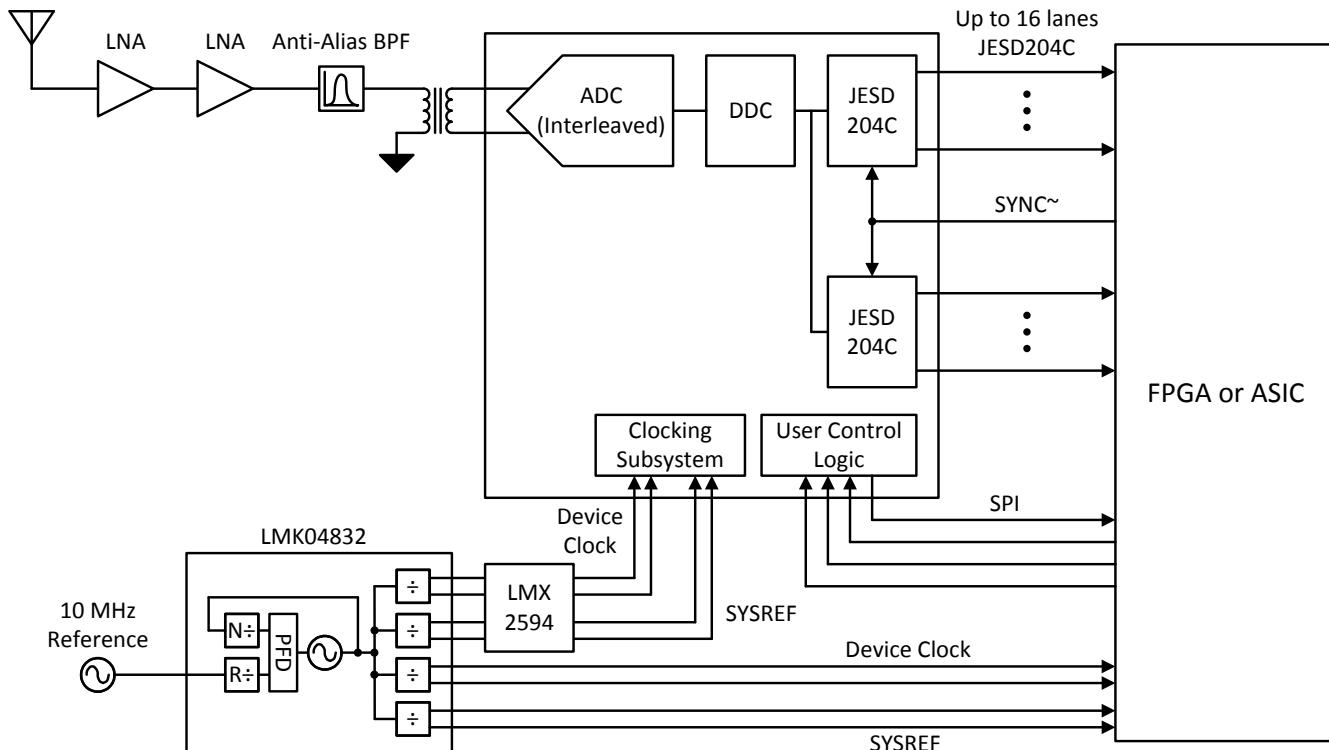

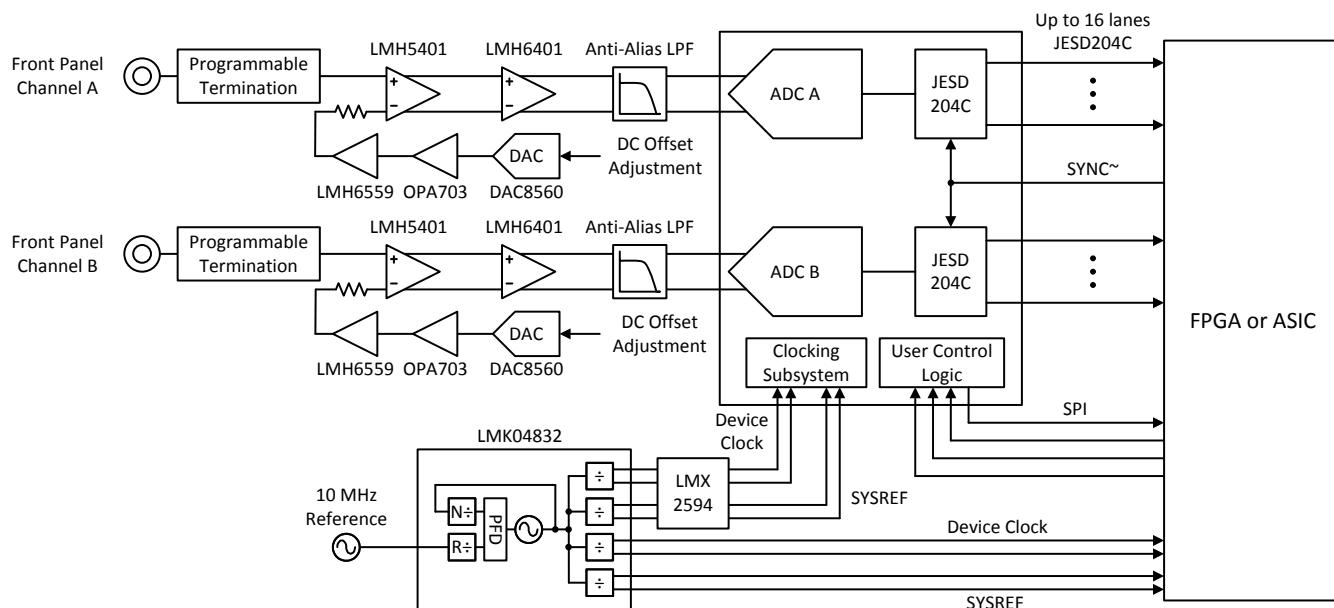

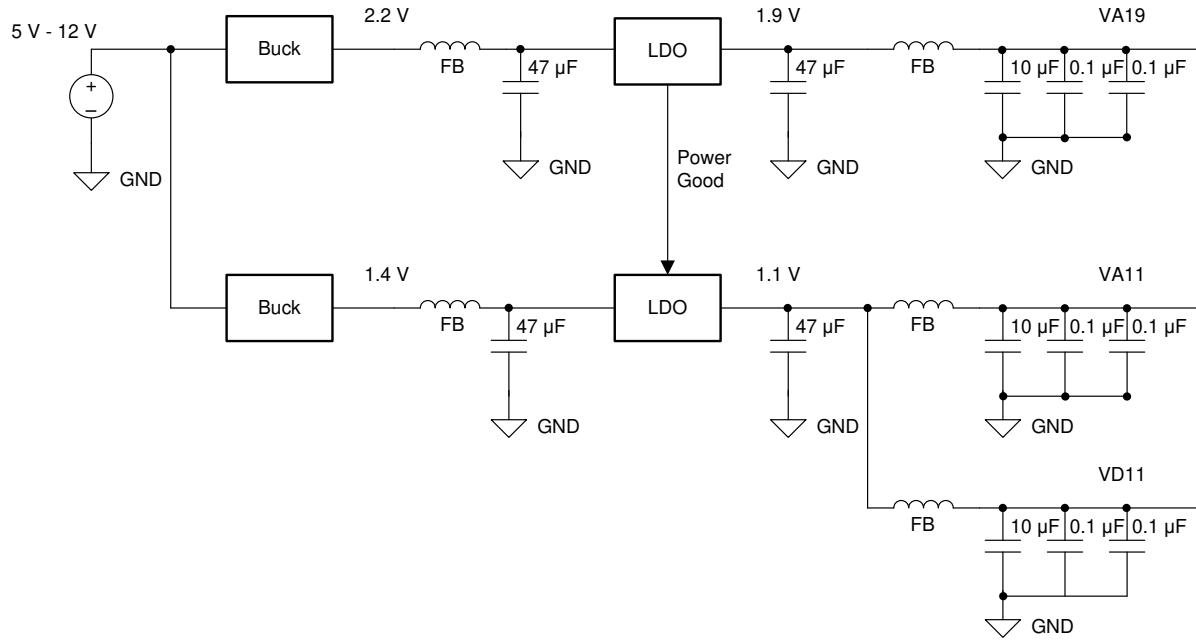

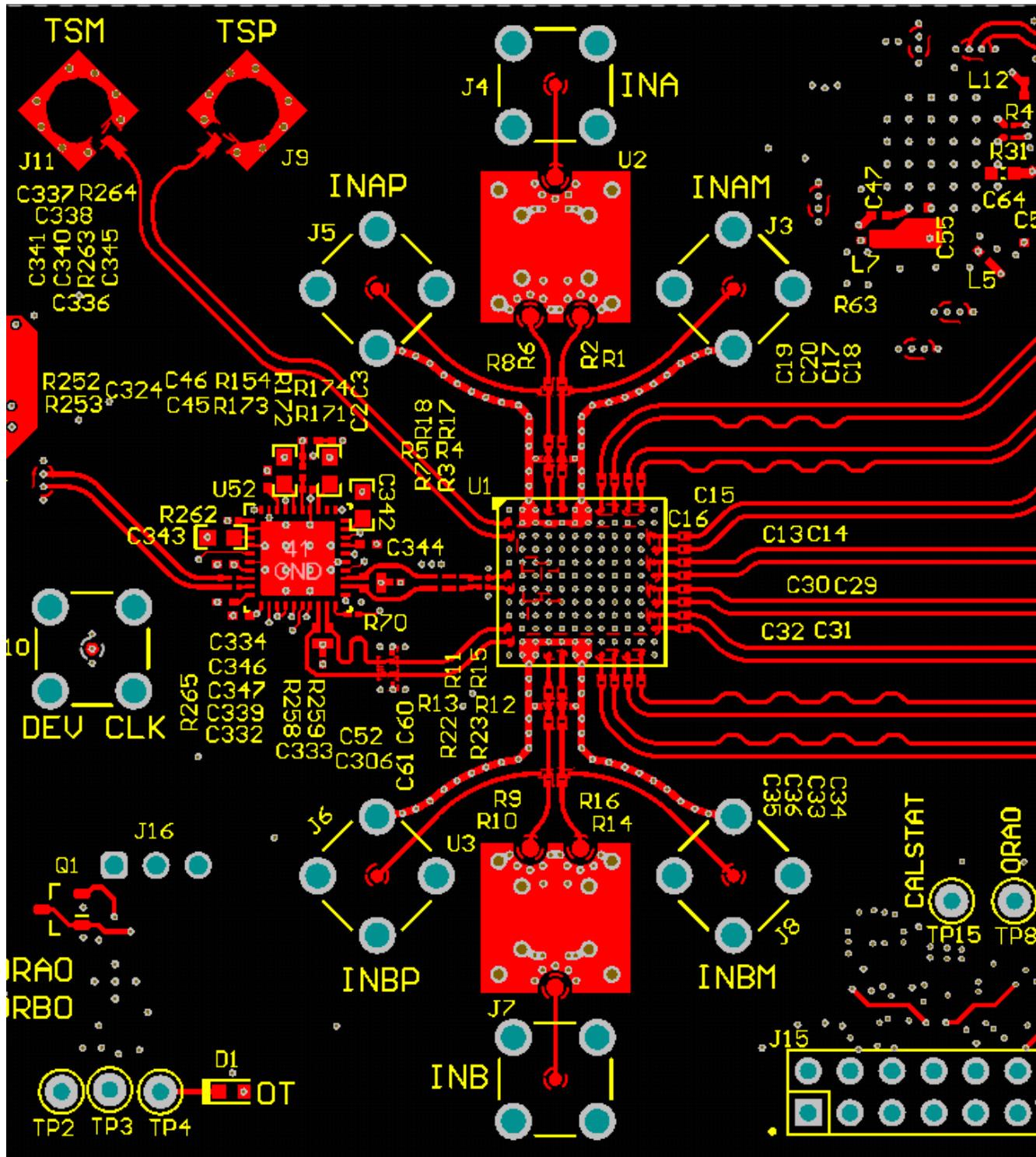

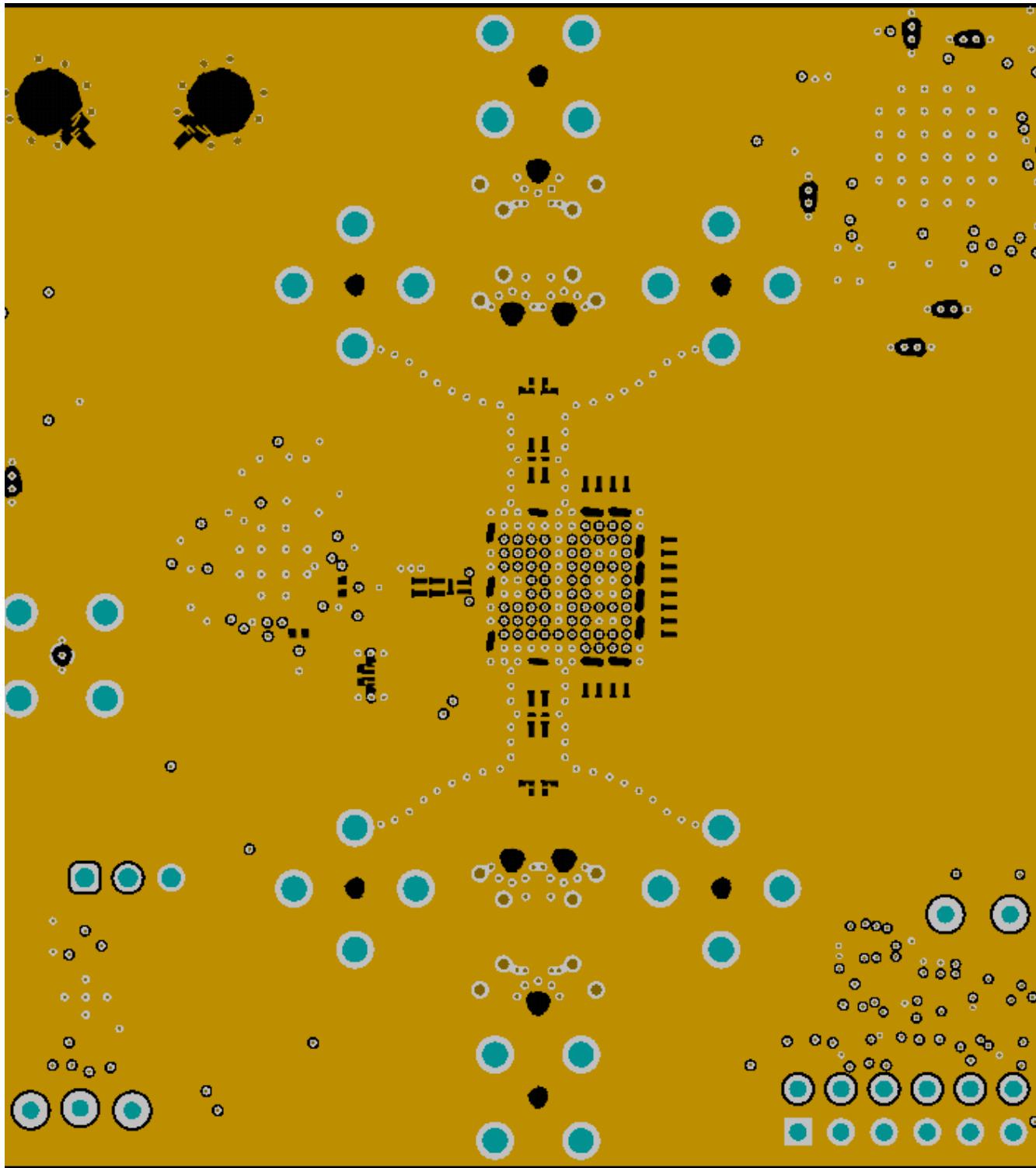

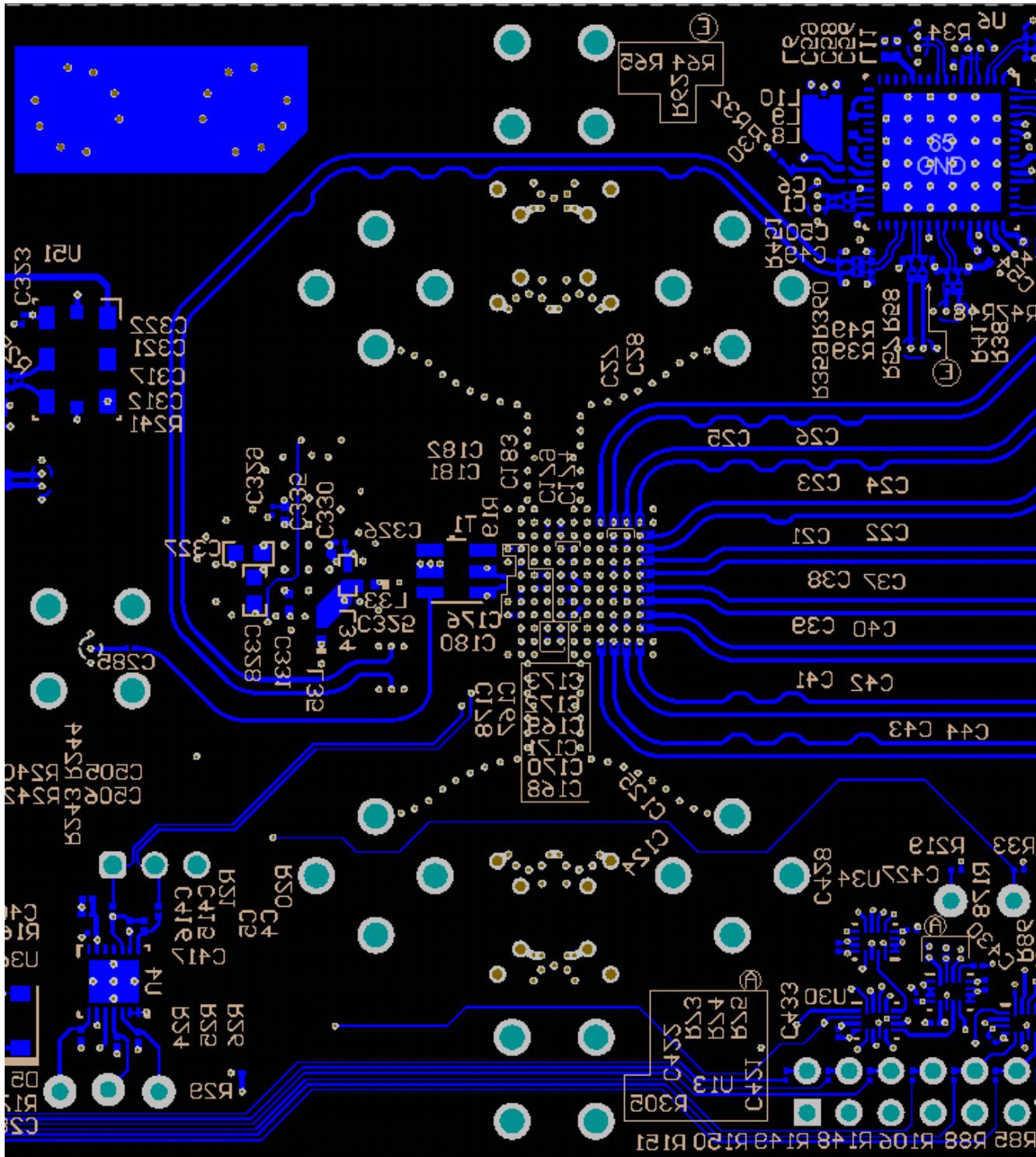

|      |                               | $f_{\text{IN}} = 7997\text{MHz}$ | $A_{\text{IN}} = -1\text{dBFS}$                                           | 50  |     |      |